# DEFT: Differentiable Automatic Test Pattern Generation

Wei Li, Yan Zou, Yixin Liang, José Moura and Shawn Blanton

Carnegie Mellon University

## Abstract

Modern IC complexity drives test pattern growth, with the majority of patterns targeting a small set of hard-to-detect (HTD) faults. This motivates new ATPG algorithms to improve test effectiveness specifically for HTD faults. This paper presents DEFT (Differentiable Automatic Test Pattern Generation), a new ATPG approach that reformulates the discrete ATPG problem as a continuous optimization task. DEFT introduces a mathematically grounded reparameterization that aligns the expected continuous objective with discrete fault-detection semantics, enabling reliable gradient-based pattern generation. To ensure scalability and stability on deep circuit graphs, DEFT integrates a custom CUDA kernel for efficient forward-backward propagation and applies gradient normalization to mitigate vanishing gradients. Compared to a leading commercial tool on two industrial benchmarks, DEFT **improves HTD fault detection by 21.1% and 48.9%** on average under the same pattern budget and comparable runtime. DEFT also supports practical ATPG settings such as partial assignment pattern generation, producing patterns with **19.3% fewer 0/1 bits** while still **detecting 35% more faults**. These results indicate DEFT is a promising and effective ATPG engine, offering a valuable complement to existing heuristic.

## 1 Introduction

Pattern sets are growing due to the increasing circuit size [1] and the adoption of fault models with much larger fault universes (cell-aware [2], PEPR [3], etc.). A large portion of these patterns is dedicated to only a small set of hard-to-detect (HTD) faults. For instance, on the NVDLA benchmark, 71.8% of patterns are generated for the last 1% of faults in a MAC cell. This motivates new ATPG approaches that more effectively target HTD faults, curb pattern growth, and scale to large designs.

Two main avenues have been explored, each with critical limitations: 1) AI-driven Heuristics: Methods using reinforcement learning [4] seek to improve the decision-making of traditional heuristic solvers. These approaches face significant scalability hurdles. 2) SAT-based Methods: Reformulating ATPG as a Boolean Satisfiability (SAT) problem is highly effective for proving fault redundancy. However, this approach suffers from a mismatch: SAT solvers are optimized for decision problems (“is this fault testable?”), whereas ATPG has evolved into an optimization problem (“find a minimal pattern set to maximize the fault coverage”). While extendable, SAT’s efficiency drops precipitously when applied to large-scale test compression, often resulting in an increase in the number of tests required to achieve desired levels of fault coverage [5].

To overcome these scalability bottlenecks and improve test effectiveness on HTD faults, differentiable programming emerges as a promising approach by reformulating discrete test generation as continuous optimization on a relaxed, differentiable circuit graph. Despite its potential for gradient-based search, there is a fundamental conceptual barrier: the inherent **semantic mismatch** between continuous relaxations and the discrete, non-smooth semantics of fault activation and error propagation. A continuous optimizer may converge to some values whose corresponding binary test pattern fails to detect the fault (see an example in Figure 1).

To address the barrier, we introduce a new reparameterized formulation that yields a continuous objective whose expected value is provably aligned with the discrete ATPG detection semantics. To overcome the gradient sparsity in early optimization stages, DEFT supplements this formulation with a vanishing exploration term that provides smooth search signals while preserving the final alignment.

While this reparameterization provides the conceptual key, scaling it to industrial circuits requires solving two practical challenges: 1) computational efficiency, as the forward and backward propagation through the massive computation graph of a large circuit creates a performance bottleneck, and 2) extreme graph depth, an inherent property of circuits that leads to vanishing gradient issues during optimization.

We propose **DEFT** (Differentiable Automatic Test Pattern Generation), an ATPG engine designed to systematically overcome these obstacles. DEFT converts the circuit into a differentiable computation graph, constructs a reparameterization framework to capture the expected discrete detection semantics, and optimizes input logits using gradient ascent. To ensure practical scalability and stability, DEFT employs gradient normalization to stabilize optimization on extremely deep graphs and implements a custom CUDA kernel, which achieves **4x-26x speedup** and **nearly 2x memory reduction** over a standard PyTorch+DGL [6] implementation. Evaluated on industrial benchmarks, DEFT improves HTD fault detection by 21.1% and 48.9% on average under the same pattern budget while achieving comparable runtime. DEFT is also flexible for practical ATPG requirements such as X-bit-aware pattern generation: it produces patterns with 19.3% fewer 0/1 bits while still detecting 35% more faults. Our contributions are summarized as follows:

- We develop a reparameterized differentiable ATPG formulation that mathematically resolves the mismatch between continuous relaxations and discrete fault semantics.

- We propose DEFT, a scalable and effective ATPG engine that addresses the practical challenges of computation efficiency and extreme graph depth.

- We implement a custom CUDA kernel that achieves 4x-26x speedup and about 2x memory savings over a PyTorch+DGL baseline.

- We validate DEFT on HTD fault sets from industrial benchmarks and compare it with a leading commercial tool, demonstrating 21.1% - 48.9% higher fault detections on average under the same pattern budget and producing 19.3% fewer specified bits in partial assignment settings.

## 2 Related Work

### 2.1 Automatic Test Pattern Generation (ATPG)

Structural ATPG algorithms like PODEM [7] and FAN [8] have dominated industrial applications due to their high efficiency and scalability. Their limitation becomes apparent on hard-to-detect (HTD) faults, where the final 1% of untested faults can consume over 71.8% of the total test patterns (see Table 2).

Recent work leverages machine learning to improve these heuristic algorithms. SmartATPG [4], for example, employs reinforcement

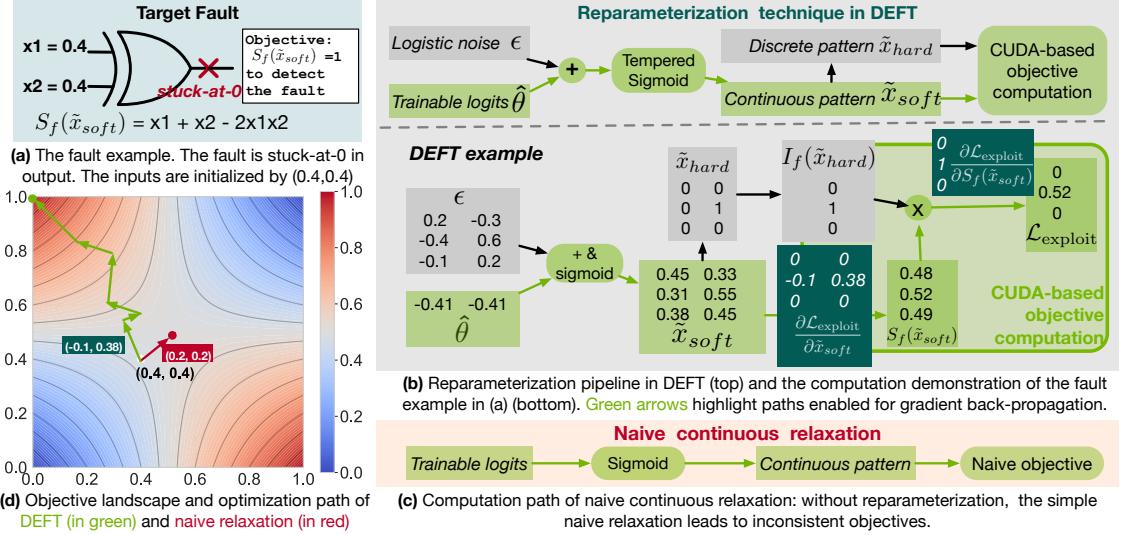

Figure 1: The reparameterization technique in DEFT vs. naive continuous relaxation.

learning to reduce backtracks with a better decision policy. A primary challenge for such methods is the inference overhead introduced at each decision step, which struggles to compete with the CPU-cycle-level efficiency of traditional heuristics.

SAT-based ATPG encodes the search problem into a Boolean Satisfiability (SAT) instance. This approach excels at resolving complex HTD faults and is highly effective for proving fault redundancy. However, SAT-based ATPG suffers from several fundamental limitations. First is a scalability challenge on large designs. Second, as noted in the introduction, is a mismatch: SAT is a decision framework, not an optimization one [9]. This makes it difficult to efficiently solve for minimal pattern sets or perform multi-target ATPG, leading to “pattern inflation” [5]. Third, SAT-based ATPG is inherently a per-fault, non-multi-target solver. Without the extensive global compaction heuristics available in commercial tools, the final test set is often much larger. Even hybrid approaches like PastATPG [5], which uses partial-assignment SAT, still generate larger test sets than highly optimized commercial tools.

## 2.2 Differentiable Programming for EDA

Differentiable Programming (DP) reframes discrete problems as continuous optimization tasks, unlocking gradient-based optimization and the massive parallelism of modern GPUs. This paradigm has achieved state-of-the-art results in several EDA domains, including placement[10], routing[11], and timing analysis[12].

A common thread in these successes is the **semantic alignment** between gradients in the continuous model and the problem’s underlying nature. In placement [10], the gradient has a clear physical meaning (electrostatic force) that guides the optimizer. In timing [12], the gradient is the classical timing sensitivity.

This fundamental alignment breaks for ATPG, where the optimization goal is fundamentally discrete: a binary test pattern. This disparity creates a “semantic mismatch”, where the gradient sometimes even misleads the optimizer away from valid test patterns. Figure 1 illustrates this misalignment on a simple XNOR circuit, where naive continuous relaxation finds a floating-point solution (0.5, 0.5) that discretizes to either (0, 0) or (1,1), neither of which detects the fault. Prior work on differentiable logic circuits (e.g., for logic synthesis [13] or neural network exploration [14]) could

tolerate this gap because their objectives only required functional approximation or “soft” relaxations of logic. ATPG, however, requires preserving strict boolean semantics to model discontinuous events like fault activation and propagation. Although prior work has explored continuous relaxations for ATPG [15], our experiments show that without resolving this semantic mismatch, direct relaxation breaks down on industrial-scale circuits.

DEFT overcomes this specific barrier by introducing a reparameterized formulation whose expected continuous objective is aligned with the discrete fault-detection goal. This alignment enables a reliable gradient-based search that, unlike SAT-based methods, naturally supports multi-fault objectives and global pattern-sharing.

## 3 Problem Formulation

A discrete input pattern  $x \in \{0, 1\}^n$  detects fault  $f$  if the output of the fault-free circuit differs from the output of the faulty circuit. We define a discrete indicator function  $I_f : \{0, 1\}^n \rightarrow \{0, 1\}$  that formalizes this.  $I_f(x)$  returns 1 if the pattern  $x$  detects  $f$  (i.e., at least one output bit differs between the fault-free and faulty circuits) and 0 otherwise. The goal of test pattern generation is to find any pattern  $x^*$  that detects the fault. This can be expressed as a discrete optimization problem:

$$\max_{x \in \{0, 1\}^n} I_f(x) \quad (\text{DEFT-P1})$$

An optimal solution  $x^*$  to equation DEFT-P1 is any pattern for which  $I_f(x^*) = 1$ .

## 4 Differentiable Reparameterization for ATPG

We present the mathematical formulation that transforms the discrete problem of ATPG into a continuous optimization problem, keeping the fault-detection semantics intact. The framework consists of three stages:

- (1) **Discrete Problem (DEFT-P1):** The original, discrete ATPG objective, as explained in Section 3.

- (2) **Probabilistic Reframing (DEFT-P2):** A conceptual reframing of the problem as maximizing an expected value.

- (3) **Differentiable Surrogate (DEFT-P3):** A practical, differentiable objective function based on reparameterization, which can be optimized with gradient ascent.

## 4.1 Probabilistic Reframing

The core difficulty in ATPG is that the test pattern is inherently discrete — changing any single bit may flip a fault from detectable to undetectable. Directly optimizing over the  $\{0,1\}$  space (DEFT-P1) is therefore non-differentiable. To enable gradient-based search, we first reinterpret a binary pattern as a probability distribution over patterns, and then optimize its expected fault-detection probability. This leads to the probabilistic formulation in DEFT-P2.

Let  $\theta \in [0,1]^n$  be a vector of continuous parameters, where each  $\theta_i$  defines the probability for an independent Bernoulli distribution. This defines a product distribution  $p(\cdot|\theta)$  over  $\{0,1\}^n$ :

$$p(x|\theta) = \prod_{i=1}^n \theta_i^{x_i} (1-\theta_i)^{1-x_i} \quad (1)$$

We can now reframe the optimization goal: instead of finding a single discrete pattern  $x$ , we seek optimal parameters  $\theta^*$  that maximize the *expected* detection probability over the distribution  $p(\cdot|\theta)$ .

$$\max_{\theta \in [0,1]^n} J_f(\theta) \quad \text{where} \quad J_f(\theta) = \mathbb{E}_{x \sim p(\cdot|\theta)} [I_f(x)] \quad (\text{DEFT-P2})$$

Then the following statement holds:

**THEOREM 4.1 (FORMULATION EQUIVALENCE<sup>1</sup>).** *The discrete problem equation DEFT-P1 from Section 3 has a solution (i.e., a detecting pattern  $x^*$  exists) if and only if the optimal value of the probabilistic problem equation DEFT-P2 is 1.*

$$\max_{x \in \{0,1\}^n} I_f(x) = 1 \iff \max_{\theta \in [0,1]^n} J_f(\theta) = 1$$

While maximizing this expectation in DEFT-P2 is tautologically equivalent to finding a distribution whose probability mass is concentrated on detecting patterns (i.e.,  $J(\theta^*) = 1$ , which implies all non-detecting patterns have zero probability), this formulation is not directly solvable. Its value is conceptual: it shifts the problem from a discrete search for  $x$  to a continuous optimization of the parameters  $\theta$ . The core technical challenge is to formulate a differentiable estimator for this expectation.

## 4.2 Differentiable Surrogate via Reparameterization

To optimize equation DEFT-P2 with gradients, we must overcome the non-differentiable sampling operation  $x \sim p(\cdot|\theta)$ . We use the Gumbel-Softmax reparameterization trick [16] to create a differentiable computation path, including the following steps:

- (1) **Logit-Space Parameterization:** We reparameterize  $\theta \in [0,1]^n$  with unconstrained logits  $\hat{\theta} \in \mathbb{R}^n$ , where  $\theta_i = \sigma(\hat{\theta}_i)$ .

- (2) **Reparameterization:** We rewrite the discrete sample  $x$  as a deterministic function of the logits  $\hat{\theta}$  and an independent Logistic noise vector  $\epsilon$ . Define the discrete pattern  $\tilde{x}_{hard}$  as:

$$\tilde{x}_{hard}(\hat{\theta}, \epsilon)_i = \mathbb{I}(\hat{\theta}_i + \epsilon_i > 0) \quad (2)$$

Using logistic reparameterization<sup>2</sup>, the expectation from equation DEFT-P2 as can be rewritten as:

$$J_f(\hat{\theta}) = \mathbb{E}_{\epsilon \sim \text{Logistic}(0,1)^n} [I_f(\tilde{x}_{hard}(\hat{\theta}, \epsilon))] \quad (3)$$

- (3) **Hybrid Surrogate Objective:** The objective in Equation 3 is still not differentiable: The term  $I_f(\tilde{x}_{hard})$  is a 0/1 indicator, and its gradient with respect to  $\hat{\theta}$  is zero almost everywhere. To create a trainable signal, we must replace the discrete objective

<sup>1</sup>Proof can be found in the appendix: <https://anonymous.4open.science/r/DEFT-Appendix-47D0/>

<sup>2</sup>See Lemma 1.2 in appendix for details.

$I_f(\tilde{x}_{hard})$  inside the expectation with a differentiable surrogate. Inspired by the method used in [17], we create a hybrid surrogate that combines the discrete indicator with a continuous, differentiable signal.

- A **continuous surrogate pattern**  $\tilde{x}_{soft}$ , which is the Gumbel-Softmax relaxation:

$$(\tilde{x}_{soft})_i(\hat{\theta}, \epsilon, \tau) = \sigma\left(\frac{\hat{\theta}_i + \epsilon_i}{\tau}\right) \quad (4)$$

where  $\tau$  is an annealed temperature parameter.

- A **differentiable surrogate signal**  $S_f : [0,1]^n \rightarrow \mathbb{R}^+$ , which is the continuous relaxation of the detection function  $I_f$  and fully differentiable w.r.t.  $\hat{\theta}$ .

We now formally define our new objective,  $\mathcal{L}_{\text{exploit}}^f$ , by replacing the discrete  $I_f(\tilde{x}_{hard})$  in Equation 3 with this hybrid surrogate,  $S_f(\tilde{x}_{soft}) \cdot I_f(\tilde{x}_{hard})$ .

$$\mathcal{L}_{\text{exploit}}^f(\hat{\theta}) = \mathbb{E}_{\epsilon} \left[ \underbrace{S_f(\tilde{x}_{soft}(\hat{\theta}, \epsilon, \tau))}_{\text{Continuous Surrogate}} \cdot \underbrace{I_f(\tilde{x}_{hard}(\hat{\theta}, \epsilon))}_{\text{Discrete Indicator}} \right] \quad (\text{DEFT-P3})$$

This formulation is the core of the “exploit” objective. It includes two key components: The **discrete indicator**  $I_f(\tilde{x}_{hard})$  acts as a “gate.” It ensures the objective is zero if the discrete pattern fails to detect the fault. The **continuous surrogate**  $S_f(\tilde{x}_{soft})$  provides a non-zero, differentiable signal (a gradient path) when the discrete gate is “open” (i.e.,  $I_f(\tilde{x}_{hard}) = 1$ ).

By maximizing  $\mathcal{L}_{\text{exploit}}^f$ , we optimize the logits  $\hat{\theta}$  to produce samples that are both discretely correct ( $I_f = 1$ ) and have a strong continuous signal ( $S_f > 0$ ).

## 4.3 Gradient Calculation of the Exploit Signal

The gradient of the “exploit” objective equation DEFT-P3 is computed by treating the discrete indicator  $I_f(\tilde{x}_{hard})$  as a constant with respect to the gradient operator. Since the gradient of the discrete indicator  $I_f(\tilde{x}_{hard})$  is zero almost everywhere, we adopt a straight-through (ST) estimator that ignores the gradient through  $I_f(\tilde{x}_{hard})$  and only propagates gradients through the continuous surrogate path  $S_f(\tilde{x}_{soft})$ .

$$\nabla_{\hat{\theta}} \mathcal{L}_{\text{exploit}}^f(\hat{\theta}) = \nabla_{\hat{\theta}} \mathbb{E}_{\epsilon} [S_f(\tilde{x}_{soft}) \cdot I_f(\tilde{x}_{hard})] \quad (5)$$

$$\approx \mathbb{E}_{\epsilon} \left[ \underbrace{\nabla_{\hat{\theta}} S_f(\tilde{x}_{soft}(\hat{\theta}, \epsilon, \tau))}_{\text{Continuous gradient path}} \cdot \underbrace{I_f(\tilde{x}_{hard}(\hat{\theta}, \epsilon))}_{\text{Discrete gate (treated as const.)}} \right] \quad (6)$$

This expectation is estimated using Monte Carlo sampling, i.e., by averaging over  $K$  noise samples:

$$\nabla_{\hat{\theta}} \mathcal{L}_{\text{exploit}}^f(\hat{\theta}) \approx \frac{1}{K} \sum_{k=1}^K \left[ \nabla_{\hat{\theta}} S_f(\tilde{x}_{soft}^{(k)}) \cdot I_f(\tilde{x}_{hard}^{(k)}) \right] \quad (7)$$

## 4.4 Handling Zero Gradients: The Explore Objective

A problem arises with the gradient in Equation (7). In the early training stage, the probability  $P(I_f(\tilde{x}_{hard}) = 1)$  is often extremely low, particularly for complex and deep circuits. This means it is highly likely that no sampled pattern  $\tilde{x}_{hard}^{(k)}$  will detect the fault,

resulting in  $I_f(\tilde{x}_{hard}^{(k)}) = 0$  for all  $K$  samples, causing the entire gradient estimate collapsing to zero, leading to optimization stagnation. To solve this, we introduce a complementary “**explore**” objective,  $\mathcal{L}_{\text{explore}}^f$ , serving as a differentiable proxy for the discrete goal and a bootstrap mechanism: when  $I_f(\tilde{x}_{hard}) = 0$  silences the exploit gradient,  $\mathcal{L}_{\text{explore}}^f$  ensures a continuous, non-zero differentiable signal is maintained.  $\mathcal{L}_{\text{explore}}^f(\hat{\theta})$  is defined as the expected continuous surrogate signal  $\mathcal{L}_{\text{explore}}^f(\hat{\theta}) = \mathbb{E}_\epsilon [S_f(\tilde{x}_{soft}(\hat{\theta}, \epsilon, \tau))]$ . The final objective combines these terms using an annealing schedule  $w_{\text{explore}}$  to dynamically control the training focus:

$$\mathcal{L}_{\text{final}}^f(\hat{\theta}) = (1 - w_{\text{explore}}) \cdot \mathcal{L}_{\text{exploit}}^f(\hat{\theta}) + w_{\text{explore}} \cdot \mathcal{L}_{\text{explore}}^f(\hat{\theta}) \quad (8)$$

$w_{\text{explore}}$  transitions from 1 (prioritizing rapid search in the continuous active region) to 0 (prioritizing the detection of a discretely valid pattern). This transition is crucial because only  $\mathcal{L}_{\text{exploit}}^f$  is mathematically aligned with the true discrete fault-detection semantics, guaranteeing a discretely correct final pattern.

## 5 DEFT Framework

In this section, we present the DEFT framework. Section 5.1 outlines the overall workflow, Section 5.2 describes the scalability mechanisms, namely the custom CUDA kernel and gradient normalization, and Section 5.3 introduces the joint multi-fault and multi-pattern formulation and extensions such as partial assignment ATPG.

### 5.1 DEFT Framework and Graph Construction

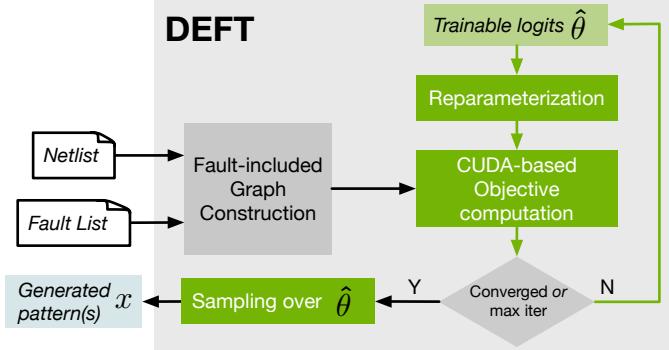

Figure 2 illustrates the workflow of DEFT. Given a circuit netlist and a target fault list  $\mathcal{F}$ , we first transform the circuit into a differentiable computation graph. We follow the well-established approach [14, 17] by modeling the circuit as a directed acyclic graph (DAG) whose nodes are logic gates and edges are wires. For nets with fan-out, we introduce a virtual node to explicitly represent each branch. The Boolean function of each gate is replaced with a smooth relaxation over  $[0, 1]$  so that the gradients can flow end-to-end. In this work, we use simple probabilistic logic as a surrogate. Table 1 summarizes the probabilistic functions used for general 2-input gates, note that DEFT supports arbitrary gate types by defining their corresponding continuous relaxations.

Figure 2: Overview of the DEFT Framework.

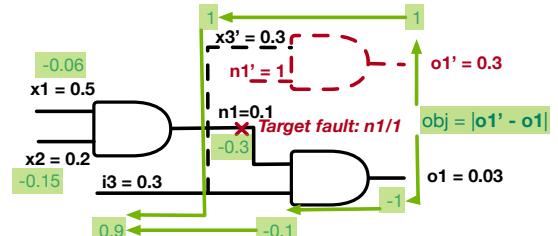

For each target fault  $f \in \mathcal{F}$ , DEFT constructs a *fault-included graph*. This involves duplicating the fan-out cone of the fault site (or the union of cones for multi-site faults) into fault-free (the original) and faulty copies. An example is shown in Figure 4.

The core of DEFT is an optimization loop that optimizes a set of trainable input logits  $\hat{\theta} \in \mathbb{R}^n$ , which parameterize the relaxed input

| Gate Function | AND      | NAND         | OR               | NOR           | XOR               | XNOR |

|---------------|----------|--------------|------------------|---------------|-------------------|------|

| $ab$          | $1 - ab$ | $a + b - ab$ | $(1 - a)(1 - b)$ | $a + b - 2ab$ | $1 - a - b + 2ab$ |      |

Table 1: Examples of 2-input  $(a, b)$  gate and corresponding continuous functions used in DEFT.

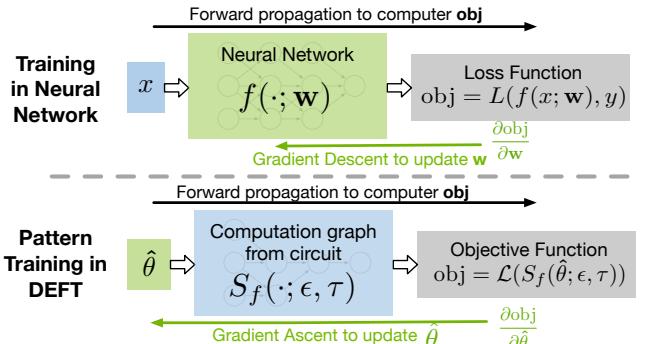

space. Figure 3 highlights the analogy between this process and standard neural network training. In each iteration, these logits are passed through the reparameterization step (detailed in Section 4) to generate  $K$  continuous samples  $\tilde{x}_{soft}$ . These samples are used to compute the continuous surrogate signal  $S_f(\tilde{x}_{soft})$ , which is the relaxed detection function:

$$S_f(\tilde{x}_{soft}) = \max_{j \in \text{POs}} |\mathcal{G}(\tilde{x}_{soft})_{PO_j}^{\text{fault-free}} - \mathcal{G}(\tilde{x}_{soft})_{PO_j}^{\text{faulty}}| \quad (9)$$

where  $\mathcal{G}(\tilde{x}_{soft})_{PO_j}^{\text{fault-free}}$  and  $\mathcal{G}(\tilde{x}_{soft})_{PO_j}^{\text{faulty}}$  are the  $j$ -th PO values from their respective fan-out cones, evaluated through the continuous computation graph. Note that while Equation (9) is for stuck-at-fault, DEFT can be readily extended to support general fault tuples [18]. For instance, the objective can be formulated to satisfy condition tuples by minimizing  $|\mathcal{G}(\tilde{x}_{soft})_i - \text{condition\_value}_i|$ . We leave the exploration of other advanced fault models for DEFT as future work.

Combining Equation (9) and Equation (8), gradients of the final objective are back-propagated to update  $\hat{\theta}$  via gradient ascent. Figure 4 gives an example to the value propagation and gradient backpropagation. After convergence or a maximum iteration limit, DEFT samples over the optimized logits  $\hat{\theta}$  to produce the final discrete test pattern.

Figure 3: Analogy Between Neural Network Training and Differentiable ATPG in DEFT. Green (blue) boxes represent trainable (fixed) components.

### 5.2 Scaling to Industrial Circuits

Scaling DEFT to industrial circuits requires solving two practical challenges: computational efficiency and optimization stability for extremely deep graphs. To address these issues, we present two

Figure 4: An example of DEFT for a stuck-at-1 fault at net n1. The green represents gradient flow and red means the copied fanout cone introduced by fault.

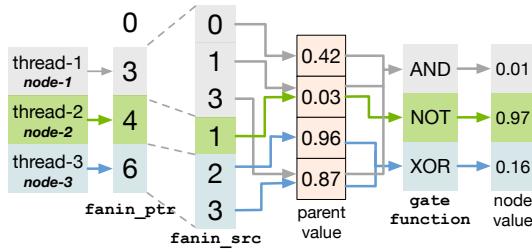

Figure 5: Illustration of continuous value propagation using custom CUDA kernel in DEFT.

key techniques in this section: a custom CUDA kernel and gradient normalization.

### 5.2.1 Custom CUDA Kernel for Efficient Propagation

Our simulator exploits GPU parallelism to propagate values over the large computation graphs. At each topological level, the host identifies the nodes in that level and launches a CUDA kernel. As shown in Figure 5, an index array stored on the GPU maps each CUDA thread to a gate. Using a node-centric Compressed Sparse Row structure (CSR) layout (`fanin_ptr`, `fanin_src`), each thread locates its fan-in range, gathers parent value, computes the output based on the gate function, and writes the result to a level-output tensor, which is then scattered back to the global node tensor. This design replaces DGL’s generic pull abstraction with a single fused kernel that performs fan-in reduction directly on dense tensors with coalesced memory accesses.

For end-to-end training, the kernel is exposed to PyTorch as a custom autograd operator. During the forward pass, the C++ wrapper stores only the information required for backpropagation—the level indices, CSR structures, gate functions, and a compact buffer of fan-in values—while omitting global node values, substantially reducing memory usage compared to a naive autograd trace over all primitive operations.

### 5.2.2 Gradient Normalization for Deep Graphs

In probabilistic-logic relaxations, per-gate derivatives are bounded within  $[-1, 1]$ . Composed across inherently deep computation graph, this leads to vanishing gradients and slow training. As a pragmatic stabilization, we apply  $\ell_2$  normalization for all gradients w.r.t. input logits  $\hat{\theta}$ . We note that while effective, this is a stabilization technique rather than a fundamental solution. A promising direction for future work is the design of continuous relaxations for logic gates that are less susceptible to vanishing gradients.

## 5.3 Multi-Target Optimization and Extensions

### 5.3.1 Joint Multi-Fault and Multi-Pattern Optimization

Unlike traditional ATPG methods that treat faults independently and rely on post-processing for compaction, DEFT naturally supports joint multi-fault and multi-pattern optimization. By merging the fan-out cones of all target faults  $\mathcal{F}$  into a single computational graph, DEFT optimizes a batch of  $T$  candidate patterns, parameterized by logits  $\hat{\theta} \in \mathbb{R}^{n \times T}$ , against a unified objective:

$$\mathcal{L}_{\text{final}}^f(\hat{\theta}) = \sum_{f \in \mathcal{F}} \max_{t \in \{0, \dots, T\}} \left( \mathcal{L}_{\text{final}}^f(\hat{\theta}_t) \right) \quad (10)$$

Moreover, DEFT naturally extends to a batched run by optimizing  $B$  independently initialized pattern sets in parallel, yielding  $\hat{\theta} \in \mathbb{R}^{n \times T \times B}$ , which stabilizes convergence.

### 5.3.2 Extensions to Practical ATPG Requirements

DEFT’s differentiable objective readily accommodates common industrial constraints.

For example, to produce patterns with more don’t-cares (X-bits), which facilitates downstream compaction, we add an X-promoting penalty:  $\mathcal{L}_X(\hat{\theta}) = \lambda \sum_{i=1}^n \sum_{t=1}^T |(\hat{x}_{\text{soft}})_i^t - 0.5|$ , where  $\lambda$  controls the strength. This pushes logits toward ambiguity (0.5) if the bit is not critical for detecting any target fault.

This flexibility extends to other requirements, such as low-power ATPG, up-weight detection on safety-critical POs (e.g., brake system in an automotive design), or prioritizing faults on timing-critical paths. DEFT can co-optimize the primary detection objective with these practical constraints in a single end-to-end framework.

## 6 Experiments

DEFT is implemented in Python, using PyTorch for the optimization API and a custom CUDA kernel for efficient forward and backward propagation through the computation graph. All experiments are conducted on a server equipped with four Intel E5-4620 @ 2.20 GHz CPU cores and a single NVIDIA H200 GPU.

We evaluate DEFT and a leading commercial ATPG tool on two industrial benchmarks—the Non-Cacheable Unit (NCU) from OpenSPARC T2 [19] and a MAC cell from NVDLA [20]. Academic benchmarks (e.g., ISCAS) are excluded because modern ATPG tools achieve near-perfect coverage and test effectiveness on them within minutes. All flip-flops are treated as scannable PIs/POs, and we target the combinational logic cone. While DEFT is applicable to typical cells from modern standard-cell libraries, in this work we synthesize RTL into a technology-independent netlist of primitive gates. Table 2 summarizes the benchmark characteristics, showing that 49.2% and 71.8% of patterns are generated to detect the final 1% of faults on NCU and MAC, respectively.

We compare DEFT with a leading commercial ATPG tool on hard-to-detect (HTD) stuck-at-fault sets extracted from each benchmark. The HTD sets are identified using the commercial tool under its default effort setting. For MAC, we collect 1171 remaining undetected faults after a full ATPG run. For NCU, we collect 348 remaining undetected faults for NCU after 400 patterns since there is no remaining undetected fault if we execute a full run. To provide a strong baseline, in the following evaluation of commercial tool, we set maximum compaction and coverage efforts, and the abort limit increases from default 30 to 10,000 for all runs. The maximum iteration of DEFT is 1000 — each single DEFT run can be finished within 10 minutes. Due to page limit, other experimental parameters and implementation details are available in the appendix<sup>3</sup>.

Note that this experiment setup is deliberately designed to benchmark the core ATPG engine on the most challenging faults, which dominate the test pattern count in practice. Our goal is to evaluate a new ATPG paradigm, not a feature-complete, product-level ATPG flow. A full-flow comparison would be dominated by trivial faults and by highly-engineered features orthogonal to our contribution. HTD faults capture a true computational bottleneck in ATPG, thus enabling a fair and focused comparison.

### 6.1 ATPG of HTD Faults

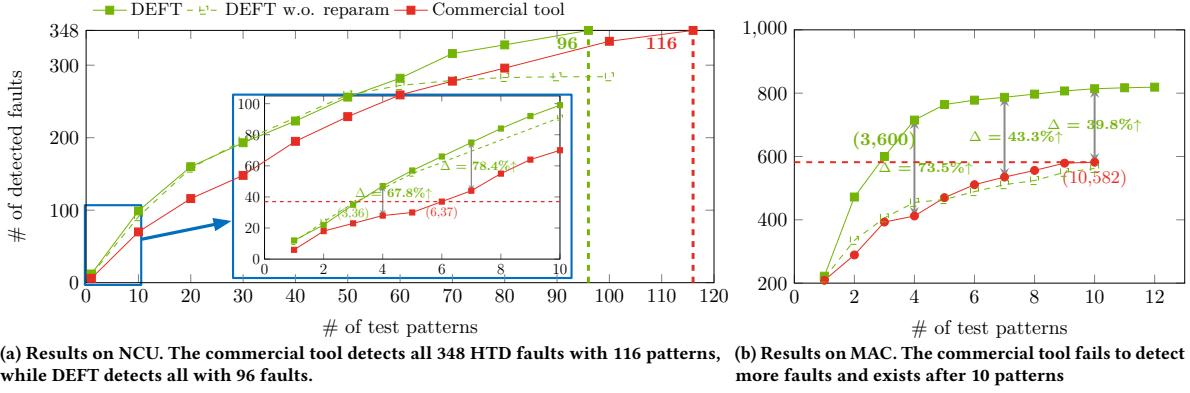

Figure 6 reports the ATPG results of DEFT and the commercial tool for the NCU and MAC benchmarks. Across both benchmarks, DEFT consistently achieves higher test effectiveness. On NCU, it

<sup>3</sup><https://anonymous.4open.science/r/DEFT-Appendix-47D0/>

(a) Results on NCU. The commercial tool detects all 348 HTD faults with 116 patterns, while DEFT detects all with 96 faults. (b) Results on MAC. The commercial tool fails to detect more faults and exists after 10 patterns

Figure 6: ATPG results of DEFT and commercial tool. y-axis is the number of detected faults.

|     | # gates | # PIs | # POs | # levels | test 1% <sup>1</sup> | # HTD <sup>2</sup> |

|-----|---------|-------|-------|----------|----------------------|--------------------|

| NCU | 112170  | 16584 | 16020 | 72       | 49.2%                | 348                |

| MAC | 445757  | 6581  | 3595  | 211      | 71.8%                | 1171               |

Table 2: Benchmark statistics used in experiments.

<sup>1</sup>‘test 1%’ is the percentage of patterns used to detect the final 1% of stuck-at faults in a full ATPG run by the commercial tool;

<sup>2</sup># HTD’ is the number of HTD faults used in experiments.

delivers 67.8-78.4% more detected faults in the low-pattern regime and maintains an average 21.1% advantage. The margin plateaus because those final faults are exceptionally difficult and cannot be simultaneously excited and propagated by a single pattern. Finally, DEFT reaches full coverage with 96 patterns, 17.8% less than the commercial tool (116 patterns). In contrast, DEFT without reparameterization (naive relaxation) initially performs comparably but fails on the final HTD faults.

On MAC, DEFT surpasses the commercial tool by detecting 600 faults in just 3 patterns, compared to 582 faults in 10. DEFT sustains a 48.9% average more detected faults and ultimately finds over 800 faults, 40% of which are missed by the commercial tool. This performance contrasts sharply with naive relaxation, underscoring the efficacy of our reparameterization.

## 6.2 CUDA Kernel Efficiency

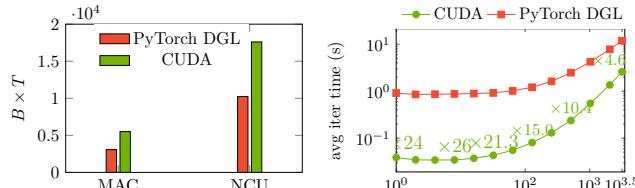

(a) Memory comparison. Bars show the maximum feasible batch-pattern combination ( $B \times T$ ). (b) Per-iteration runtime comparison on MAC (forward+backward). x-axis is the batch-pattern combination ( $B \times T$ ).

Figure 7: Performance comparison of CUDA and PyTorch DGL implementations.

As shown in Figure 7, our CUDA kernel supports about 2x larger batch-pattern capacity ( $B \times T$ ) on both benchmarks and delivers 4.6x-26x lower per-iteration runtime than the PyTorch+DGL baseline on MAC. The kernel is highly efficient, enabling over 500 patterns to be generated in parallel on MAC, with each iteration completing in less than one second.

|                  | 0/1 bits ratio (%)            | # detected faults         |

|------------------|-------------------------------|---------------------------|

| commercial Tool  | 0.393                         | 117                       |

| $\lambda = 0$    | 0.413 ( $\uparrow 5.1\%$ )    | 161 ( $\uparrow 37.6\%$ ) |

| DEFT             | 0.338 ( $\downarrow 14.0\%$ ) | 160 ( $\uparrow 36.7\%$ ) |

| $\lambda = 0.01$ | 0.317 ( $\downarrow 19.3\%$ ) | 158 ( $\uparrow 35.0\%$ ) |

| $\lambda = 0.1$  | 0.274 ( $\downarrow 30.3\%$ ) | 145 ( $\uparrow 23.9\%$ ) |

Table 3: X-bit experiment on NCU with 20 pattern limits.

To produce X-bit, DEFT set  $x_i = X$  when  $\sigma(\hat{\theta}_i) \in (0.0001, 0.9999)$ .

## 6.3 Runtime vs. Quality

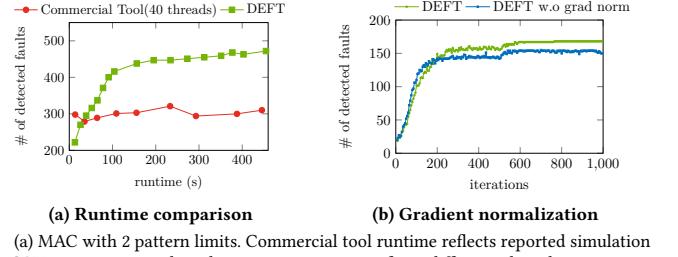

(a) Runtime comparison

(b) Gradient normalization

(a) MAC with 2 pattern limits. Commercial tool runtime reflects reported simulation CPU time using 40 threads; its variation comes from different abort-limit settings (200-10,000), while DEFT’s variance is from changing the iteration limit (20-700).

(b) NCU with 20 pattern limits.

Figure 8a compares the runtime-quality tradeoff between DEFT and the commercial tool. With about 30 seconds, DEFT achieves similar fault coverage as the commercial tool, and its fault coverage increases rapidly as runtime grows, eventually plateauing above 450 detected faults. The commercial tool exhibits limited improvement with increasing abort limits, detecting roughly 300 faults at best.

## 6.4 X-ratio and Gradient Normalization

We evaluate DEFT’s capability to produce X-bit, as shown in Table 3, where  $\lambda$  controls the X-bit regularization strength (Section 5.3.2). Compared with the commercial tool, DEFT achieves higher fault detection across all  $\lambda$  settings, improving fault detection by 23.9%-37.6%. Without regularization ( $\lambda=0$ ), DEFT attains a 0/1-bit ratio comparable to the commercial tool, indicating that optimization in the relaxed continuous space naturally sharpens only the critical PIs. As  $\lambda$  increases, the 0/1-bit ratio decreases smoothly, confirming that the regularizer effectively promotes X-bit usage. Even with strong regularization ( $\lambda=0.1$ ), DEFT retains a 23.9% advantage in detected faults while reducing the bit-ratio by 30.3%. Figure 8b shows the impact of gradient normalization. With gradient normalization, the curve converges to a slightly higher fault detection (>160), avoiding early saturation at less than 150 faults.

## 7 Conclusion

This work introduced DEFT, a differentiable ATPG framework that reformulates ATPG as a continuous optimization problem and enables scalable gradient-based search on industrial circuits. Experiments on two industrial benchmarks demonstrate substantial gains in HTD fault detection. These results highlight DEFT as a practical and extensible foundation for next-generation ATPG.

## References

- [1] “Chapter 17: Test technology,” in *Heterogeneous Integration Roadmap (HIR), 2024 Edition*, 2024, online: <https://eps.ieee.org/hir>.

- [2] F. Hapke, W. Redemund, A. Glowatz, J. Rajski, M. Reese, M. Hustava, M. Keim, J. Schloeffel, and A. Fast, “Cell-aware test,” *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 33, no. 9, pp. 1396–1409, 2014.

- [3] W. Li, C. Nigh, D. Duvalsaunt, and S. Mitra, “Pepr: Pseudo-exhaustive physically-aware region testing,” in *2022 IEEE International Test Conference (ITC)*. IEEE, 2022, pp. 314–323.

- [4] W. Li, H. Lyu, S. Liang, T. Wang, and H. Li, “Smartatpg: Learning-based automatic test pattern generation with graph convolutional network and reinforcement learning,” in *Proceedings of the 61st ACM/IEEE Design Automation Conference*, 2024, pp. 1–6.

- [5] Z. Chao, X. Zhang, X. Zhang, J. Mu, Z. Liu, S. Liang, S. Cai, J. Ye, X. Li, and H. Li, “Pastatpg: A hybrid atpg framework for better test compaction with partial assignment sat,” in *2025 62nd ACM/IEEE Design Automation Conference (DAC)*. IEEE, 2025, pp. 1–7.

- [6] M. Y. Wang, “Deep graph library: Towards efficient and scalable deep learning on graphs,” in *ICLR workshop on representation learning on graphs and manifolds*, 2019.

- [7] Goel, “An implicit enumeration algorithm to generate tests for combinational logic circuits,” *IEEE transactions on Computers*, vol. 100, no. 3, pp. 215–222, 1981.

- [8] Fujiwara and Shimono, “On the acceleration of test generation algorithms,” *IEEE transactions on Computers*, vol. 100, no. 12, pp. 1137–1144, 1983.

- [9] B. Becker, R. Drechsler, S. Eggertsglüß, and M. Sauer, “Recent advances in sat-based atpg: Non-standard fault models, multi constraints and optimization,” in *2014 9th IEEE International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS)*. IEEE, 2014, pp. 1–10.

- [10] Y. Lin, S. Dhar, W. Li, H. Ren, B. Khailany, and D. Z. Pan, “Dreamplace: Deep learning toolkit-enabled gpu acceleration for modern vlsi placement,” in *Proceedings of the 56th Annual Design Automation Conference 2019*, 2019, pp. 1–6.

- [11] W. Li, R. Liang, A. Agnesina, H. Yang, C.-T. Ho, A. Rajaram, and H. Ren, “Dgr: Differentiable global router,” in *Proceedings of the 61st ACM/IEEE Design Automation Conference*, 2024, pp. 1–6.

- [12] Y.-C. Lu, Z. Guo, K. Kunal, R. Liang, and H. Ren, “Insta: An ultra-fast, differentiable, statistical static timing analysis engine for industrial physical design applications,” in *2025 62nd ACM/IEEE Design Automation Conference (DAC)*. IEEE, 2025, pp. 1–7.

- [13] Z. Wang, J. Wang, Q. Yang, Y. Bai, X. Li, L. Chen, J. Hao, M. Yuan, B. Li, Y. Zhang *et al.*, “Towards next-generation logic synthesis: A scalable neural circuit generation framework,” *Advances in Neural Information Processing Systems*, vol. 37, pp. 99 202–99 231, 2024.

- [14] F. Petersen, C. Borgelt, H. Kuehne, and O. Deussen, “Deep differentiable logic gate networks,” *Advances in Neural Information Processing Systems*, vol. 35, pp. 2006–2018, 2022.

- [15] X. Tan, D. Thapar, D. Sahoo, A. Chaudhuri, S. Banerjee, K. Chakrabarty, and R. Parekhji, “Safety-guided test generation for structural faults,” in *2024 IEEE International Test Conference (ITC)*. IEEE, 2024, pp. 233–242.

- [16] E. Jang, S. Gu, and B. Poole, “Categorical reparameterization with gumbel-softmax,” *arXiv preprint arXiv:1611.01144*, 2016.

- [17] Z. Geng, J. Wang, X. Li, F. Zhu, J. Hao, B. Li, and F. Wu, “Differentiable integer linear programming,” in *The Thirteenth International Conference on Learning Representations*, 2025.

- [18] R. D. Blanton, K. N. Dwarakanath, and R. Desineni, “Defect modeling using fault tuples,” *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 25, no. 11, pp. 2450–2464, 2006.

- [19] Sun Microsystems, Inc., “Opensparc t2 system-on-chip (soc) design,” <https://www.oracle.com/servers/technologies/opensparc-t2-page.html>, 2008.

- [20] NVIDIA Corporation, “Nvdla open source hardware,” <https://github.com/nvdla/hw>, 2017.