# HLS4PC: A Parametrizable Framework For Accelerating Point-Based 3D Point Cloud Models on FPGA

Amur Saqib Pal<sup>1\*</sup>, Muhammad Mohsin Ghaffar<sup>2\*(✉)</sup>, Faisal Shafait<sup>1</sup>, Christian Weis<sup>2</sup>, and Norbert Wehn<sup>2</sup>

<sup>1</sup> National University of Sciences and Technology, 44000 Islamabad, Pakistan

{apal.bee19seecs,faisal.shafait}@seecs.edu.pk

<sup>2</sup> Microelectronic Systems Design Research Group, RPTU Kaiserslautern-Landau, 67663 Kaiserslautern, Germany

{mohsin.ghaffar, christian.weis, norbert.wehn}@rptu.de

**Abstract.** Point-based 3D point cloud models employ computation and memory intensive mapping functions alongside Neural Network (NN) layers for classification/segmentation, and are executed on server-grade Graphics Processing Units (GPUs). The sparse, and unstructured nature of 3D point cloud data leads to high memory and computational demand, hindering real-time performance in safety-critical applications due to GPU under-utilization. To address this challenge, we present HLS4PC, a parameterizable High Level Synthesis (HLS) framework for Field-Programmable Gate Array (FPGA) acceleration. Our approach leverages FPGA parallelization and algorithmic optimizations to enable efficient fixed-point implementations of both mapping and NN functions. We explore several hardware-aware compression techniques on a state-of-the-art PointMLP-Elite model, including replacing Farthest Point Sampling (FPS) with Uniform Random Sampling (URS), parameter quantization, layer fusion, and input-points pruning, yielding PointMLP-Lite, a  $4\times$  less complex variant with only  $\sim 2\%$  accuracy drop on ModelNet40. Secondly, we demonstrate that the FPGA acceleration of the PointMLP-Lite results in  $3.56\times$  higher throughput than previous works. Furthermore, our implementation achieves  $2.3\times$  and  $22\times$  higher throughput compared to the GPU and Central Processing Unit (CPU) implementations, respectively. The code of the HLS4PC framework will be available at: <https://github.com/dll-ncai/HLS4PC>.

**Keywords:** FPGA · Dataflow Architecture · Point Cloud Acceleration

## 1 Introduction

In recent years, 3D point cloud data from Light Detection and Ranging (LiDAR) or RGB-D sensors is increasingly used in applications such as autonomous

---

\* These authors contributed equally to this work

The research reported in this work is partially supported by the Carl Zeiss Stiftung, Germany, under the Sustainable Embedded AI project (P2021-02-009).

driving, robotics, drones, 3D reconstruction, Virtual Reality (VR)/Augmented Reality (AR) head-sets and even the iPhone 16 Pro. Processing 3D point clouds is challenging due to their sparsity, with unevenly distributed data points in 3D space. Since classification and segmentation are vital for safety-critical and real-time applications, these models must meet strict throughput demands. For instance, the throughput requirement for an end-to-end level-5 autonomous driving solution is estimated to be at 2,000 TOPS [7].

In the literature, researchers have proposed projection-based, volumetric-based, mesh-based, and point-based methods for classification and segmentation of 3D point cloud data [11]. The point-based approaches [10,6,8] dominate due to the ability to operate directly on raw 3D data, achieving up to 5% higher accuracy and lower complexity [5]. These models combine Deep Neural Network (DNN) layers with mapping functions like Farthest Point Sampling (FPS) and K-Nearest Neighbor (KNN) to extract features from unordered, sparse 3D data. While Graphics Processing Units (GPUs) excel at dense matrix operations, they struggle with irregular mapping functions due to data sparsity [10], leading to resource under-utilization. A limited number of prior studies have explored the use of Application-Specific Accelerators [5] to enhance the throughput of 3D point cloud models. Although, these accelerators can deliver high throughput, they inherently lack flexibility, making it challenging to deploy evolving and mixed-precision models.

In contrast, Field-Programmable Gate Array (FPGA) allow precision to be configured at compile-time, support mixed-precision acceleration without hardware redesign. Additionally, new layers or functions can be added by updating hardware libraries or reconfiguring logic blocks. These advantages make FPGAs ideal for 3D point cloud processing, where models evolve rapidly. While various FPGA-based DNN frameworks exist [2,13], they cannot accelerate 3D point cloud models due to their lack of support for point cloud mapping functions. To bridge this gap, we propose a parameterizable mixed-precision dataflow-based streaming framework for acceleration of 3D point cloud models on FPGA presented as HLS4PC. We perform an in-depth investigation of the effects of compression techniques such as input point pruning, quantization, and layer fusion combined with hardware-aware mapping functions on model accuracy, utilizing the ModelNet40 and ScanObjectNN as benchmarks. Based on these explorations, we introduce PointMLP-Lite, a  $4\times$  smaller version of PointMLP-Elite, with only a  $\sim 2\%$  accuracy drop. We deploy PointMLP-Lite on a ZC706 development board, achieving  $3.56\times$  higher throughput than prior work, and outperforming GPU and Central Processing Unit (CPU) in terms of throughput by  $2.3\times$  and  $22\times$  respectively.

## 2 HLS4PC Workflow

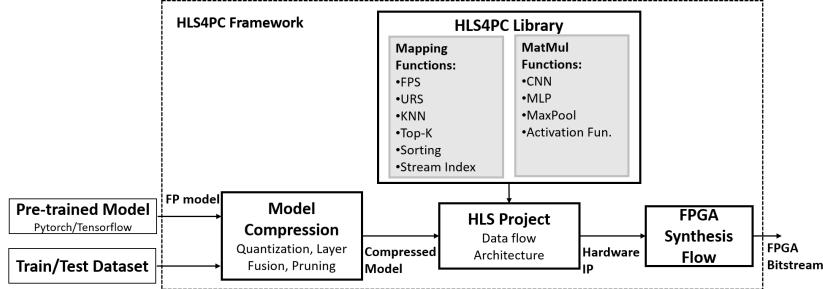

In this section, we introduce HLS4PC, a framework designed to accelerate 3D point cloud models on FPGAs. HLS4PC leverages High Level Synthesis (HLS) to translate a high-level classification/segmentation 3D point cloud model into

**Fig. 1.** The HLS4PC framework workflow.

a hardware implementation. This approach allows for the rapid prototyping and deployment of customized hardware accelerators tailored to the specific requirements (precision, parallelism, and throughput). This framework consists of a fixed-point parameterizable HLS4PC library, which can be used to deploy 3D point cloud mapping (such as FPS, Uniform Random Sampling (URS), sorting and KNN) and MatMul (Convolutional Neural Network (CNN), Multi-Layer Perceptron (MLP), and max-pooling) functions, as illustrated in Fig. 1. All these functions and layers are implemented using a streaming-based dataflow architecture approach. The HLS4PC framework accepts a pre-trained Floating-Point (FP) model along with the dataset as input. It employs quantization-aware training to compress the model, uses the HLS4PC library to generate an HLS template, synthesizes the design, and ultimately produces an FPGA bitstream for deployment.

## 2.1 Mapping Functions

Point-based methods [6,9,16] commonly use FPS to select Regions of Interest (ROI) for local feature extraction, but its sequential nature and frequent distance updates make it compute and memory intensive. Previous works [17,4] have explored URS for the accuracy/resolution trade-off and data augmentation. Unlike FPS, URS selects points randomly, making it hardware-friendly. Rather than using URS solely for augmentation, we replace FPS with URS in the model architecture itself. Although URS introduces stochasticity that hinders convergence, we mitigate this by increasing the batch size (up to 256) and training duration (up to 1,000 epochs), enabling the model to learn stable, geometry-invariant features. For hardware implementation, we implement URS using a pseudo-random number generator based on Linear Feedback Shift Registers (LFSRs). We seed our training experiments, initialize the LFSRs with the same starting states, and use primitive polynomials to define their feedback mechanism.

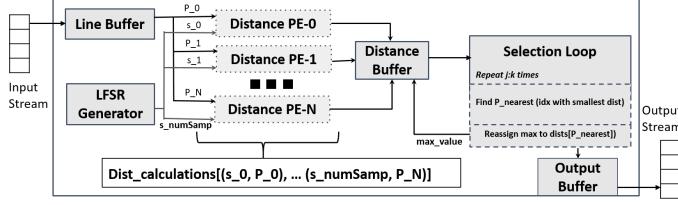

We take a multi-Processing Element (PE) approach to implementing KNN and leverage several HLS optimization techniques such as buffer partitioning, loop unrolling, and pipelining in our design. The implementation, shown in

**Fig. 2.** Architecture of the KNN algorithm

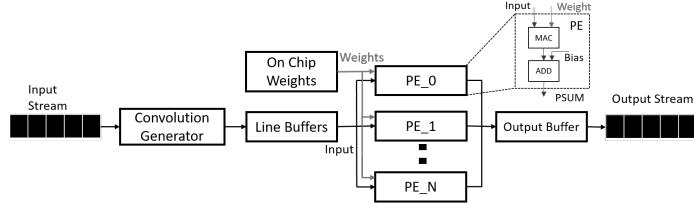

**Fig. 3.** Architecture of the convolution layer

Fig. 2, uses a set of  $X$  parallelized distance calculation units referred as *distance PE-0* to *distance PE-N*, which take *numSamp* LFSR samples ( $s\_0$  to  $s\_numSamp$ ) and  $N$  points/features ( $P\_0$  to  $P\_N$ ) as input. For every sample, the distance from each point in the input is calculated and stored in a *distance buffer*. A selection sort-style module then finds KNN of each sample. The index of the point with the smallest distance to the sample is identified, and the distance value of that neighboring point is reassigned the maximum numeric limit of its fixed-point representation. This process is repeated  $k$  times for *numSamp* samples (the total number of samples), where  $k$  is the number of neighbors required for each sample. These neighbor sets collectively represent the isolated local region which is used for feature extraction further in the network. In our implementation, we use  $k = 16$ ,  $X=4$ ,  $numSamp \in \{256, 128, 64, 32\}$  for 4 stages of the PointMLP-Lite topology.

## 2.2 MatMul Functions

CNN and MLP layers are implemented using a streaming dataflow architecture, where each layer is a distinct hardware module with configurable parallelism, as shown in Fig. 3. The number of PEs, labeled  $PE_0$  to  $PE_N$ , controls the degree of parallel Multiply-Accumulate (MAC) operations per layer. These compile-time parameters enable customization based on resource availability and throughput requirement. Since the most complex layer dictates overall throughput, higher resources (parallel PEs) are allocated to boost performance. Before convolution, input is reorganized into kernel-size segments. Each PE fetches weights/biases from on-chip memory and computes outputs using fixed-point arithmetic. The max-pooling layers and ReLU activations are optimized with Single Instruction

Multiple Data (SIMD) parallelism. For each input convolution feature map ( $C_{\text{in}}$ ),  $N_{\text{SIMD}}$  channels are processed per clock cycle using a dedicated activation unit that clamps negative values to zero. Each SIMD lane concurrently processes one activation element from the segment and new input values are streamed in via the line-buffers. The folding factor for the  $i^{\text{th}}$  ReLU layer is computed as  $F^{(i)} = C_{\text{in}}^{(i)} / N_{\text{SIMD}}^{(i)}$ . The batch-norm layer is merged with the preceding convolution layer. This approach reduces the utilization of Block Random Access Memory (BRAM) by eliminating the need to store layer parameters separately in on-chip memory. In addition, it minimizes the hardware resources required for the synthesis of the layer. This fusion is performed after the quantization-aware training, and the fused network parameters are exported for deployment on FPGA.

### 3 Evaluation Setup

We selected two widely-used 3D object classification benchmarks, ModelNet40 [15] and ScanObjectNN [12] for evaluation. For hardware deployment, we use PointMLP-Elite [6], a state-of-the-art model that achieves an overall classification accuracy of 93.6% on the ModelNet40 dataset. PointMLP-Elite captures local geometric structures in point cloud data using a local grouper module, and applies a learnable affine transformation to normalize them to a stable representation before local and global feature extraction. Topologically, the model is structured into four distinct stages of varying depths with 24 1D-convolution layers, a classifier head, and a geometric normalization module with two geometric parameters,  $\alpha$  and  $\beta$ . The value of these parameters are determined during training alongside weights and activations, requiring extra resources for storage and computation.

The PointMLP-Lite model experiments were carried out using Python version 3.10.14, PyTorch version 2.4.0, and CUDA version 12.4 on an NVIDIA GeForce RTX 3090 GPU. For quantization-aware training, Brevitas framework 0.7.0 was used. We use *stochastic gradient descent* optimizer with *momentum* = 0.8 and *weightDecay* = 0.0002, and *CosineAnnealingLR* scheduler with initial and minimum *learning rate* values of 0.1 and 0.005 respectively. We train our models for 1,000 epochs with a batch size of 256. Vivado HLS 2018.3 was used for synthesis and FPGA deployment pipeline. The complete system was implemented using Vivado Block Design, targeting the Xilinx Zynq 7000 SoC ZC706 board. For FPGA power measurement, a socket power meter Voltacraft VC-870 was used.

### 4 Evaluation Results

Table 1 summarizes the impact of various compression strategies on Overall Accuracy (OA) and Mean Accuracy (mA) for the ModelNet40 and ScanObjectNN datasets. The OA metric shows the average accuracy across all test instances, while mA presents the mean accuracy across all shape classes. Starting from the

**Table 1.** PointMLP-Elite accuracy results on ModelNet40 & ScanObjectNN.

| Model              | Num of Input Points | Geometric Sampling Param. $\alpha$ & $\beta$ | FPS | BN Layer Fusion | ModelNet40 |       | ScanObjectNN |       |

|--------------------|---------------------|----------------------------------------------|-----|-----------------|------------|-------|--------------|-------|

|                    |                     |                                              |     |                 | Algo.      | OA(%) | mA(%)        | OA(%) |

| PointMLP-Elite [6] | 1024                | ✓                                            | ✓   | ✗               | 93.60      | 90.90 | 83.50        | 81.10 |

| $M-1$              | 1024                | ✗                                            | URS | ✓               | 92.30      | 89.80 | 80.88        | 78.73 |

| $M-2$              | 512                 | ✗                                            | URS | ✓               | 91.69      | 88.96 | 80.22        | 77.94 |

| $M-3$              | 256                 | ✗                                            | URS | ✓               | 90.56      | 87.72 | 72.31        | 68.64 |

| $M-4$              | 128                 | ✗                                            | URS | ✓               | 89.59      | 86.87 | 68.91        | 65.38 |

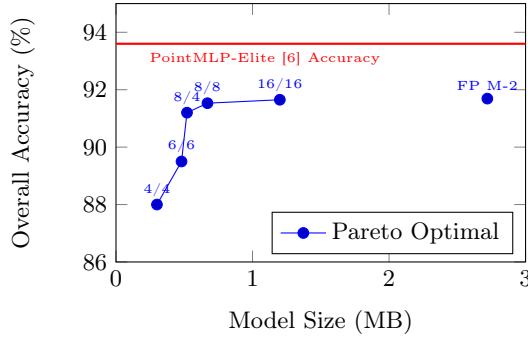

**Fig. 4.** Pareto frontier illustrating OA vs. model size trade-off on the ModelNet40.

original model with  $N_{input} = 1024$ , we experimented with reduced input sizes  $N_{input} \in [512, 256, 128]$ , pruning the  $\alpha$  and  $\beta$  parameters, replacing FPS with URS, and fusing batch-norm with convolution layers. The models are labeled  $M-1$  to  $M-4$ . Notably, model  $M-2$ , with 512 input points, shows only a  $\sim 2\%$  drop in OA on ModelNet40 and  $\sim 3\%$  on ScanObjectNN, while halving the size of intermediate features. This significantly reduces the memory footprint, making it a practical trade-off for FPGA deployment. Based on these results, we select  $M-2$  as the baseline for quantization. The Pareto-frontier chart in Fig.4 illustrates the OA vs. model size trade-off using the ModelNet40 dataset. Each data point in the figure is represented with a *weight-precision/activation-precision*. It can be seen that 8/8-bit quantized model is Pareto optimal with similar accuracy as compared to the  $M-2$  model but with 4 $\times$  less complexity. Based on these findings, we introduce a new model called PointMLP-Lite.

Table 2 shows the FPGA deployment results of the PointMLP-Lite model using the HLS4PC framework and compares them with prior FPGA-based 3D point cloud accelerators in terms of resource utilization, throughput, power consumption, and energy efficiency. Note that previous accelerators differ in architecture, target models, and model complexity. Our framework achieves significantly higher throughput (3.56 $\times$ ) and energy efficiency (57.4 $\times$ ). These gains result from hardware-aware optimizations of the PointMLP-Lite model, and careful algorithm-hardware co-design while considering the compute and memory constraints of FPGAs. In contrast, prior works focused on deploying models directly with minimal optimizations (e.g. FP32 implementation of [3]). Furthermore, the

**Table 2.** Comparison with previous 3D point cloud FPGA architectures.

|                                   | SOCC 2022<br>[14]           | ISCAS 2020<br>[1]             | CSSP 2023<br>[3]             | ASICON 2019<br>[18]        | HLS4PC<br>(This Work)       |

|-----------------------------------|-----------------------------|-------------------------------|------------------------------|----------------------------|-----------------------------|

| <b>Benchmarks</b>                 | ShapeNet/<br>NYU Depth      | –                             | ModelNet40/<br>ShapeNet2Core | –                          | ModelNet40/<br>ScanObjectNN |

| <b>Topology</b>                   | SSCN                        | PointNet                      | DGCNN                        | O-PointNet                 | PointMLP-Lite               |

| <b>Conv layers</b>                | –                           | 6                             | 4 EdgeConv                   | 7                          | 24                          |

| <b>MLP layers</b>                 | –                           | 6                             | 3                            | 1                          | 3                           |

| <b>Platform</b>                   | ZCU102                      | ZCU104                        | Ultrascale V9UP              | ZC706                      | ZC706                       |

| <b>Architecture type</b>          | Compute Array<br>(PE) Array | Process Element<br>(PE) Array | Systolic Array               | Parallel<br>Computing Unit | Streaming-based<br>Dataflow |

| <b>Precision</b>                  | Int8                        | Int8/Int16                    | FP32                         | fp16                       | fp8                         |

| <b>FF</b>                         | 12.1K (2.22%)               | 36K (8%)/60K (13%)            | 44.48%                       | –                          | 34k (8%)                    |

| <b>LUT</b>                        | 17.6K (6.43%)               | 19K (8%)/30K (13%)            | 78.92%                       | –                          | 92k (42%)                   |

| <b>DSP</b>                        | 256 (10.16%)                | 1K (60%)/1K (60%)             | 27.42%                       | –                          | 0 (0%)                      |

| <b>BRAM</b>                       | 365 (40.08%)                | 114 (37%)/123 (39%)           | 39.2%                        | –                          | 401 (73%)                   |

| <b>URAM</b>                       | 0                           | 48 (50%)/96 (100%)            | 0                            | 0                          | 0                           |

| <b>Frequency [MHz]</b>            | <b>270</b>                  | 100                           | 130                          | 100                        | 100                         |

| <b>Power Consumption [W]</b>      | 3.45                        | –                             | 17                           | <b>2.14</b>                | 2.2                         |

| <b>Throughput [GOPS]</b>          | 17.73                       | 182.1/130                     | –                            | 1.208                      | <b>648</b>                  |

| <b>Energy Efficiency [GOPS/W]</b> | 5.13                        | –                             | –                            | 0.56                       | <b>294.5</b>                |

reconfigurable layer-level parallelism of our library results in increased throughput and enables energy-efficient deployment even if it may affect accuracy to some extent.

Table 3 presents a comparison of throughput of CPU, FPGA, and GPU of our PointMLP-Lite model against GPU implementation of the baseline PointMLP-Elite Model. Our proposed architecture achieves  $5.6 \times$  higher throughput as compared to the baseline GPU implementation.

**Table 3.** Comparison of the FPGA architecture with baseline, CPU and GPU

| Model                         | Platform       | Frequency(GHz) | Throughput(SPS) |

|-------------------------------|----------------|----------------|-----------------|

| PointMLP-Elite (Baseline) [6] | Tesla V-100    | 1.2            | 176             |

| PointMLP-Elite                | RTX 3060 Ti    | 2.1            | 187             |

| PointMLP-Lite (This Work)     | RTX 3060 Ti    | 2.1            | 421             |

| PointMLP-Lite (This Work)     | Intel i5-13400 | 4.6            | 45              |

| PointMLP-Lite (This Work)     | Xilinx ZC706   | 0.1            | <b>990</b>      |

## 5 Conclusion

In this paper, we present HLS4PC, a parameterizable FPGA-based framework for accelerating point-based 3D point cloud models. We also propose a compressed PointMLP-Lite model, which uses 8-bit precision for both weights/activations

and 512 input 3D points. The model integrates batch-norm into convolution layers, replaces FPS with URS, and prunes geometric normalization parameters. PointMLP-Lite reduces complexity by  $4\times$  compared to the baseline PointMLP-Elite, while achieving a  $3.56\times$  higher throughput when deployed on an FPGA compared to prior works. As future work, we plan to explore Hilbert Curve-based sampling to reduce accuracy loss from URS.

## References

1. Bai, Lin, et al.: PointNet on FPGA for Real-Time LiDAR Point Cloud Processing. In: IEEE ISCAS (2020)

2. Fahim, Farah, et al.: hls4ml: An Open-Source Codesign Workflow to Empower Scientific Low-Power Machine Learning Devices. arXiv preprint arXiv:2103.05579 (2021)

3. Jamali Golzar, Saleh, et al.: DGCNN on FPGA: Acceleration of the Point Cloud Classifier Using FPGAs. Circuits, Systems, and Signal Processing (2023)

4. Li, Yangyan, et al.: PointCNN: Convolution On X-Transformed Points. Advances in Neural Information Processing Systems (2018)

5. Lin, Yujun, et al.: PointAcc: Efficient Point Cloud Accelerator. In: IEEE/ACM MICRO-54 (2021)

6. Ma, Xu, et al.: Rethinking network design and local geometry in point cloud: A simple residual MLP framework. arXiv preprint arXiv:2202.07123 (2022)

7. NVIDIA: NVIDIA Unveils DRIVE Thor (2022), <https://nvidianews.nvidia.com/news/nvidia-unveils-drive-thor-centralized-car-computer-unifying-cluster-infotainment-automated-driving-and-parking-in-a-single-cost-saving-system>, accessed: 2025-03-17

8. Paul, Sneha, et al.: DualMLP: A two-stream fusion model for 3D point cloud classification. The Visual Computer (2024)

9. Qi, Charles R., et al.: PointNet++: Deep Hierarchical Feature Learning on Point Sets in a Metric Space. Advances in neural information processing systems (2017)

10. Qi, Charles R., et al.: PointNet: Deep Learning on Point Sets for 3D Classification and Segmentation. In: IEEE CVPR (2017)

11. Sarker, Sushmita, et al.: A comprehensive overview of deep learning techniques for 3D point cloud classification and semantic segmentation. Machine Vision and Applications (2024)

12. Uy, Mikaela Angelina, et al.: Revisiting Point Cloud Classification: A New Benchmark Dataset and Classification Model on Real-World Data. In: IEEE/CVF ICCV (2019)

13. Venieris, Stylianos, et al.: fpgaConvNet: A Framework for Mapping Convolutional Neural Networks on FPGAs. In: IEEE FCCM (2016)

14. Wang, Zilun, et al.: An Efficient FPGA Accelerator for Point Cloud. In: IEEE SOCC (2022)

15. Wu, Zhirong, et al.: 3D ShapeNets: A Deep Representation for Volumetric Shapes. In: IEEE CVPR (2015)

16. Yan, Xu, et al.: PointASNL: Robust Point Clouds Processing using Nonlocal Neural Networks with Adaptive Sampling. In: IEEE / CVF CVPR (2020)

17. Zhang, Min, et al.: PointHop: An Explainable Machine Learning Method for Point Cloud Classification. IEEE Transactions on Multimedia (2020)

18. Zheng, Xitao, et al.: An FPGA based Parallel Implementation for Point Cloud Neural Network. In: IEEE ASICON (2019)