# Pinball: A Cryogenic Predecoder for Quantum Error Correction Decoding Under Circuit-Level Noise

Alexander Knapen<sup>†\*</sup>, Guanchen Tao<sup>†\*</sup>, Jacob Mack<sup>†</sup>, Tomas Bruno<sup>†</sup>, Mehdi Saligane<sup>‡</sup>, Dennis Sylvester<sup>†</sup>,

Qirui Zhang<sup>†</sup>, and Gokul Subramanian Ravi<sup>†</sup>

<sup>†</sup>University of Michigan, Ann Arbor; <sup>‡</sup>Brown University

Email(s): {aknapen, guanchen, jmackmi, tbruno}@umich.edu, mehdi\_saligane@brown.edu,

{dmcs, qiruizh, gsravi}@umich.edu

Abstract—Scaling fault tolerant quantum computers, especially cryogenic systems, to millions of qubits is very challenging due to poorly-scaling data processing and power consumption overheads. One key challenge is the design of decoders for real-time quantum error correction (QEC), which demands high data rates for error processing; this is particularly apparent in systems with cryogenic qubits and room temperature (RT) decoders. In response, cryogenic predecoding using lightweight logic has been proposed to handle common, sparse errors within the cryogenic domain. However, prior work only accounts for a subset of the error sources present in real-world quantum systems with limited accuracy, often degrading performance below a useful level in practical scenarios. Furthermore, prior reliance on SFQ logic precludes detailed architecture-technology co-optimization.

To address these shortcomings, this paper introduces Pinball 1, a comprehensive design in cryogenic CMOS of a QEC predecoder tailored to realistic, circuit-level noise. By accounting for error generation and propagation through QEC circuits, our design achieves higher predecoding accuracy, outperforming logical error rates of the current state-of-the-art cryogenic predecoder by nearly six orders of magnitude. Remarkably, despite operating under much stricter power and area constraints, Pinball also reduces logical error rates by  $32.58\times$  and  $5\times$ , respectively, compared to the state-of-the-art RT predecoder and an RT ensemble configuration. By increasing cryogenic coverage, we also reduce syndrome bandwidth up to 3780.72×. Through co-design with 4K-characterized 22 nm FDSOI technology, we achieve a peak power consumption under 0.56 mW. Voltage/frequency scaling and body biasing enable 22.2× lower typical power consumption, yielding up to 67.4× total energy savings. Assuming a 4K power budget of 1.5 W, our predecoder can support up to **2,668** logical qubits at d=21.

## I. INTRODUCTION

While quantum computing offers significant advantages for problems in domains like chemistry and optimization, solving practical instances will require  $10^5-10^6$  qubits with error rates near  $10^{-15}$  [6]. Due to environmental noise, however, current systems are limited to just  $10^2-10^3$  qubits with errors rates of  $10^{-2}-10^{-3}$ . To bridge this gap between present-day devices and future application requirements, quantum error correction (QEC) uses redundancy to encode low-error *logical* qubits from many error-prone *physical* qubits. Errors are detected through repeated measurements, producing a binary *error syndrome* used by a classical decoder to determine corrections. If physical error rates stay below a threshold, logical error rates

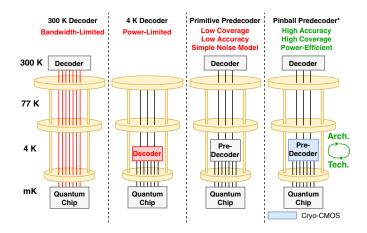

Fig. 1. The classical hardware landscape for QEC decoding. Relative to prior work, our design (rightmost) (1) improves predecoding performance in realistic settings by analyzing error sources and propagation at the circuit-level, and (2) co-optimizes architecture with technology to achieve this higher performance at lower overheads.

can drop exponentially. The surface code [23] is a leading QEC code candidate, especially in the intermediate-term, due to its planar layout, local connectivity, and high error threshold.

Despite its advantages, the surface code is challenging to implement practically. For instance, the volume of syndrome data scales cubically with the code's distance, *d*, and some gates in quantum circuits are conditioned on the results of decoding, introducing strict real-time latency requirements. Furthermore, many prominent qubit modalities are stored cryogenically inside dilution refrigerators [38], [66], creating significant spatial separation with the decoder at room-temperature (RT). This requires high-bandwidth, cross-temperature interconnects via long, lossy coaxial cables, which is unsustainable due to: (1) limited microwave I/O, (2) heat flux from RT connections that degrades coherence, and (3) long, variable feedback delays that hinder synchronization.

To address control and readout bandwidth, academia and industry have explored co-locating electronics alongside qubits in the cryogenic domain, typically at 4 K [3], [4], [8], [18], [24], [53], [65], [71]. However, the 4 K cooling capacity is very low (~1.5 W [45]), and if cryogenic hardware exceeds this budget, the added thermal noise harms qubit fidelity. While optimization is still needed to reduce control and readout power, substantial advances have been made in recent years to

<sup>\*</sup>These authors contributed equally to this work.

<sup>&</sup>lt;sup>1</sup>Source code available at: https://github.com/aknapen/Pinball

lower overheads (e.g., 23 mW/qubit control power [25] down to <4 mW/qubit [71]).

Nonetheless, even with additional reductions, QEC syndrome transmission power will remain a prominent concern if left unaddressed. Similar to control and readout, cryogenic decoding has been explored to reduce bandwidth requirements. However, due to 4 K power constraints, fully cryogenic decoders [33], [63], [64] suffer from insufficient accuracy and are unable to support many high-distance logical qubits. Thus, significant architecture and technology innovations (Fig. 1) are needed to realize cryo-compatible decoding strategies.

At the architecture level, **cryogenic predecoding** [54] has been proposed to apply local decoding heuristics instead of complex, global algorithms. Predecoding can maintain high accuracy because, even at current error rates, long error chains are rare, and most syndromes are sparse and local. Cryogenic predecoders use low-power logic to decode simple syndromes and flag rare, complex ones for further processing. If cryogenic predecoders work well, only complex syndromes are sent to a more power-intensive RT decoder, keeping interconnect bandwidth between 4 K and RT low without sacrificing accuracy.

While cryogenic predecoding holds great promise, prior work [54] has tailored to simplistic noise models that fail to account for many sources of errors and how they propagate in real QEC implementations. When evaluated under more realistic noise, we find that prior work's utility is significantly dampened in terms of coverage and predecoding accuracy, limiting the predecoder's ability to reduce syndrome bandwidth and achieve sufficiently low logical error rates (see Sec. II-E).

At the technology level, **cryogenic CMOS** (**cryo-CMOS**) and single-flux quantum (SFQ) logic have emerged as leading candidates for low-power, cryogenic electronics. However, today's SFQ has many scaling disadvantages such as significant area consumption [33], complex pulse-based physical design [10], less mature EDA toolchains, and challenging integration with ubiquitous CMOS technologies. By contrast, cryo-CMOS logic benefits from extremely high area density, decades of research in design optimization techniques, and a mature EDA toolchain. These advantages have spurred significant academic [18], [40], [56] and industrial [3], [4], [8], [24], [65], [71] investment in cryo-CMOS qubit interfacing systems.

Despite cryo-CMOS's advantages, prior cryogenic decoding works [33], [54], [63], [64] have almost exclusively used SFQ, limiting design characterization and precluding the essential architecture-technology co-design needed for practical solutions. On the one hand, hardware characterization enables the detailed analyses required to accurately assess design scalability, and on the other, cross-layer optimizations can yield scalability surpassing that achievable by optimizations made in a single layer. These implications are critical in the context of cryogenic predecoding, where designs cannot be evaluated based only on raw performance metrics (e.g., bandwidth reduction), but by how much performance they can achieve while still operating within the power and area constraints of the dilution refrigerator.

For these reasons, this paper presents a cross-layer design,

from algorithm to cryo-CMOS implementation in 22 nm Fully Depleted Silicon on Insulator (FDSOI), of **Pinball**, a cryogenic predecoder for surface code QEC capable of handling realistic, circuit-level noise. By analyzing both how errors occur on and propagate across qubits in syndrome measurement circuits, as well as how errors correlate syndromes together, we derive a small set of simple algorithmic predecoding primitives capable of correcting them. Further, we identify race conditions between conflicting primitives that motivate the algorithm's translation into a pipelined architecture, using error frequency analysis to determine a good ordering of pipeline stages. Finally, by co-designing with cryo-CMOS FDSOI technology, we exploit latency requirement imbalances in predecoding to markedly reduce power and energy consumption through voltage/frequency scaling and forward body biasing.

To summarize, the contributions of this paper are:

- Circuit-Level Noise Analysis: Detailed analysis of error propagation within QEC circuits, categorizing them based on how they correlate syndromes across space and time. In conjunction with error frequency distribution analysis, these enable predecoding improvements over prior work.

- 2) Pinball Predecoding Algorithm and Architecture: Development of a novel predecoding algorithm, Pinball, and its pipelined architecture, capable of predecoding under realistic, circuit-level noise. At near-term (long-term) error rates, Pinball reduces syndrome transmission by up to 5.65× (34.72×) and increases predecoding accuracy by up to 4.23× (1.46×) relative to the state-of-the art cryogenic predecoder, achieving total syndrome bandwidth reduction up to 3780.72× and reducing logical error rate (LER) up to nearly six orders of magnitude. Remarkably, Pinball even reduces LER by 32.58× and 5× relative to the state-of-the-art RT predecoder and ensemble configurations, respectively.

- 3) Architecture-Technology Co-Optimization: By identifying significant latency requirement imbalances in the per-round predecoding process, we co-design with cryo-CMOS capabilities, leveraging voltage/frequency scaling and forward body biasing for lower supply voltage and reducing power by up to 22.2×. Factoring in cryo-to-RT transmission, we can achieve total energy savings up to 37.05×. Considering additional overheads from a real-world QEC interface [36], this number rises to 67.4×.

- 4) **Cryo-CMOS Implementation and Evaluation**: Using a 22 nm FDSOI technology designed for 4 K, we perform synthesis, placement, and routing of Pinball with power, performance, and area evaluation. Under a 1.5 W budget for cryogenic predecoding, our design supports 37,313 and 2,668 logical qubits at code distances of 3 and 21 respectively, at a physical error rate of  $10^{-3}$ .

#### II. BACKGROUND AND MOTIVATION

#### A. Quantum Error Correction

Similar to classical error correction, quantum error correction (QEC) uses redundancy to encode a logical qubit

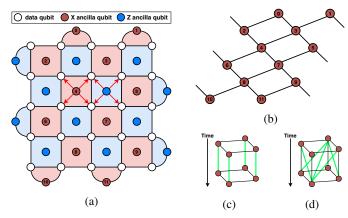

Fig. 2. (a) d=5 rotated surface code lattice. (b) Corresponding decoding graph for Z errors in one QEC round. (c, d) Unit cells for the Z-error decoding graph under (c) phenomenological noise and (d) circuit-level noise.

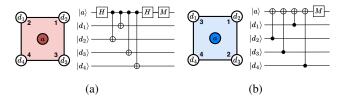

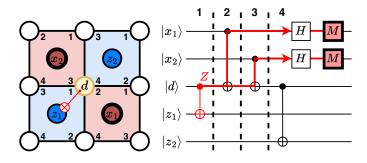

Fig. 3. Syndrome measurement circuits for detecting (a) Z errors and (b) X errors. X/Z ancilla patches are annotated with numbers specifying the order of CNOTs in their circuits.

using many physical qubits with high *physical error rate*, p. However, QEC faces two unique challenges: measuring a qubit collapses its state, and qubits suffer both bit flip (X) and phase flip (Z) errors, unlike classical bits.

To address these, various QEC codes have been developed, with the surface code being a leading candidate due to its planar layout and local connectivity. Implemented on a 2D lattice (Fig. 2a), the rotated surface code uses  $2d^2 - 1$  physical qubits (data qubits and X/Z ancilla qubits) where d is the code distance, or the minimum length of a logical error.

Ancilla qubits are entangled with neighboring data qubits (red arrows) and measured to detect Z and X errors. The circuits implementing these interactions are shown in Fig. 3. They exploit the propagation of Pauli terms through CNOTs, namely that Pauli-Z terms propagate through a CNOT from the target qubit to the control qubit while Pauli-X terms propagate from the control qubit to the target qubit, in order to transmit error information from data qubits to ancilla qubits.

At the end of each circuit, the ancilla qubits are measured, and the parity between consecutive measurement outcomes forms a binary syndrome which a decoder uses to infer corrections. Each ancilla reports only error parity (0 for even, 1 for odd) so different error patterns can yield identical syndromes, complicating decoding. In CSS codes, X and Z syndromes can be decoded separately.

## B. Noise Models & the Decoding Graph

QEC decoding complexity and accuracy greatly depend on the degree to which physical qubit noise and its corresponding error sources are accounted for. This complexity is often reflected in the noise model used to analyze and design the classical decoder. For example, the simplest, lowest-accuracy decoders assume errors are stochastically injected onto each data qubit with a probability, p; this process is captured by the code capacity noise model. In reality, ancilla measurement itself is error-prone, requiring decoders to process multiple (typically d) syndrome measurement rounds under the more accurate phenomenological noise model. This description is still lacking, since single-qubit, two-qubit, and reset operations in QEC circuits also introduce errors; these are incorporated into the circuit-level noise model used by the highest-accuracy decoders. While error interactions become increasingly complex to decode with each model, accounting for all of them is critical to enable the high-accuracy QEC decoding required for practically useful, fault-tolerant execution.

The decoding problem can be represented by a weighted graph with three dimensions: two spatial (the surface code lattice) and one temporal (multiple measurement rounds). Fig. 2b shows the Z-error decoding graph for one measurement round, corresponding to the code capacity noise model. Vertices represent syndromes, and edges represent error sources that flip the syndrome values at their endpoints. Optionally, edge weights can be used to reflect error probabilities. Syndromes with an odd number of adjacent errors are termed active and are paired by the decoder to infer corrections on data qubits.

Fig. 2c shows a single unit cell of the Z-error decoding graph for the phenomenological noise model. In addition to the horizontal edges within a round (space-like errors), vertical edges (green) correspond to measurement errors (time-like errors). In the unit cell for the circuit-level noise model (Fig. 2d), additional diagonal edges (green) with both space and time components (spacetime-like errors) account for errors propagating through CNOT gates in the syndrome measurement circuits. Critically, the decoding algorithm requires a mapping from each error edge to the correspondingly affected data qubit(s), necessitating an analysis of how errors emerge and propagate throughout the syndrome measurement circuit.

#### C. Decoding Algorithms

To address the complexity of surface code decoding, several algorithms have been developed to accurately identify and correct errors. Critically, these algorithms must operate within strict real-time constraints. One reason is that non-Clifford gates (e.g., T gates) can fail injection, and if so, require corrective S gates dependent on the decoding history [23]. Moreover, decoding must be completed at least as quickly as the rate of qubit measurement to avoid an exponentially growing backlog of error data [62]. For superconducting qubits, this latency can be as low as  $1 \mu s$  [57].

The Blossom algorithm [19] based minimum-weight perfect matching (MWPM) decoder offers high accuracy, but with  $O(d^5)$  time complexity. The Union-Find decoder [16] trades off accuracy for improved latency  $(O(d^3)$  complexity). While effective, these and related algorithms [31], [70] impose high resource and latency costs. At RT, these costs are tolerable,

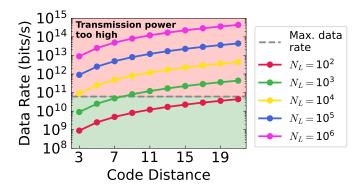

Fig. 4. Data rates needed to support  $N_L$  logical qubits at various code distances. Horizontal line: the data rate at which transmission power exceeds the  $4\,\mathrm{K}$  power budget.

but cryogenic constraints, especially the low power budgets (~1.5 W at 4 K [45]), make such decoders impractical to colocate with cryogenic quantum hardware.

#### D. 4 K-to-RT Bandwidth Constraints

In addition to power and latency constraints, an important design constraint is the volume of data entering and exiting the dilution refrigerator between the 4 K and RT stages. This volume includes qubit control instructions as well as syndrome and correction data. While the repetitive structure of logical operations [60] will likely allow minimizing instruction bandwidth using a cryogenic quantum control processor [61], streaming surface code syndrome data to RT will continue to dominate, especially since (1) its volume scales as  $O(d^2)$  per round per logical qubit (see Fig. 4) and (2) d QEC rounds are required per logical operation [47].

Using a state-of-the-art wireline transmitter dissipating 0.92 pJ/b [11], we estimate the interconnect power as a function of the required syndrome bandwidth. We find that, given 1.5 W of cooling power at 4 K [45], the transmission power exceeds the entire budget at 60.98 Gb/s, only enabling support of 1000 logical qubits for code distances up to 7. Moreover, since every cable entering the 4 K stage from RT introduces additional passive heat load [45], [69], the number of links must be minimized. Clearly, scaling to the large code distances required for fault-tolerant quantum computing requires innovative strategies to mitigate this bandwidth bottleneck.

#### E. Predecoding Algorithms

Fortunately, most decoding scenarios involve sparse active syndromes [14], [54], as long error chains are exponentially unlikely. This has motivated the development of QEC predecoding [1], [54], [58] which uses much simpler logic than full-fledged decoders to pre-process these sparse syndromes. We discuss two types of previously studied predecoding: RT predecoding and cryogenic predecoding.

RT predecoding [1], [58] typically seeks to minimize decoding latency by sparsifying syndromes before they are sent to the full-fledged RT decoder. Specifically, RT predecoders identify short correction chains to match local pairs of syndrome bits, remove them, and pass the reduced syndrome on to the

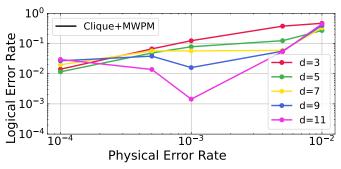

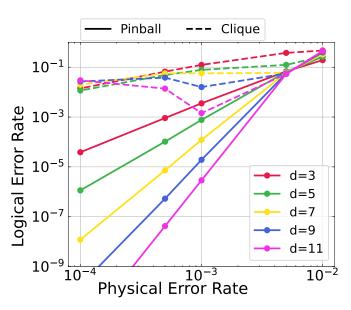

Fig. 5. LER achieved under circuit-level noise by Clique [54].

decoder. By giving the decoder a sparser, simpler decoding graph, its latency remains below the  $1\,\mu s$  budget for higher code distances than would be possible without predecoding. A state-of-the-art RT predecoder is Promatch [1].

On the other hand, cryogenic predecoding [54] seeks to minimize 4 K-to-RT syndrome bandwidth by decoding a large fraction of syndromes within the 4 K temperature stage. Cryogenic predecoders use lightweight decoding heuristics to handle common, short (typically length-1) error chains within the 4 K power and area constraints. To maintain the extremely low logical error rates (10<sup>-15</sup>) required for applications, cryogenic predecoders must also detect longer error chains, offloading their complex syndromes to RT for full-fledged decoding. Since complex scenarios are very rare, 4 K-to-RT syndrome bandwidth can be significantly lowered. The state-of-the-art cryogenic predecoder is Clique [54].

Since they solve different problems, RT and cryogenic predecoders are orthogonal. Ideally, future quantum computing systems will combine both, using the former to minimize 4 K-to-RT bandwidth and the latter to minimize decoding latency when complex syndromes are propagated to RT. While we focus on cryogenic predecoding, we include comparisons of our predecoder with both Promatch and Clique in Sec. VI.

Predecoding Under Realistic Noise: We now motivate our reasoning for targeting cryogenic predecoding by analyzing how the current state-of-the-art, Clique [54], performs under noise present in real quantum computing systems. As a simplification, Clique considers only space-like and time-like errors, ignoring syndrome pairs due to spacetime-like errors. Since its evaluation in [54] used only phenomenological noise, Clique still maintained high accuracy while achieving high bandwidth savings. To understand Clique's benefits for real-world systems, we evaluated it under realistic, circuit-level noise (described in Sec. V). Fig. 5 shows that Clique is unable to provide the exponential logical error rate suppression needed by applications (discussed further in Sections III-D and VI-A). Thus, to the best of our knowledge, there are no cryogenic predecoders which can provide both low enough syndrome bandwidth and low enough logical error rates to achieve a practical, scalable quantum computing system. Clearly, further innovations are needed in cryogenic predecoding, and this is the crux of our motivation to design Pinball.

#### F. Cryogenic Technology

To meet the stringent design constraints of cryogenic environments, both cryo-CMOS and SFQ logic have emerged as promising technologies. Recent work has explored SFQbased accelerators for domain-specific applications [33], [37], [39], [41], but SFQ design presents several challenges. First, scalability is difficult due to SFQ's inherently low area density: standard SFQ logic cells (e.g., AND, OR, XOR) are typically  $\sim 10^5 - 10^6 \times$  larger than their CMOS counterparts [33]. Second, SFQ's pulse-based logic requires each cell to be clocked separately, demanding deep pipelining and non-standard architectural techniques [10] that complicate physical design. Third, the SFQ design ecosystem suffers from a lack of mature EDA tools, limiting design productivity and optimization [34]. Finally, integrating SFQ circuits with conventional CMOS technologies, whether at cryogenic temperatures or RT, introduces considerable system-level complexity.

In contrast, cryo-CMOS offers several compelling advantages: it supports high integration density, benefits from decades of design optimization research, and leverages well-developed EDA tools. Moreover, major quantum computing initiatives, including those at IBM [8], [24], [65] and Google [3], [4], [71], have adopted cryo-CMOS for control hardware, reinforcing its ecosystem maturity. Thus, using cryo-CMOS for cryogenic QEC hardware simplifies system integration and aligns with current industry practices.

Therefore, we select cryo-CMOS, specifically a 22 nm FD-SOI technology re-characterized at 4 K, for Pinball. While cryo-CMOS is sometimes considered less energy-efficient than SFQ, we demonstrate that through careful architecture-technology co-design, Pinball achieves better energy consumption than SFQ designs. Note that CMOS behavior at 4 K differs significantly from RT in several key aspects:

- **Increased threshold voltage** reduces voltage scaling headroom but can be mitigated by forward body biasing [51].

- Enhanced carrier mobility improves transistor speed and performance.

- Technology-dependent current gain: [52] reports +1.5% in 40 nm, -3.8% in 14 nm FinFET, and we observe -10.5% in the 22 nm FDSOI technology used in this work.

- **Reduced subthreshold slope** lowers leakage and enables faster switching which benefits low-power operation [52].

- **Increased mismatch** [46] requires conservative design with extensive calibration to maintain reliability.

These cryogenic effects collectively influence digital logic performance. In particular, enhanced mobility and lower resistance compensate for increased threshold voltage, resulting in faster operation at 4 K [20] with lower leakage. Moreover, reduced subthreshold slope and body biasing enable reliable subthreshold operation for ultra-low-power design.

#### III. PINBALL PREDECODING ALGORITHM

We begin by describing Pinball's lightweight predecoding algorithm which is responsible for decoding a single logical qubit. As with previous cryogenic predecoding work [54], we

Fig. 6. Distribution of maximum-length error chains in the SI1000 noise model (see Sec. V).

target predecoding of error chains spanning a single edge in the decoding graph, since they constitute a significant fraction of observed errors and are relatively easy to decode and correct. In Fig. 6, we verify this claim by simulating  $10^5$  blocks of d-round syndromes across many physical error rates and code distances, recording the longest-observed error chain per block. For almost all code distances and error rates, the longest error chains have length 1 at least 20% (often much higher) of the time. Underlying the Pinball algorithm is the observation first made in [14] and also leveraged in [1], [54], [58] that, if syndromes adjacent to each other in the decoding graph are both active, then there is a high likelihood that the edge between them has been flipped by an error.

Motivated by this observation, we derive a basic predecoding primitive with the following logic: for a given pair of neighboring syndromes, (1) check if they are both active, and if so, (2) assign corrections to the data qubit(s) corresponding to the edge between them. We can then pattern this predecoding primitive over every edge in the decoding graph to assign a full set of corrections for length-1 errors. While the logic itself is very simple, achieving predecoding coverage of the entire decoding graph at once requires  $O(d^3)$  such primitives.

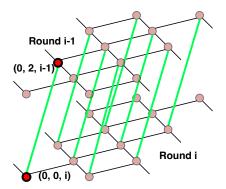

To improve cryogenic scalability, Pinball operates in a streaming fashion, predecoding only on pairs of successive syndrome rounds,  $S_{i-1}$  and  $S_i$ , two at a time, as they become available from the readout circuitry. Operating on this smaller predecoding subgraph reduces hardware overheads to  $O(d^2)$ . Notably, this simplification does not sacrifice predecoding accuracy: since ancilla qubits are reset following every round of syndrome measurement, all length-1 error chains span at most two syndrome rounds.

As introduced in Sec. II-B, the circuit-level noise model requires a predecoding subgraph composed of three types of edges: space-like, time-like, and spacetime-like. From the predecoding subgraph, we can derive which syndrome pairs must be covered by predecoding primitives to ensure full coverage. The only remaining step is to determine which qubit(s) to correct for each edge between covered syndrome pairs. To do so, in the following sections, we analyze error sources and their propagation in the syndrome measurement circuits. Although we restrict our analysis to Z errors, it

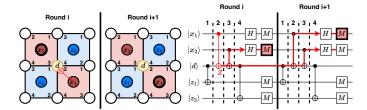

Fig. 7. Formation of a space-like error.

is applicable for any Pauli-type error, since X errors are symmetric and Y errors can be decomposed into Z and X components.

#### A. Space-like Errors

Space-like errors correlate two syndromes within the same syndrome measurement round. Fig. 7 shows one example of error generation and propagation causing such a correlation. In the first timestep, the CNOT gate between qubits d and  $z_1$  induces a Z error on qubit d. In timesteps 2 and 3, subsequent CNOT interactions with qubits  $x_1$  and  $x_2$  propagate the Z error to them, leading to error detections at the end of their circuits. From this example, it is clear that, for space-like errors, the data qubit requiring correction is the one shared between the two active syndromes in the surface code lattice. The only exceptions are at the edge of the code lattice, where errors on data qubits are detected by only a single ancilla.

For Pinball to obtain full coverage of length-1 space-like errors, we require predecoding primitives for all pairs of neighboring ancilla qubits in the lattice, as well as for each ancilla qubit at the lattice edges (Fig. 8).

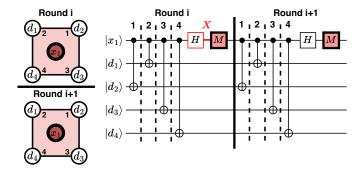

# B. Time-like Errors

Time-like errors correlate the same syndrome across different syndrome measurement rounds. In Fig. 9, we show an example of how a single X error on an X ancilla qubit due to the Hadamard gate preceding its measurement operation flips syndromes in two consecutive rounds, i and i+1. Recall that the vertices in the predecoding subgraph store the parity of measurements between rounds rather than the raw measurement values from each round. Thus, assuming an error-free round i-1, the X error in round i flips the first measurement outcome from 0 to 1 relative to the previous measurement, inducing an active syndrome in round i. Similarly, assuming an error-free round i+1, the second measurement operation flips the outcome from 1 back to 0 relative to round i, inducing a second active syndrome in round i+1.

To achieve full coverage of time-like length-1 errors, we require predecoding primitives that consider pairs of the same syndrome across consecutive rounds (Fig. 10). Unlike space-like errors, time-like errors do not require correction assignment since the errors are associated with ancilla qubits which are reset before each measurement round.

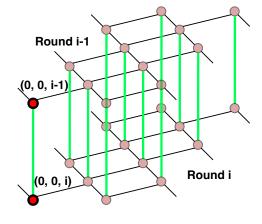

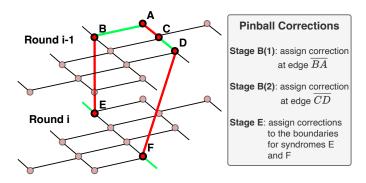

Fig. 8. Full coverage for space-like errors in the predecoding subgraph. Green edges indicate covered errors, and 3D coordinates (x,y,t) specify relative spatial (x,y) and temporal (t) positioning of syndromes. Space-like errors within the bulk of the subgraph are divided into four non-conflicting groups mapped to pipeline stages: (a)  $\mathbf{B}(\mathbf{1})$ , (b)  $\mathbf{B}(\mathbf{2})$ , (c)  $\mathbf{B}(\mathbf{3})$ , and (d)  $\mathbf{B}(\mathbf{4})$ . (e) Space-like errors at the edges of the subgraph are mapped to a separate pipeline stage,  $\mathbf{E}$

Fig. 9. Formation of a time-like error.

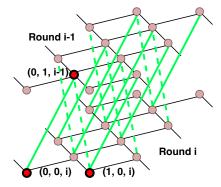

Fig. 10. Full coverage for time-like errors in the predecoding subgraph which are mapped to a single pipeline stage, M.

Fig. 11. Formation of a spacetime-like error.

Fig. 12. Full coverage for single-qubit, spacetime-like errors in the predecoding subgraph. These errors are divided into two non-conflicting groups mapped to pipeline stages ST(1) (solid edges) and ST(2) (dashed edges).

## C. Spacetime-like Errors

We now introduce spacetime-like errors, which arise when considering single-qubit and two-qubit gate errors and how they propagate through the syndrome measurement circuit. Spacetime-like errors correlate syndromes separated both in time (across rounds), and in space (different locations within the surface code lattice). We differentiate between those which propagate to a single data qubit and those which propagate to two data qubits (i.e., hook errors [17]).

An example single-qubit spacetime-like error is shown in Fig. 11. During syndrome measurement round i, the CNOT gate between qubits  $x_1$  and d induces a Z error on qubit d. Since this error only manifests after the CNOT, it is not immediately propagated to qubit  $x_1$  in timestep 2. In timestep 3, the CNOT between qubits  $x_2$  and d propagates the error to qubit  $x_2$  which detects it at the end of the syndrome measurement round. In the absence of correction (corrections are typically applied only after every d rounds of syndrome measurement), the Z error on qubit d persists into round i+1, where it propagates to both qubit  $x_1$  and qubit  $x_2$  in timesteps 2 and 3, respectively. Only qubit  $x_1$  produces an active syndrome, since qubit  $x_2$ 's error parity has not changed from round i.

To achieve full coverage of single-qubit, spacetime-like length-1 errors, we require predecoding primitives covering all pairs of syndromes across consecutive rounds which are adjacent to each other in the surface code lattice (Fig. 12). If both syndromes in a pair are active, the predecoding primitive assigns a correction to the shared data qubit between the ancilla qubits in the lattice.

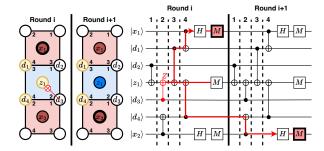

Fig. 13. Formation of a hook spacetime-like error.

Fig. 14. Full coverage for hook spacetime-like errors in the predecoding subgraph mapped to a single pipeline stage, **H**.

Finally, we consider hook spacetime-like errors which are shown in Fig. 13. Unlike all previously analyzed errors, hook errors arise from a unique error source in the syndrome measurement circuit. Specifically, they happen when a Z error occurs on a Z ancilla qubit due to its CNOT gate in timestep 2. Through the CNOT interactions in timesteps 3 and 4, the Z error is propagated to two data qubits,  $d_1$  and  $d_4$ . When qubit  $x_1$  interacts with qubit  $d_1$  in timestep 4, the Z error has already propagated to qubit  $d_1$ , so it is detected in round i. However, by the time the Z error propagates to qubit  $d_4$  (timestep 4), qubit  $x_2$  has already interacted with qubit  $d_4$  for round i, so it does not detect the error. Qubit  $x_2$  is only able to detect the Z error one round later in round i+1.

For Pinball to achieve full coverage of hook errors, we require predecoding primitives which consider pairs of syndromes across consecutive rounds which are separated vertically by two rows of data qubits (Fig. 14). Then, each of these predecoding primitives must correct along the chain of two data qubits between them. It does not matter whether the pair of qubits  $d_1$  and  $d_4$  or qubits  $d_2$  and  $d_3$  are corrected, since these corrections differ by a stabilizer.

#### D. Comparison with Clique

Pinball's coverage substantially improves compared to the current state-of-the-art cryogenic predecoder, Clique [54]. As indicated in Tab. I, Clique includes robust handling of space-like errors, limited handling of time-like errors, and no logic for handling spacetime-like errors. As such, Clique fails to account for many types of error propagation in the syndrome

TABLE I

PREDECODING PRIMITIVE CHECKS: PINBALL VS. CLIQUE.

| Predecoding Primitive Check | Clique | Pinball |

|-----------------------------|--------|---------|

| Bulk Space-like Errors      | Good   | Good    |

| Edge Space-like Errors      | Okay   | Good    |

| Time-like Errors            | Poor   | Good    |

| Spacetime-like Errors       | Absent | Good    |

measurement circuit. Conversely, through detailed circuit-level analysis, we have derived the predecoding primitives necessary to maintain strong coverage of all three error classes. As we show in Sec. VI, these design improvements enable Pinball to significantly outperform Clique in realistic noise settings.

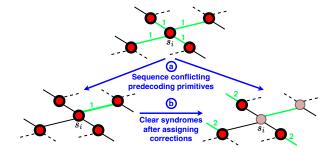

## E. Resolving Predecoding Primitive Conflicts

Since every syndrome in the predecoding subgraph has degree greater than one, an active syndrome,  $s_i$ , could have multiple neighboring syndromes which are also active. Consider the top scenario in Fig 15: as we have described it thus far, Pinball would naively assign corrections to all four edges between  $s_i$  and its active neighbors. However, if these four errors had actually occurred,  $s_i$ 's error parity would have been even, so it never would have been active - thus, the correction is wrong. This contradiction is due to a race condition between the four predecoding primitives which share  $s_i$ . If these primitives are allowed to execute in parallel, they quadruple-count  $s_i$  by mapping it to four predecoding subgraph edges.

To avoid this, two requirements must be met. First, predecoding primitives sharing a syndrome between them must be executed sequentially, one after the other; we refer to such predecoding primitives as *conflicting*. This resolves the race condition by enforcing an ordering between them. Second, to avoid re-counting the same syndrome for multiple errors, each predecoding primitive must clear its pair of active syndromes after mapping them to their corresponding predecoding subgraph edge. These two steps are shown at the bottom of Fig 15. Clearing syndromes after assigning corrections also enables very lightweight complex detection logic: if any active syndromes remain after executing all predecoding primitives, the error pattern must be complex, and the *original*, *unmodified syndromes* are propagated to the RT decoder to generate corrections.

#### IV. HARDWARE DESIGN

Having defined Pinball's algorithm, we now translate it into a lightweight, low-power hardware design. We first discuss the hardware for the predecoding primitive and then expand to a full design covering the entire predecoding subgraph.

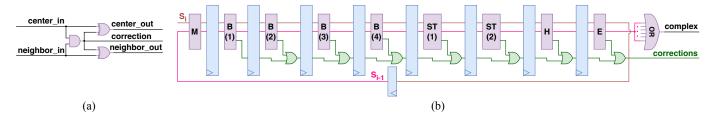

#### A. Predecoding Primitive Logic

A predecoding primitive is responsible for checking a pair of syndromes in the predecoding subgraph, and if they are both active, assigning a correction to the data qubit(s) corresponding to the edge between them. To avoid double-counting active syndromes, it must also clear its syndromes after assigning a

Fig. 15. By sequencing conflicting predecoding primitives and clearing active syndromes (highlighted) after assigning corrections, race conditions are resolved.

correction. The hardware implementing this logic is organized as a two-level combinational circuit as shown in Fig. 16a.

For each pair of syndromes, we call one the "center" and the other the "neighbor". The first-level AND gate indicates if both syndromes are active, and if so, a (set of) correction bit(s) are sent to the location(s) in a  $d \times d$  buffer corresponding to the data qubits that should be corrected. In the second level, the AND gate's output is fed into two XOR gates to conditionally clear the pair of active syndromes if a correction is assigned.

# B. Pipeline Design

To avoid race conditions in assigning corrections, conflicting predecoder primitives must be executed sequentially. To orchestrate this in hardware, we organize Pinball into a sequence of nine pipeline stages (Fig. 16b) where each stage executes a disjoint set of conflict-free primitives in parallel. We now discuss how we derive the nine disjoint sets in each stage.

Beginning with space-like errors, we observe that each syndrome within the bulk of the decoding graph has four neighbors. We refer to the corresponding edges as *bulk space-like errors*. Per bulk syndrome, none of the four predecoding primitives covering its edges can be executed in parallel, and so four separate pipeline stages, **B(1)-B(4)**, are needed.

Space-like errors at the edges of the lattice activate only a single edge syndrome, so we use predecoding primitives with these syndromes as center and *artificial* neighbors. Artificial syndromes are always set to active, allowing Pinball to assign corrections conditioned only on the values of the isolated edge syndromes. These edge space-like errors are handled in a separate stage, **E**, for reasons described in Sec. IV-C.

In Fig. 10, it is clear that, for time-like errors, none of the predecoding primitives conflict. Thus, they can all be executed in parallel within a single pipeline stage which we call **M**.

Finally, recall that spacetime-like errors are organized into two distinct sets: one for errors on a single data qubit and the other, hook errors, for errors on two qubits. From Figs. 12 and 14, most syndromes participate in decoding primitives within both sets, so we handle each set in separate stages.

For single-qubit spacetime-like errors, most syndromes participate in two predecoding primitives, one which leans to the bottom-left from round i-1 to round i (solid lines in Fig. 12) and the other which leans to the bottom-right (dashed lines

Fig. 16. The hardware design for Pinball. (a) The two-level combinational logic implementing a predecoding primitive. (b) Pinball is organized into a pipeline, where each pipeline stage processes a disjoint group of predecoding primitives.

in Fig. 12). We separate these groups into two pipeline stages called **ST(1)** and **ST(2)**. Within the set of hook spacetime-like errors, no predecoding primitives share syndromes, so they can all be executed in parallel in a single stage which we call **H**.

In the final pipeline stage, if any syndromes in  $S_{i-1}$  (and  $S_i$  in the last round of the d-round block) remain active, Pinball was clearly unable to account for all errors, and second-level decoding is required. An OR-reduction tree detects this case, and its complex output triggers offloading of the unmodified d syndrome rounds to RT. Importantly, our selection of disjoint groups allows Pinball to achieve constant predecoding latency per syndrome round independent of code distance.

## C. Pipelining Benefits

The use of pipelining in Pinball has three primary benefits compared to prior cryogenic predecoding work.

- ① First, it allows for the decoding problem to be progressively simplified *in situ* by clearing syndromes in each stage as Pinball generates new corrections. Consequently, full coverage of the decoding graph can be achieved with minimal decoding hardware. Each edge is covered only once and in a single stage throughout the pipeline, so our design features no redundant hardware. This lies in contrast to Clique [54] which redundantly covers each space-like edge twice in order to provide a full set of corrections in one pass. This increased efficiency reduces the additional hardware overhead incurred by Pinball to cover the new spacetime-like edges.

- ② Second, pipelining provides a natural enforcing of order between decoding primitive checks, allowing us to prioritize certain checks over others by placing them earlier in the pipeline. We describe two heuristics for ordering checks. First, decoding primitive groups covering the most common errors should be placed earlier in the pipeline to minimize the likelihood that their associated syndromes are paired with other active syndromes as part of different checks for less common errors. Second, the decoding primitives for edge space-like errors should be placed at the end of the pipeline, since they clear only one syndrome at a time. By doing so, we account for more syndromes through fewer potential errors which has a higher likelihood of being correct.

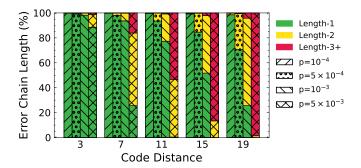

To properly order checks, we simulated  $10^5$  shots of d-round syndrome blocks to obtain a frequency distribution of different error classes in the SI1000 noise model (see Sec. V). In Tab. II, time-like and space-like errors dominate, suggesting their

TABLE II DISTRIBUTION OF LENGTH-1 ERRORS FOR d=11 and  $p=10^{-3}$  in the SI1000 noise model.

| Error Type                           | Frequency (%) |

|--------------------------------------|---------------|

| Time-like Errors                     | 48.02         |

| Space-like Errors                    | 41.65         |

| Spacetime-like Errors (single qubit) | 7.69          |

| Hook Errors                          | 2.63          |

checks should be prioritized. Empirically, we observed best performance when checking time-like errors first.

③ Finally, since there are no control dependencies between Pinball's pipeline stages, it is a fully modular design providing complete freedom to reorder/re-prioritize certain decoding primitive checks. This maybe be useful if different error sources start to dominate over others.

#### D. Pinball Failure Modes

While Pinball's heuristics yield high predecoding performance (Sec. VI), there are inevitably some scenarios in which Pinball both fails to provide an accurate set of corrections *and* fails to detect that the decoding is complex, leading to a logical error. Fig. 17 shows an illustrative example. First, suppose the ordering of bulk space-like checks happens to check edges  $\overline{BA}$  and  $\overline{CD}$  in stages B(1) and B(2), respectively, before edge  $\overline{CA}$  is checked in stage B(4). Consequently, Pinball assigns corrections to the wrong space-like edges, and syndrome pairs BE and DF are broken up, isolating syndromes E and F.

Normally, isolated syndromes raise Pinball's complex flag, but critically, since they both reside at the edges of the decoding graph, Pinball can clear both in stage E. More generally, Pinball's local heuristics are vulnerable in scenarios where it breaks up a pair of active syndromes, and the remaining isolated syndrome lies at the edge of the decoding graph.

## E. Predecoding Imbalance: Energy Saving Opportunity

From Sec. II-C, recall that the decoding rate must be at least as high as the rate of syndrome generation. This sets a most stringent per-round decoding latency budget of  $1\,\mu s$  for superconducting qubit systems. Since the predecoder introduces additional end-to-end latency to the decoding hierarchy, this must be accounted for when determining the operating frequency of the hardware. We can allocate a conservative 10% of the per-round decoding latency budget (100 ns) for predecoding, ensuring that enough time is always reserved for

Fig. 17. A set of errors which Pinball would both fail to decode correctly and flag as complex. Red (green) edges correspond to errors (corrections).

syndrome transmission to RT and second-level decoding. At high code distances, this is much less than 1% of the  $d~\mu s$  required to generate syndrome data, so we can expect Pinball's latency overhead to be negligible.

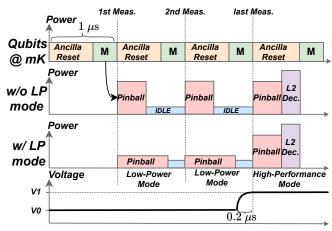

Naively, we would use this 100 ns budget across all d rounds (middle row in Fig. 18) since the same predecoding is performed in each round. However, notice that the predecoding latency impacts the critical path only in the last (d-th) round when data may be transmitted to the second-level decoder. Thus, we identify a significant per-round latency constraint imbalance in the predecoding process: in the first d-1 rounds, predecoding can utilize the full  $1~\mu s$  budget, whereas it must operate within the 100~ns budget in the last (d-th) round.

We exploit this imbalance to lower power and energy consumption through 'workload'-aware performance scaling. For the first d-1 rounds, we use a "low-power (LP) mode", extending processing time while operating at a lower voltage and frequency, whereas in the last round, we use a "high-performance (HP) mode", ramping up to higher voltage and frequency to decrease processing time. Fig. 18 details the proposed workload-aware performance scaling scheme.

We employ a power multiplexer to switch between supply voltages [21] and voltage multiplexers to switch between corresponding body biases. On-chip overhead is limited to only a simple state machine to control the transitions, a small LUT to store voltage-frequency pairs, and a small bank of multiplexing transistors. Transistors can be moderately sized to minimize both power and area overhead, and voltage-frequency pairs can be calibrated during post-silicon testing to compensate for process variation and minimize energy. Additionally, power multiplexing supports fast switching times, enabling the voltage to settle within 200 ns [21] after which the clock frequency can be elevated. As shown in Fig. 18, with the workload-aware performance scaling scheme enabled, Pinball occupies at most 800 ns of the  $1\,\mu s$  window, leaving 200 ns for the power multiplexers to settle before the d-th round.

CMOS threshold voltages increase significantly at cryogenic temperatures, limiting the operable supply voltage headroom; however, forward body biasing can effectively reduce threshold voltages [51]. The 22 nm FDSOI technology supports a wide body biasing range, offering designers fine-grained control of threshold voltages and performance [22]. To char-

Fig. 18. Workload-aware performance scaling by selecting from different supplies and body biases. Voltage switching occurs 200 ns prior to the end of the penultimate round.

TABLE III FREQUENCY AND POWER OF A RING OSCILLATOR AT 4 K ACROSS VARYING SUPPLY AND BODY BIAS VOLTAGES.

| Supply (V)  | 0.8   | 0.6   | 0.54 | 0.5  | 0.48 | < 0.47    |

|-------------|-------|-------|------|------|------|-----------|

| VBN (V)     | 0     | 0     | 0    | 0.2  | 0.3  |           |

| VBP (V)     | 0     | 0     | 0    | -0.3 | -0.3 | Fails to  |

| Freq. (MHz) | 355.9 | 158.5 | 93   | 72.1 | 53.2 | Oscillate |

| Power (µW)  | 184.5 | 16.1  | 2.6  | 1.6  | 0.98 |           |

acterize the impact of supply voltage on the maximum operating frequency at 4 K in the 22 nm FDSOI technology, we constructed a ring oscillator consisting of 301 inverter gates and simulated it under various supply voltages and body biases (VBN for NMOS and VBP for PMOS). The resulting frequency and power data are shown in Tab. III. At supply voltages above 0.54 V, the ring oscillator oscillates successfully without any body bias adjustment. At 0.5 V, forward body biasing becomes necessary to lower the threshold voltages and maintain oscillation. As the supply voltage decreases further, both the operating frequency and power consumption drop significantly. Below 0.47 V, the ring oscillator fails to oscillate regardless of body biasing. We refer to Tab. III in Sec. VI to estimate the energy savings achieved by our workload-aware performance scaling scheme.

#### V. METHODOLOGY

## A. Noise Model

In our evaluations, we use a circuit-level noise model which captures measurement errors, single-qubit and two-qubit gate errors, reset errors, and qubit idling errors. Within circuit-level noise, the error rates of each error source can be scaled by a base physical error rate, p. We simulate p in the range  $10^{-4}-10^{-2}$  to capture performance between higher-end error rates for present-day hardware  $(10^{-2})$  and realistic, future hardware error rates  $(10^{-4})$ . Tab. IV summarizes the SI1000 noise model [28] we use, a realistic noise model inspired by superconducting hardware.

TABLE IV SUPERCONDUCTING HARDWARE NOISE MODEL [28].

| Error Source | Meas. | Reset | 1Q             | 2Q | Idle           | Resonator Idle |

|--------------|-------|-------|----------------|----|----------------|----------------|

| Error Rate   | 5p    | 2p    | $\frac{p}{10}$ | p  | $\frac{p}{10}$ | 2p             |

## B. Decoding Simulation Framework

We run Monte Carlo simulations of decoding on a single logical qubit, varying code distance with odd values between d=3-21. We use Stim [26] to generate d+1 rounds of random error patterns per simulation shot. Corresponding syndromes are sent to the decoder. Since X and Z errors are handled identically, we only simulate Z errors, as is typical in prior QEC work [1], [13], [33], [48], [54], [67], [70].

Per round, we first supply syndromes to Pinball. If it cannot find a full set of corrections, the round is marked complex. If any round with a d-round block is marked complex, the block is passed to Pymatching [31], a Python minimum-weight-perfect matching (MWPM) second-level decoder. In either case, we check if the final corrections cause a logical error. In parallel to Pinball, we also simulate Clique [54] and Promatch [1] to compare with state-of-the-art cryogenic and RT predecoders. For all experiments using a predecoder, we use Pymatching as the L2 decoder. Finally, since [1] found that running Promatch in parallel with Astrea-G [67], a greedy L2 decoder, improved LER, we also compare Pinball to this ensemble configuration labeled Promatch||Astrea-G. Both the predecoder/decoder hierarchies as well as Astrea-G are given a total of d  $\mu$ s to complete decoding.

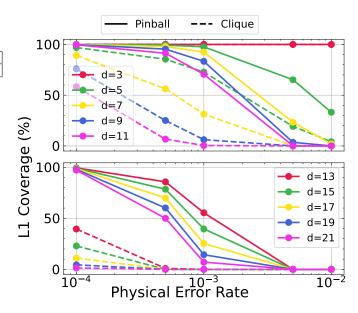

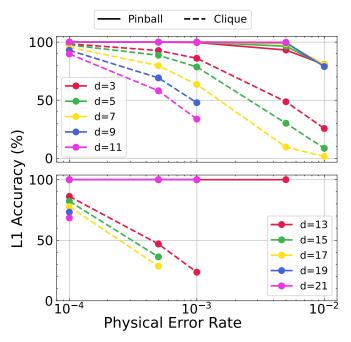

We evaluate Pinball's L1 coverage, the percentage of d-round blocks where none of the rounds were marked complex, and its L1 accuracy, the percentage of non-complex blocks decoded correctly, and compare them with Clique's over  $10^7$  d-round blocks of syndromes. The former is a proxy for syndrome bandwidth reduction, and the latter is a proxy for logical error rate. For all predecoders, we simulate up to  $10^9$  syndrome blocks to determine logical error rate.

## C. Hardware Characterization

We implement Pinball in 22 nm FDSOI technology to measure its power, performance, and area. Standard cells were re-characterized with a commercial 4 K device model to accurately capture cryogenic behavior, after which synthesis, placement, and routing were performed. The resulting netlist was simulated with delay back-annotation, and its activity vectors enable precise per-error-rate 4 K power estimates.

In HP mode, Pinball operates at 0.8 V and 100 MHz, while in LP mode, it operates at 0.48 V and 12.5 MHz, meeting the 800 ns latency over nine clock cycles. Using Tab. III, we scale power and energy according to  $P \propto CV^2 f$  and  $E \propto CV^2$ , respectively, where C is the effective switching capacitance, V the supply voltage, and f the operating frequency.

We compare Pinball's energy consumption with both SFQ and 22 nm FDSOI implementations of Clique. Since the onchip cost for power multiplexing and body biasing is very low, we omit power multiplexing and body biasing when estimating

Fig. 19. L1 coverage comparison between Pinball (solid) and Clique (dashed) showing that Pinball decodes a higher percentage of syndromes within the 4 K stage of the dilution refrigerator.

Pinball's energy consumption. As a baseline, we also consider a system without a cryogenic predecoder where syndrome data is always sent to RT. Two factors contribute to Pinball's energy reduction. First, through its L1 coverage, it reduces the transmission energy used to transmit syndromes to RT. Second, it reduces energy at 4 K by operating in LP mode for d-1 rounds, only switching to HP mode in the last round. In our assessment of these impacts, we use the 2.46 pJ/bit energy efficiency of a recently-proposed cryogenic transmitter [20] to estimate transmission energy.

## VI. EVALUATION

## A. System-Level Cryogenic Predecoding Benefits

Cryogenic predecoding aims to maximize decoding within the cryogenic domain (L1 coverage) without loss of accuracy (L1 accuracy), thereby reducing syndrome bandwidth while maintaining low LER. We evaluate how effectively Pinball achieves this compared to the state-of-the-art Clique [54].

L1 Coverage and Bandwidth Reduction: As shown in Fig. 19, Pinball consistently achieves higher coverage than Clique, and the gap increases with code distance. For near-term error rates ( $p=10^{-3}$ ), Pinball increases coverage up to 77.22% at d=9, reducing syndrome transmission to RT by 5.65× relative to Clique. For long-term error rates ( $p=10^{-4}$ ), Pinball increases coverage up to 95.75% at d=21, giving an additional 34.72× transmission reduction. Note that marginal gains in coverage still give striking system-level performance benefits: both Pinball and Clique have high coverage (> 89%) at  $p=10^{-4}$  and d=7, but Pinball's 10.72% increase gives  $124.33 \times$  higher transmission reduction.

Pinball's coverage improvements are due to three factors. First, and most importantly, Clique fails to consider syndrome

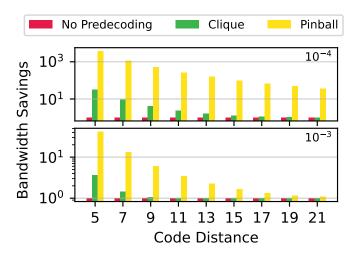

Fig. 20. Bandwidth savings comparisons between Pinball and Clique, normalized to a system which does not use predecoding. Pinball achieves higher bandwidth savings than Clique due to increased L1 coverage.

pairs across space *and* time, so it cannot correct the significant fraction (Tab. II) of spacetime-like errors. Second, Clique handles edge space-like errors before measurement errors, ruling out matching pairs of active syndromes too quickly. Third, for time-like errors, while Pinball clears the syndromes at both endpoints, Clique only suppresses the one in the oldest round. Due to the latter two factors, Clique breaks up more syndrome pairs within the same and across different rounds, leaving more isolated syndromes to be marked complex.

Based on these coverage improvements, we show the increase in syndrome bandwidth savings achieved by Pinball in Fig. 20. Clearly, independent of the underlying physical error rate, p, Pinball achieves exceptional bandwidth savings; at d=3, Pinball achieves full coverage and at d=5  $p=10^{-4}$ , reduces total bandwidth by a maximum  $3780.72\times$ . In the worst case (d=21 and  $p=10^{-3}$ ),  $1.08\times$  reduction is still achieved. **L1 Accuracy and Logical Error Rate:** In Fig. 21, we compare Pinball's L1 accuracy to Clique. Again, Pinball consistently achieves higher accuracy, and the gap increases with code distance and physical error rate. At  $p=10^{-3}$ , Pinball increases accuracy up to  $4.23\times$  at d=13. For d>13, Pinball maintains 100% while Clique's drops to 0%. At  $p=10^{-4}$ , Pinball still gives up to  $1.46\times$  accuracy increase at d=21.

Pinball's improved L1 accuracy translates into radically different LER performance in Fig. 22. As opposed to Clique, using Pinball as the L1 cryogenic predecoder exponentially reduces LER as physical error rate lowers and code distance increases. At  $p=5\cdot 10^{-4}$  and d=11, Pinball improves LER by nearly six orders of magnitude compared to Clique. Clique only achieves comparable LER at high code distances and physical error rates, since in this regime, it offloads most decoding to Pymatching at L2. Again, seemingly marginal gains yield considerably different system-level outcomes. At  $p=10^{-4}$  and d=7, Pinball's "small" L1 accuracy increase of 4.42% reduces LER by nearly seven orders of magnitude.

These results are especially noteworthy when considered

Fig. 21. L1 accuracy comparison between Pinball (solid) and Clique (dashed) showing that Pinball decodes syndromes with higher accuracy than Clique. Note: some data points omitted in due to insufficient L1 coverage.

Fig. 22. Logical error rate comparison between Pinball and Clique.

together with coverage: not only does Pinball handle more decoding scenarios than Clique, it handles this greater number with higher accuracy. On the surface, this result seems counter-intuitive. As Clique's coverage decreases, it is becoming more selective with which syndromes it chooses to handle itself. However, despite being more selective, its accuracy continues to decrease. This is not the case for Pinball; even as its coverage decreases, it consistently maintains high accuracy, suggesting it is more robust against false positives (complex syndromes which it misclassifies as simple) than Clique.

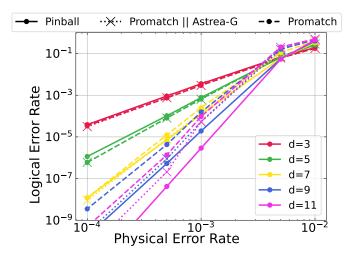

Fig. 23. Logical error rate comparison between Pinball, Promatch, and the ensemble Promatch||Astrea-G [1].

In summary, while Clique was instrumental in laying foundations for cryogenic predecoding, our results indicate it is less likely to provide direct benefits in real-world quantum computing systems. Pinball is the first cryogenic predecoder providing system-level benefits under realistic circuit noise.

#### B. Comparison with RT Predecoding

Next, we contrast Pinball to a recent state-of-the-art RT predecoder, Promatch [1]. As mentioned in Sec. II-E, an ideal decoding hierarchy could feature both cryogenic and RT predecoders. To study their respective predecoding capabilities, we compare the LER of Pinball to Promatch in Fig. 23 when both are independently integrated with Pymatching.

Remarkably, we find that, despite stricter power and area constraints limiting Pinball's complexity, it still achieves a lower LER than both Promatch and Promatch || Astrea-G for  $d \geq 7$ , and the performance gap widens as code distance increases; at  $p = 5 \cdot 10^{-4}$  and d = 11, we observe a  $32.38 \times (5 \times)$  reduction in LER compared to Promatch (Promatch||Astrea-G). We attribute the improvement over Promatch to the different prioritization schemes used in each design: Promatch prioritizes corrections which avoid creating isolated syndromes, whereas Pinball also accounts for the frequencies of different error classes in the ordering of its pipeline stages. Further, Astrea-G often struggles to generate matchings within its allocated latency budget due to denser syndromes under SI1000 noise, limiting the ensemble configuration's benefits<sup>2</sup>. Its results may be improved by increasing its latency budget/operating frequency, but this is orthogonal to our work. Importantly, this result shows that, in a decoding hierarchy with Pinball and Promatch, the system's LER would be limited by Promatch's performance, not Pinball's. For Pinball's full benefits, it could be used with higher-accuracy RT predecoders in the future.

<sup>2</sup>Our Astrea-G comparisons rely on the original paper and codebase. The authors noted in correspondence that they are exploring further optimizations.

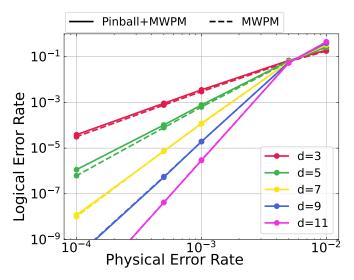

Fig. 24. Logical error rate comparison between a system using Pinball as an L1 predecoder and a system with no predecoder.

## C. Cryogenic Predecoding Impacts on Logical Error Rate

So far, we have compared systems with different predecoders. While Pinball improves LER over these, it must also match the performance of a system without predecoding to ensure its bandwidth gains do not compromise fidelity.

To confirm this, in Fig. 24, we evaluate LER for two configurations: one using Pinball at L1 and Pymatching at L2 and one using only Pymatching at L2. Since Pymatching provides state-of-the-art decoding accuracy, we see a slight increase in LER when using Pinball for low d and physical error rates ( $d \leq 7, p < 10^{-3}$ ). However, beyond d = 7, the system using Pinball closes the gap to achieve near parity in LER, demonstrating that using Pinball maintains the required QEC performance.

## D. Hardware Overheads

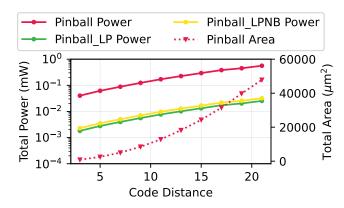

Fig. 25 presents the power and area consumption of Pinball (HP mode), Pinball\_LPNB (LP mode, no body biasing) and Pinball\_LP (LP mode, body biasing), evaluated for  $p=10^{-3}$ . In area, Pinball only consumes  $< 0.05\,mm^2$ , even at the highest d=21. Pinball consumes between 0.04 mW and 0.56 mW of power in HP mode. Based on Sec. V-C, Pinball\_LPNB can operate at 0.54 V supply voltage, while Pinball\_LP can operate even lower at 0.48 V. Both variants can operate at a 12.5 MHz frequency which satisfies the latency constraint of 800 ns (Sec. IV-E). Thus, Pinball\_LPNB and Pinball\_LP achieve 17.5× and  $22.2\times$  power reductions, respectively, compared to HP mode.

Assuming a 1.5 W cooling budget at 4 K [45], and conservatively using worst-case power (i.e, HP mode during the d-th syndrome round), at  $p=10^{-3}$ , we support enough Pinball instances within a single dilution refrigerator to simultaneously decode 37,313 logical qubits at d=3 and 2,668 logical qubits at d=21, showing our design reaches targets well within the early fault-tolerant quantum computing (eFTQC) regime [42].

Fig. 25. Area and power analysis of Pinball's HP and LP mode with (Pinball\_LP) and without (Pinball\_LPNB) body biasing.

## E. Energy Savings

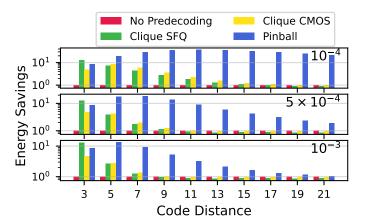

We evaluate the energy of Pinball, CMOS/SFQ Clique, and the baseline system, including predecoder and 4 K-to-RT transmission costs. As shown in Fig. 26, the predecoder's hardware overhead grows with code distance and error rate, reducing its benefit. Still, Pinball's higher coverage allows it to consistently outperform CMOS and SFQ Clique for d > 3.

For  $p=10^{-3}$ , corresponding to the eFTQC regime, energy savings range from  $1.05\times -13.35\times$ . eFTQC devices containing  $\sim 10^4$  physical qubits will likely use code distances below 11 to support 50-100 logical qubits. At these lower code distances, Pinball provides  $3.15\times -13.35\times$  energy savings.

As error rates decrease, higher L1 coverage improves energy savings. Pinball's savings range from  $1.92\text{-}18.57\times$  for  $p=5\cdot10^{-4}$  and from  $8.61\text{-}37.05\times$  for  $p=10^{-4}$ . Thus, as hardware improves, Pinball remains scalable and effective for the higher code distances needed in long-term FTQC. These estimates assume only syndrome payloads are transmitted, underestimating actual transmission costs. In practice, protocols like Riverlane's QEC interface (QECi) [36] use 64-bit packets with 32-bit headers, doubling transmission cost. Accounting for this boosts Pinball's savings to  $1.06\text{-}22.77\times$  at  $p=10^{-3}$ , and up to  $67.4\times$  at  $p=10^{-4}$ .

## VII. DISCUSSION & RELATED WORK

**QEC Codes:** Although we focus on the surface code, many works have explored the general family of quantum low-density parity check codes [15], [27], [29], [55], [59], [68]. We anticipate predecoding to be equally valuable for them.

**Second-Level Decoders:** While we analyzed Pinball with an MWPM-based second-level decoder, many other decoders exist [2], [12], [13], [16], [48], [67], [70]. Our design can be interfaced with any of them. Some work has investigated full-fledged cryogenic decoders [33], [63], [64], but strict 4 K constraints preclude scalability without sacrificing accuracy.

**Predecoders:** Prior works have used neural networks [9] and greedy heuristics [1], [14], [54], [58] to simplify decoding. Only Clique [54] considers cryogenic operation. Relative to state-of-the-art RT and cryogenic predecoders, Promatch [1] and Clique [54], Pinball achieves much lower LER.

Fig. 26. Total energy savings combines the benefits of predecoding and LP mode operation in the first d-1 rounds. Results are shown for physical error rates between  $10^{-4}$  (top) and  $10^{-3}$  (bottom).

**Cryo-CMOS and SFQ Logic:** Advances have been made in both cryo-CMOS [3]–[5], [8], [18], [24], [32], [44], [53], [65], [73] and SFQ [10], [33], [37], [39], [41], [43] technologies as well as modeling tools [7], [49], [50]. As they mature, they may permit deeper decoding hierarchies at intermediate temperature stages (e.g., 77 K) inside the dilution refrigerator.

**Qubit Control and Readout Power:** Current cryo-CMOS control and readout electronics [4], [8], [30], [35], [40], [72] draw too much power, requiring higher efficiency to stay within the 4 K budget. Once trimmed, syndrome transmission power will remain prominent, motivating bandwidth reduction techniques like predecoding. Equally important, the predecoding hardware must add only minimally to the power overhead. These constraints drive the optimizations presented.

#### VIII. CONCLUSION

In this paper, we presented Pinball, a novel cryogenic predecoder tailored to surface code QEC decoding under circuitlevel noise. We analyzed error generation and propagation at the circuit-level to increase predecoder performance, and using an architecture co-optimized with cryo-CMOS technology, effectively managed increased predecoding complexity. Pinball is the first scalable cryogenic predecoder capable of operating effectively under noise present in real quantum systems.

#### **ACKNOWLEDGEMENTS**

This material is based upon work supported by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research, Accelerated Research in Quantum Computing under Award Number DE-SC0025633. This research used resources of the National Energy Research Scientific Computing Center, a DOE Office of Science User Facility supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231 using NERSC award ASCR-ERCAP0033197. The authors also thank Semiwise Ltd., UK for access to the cryo-CMOS PDK used for hardware evaluation in this work.

#### REFERENCES

- [1] N. Alavisamani, S. Vittal, R. Ayanzadeh, P. Das, and M. Qureshi, "Promatch: Extending the reach of real-time quantum error correction with adaptive predecoding," in *Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3*, 2024, pp. 818–833.

- [2] B. Barber, K. Barnes, T. Bialas, O. Bugdaycı, E. Campbell, N. Gillespie, K. Johar, R. Rajan, A. Richardson, L. Skoric, C. Topal, M. Turner, and A. Ziad, "A real-time, scalable, fast and resource-efficient decoder for a quantum computer," *Nature Electronics*, vol. 8, pp. 84–91, 01 2025.

- [3] J. Bardin, E. Jeffrey, E. Lucero, T. Huang, S. Das, D. Sank, O. Naaman, A. Megrant, R. Barends, T. White, M. Giustina, K. Satzinger, K. Arya, P. Roushan, B. Chiaro, J. Kelly, Z. Chen, B. Burkett, Y. Chen, and J. Martinis, "Design and characterization of a 28-nm bulk-cmos cryogenic quantum controller dissipating less than 2 mw at 3 k," *IEEE Journal of Solid-State Circuits*, vol. 54, pp. 1–18, 10 2019.

- [4] J. Bardin, E. Jeffrey, E. Lucero, T. Huang, O. Naaman, R. Barends, T. White, M. Giustina, D. Sank, P. Roushan, K. Arya, B. Chiaro, J. Kelly, J. Chen, B. Burkett, Y. Chen, A. Dunsworth, A. Fowler, B. Foxen, and J. Martinis, "29.1 a 28nm bulk-cmos 4-to-8ghz <2mw cryogenic pulse modulator for scalable quantum computing," in 2019 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 02 2019, pp. 456–458.</p>

- [5] F. Bersano, M. Aldeghi, E. Collette, M. Ghini, F. De Palma, F. Oppliger, P. Scarlino, F. Braakman, M. Poggio, H. Riel, G. Salis, R. Allenspach, and A. Ionescu, "Quantum dots array on ultra-thin soi nanowires with ferromagnetic cobalt barrier gates for enhanced spin qubit control," in 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). IEEE, 06 2023, pp. 1–2.

- [6] M. E. Beverland, P. Murali, M. Troyer, K. M. Svore, T. Hoefler, V. Kliuchnikov, G. H. Low, M. Soeken, A. Sundaram, and A. Vaschillo, "Assessing requirements to scale to practical quantum advantage," arXiv preprint arXiv:2211.07629, 2022.

- [7] I. Byun, J. Kim, D. Min, I. Nagaoka, K. Fukumitsu, I. Ishikawa, T. Tanimoto, M. Tanaka, K. Inoue, and J. Kim, "Xqsim: Modeling crosstechnology control processors for 10+ k qubit quantum computers," in Proceedings of the 49th Annual International Symposium on Computer Architecture, 2022, pp. 366–382.

- [8] S. Chakraborty, D. Frank, K. Tien, P. Rosno, M. Yeck, J. Glick, R. Robertazzi, R. Richetta, J. Bulzacchelli, D. Underwood, D. Ramirez, D. Yilma, A. Davies, R. Joshi, S. Chambers, S. Lekuch, K. Inoue, D. Wisnieff, C. Baks, and D. Friedman, "A cryo-cmos low-power semiautonomous transmon qubit state controller in 14-nm finfet technology," *IEEE Journal of Solid-State Circuits*, vol. 57, pp. 3258–3273, 11 2022.

- [9] C. Chamberland, L. Goncalves, P. Sivarajah, E. Peterson, and S. Grimberg, "Techniques for combining fast local decoders with global decoders under circuit-level noise," *Quantum Science and Technology*, vol. 8, no. 4, p. 045011, 2023.

- [10] J. Choi, I. Byun, J. Hong, D. Min, J. Kim, J. Cho, H. Jeong, M. Tanaka, K. Inoue, and J. Kim, "Supercore: An ultra-fast superconducting processor for cryogenic applications," in 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO). IEEE, 2024, pp. 1532– 1547.

- [11] M. Cusmai, N. Familia, E. Kuperberg, M. Nashash, D. Gottesman, D. Kumar, Z. Marcus, Y. Horwitz, S. Zalcman, J. Kim et al., "7.2 a 224gb/s sub pj/b pam-4 and pam-6 dac-based transmitter in 3nm finfet," in 2024 IEEE International Solid-State Circuits Conference (ISSCC), vol. 67. IEEE, 2024, pp. 126–128.

- [12] P. Das, A. Locharla, and C. Jones, "Lilliput: a lightweight low-latency lookup-table decoder for near-term quantum error correction," in Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, 2022, pp. 541–553.

- [13] P. Das, C. A. Pattison, S. Manne, D. M. Carmean, K. M. Svore, M. Qureshi, and N. Delfosse, "Afs: Accurate, fast, and scalable errordecoding for fault-tolerant quantum computers," in 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, 2022, pp. 259–273.

- [14] N. Delfosse, "Hierarchical decoding to reduce hardware requirements for quantum computing," arXiv preprint arXiv:2001.11427, 2020.

- [15] N. Delfosse, V. Londe, and M. E. Beverland, "Toward a union-find decoder for quantum ldpc codes," *IEEE Transactions on Information Theory*, vol. 68, no. 5, pp. 3187–3199, 2022.

- [16] N. Delfosse and N. H. Nickerson, "Almost-linear time decoding algorithm for topological codes," *Quantum*, vol. 5, p. 595, 2021.

- [17] E. Dennis, A. Kitaev, A. Landahl, and J. Preskill, "Topological quantum memory," *Journal of Mathematical Physics*, vol. 43, no. 9, pp. 4452– 4505, 2002.

- [18] J. Dijk, B. Patra, S. Subramanian, X. Xue, N. Samkharadze, A. Corna, C. Jeon, F. Sheikh, E. Juarez-Hernandez, B. Esparza, H. Rampurawala, B. Carlton, S. Ravikumar, C. Nieva, S. Kim, H.-J. Lee, A. Sammak, G. Scappucci, M. Veldhorst, and F. Sebastiano, "A scalable cryo-cmos controller for the wideband frequency-multiplexed control of spin qubits and transmons," *IEEE Journal of Solid-State Circuits*, vol. 55, pp. 2930–2946, 11 2020.

- [19] J. Edmonds, "Paths, trees, and flowers," *Canadian Journal of mathematics*, vol. 17, pp. 449–467, 1965.

- [20] N. Fakkel, M. Mortazavi, R. Overwater, F. Sebastiano, and M. Babaie, "A cryo-cmos dac-based 40 gb/s pam4 wireline transmitter for quantum computing applications," in 2023 IEEE Radio Frequency Integrated Circuits Symposium (RFIC). IEEE, 2023, pp. 257–260.

- [21] Z. Fan, Q. Zhang, P. Abillama, S. Shoori, J. Lee, C.-W. Tseng, W. Meng, H.-S. Kim, D. Blaauw, and D. Sylvester, "A 22nm 25.08tops/w multitask transformer accelerator with mixed precision structured sparsity and two-stage task-adaptive power management," in 2025 Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2025, pp. 1–3.

- [22] P. Flatresse, B. Giraud, J.-P. Noel, B. Pelloux-Prayer, F. Giner, D.-K. Arora, F. Arnaud, N. Planes, J. Le Coz, O. Thomas et al., "Ultra-wide body-bias range ldpc decoder in 28nm utbb fdsoi technology," in 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers. IEEE, 2013, pp. 424–425.

- [23] A. G. Fowler, M. Mariantoni, J. M. Martinis, and A. N. Cleland, "Surface codes: Towards practical large-scale quantum computation," *Physical Review A—Atomic, Molecular, and Optical Physics*, vol. 86, no. 3, p. 032324, 2012.

- [24] D. Frank, S. Chakraborty, K. Tien, P. Rosno, M. Yeck, J. Glick, R. Robertazzi, R. Richetta, J. Bulzacchelli, D. Ramirez, D. Yilma, A. Davies, R. Joshi, S. Lekuch, K. Inoue, D. Underwood, D. Wisnieff, C. Baks, J. Timmerwilke, and D. Friedman, "Low power cryogenic rf asics for quantum computing," in 2023 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 04 2023, pp. 1–8.

- [25] D. J. Frank, S. Chakraborty, K. Tien, P. Rosno, T. Fox, M. Yeck, J. A. Glick, R. Robertazzi, R. Richetta, J. F. Bulzacchelli et al., "A cryocmos low-power semi-autonomous qubit state controller in 14nm finfet technology," in 2022 IEEE International Solid-State Circuits Conference (ISSCC), vol. 65. IEEE, 2022, pp. 360–362.

- [26] C. Gidney, "Stim: a fast stabilizer circuit simulator," Quantum, vol. 5, p. 497, 2021.

- [27] C. Gidney and C. Jones, "New circuits and an open source decoder for the color code," arXiv preprint arXiv:2312.08813, 2023.

- [28] C. Gidney, M. Newman, A. Fowler, and M. Broughton, "A fault-tolerant honeycomb memory," *Quantum*, vol. 5, p. 605, 2021.

- [29] S. Gu, C. A. Pattison, and E. Tang, "An efficient decoder for a linear distance quantum ldpc code," in *Proceedings of the 55th Annual ACM Symposium on Theory of Computing*, 2023, pp. 919–932.

- [30] Y. Guo, Q. Liu, W. Huang, Y. Li, T. Tian, N. Wu, S. Zhang, T. Li, Z. Wang, N. Deng et al., "29.4 a cryo-cmos quantum computing unit interface chipset in 28nm bulk cmos with phase-detection based readout and phase-shifter based pulse generation," in 2024 IEEE International Solid-State Circuits Conference (ISSCC), vol. 67. IEEE, 2024, pp. 476–478.

- [31] O. Higgott and C. Gidney, "Sparse blossom: correcting a million errors per core second with minimum-weight matching," *Quantum*, vol. 9, p. 1600, 2025.

- [32] M. Hinderling, S. Kate, D. Haxell, M. Coraiola, S. Paredes, E. Cheah, F. Krizek, R. Schott, W. Wegscheider, D. Sabonis, and F. Nichele, "Flipchip-based fast inductive parity readout of a planar superconducting island," *PRX Quantum*, vol. 5, 08 2024.

- [33] A. Holmes, M. R. Jokar, G. Pasandi, Y. Ding, M. Pedram, and F. T. Chong, "Nisq+: Boosting quantum computing power by approximating quantum error correction," in 2020 ACM/IEEE 47th annual international symposium on computer architecture (ISCA). IEEE, 2020, pp. 556–569.

- [34] J. Huang, R. Fu, X. Ye, and D. Fan, "A survey on superconducting computing technology: circuits, architectures and design tools," *CCF Transactions on High Performance Computing*, vol. 4, no. 1, pp. 1–22, 2022.

- [35] W. Huang, Y. Guo, T. Tian, Q. Liu, G. Wei, X. Liu, T. Li, W. Jia, Y. Zheng, Z. Wang et al., "A cryogenic 1.08 mw/qubit fully-integrated 4-channel frequency-division-multiplexing transmon qubit state readout asic in 28nm bulk cmos," in 2025 Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). IEEE, 2025, pp. 1–3.

- [36] A. Husseiniova, K. Johar, K. Barnes, A. Datta, C. Topal, and A. Zeffertt, "QEC Interface for real-time quantum error correction," APS March Meeting, March 2025. [Online]. Available: https://www.youtube.com/watch?v=raVomqQttfU

- [37] K. Ishida, I. Byun, I. Nagaoka, K. Fukumitsu, M. Tanaka, S. Kawakami, T. Tanimoto, T. Ono, J. Kim, and K. Inoue, "Supernpu: An extremely fast neural processing unit using superconducting logic devices," in 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO). IEEE, 2020, pp. 58–72.

- [38] T. Iwai, K. Kawaguchi, T. Miyatake, T. Ishiguro, S. Miyahara, Y. Doi, S. Nur, R. Ishihara, and S. Sato, "Cryogenic integration for quantum computer using diamond color center spin qubits," in 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC). IEEE, 2023, pp. 967–972.

- [39] M. R. Jokar, R. Rines, G. Pasandi, H. Cong, A. Holmes, Y. Shi, M. Pedram, and F. T. Chong, "Digiq: A scalable digital controller for quantum computers using sfq logic," in 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, 2022, pp. 400–414.

- [40] K. Kang, D. Minn, J. Lee, H.-J. Song, M. Lee, and J.-Y. Sim, "34.4 a cryogenic controller ic for superconducting qubits with drag pulse generation by direct synthesis without using memory," in 2023 IEEE International Solid-State Circuits Conference (ISSCC), 2023, pp. 33–35.

- [41] R. Kashima, I. Nagaoka, M. Tanaka, T. Yamashita, and A. Fujimaki, "64-ghz datapath demonstration for bit-parallel sfq microprocessors based on a gate-level-pipeline structure," *IEEE Transactions on Applied Superconductivity*, vol. 31, no. 5, pp. 1–6, 2021.