# **Graph-Based Bayesian Optimization for Quantum Circuit Architecture Search with Uncertainty Calibrated Surrogates**

Prashant Kumar Choudhary prashantkchoudhary.rs.phy22@iitbhu.ac.in Indian Institute of Technology (BHU) Varanasi, Uttar Pradesh, INDIA

Muhammad Shafique New York University Abu Dhabi (NYUAD) Abu Dhabi, UAE muhammad.shafique@nyu.edu

#### **Abstract**

Quantum circuit design is a key bottleneck for practical quantum machine learning on complex, real-world data. We present an automated framework that discovers and refines variational quantum circuits (VQCs) using graph-based Bayesian optimization with a graph neural network (GNN) surrogate. Circuits are represented as graphs, mutated and selected via an expected improvement acquisition function informed by surrogate uncertainty with Monte Carlo dropout. Candidate circuits are evaluated with a hybrid quantum-classical variational classifier on the next-generation firewalltelemetry and network internet of things (NF-ToN-IoT-V2) cybersecurity dataset, after feature selection and scaling for quantum embedding. We benchmark our pipeline against an MLP-based surrogate, random search, and greedy GNN selection. The GNN-guided optimizer consistently finds circuits with lower complexity and competitive or superior classification accuracy compared to all baselines. Robustness is assessed via a noise study across standard quantum noise channels, including amplitude damping, phase damping, thermal relaxation, depolarizing, and readout bit-flip noise. The implementation is fully reproducible, with time benchmarking and export of best-found circuits, providing a scalable and interpretable route to automated quantum circuit discovery.

#### Keywords

Quantum Machine Learning, Variational Quantum Circuits, Bayesian Optimization, Graph Neural Networks, Quantum Architecture Search, Surrogate Modeling.

#### 1 Introduction

Variational quantum circuits (VQCs) have become a central computational primitive for many near-term quantum algorithms, including variational quantum classifier (VQ-C), Quantum Neural Network (QNN), quantum generative adversarial network (QGAN), variational quantum eigensolver (VQE), and quantum approximate optimization algorithm (QAOA) [5,6,9,10,22–24,26–29,41,45]. The performance of a VQC depends critically on both its parameter values and architectural design, defined by the arrangement, type, and connectivity of quantum gates within the circuit [1,19,25,46]. Designing VQC architectures for noisy intermediate-scale quantum (NISQ) devices thus presents a high-dimensional, non-convex optimization problem, with a combinatorial search space that quickly

Nouhaila Innan New York University Abu Dhabi (NYUAD) Abu Dhabi, UAE nouhaila.innan@nyu.edu

Rajeev Singh Indian Institute of Technology (BHU) Varanasi, INDIA rajeevs.phy@iitbhu.ac.in

renders brute-force or exhaustive enumeration intractable as the number of qubits and circuit depth increase [48,56].

To address this challenge, recent work on automated quantum architecture search has adopted techniques from classical neural architecture search (NAS) [8,43], evolutionary strategies, and black-box optimization to systematically explore the quantum circuit design space [12, 13, 17, 30, 49, 54]. In particular, Bayesian optimization (BO) provides a principled and sample-efficient framework for global optimization of expensive-to-evaluate objectives, making it highly suitable for quantum circuit architecture search, where each candidate must be validated via simulation or hardware execution [32, 40, 44, 47, 53].

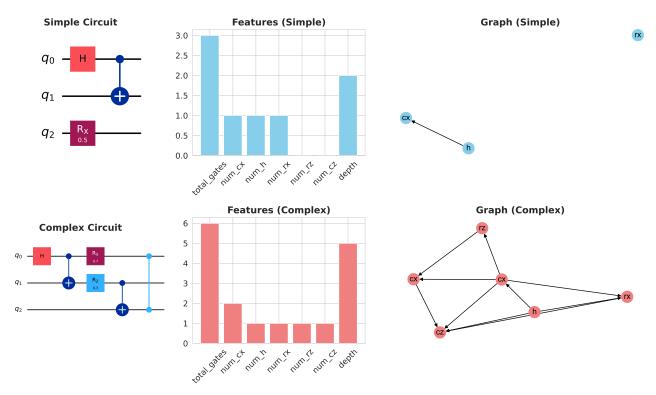

One of the main challenges in BO lies in constructing a surrogate model that can both accurately predict a circuit's performance and provide calibrated epistemic (model) uncertainty that shrinks with data, as opposed to aleatoric (noise) uncertainty [33]. Classical BO typically employs Gaussian processes [4], while simple multilayer perceptrons (MLPs) require fixed-size, hand-crafted vectors and cannot exploit the directed acyclic graph (DAG) structure of quantum circuits, where nodes represent gate operations and edges capture temporal or qubit dependencies. As illustrated in Fig. 1, two circuits may share the same aggregate scalars (e.g., total gates, depth) yet differ substantially in topology and function-information preserved only in their graph representations. This limitation motivates the use of structure-aware surrogates, such as graph neural networks (GNNs), which are designed to process variable-sized, structured data and can naturally represent quantum circuits as graphs—nodes corresponding to gate operations and edges capturing connectivity or temporal dependencies [37,55]. Among them, the Graph Isomorphism Networks (GIN) offer provably strong graph discrimination power (Weisfeiler-Lehman test level) and have demonstrated superior ranking and generalization performance on graph-structured tasks [52]. When equipped with Monte Carlo dropout, GNN-based surrogates can provide both accurate performance predictions and calibrated uncertainty estimates, enabling acquisition strategies such as Expected Improvement (EI) to more effectively balance exploration and exploitation in the BO loop [16].

In this work, we present a graph-based BO pipeline for automated quantum circuit architecture search, targeted toward hybrid quantum-classical classification tasks. Automated quantum circuit search typically suffers from five issues: (i) *collapsed architectural differences* in fixed-vector surrogates (gate counts/depth collapse

Figure 1: Comparison of two quantum circuits with their feature vectors and graph representations. While aggregate scalar features (e.g., gate counts, depth) can appear similar, the graph encoding preserves topological and dependency information critical for distinguishing circuit function. This motivates the use of graph neural networks (GNNs) as structure-aware surrogates in quantum circuit optimization.

non-isomorphic circuits to similar features), (ii) uncertainty miscalibration that destabilizes exploration-exploitation in BO, (iii) hardware insensitivity to device constraints, where architecture selection ignores routing overheads (extra CX/SWAP) that appear after transpilation, (iv) noise insensitivity to realistic  $T_1/T_2$  and readout effects, and (v) search bloat toward deep, two-qubit-heavy layouts.

Our method addresses these challenges through a unified pipeline comprising: a structure-aware GIN surrogate with MC-dropout for calibrated epistemic uncertainty, a tempered, *cost* and noise-aware expected improvement, and a transpiler-aware selection strategy that mitigates the simulator-device gap. The full pipeline is evaluated under comprehensive noise studies and reproducible experimental protocols.

#### Specifically, our contributions are as follows:

- (1) Structure-aware surrogate for VQCs. We encode circuits as graphs with temporal and shared-qubit edges and train a lightweight GIN surrogate that predicts performance and uncertainty (via MC dropout), improving ranking stability across mutated candidates.

- (2) **Cost and noise-aware acquisition.** We introduce a tempered expected improvement objective that integrates normalized complexity terms (depth, total gates, two-qubit/CZ counts) and an optional *decoherence-aware* penalty derived from gate times relative to  $T_2/T_1$ .

- (3) **Hardware-realistic optimization.** We incorporate compilation-induced costs and basic decoherence models into BO, the search

- is biased toward circuits that maintain performance after mapping, narrowing the simulator-to-device gap.

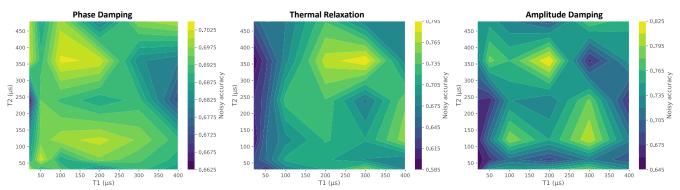

- (4) Comprehensive noise study. We evaluate robustness through thermal T<sub>1</sub>×T<sub>2</sub> sweeps (heatmaps/contours/surfaces), amplitude and phase damping analyses, and probability curves for depolarizing and readout bit-flip noise, clarifying which noise regimes most affect learned circuits.

- (5) Fair and transparent evaluation. Our experiments use leakage-free preprocessing on next generation firewall-telemetry and network internet of things (NF-ToN-IoT-V2), and quantum baselines (BO+VQC+MLP, greedy GNN, random search), with timing breakdowns and Pareto frontiers for accuracy-complexity trade-offs.

- (6) **Reproducibility.** We will release code, configuration files, exported best circuits (QASM/PKL), surrogate metrics (Kendall-*τ*, calibration), and thermal-sweep CSVs; all artifacts will be made public upon acceptance/publication.

The rest of the paper is organized as follows: Section 2 summarizes background and related work. Section 3 details the proposed methodology. Section 4 presents results and ablations, including robustness and Pareto analyses, and discusses limitations and future work. Section 5 concludes the paper.

# 2 Background and Related Work

# 2.1 Automated Quantum Circuit Design

A VQC is a parameterized quantum circuit whose gate parameters are optimized to minimize a task-specific objective (e.g., energy or classification loss). We use automated quantum circuit design to denote methods that search over the discrete, structural degrees of freedom of a quantum program, gate types, ordering, placement, connectivity, depth, and hardware layout, rather than (or in addition to) tuning continuous variational parameters. In the VQC setting, this is precisely architecture search: automatically selecting an ansatz topology (and its hyperparameters) that delivers high task performance under realistic compilation and hardware constraints.

Concretely, a design loop specifies a *search space* of candidate circuits (templates, grammars, or free-form DAGs), a *search algorithm* to propose candidates (heuristics, evolutionary/RL, differentiable relaxations, or BO), and an *evaluation objective* that scores each candidate (validation loss, energy, fidelity), optionally augmented with *cost terms* for routing depth, two-qubit count, and noise penalties.

Automating the design of VQCs has been explored along several fronts: (i) template or heuristic guided search (e.g., QAOA-style layers and their variants) [14]; (ii) differentiable quantum architecture search, which relaxes the discrete circuit space to enable gradientbased selection of gates/topologies (DQAS, QuantumDARTS, and follow-ups) [51]; and (iii) hardware/noise-aware frameworks that cosearch hardware circuits and mappings or otherwise bias search toward device-robust designs (e.g., QuantumNAS and successors) [50]. Despite these advances, recent studies emphasize persistent challenges: how to represent circuits in a way that preserves structural distinctions (beyond coarse counts/depth), how to rank candidates sample-efficiently, and how to account for compilation overheads and decoherence during search [38]. In parallel, BO-style search remains attractive when evaluations are expensive: surrogates with calibrated epistemic uncertainty, using methods such as MC-dropout, coupled with acquisition rules such as EI are standard tools [4, 16, 31].

Our work addresses these gaps by (a) representing circuits as DAGs consistent with compiler toolchains [20] and using a structure-aware GNN surrogate (GIN, with WL-level discriminative power) [52,55], and (b) folding transpiler-induced costs (routing, depth) and simple  $T_1/T_2$ -based decoherence proxies into a cost-aware EI, leveraging realistic compilation settings using SWAP-based bidirectional heuristic search (SABRE) routing algorithm [21].

# 2.2 Bayesian optimization for quantum and hybrid models

BO is a sample-efficient strategy for optimizing expensive black-box objectives by learning a surrogate model over observed evaluations and querying new candidates via an acquisition rule [4,31]. Classical BO commonly relies on gaussian processes (GPs) for smooth, low-dimensional spaces, while neural surrogates (e.g., MLPs) are favored in higher-dimensional or structured settings. A persistent challenge is quantifying *epistemic* uncertainty so acquisition rules like EI can balance exploration and exploitation; practical approximations include MC dropout as approximate Bayesian inference and deep ensembles [16,34].

For discrete or structured design spaces, such as architectures, graphs, or programs, BO must respect non-Euclidean geometry and combinatorial constraints. Early work on *combinatorial BO* introduced structured kernels and learned embeddings to handle sets, sequences, and graphs [2]. In the quantum setting, BO has been used to tune variational parameters and ansatz hyperparameters; however, *architecture-level* search requires surrogates that ingest circuit structure and costs beyond simple scalar features (e.g., depth or two-qubit count). Moreover, realistic acquisition should incorporate device-facing effects (mapping/routing overhead, SWAP/CNOT inflation) and decoherence-aware penalties to avoid overfitting to ideal simulators. These limitations motivate graph-native surrogates with calibrated uncertainty, combined with *cost and noise-aware* acquisition tailored to near-term hardware.

# 2.3 Graph representations of quantum circuits

A quantum circuit admits a DAG representation G = (V, E) whose nodes are operations (including I/O) and whose edges follow qubit/bit wires and temporal dependencies. A *coupling map* is a hardware graph that specifies which qubit pairs support native two-qubit gates; *routing* (or mapping) inserts SWAPs to satisfy this map.

Mainstream toolchains such as Qiskit expose DAGCircuit objects for analysis and transpiler passes [20]. Compiler work exploits these graph forms to reason about coupling maps and routing, with scalable mappers such as SABRE and successive refinements that trade off additional SWAPs, depth, and fidelity [7, 21, 35, 42]. Graph learning has recently been applied to circuits: GNNs and graph transformers can predict circuit fidelity under noise or compilation outcomes from graph-encoded circuits with gate attributes, outperforming flat, hand-engineered features [37, 50]. For VQCs, structural choices affect expressibility and trainability [11, 15, 46], reinforcing the need for structure-aware surrogates in architecture search. Graph encodings preserve topological and temporal information that scalar summaries discard, enable principled interaction with compilers and hardware graphs, and are well matched to modern GNN surrogates for circuit-level prediction. Embedding these encodings within BO closes the loop for automated quantum circuit design as architecture search under realistic hardware constraints.

#### 3 Methodology

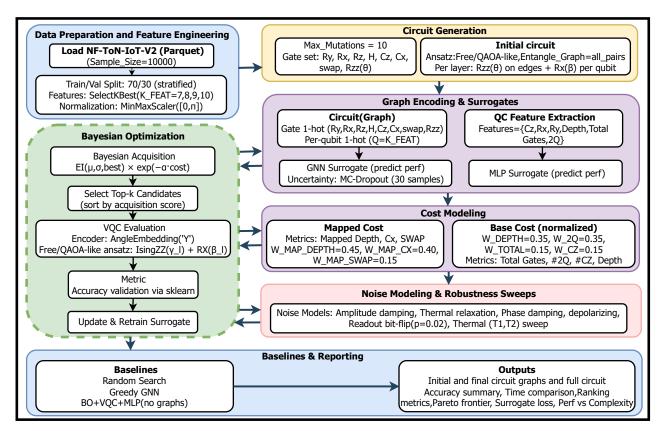

Our proposed pipeline, as presented in Fig. 2, performs hardwarerealistic circuit discovery end-to-end. We begin with data preparation and a fixed VQC model (§3.1), then configure noise and decoherence models (amplitude/phase damping, thermal relaxation, readout error) (§3.2). Next, we apply graph encoding and score candidates with a GIN surrogate using MC-dropout uncertainty, alongside feature-based MLP scores and a cost- and noise-aware EI acquisition (§3.4). We define the hardware-constrained search space and mutation operators that generate candidate circuits (§3.3). The BO loop then iterates: mutate parents  $\rightarrow$  surrogate score  $\rightarrow$  acquire (EI tempered by mapped cost: depth, two-qubit count, CZ/CX, SWAP)  $\rightarrow$  evaluate top-k with the true VQC under the selected noise model → augment the training set and briefly retrain the surrogate (§3.5). Finally, we report accuracy, wall-time, ranking metrics, Pareto fronts, and robustness sweeps, and compare to random, greedy-GNN, and BO+VQC+MLP baselines (§3.6).

# 3.1 Data Preparation and Variational Model

We consider a binary classification task on a balanced subset of the NF-ToN-IoT-V2 dataset [39], comprising N=10,000 samples. Each example represents a network traffic instance characterized by D real-valued features and a binary label indicating normal or attack traffic, denoted as  $(\mathbf{x}_j, y_j)_{i=1}^N$ , with  $\mathbf{x}_j \in \mathbb{R}^D$  and  $y_j \in \{0, 1\}$ .

The dataset is partitioned into a fixed test set of size 2000, a fixed validation set of size 1000, and a remaining training pool. Feature preprocessing is performed on the *train pool only*, we apply a univariate ANOVA-F filter to select the top K informative features, followed by min–max scaling to match the angular encoding range  $[0,\pi]$ . For feature k with train-pool bounds  $a_k,b_k$ , an angle-embedded input used by the quantum circuit is

$$x'_{jk} = \pi \frac{x_{jk} - a_k}{b_k - a_k + \varepsilon}, \qquad k = 1, \dots, K,$$

(1)

where a small constant  $\varepsilon>0$  prevents the division by zero. Throughout, we set the number of qubits to Q:=K and apply AngleEmbedding with  $R_y$  rotations. A candidate VQC consists of a dataencoding unitary  $U_{\rm enc}(\mathbf{x}')$  and a parameterized ansatz  $U(\theta)$  acting on Q qubits. We adopt the standard Hamiltonian-exponential form for all parameterized gates:

$$U(\boldsymbol{\theta}) = \prod_{\ell=1}^{L} \exp\left(-\frac{i}{2} \theta_{\ell} H_{\ell}\right), \tag{2}$$

where each  $H_{\ell}$  is a tensor product of Pauli operators. The gate types used in our search space are {RX, RY, RZ, RZZ, CZ, CX, SWAP, H}. In particular,

$$RX_{i}(\phi) = \exp\left(-\frac{i}{2}\phi X_{i}\right), \qquad RY_{i}(\phi) = \exp\left(-\frac{i}{2}\phi Y_{i}\right),$$

$$RZ_{i}(\phi) = \exp\left(-\frac{i}{2}\phi Z_{i}\right), \qquad RZZ_{ij}(\theta) = \exp\left(-\frac{i}{2}\theta Z_{i}Z_{j}\right), \qquad (3)$$

$$CZ_{ij} = \operatorname{diag}(1, 1, 1, -1), \qquad CX_{ij} = \operatorname{CNOT}_{ij}.$$

The scaled features  $x'_{jk}$  from Eq. (1) are then injected into the quantum circuit through a data-encoding layer composed of single-qubit  $R_v$  rotations:

$$U_{\text{enc}}(\mathbf{x}') = \prod_{i=1}^{Q} \text{RY}_i(x_i'). \tag{4}$$

This encoding maps each normalized feature value to a qubit rotation angle and forms the input layer of the variational quantum circuit.

Beyond the generic ansatz, our framework also covers a QAOA-inspired template with depth p, characterized by a cost Hamiltonian  $H_C$  and a mixer Hamiltonian  $H_M$ :

$$U_{\text{QAOA}}(\boldsymbol{\gamma}, \boldsymbol{\beta}) = \prod_{\ell=1}^{p} \left[ e^{-i\gamma_{\ell} H_{C}} e^{-i\beta_{\ell} H_{M}} \right]. \tag{5}$$

In our experiments,  $H_C$  comprises pairwise  $Z_iZ_j$  couplings (realized via RZZ) and the mixer via single-qubit X rotations,  $H_M = \sum_{i=1}^Q X_i$ . With the encoding and ansatz specified, the circuit generates a parameterized quantum state conditioned on the input features.

Given an input x', the circuit prepares the quantum state

$$|\psi(\boldsymbol{\theta}, \mathbf{x}')\rangle = U(\boldsymbol{\theta}) U_{\text{enc}}(\mathbf{x}') |0^{\otimes Q}\rangle.$$

(6)

Local Pauli-Z expectation values are then measured as

$$z_i(\theta, \mathbf{x}') = \langle \psi(\theta, \mathbf{x}') | Z_i | \psi(\theta, \mathbf{x}') \rangle, \quad i = 1, \dots, Q,$$

(7)

and collected into the vector  $\mathbf{z} \in [-1, 1]^Q$ . These measurements are subsequently processed by a small classical network  $g_{\varphi} : \mathbb{R}^Q \to [0, 1]^2$ , which outputs class probabilities  $p_{\varphi}(c \mid \mathbf{z})$ . The hybrid model parameters  $(\theta, \varphi)$  are optimized jointly using the crossentropy loss over a minibatch  $\mathcal{B}$  of size m:

$$\mathcal{L}_{CE}(\varphi, \boldsymbol{\theta}) = -\frac{1}{m} \sum_{(\mathbf{x}', y) \in \mathcal{B}} \sum_{c \in \{0, 1\}} \mathbb{1}[y = c] \log p_{\varphi}(c \mid \mathbf{z}(\boldsymbol{\theta}, \mathbf{x}')).$$

(8)

## 3.2 Noise and Decoherence Modeling

To emulate realistic NISQ behavior, each candidate circuit is evaluated sequentially under each of the following gate-level noise models: (i) single-qubit *depolarizing*, (ii) *amplitude damping* (AD), (iii) *phase damping* (PD), or (iv) a *thermal* mode that composes generalized amplitude damping (GAD) with PD. For one-qubit and two-qubit gates with durations  $t_{1Q}$  and  $t_{2Q}$ , and device-like relaxation parameters  $(T_1, T_2)$ , we define the effective dephasing time

$$\frac{1}{T_{\phi}} = \frac{1}{T_2} - \frac{1}{2T_1},\tag{9}$$

and the corresponding probabilities as

$$p_{\rm AD}(t) = 1 - e^{-t/T_1}, \qquad p_{\rm PD}(t) = 1 - e^{-t/T_{\phi}}.$$

(10)

where  $p_{\rm AD}(t)$  and  $p_{\rm PD}(t)$  define the characteristic probabilities of AD and PD processes, respectively. In the AD and PD modes, we apply the corresponding channel after each gate using probabilities derived from its duration  $t \in \{t_{1\rm Q}, t_{2\rm Q}\}$  via (10). Each noise process can be described as a completely positive trace-preserving (CPTP) quantum channel  $\mathcal E$  acting on a density matrix  $\rho$ , represented through its Kraus operators:

$$E_{0} = \begin{bmatrix} 1 & 0 \\ 0 & \sqrt{1 - \gamma} \end{bmatrix}, \quad E_{1} = \begin{bmatrix} 0 & \sqrt{\gamma} \\ 0 & 0 \end{bmatrix},$$

$$\mathcal{E}_{AD}(\rho) = E_{0}\rho E_{0}^{\dagger} + E_{1}\rho E_{1}^{\dagger}.$$

(11)

For AD with damping probability  $\gamma$ . Similarly, PD with dephasing probability  $\lambda$  is represented by

$$F_{0} = \sqrt{1 - \lambda} I, \quad F_{1} = \sqrt{\lambda} |0\rangle\langle 0|,$$

$$F_{2} = \sqrt{\lambda} |1\rangle\langle 1|, \quad \mathcal{E}_{PD}(\rho) = \sum_{k=0}^{2} F_{k} \rho F_{k}^{\dagger}.$$

(12)

with  $\lambda = p_{PD}(t)$ .

To approximate simultaneous energy relaxation and pure dephasing, the thermal mode composes a GAD channel (with excited-state

Figure 2: Overview of the hardware-aware, graph-based BO pipeline for VQC circuit search. The workflow proceeds from inputs to results as follows. Data Preparation and Feature Engineering handles preprocessing (§3.1), after which Circuit Generation specifies the ansatz and mutation operators (§3.3). Candidates are then represented via Graph Encoding & Surrogates together with QC Feature Extraction, using a GIN with MC-dropout and a feature MLP (§3.4). Cost Modeling integrates base and mapped hardware costs into the acquisition criterion (§3.4), while Noise Modeling & Robustness Sweeps configure device-level noise and related analyses (§3.2). Within BO, we apply cost-aware expected improvement, select the top-k candidates, perform VQC Evaluation, and update and retrain the surrogate (§3.5). Baselines & Reporting summarize results and comparisons, including accuracy, wall-time, ranking, Pareto and robustness analyses, and final circuit graphs (§3.6).

population  $p_e$ ) and a PD channel after each gate. The GAD component uses

$$G_{0} = \sqrt{p_{e}} \begin{bmatrix} \sqrt{1-\gamma} & 0 \\ 0 & 1 \end{bmatrix}, \quad G_{1} = \sqrt{p_{e}} \begin{bmatrix} 0 & 0 \\ \sqrt{\gamma} & 0 \end{bmatrix},$$

$$G_{2} = \sqrt{1-p_{e}} \begin{bmatrix} 1 & 0 \\ 0 & \sqrt{1-\gamma} \end{bmatrix}, \quad G_{3} = \sqrt{1-p_{e}} \begin{bmatrix} 0 & \sqrt{\gamma} \\ 0 & 0 \end{bmatrix},$$

$$\mathcal{E}_{GAD}(\rho) = \sum_{k=0}^{3} G_{k} \rho G_{k}^{\dagger}, \tag{13}$$

with  $\gamma = 1 - e^{-t/T_1}$ , and is followed by an independent PD channel with probability  $p_{\text{PD}}(t)$  consistent with the target  $T_2$ .

In the depolarizing mode, we model stochastic gate errors with a single-qubit depolarizing channel of probability p,

$$\mathcal{E}_{\rm dep}(\rho) = (1 - p)\rho + \frac{p}{3}(X\rho X + Y\rho Y + Z\rho Z). \tag{14}$$

We apply  $\mathcal{E}_{\text{dep}}$  after each 1-qubit gate with  $p=p_{1q}$  and independently to both qubits after each 2-qubit gate with  $p=p_{2q}$ . (These  $p_{1q}$ ,  $p_{2q}$  are constants in our implementation, not functions of  $T_1$ ,  $T_2$ .)

To account for readout noise and idle-time damping, we apply a classical bit-flip error with probability  $p_{ro}$  to each qubit immediately

before measurement.

$$\mathcal{N}_{\rm ro}(\rho) = (1 - p_{\rm ro}) \rho + p_{\rm ro} X \rho X. \tag{15}$$

Between logical layers, we optionally apply idle-time damping (using the same  $T_1$ ,  $T_2$  mapping) for a fixed inter-layer gap.

To discourage overly deep circuits during search, we add a penalty based on total gate time

$$T_{\text{total}} = n_{1Q} t_{1Q} + n_{2Q} t_{2Q}, \qquad \mathcal{D} = 1 - \exp\left(-\frac{T_{\text{total}}}{T_2}\right), \quad (16)$$

where  $n_{1Q}$  and  $n_{2Q}$  are the counts of one- and two-qubit gates. The quantity  $\mathcal{D}$  is computed per candidate and min–max normalized within the current candidate batch before being combined with other cost terms in the acquisition score.

# 3.3 Graph-Based Surrogate Modeling and Acquisition Strategy

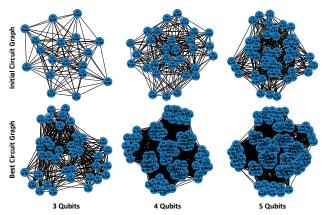

To enable structure-aware circuit evaluation, each candidate circuit is first represented as a directed graph G=(V,E), as illustrated in Fig. 3. Each node  $v\in V$  corresponds to a gate instance and is associated with a feature vector  $x_v$  comprising a one-hot gate type encoding, a normalized temporal position within the circuit,

a Q-dimensional one-hot qubit-incidence vector, and a binary flag indicating whether the gate is two-qubit or single-qubit. Edges capture dependencies between gates, including temporal adjacency (i, i+1), shared-qubit connectivity between gates acting on a common qubit, and per-qubit sequential links connecting consecutive operations on the same qubit.

Figure 3: Graph encoding of a quantum circuit. Each node represents a gate instance with one-hot features for gate type, position, and qubit involvement; edges capture temporal and shared-qubit dependencies. The resulting directed graph enables the GIN surrogate to capture structure-dependent circuit behavior.

We employ a two-layer GIN to learn a surrogate function  $f_{\theta}(G)$  that predicts the validation performance of a circuit from its graph representation. Each GIN layer uses a hidden width of 128, ReLU activations, and dropout of 0.3, followed by global mean pooling and a linear output head.

The surrogate is trained by mean squared error (MSE) to target validation performance  $t_i$ :

$$\min_{\theta} \ \frac{1}{B} \sum_{i=1}^{B} (f_{\theta}(G_i) - t_i)^2. \tag{17}$$

To steer exploration, we estimate epistemic uncertainty with Monte-Carlo dropout with T stochastic forward passes, computing the sample mean and variance as

$$\hat{\mu}(G) = \frac{1}{T} \sum_{t=1}^{T} f_{\theta}^{(t)}(G), \qquad \hat{\sigma}^{2}(G) = \frac{1}{T-1} \sum_{t=1}^{T} (f_{\theta}^{(t)}(G) - \hat{\mu}(G))^{2}.$$

(18)

The surrogate produces, for each candidate graph G, a predictive mean  $\hat{\mu}(G)$  and an uncertainty estimate  $\widehat{\sigma}(G)$ , corresponding to the expected performance and epistemic uncertainty inferred from the GIN model, respectively. These quantities are then used to guide exploration through a cost-aware acquisition function.

Let  $f^*$  denote the best observed validation performance so far. For each candidate, we compute the EI

$$EI(\mu, \sigma; f^{\star}) = (\mu - f^{\star}) \Phi(z) + \sigma \phi(z), \qquad z = \frac{\mu - f^{\star}}{\sigma + \varepsilon}, \quad (19)$$

where  $\Phi$  and  $\phi$  are the standard normal cumulative distribution function (CDF) and probability density function (PDF), respectively, and  $\varepsilon > 0$  ensures numerical stability. To balance performance gain

against circuit complexity, the EI is exponentially tempered by a total cost term:

$$ACQ = EI \cdot exp(-\alpha C_{total}), \qquad C_{total} = C_{base} + C_{map}, \qquad (20)$$

where  $\alpha > 0$  is a weighting hyperparameter and by definition,  $C_{\rm map} = 0$  when mapped-cost routing is disabled or no backend is available. All experiments in this paper satisfy this condition, so  $C_{\rm total} = C_{\rm base}$ .

The base cost  $C_{\text{base}}$  aggregates min–max normalized structural terms within the current candidate batch  $\mathcal{B}$ :

$$C_{\text{base}} = W_{\text{TOTAL}}\widetilde{G} + W_{2Q}\widetilde{G}_{2Q} + W_{\text{CZ}}\widetilde{G}_{\text{CZ}} + W_{\text{DEPTH}}\widetilde{D} + W_{\text{DECOH}}\widetilde{\mathcal{D}},$$

(21)

where  $\widetilde{\mathcal{D}}$  and  $\widetilde{v}$  denote, respectively, the normalized decoherence proxy from Eq. (16) and the min-max scaled quantities:

$$\widetilde{v}_i = \frac{v_i - v_{\min}}{v_{\max} - v_{\min} + \varepsilon}, \quad v \in \{G, G_{2Q}, G_{CZ}, D, \mathcal{D}\}.$$

(22)

This acquisition strategy favors circuits that are predicted to perform well, while penalizing those that are deep, highly entangled, or prone to decoherence and mapping overheads.

# 3.4 Quantum Circuit Search Space and Mutations

Let *C* denote the set of valid circuits over the gate types

$$G = \{RX, RY, RZ, RZZ, CZ, CX, SWAP, H\}.$$

Each circuit  $c \in C$  is represented as an ordered sequence of gate instances  $g_{\ell}(\vartheta_{\ell})$ , each associated with one or more target qubits and, when applicable, a continuous rotation parameter  $\vartheta_{\ell} \in [0, 2\pi)$ . For a fixed, leakage-free data split and a given noise configuration (Sec. 3.2), the black-box objective optimized during BO is defined as

$$F(c) = \mathbb{E}\left[\operatorname{Acc}_{\text{val}}(c)\right] - \lambda \operatorname{penalty}(c),$$

(23)

where  $\mathrm{Acc_{val}}(c)$  is the validation accuracy of the hybrid model based on circuit c, and penalty (c) is a lightweight structural regularization term combining normalized depth, total gate count, and two-qubit gate counts. In the main experiments,  $\lambda$  is set to a small value, and accuracy and mapped hardware costs are reported separately.

Exploration proceeds through local, structure-preserving mutations that maintain each candidate c within C. Given a parent circuit, one of three possible edits is sampled:

- (1) Removing a gate at a uniformly chosen position.

- Replacing a gate with another gate sampled from G while resampling parameters and targets.

- (3) Inserting a new gate from  $\mathcal G$  at a random position.

For parameterized gates,  $\vartheta \sim \mathcal{U}(0,2\pi)$ . Two-qubit targets are drawn uniformly from unordered qubit pairs, and single-qubit targets are drawn uniformly from all available qubits. Let  $p_{\text{rem}}, p_{\text{rep}}, p_{\text{ins}}$  denote the (user-set) probabilities of the three edits operations, satisfying  $p_{\text{rem}} + p_{\text{rep}} + p_{\text{ins}} = 1$ . The resulting mutation kernel  $M(c' \mid c)$  defines a proposal distribution over offspring (children) c' reachable from c in one step; in practice, we apply up to  $m_{\text{max}}$  independent edits per proposal to adjust exploration strength, ensuring circuit validity while introducing architectural diversity for BO selection.

At BO iteration t, the set of evaluated circuits is  $S_t = \{(c_i, y_i)\}_{i=1}^{n_t}$ , where  $y_i = F(c_i)$  denotes the observed performance. A parent pool  $\mathcal{P}_t$  is formed by selecting the top-K circuits according to  $y_i$ , from

which parents are sampled uniformly. Children are generated by applying at most  $m_{\rm max}$  local edits (MAX\_MUTATIONS) to a parent c. At each edit step, the mutation type is drawn from the mixture

$$Pr[delete] = \rho, Pr[replace] = \eta, Pr[insert] = 1 - \rho - \eta,$$

(24)

with  $(\rho, \eta) = (REMOVE\_PROB, REPLACE\_PROB)$ . A *delete* removes a uniformly random gate (if any); *replace* removes a random gate and inserts a new one at the same position; and *insert* adds a new gate at a uniformly random position.

Gate proposals follow  $g \sim \text{Unif}(\mathcal{G})$ , with  $\{i,j\} \sim \text{Unif}(\{\text{unordered qubit pairs}\})$  for two-qubit gates, while  $i \sim \text{Unif}(\{1,\ldots,Q\})$  for single-qubit gates. Parameters for rotation gates (RX/RY/RZ/RZZ) are sampled as

$$\vartheta \sim \text{Unif}[0, 2\pi).$$

(25)

If a sequence becomes empty due to deletions, a single H is inserted on a uniformly chosen qubit to preserve validity. Optionally, a QAOA-inspired restricted space can be enforced by alternating RZZ and RX layers of depth p (cf. (5)); by default, we use a free-form (unrestricted) ansatz.

Each iteration draws N children (N\_CANDS) by repeating the parent sampling and mutation steps. Every child c is mapped to its circuit graph G(c) and scored by the GIN surrogate to obtain MC-dropout statistics  $(\hat{\mu}(c), \widehat{\sigma}(c))$  via Eq. (18). We then compute EI as in Eq. (19) using  $f^* = \max_i y_i$  and temper it with the total cost  $C_{\text{total}}$  to form

$$ACQ(c) = EI[\hat{\mu}(c), \widehat{\sigma}(c); f^{\star}) \cdot \exp(-\alpha [C_{base}(c)]), \quad (26)$$

where  $C_{\text{base}}$  aggregates normalized total gates, two-qubit gates, CZ count, depth, and the decoherence proxy  $\widetilde{\mathcal{D}}$  (Eqs (21)–(22)). The loop runs for T BO iterations (BO\_ITERS); wall-clock and stage-wise timings are logged, and checkpoints of  $(\mathcal{S}_t, \theta)$  are saved periodically. Upon completion, the best circuit by validation accuracy is retrained on train+val and evaluated once on the fixed test split.

Let b=N be the candidate batch size and  $\kappa$  the average number of GIN forward passes per candidate for MC-dropout (MC\_SAMPLES). Per iteration, surrogate scoring is  $O(b \kappa \|G\|)$  where  $\|G\|$  denotes the GNN cost on the circuit graphs (approximately linear in gate and edge counts). True evaluations dominate: if each selected child trains for E epochs on M samples with batch size M, the VQC stage requires O(MEm/B) circuit executions per iteration (with a constant factor for hybrid backpropagation).

To avoid trivial duplicates, canonical gate sequences are hashed, and any repeats are re-sampled. Diversity is encouraged both implicitly by the stochastic mutation kernel and explicitly by cost terms (which penalize over-entangling, deep, and poorly mappable circuits). For reporting, we compute a Pareto frontier of (cost, performance) as in Eq (29).

# 3.5 Bayesian Optimization Loop

The hardware-aware BO loop proceeds per iteration as summarized in Algorithm 1.

#### 3.6 Evaluation and Baseline Strategies

Following completion of the BO loop, the top circuit by validation performance is retrained on the union of the training pool and validation sets (*train+validation*) for 20 epochs with batch size 256, and

Algorithm 1 Hardware-aware BO for VQC circuit discovery

**Require:** Budget: iterations T, parents K, candidates N, evaluations M; MC-dropout samples  $T_{\rm mc}$ ; cost weights W.; tempering  $\alpha > 0$

- 1: Initialize evaluated set  $S_0 \leftarrow \emptyset$  and surrogate  $f_\theta$

- 2: **for** t = 1 to T **do**

- 3: **Select parents:**  $\mathcal{P}_t \leftarrow \text{top-}K$  circuits from  $\mathcal{S}_{t-1}$  by  $y_i = F(c_i)$

- 4: **Mutate & encode:** Generate N children via up to  $m_{\text{max}}$  edits per parent; map each c to graph G(c)

- 5: **Score surrogate:** Compute  $(\hat{\mu}(c), \hat{\sigma}(c))$  via MC-dropout (Eq. (18))

- 6: **Compute costs:** Build  $C_{\text{base}}(c)$  from normalized  $\{\widetilde{G},\widetilde{G}_{\text{2Q}},\widetilde{G}_{\text{CZ}},\widetilde{D},\widetilde{\mathcal{D}}\}$  (Eqs. (21)-(22))

- 7: Acquire:  $\text{EI}(\hat{\mu}, \widehat{\sigma}; f^*)$  with  $f^* = \max y_i$ ; ACQ(c) = EI · (Eqs. (19), (20))

- 8: **Select & evaluate:** Pick top-M by ACQ; train hybrid model (loss  $\mathcal{L}_{CE}$ ) and record y = F(c) (Eqs. (8), (23))

- 9: **Update surrogate:**  $S_t \leftarrow S_{t-1} \cup \{(c, y)\}$ ; brief MSE update of  $f_\theta$  (Eq. (17))

- 10: **Log:** best-so-far, Kendall's au, wall-clock; checkpoint  $(\mathcal{S}_t, \theta)$

- 11: end for

- 12: Finalize: Retrain best-by-validation on train+validation; evaluate once on the fixed test set

then evaluated once on the fixed test split. During BO, the objective is validation accuracy with an optional lightweight complexity penalty,

perf =

$$acc_{val} - \lambda penalty(C)$$

,  $\lambda > 0$ , (27)

where penalty (C) is a normalized structural proxy (e.g., depth, total gates, or fraction of two-qubit/parameterized gates). Unless otherwise stated,  $\lambda$  is small and complexity is also reported separately.

Comparative baselines include BO+VQC with MLP surrogate on flat circuit features (no graph), a greedy GNN selector that ranks candidates by surrogate mean and evaluates the top set, and a random-search policy over the same mutation space. All methods use identical data splits, noise configuration, training hyperparameters, and selection budgets.

We report classification performance (validation during BO, final test at the end), circuit complexity summaries (total gates, two-qubit gates, CZ count, and depth), transpilation/mapping indicators ( $D_{\rm map}$ , CX, SWAP), and performance-cost trade-offs via Pareto frontiers. Robustness is assessed under calibrated noise sweeps, including thermal ( $T_1, T_2$ ) grids as well as amplitude/phase damping and depolarizing/readout variations around the nominal device parameters. Convergence is summarized by best-so-far curves across BO iterations, and runtime by per-iteration wall-clock breakdowns.

For surrogate diagnostics, uncertainty moments from Monte-Carlo dropout are computed as in Eq. (18). Agreement between surrogate predictions and realized performances is quantified by Kendall's  $\tau$ ,

$$\tau = \frac{2}{n(n-1)} \sum_{1 \le i < j \le n} \text{sgn}((\hat{y}_i - \hat{y}_j)(y_i - y_j)), \tag{28}$$

aggregated over candidates scored in each iteration. Pareto dominance in the (cost, performance) plane follows

$cost_a \le cost_b$ ,  $perf_a \ge perf_b$ , with at least one strict inequality,

(29)

and the reported frontier is the set of non-dominated circuits under these criteria.

#### 4 Results and Discussion

### 4.1 Experimental Settings

Experiments are conducted using a High-Performance Computing (HPC) cluster. Models were trained on the PARAM Shivay supercomputer at IIT (BHU), utilizing GPU nodes equipped with 2  $\times$  Intel Xeon Skylake 6148 CPUs (20 cores @ 2.4GHz each), 192GB RAM, and 2  $\times$  NVIDIA Tesla V100 GPUs (5120 CUDA cores, 16GB HBM2). The code execution is parallelized using CUDA and scheduled via Slurm job management, leveraging 100Gbps InfiniBand EDR network communication for efficient multi-node execution.

The key settings are summarized in Table 1.

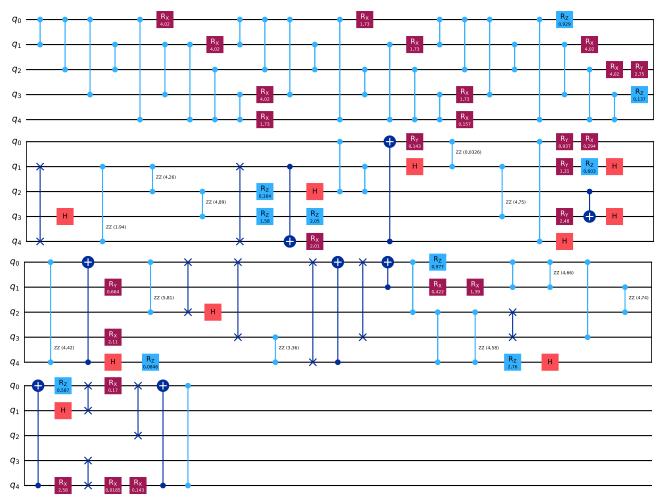

#### 4.2 Best-Found 5-Qubit Circuit

To exemplify the architectural characteristics identified by the proposed BO+VQC+GNN framework, we report a representative 5-qubit configuration obtained during the optimization process (see Fig. 4). Although this instance does not serve as the primary benchmark for the subsequent large-scale evaluations, it provides a concise visualization of the design principles emerging across different qubit regimes. The selected circuit encapsulates the intrinsic tradeoff between representational capacity and cost-constrained search efficiency.

The discovered 5-qubit circuit exhibits a structured alternation of single-qubit parameterized rotations and selective two-qubit entangling operations. The optimization trajectory converged toward a shallow configuration characterized by controlled entanglement density, guided by cost tempering through depth and two-qubit gate regularization. The surrogate model effectively promoted topologies maximizing expressivity under coherence-limited constraints, revealing the model's structural bias toward cost-efficient entanglement.

The learned architecture displays the surrogate's bias toward *cost-efficient entanglement*: it uses just enough two-qubit operations to unlock nontrivial correlations while preserving short depth under coherence constraints. This mirrors our acquisition tempering (Sec. 4.3) and explains why BO+VQC+GNN dominates MLP and search baselines at larger *Q* as well—accurate ranking steers selection, and cost tempering keeps solutions on or near the accuracy—complexity Pareto knee.

The resulting topology demonstrates the surrogate's bias toward low-depth, high-utility circuits, effectively balancing expressiveness and hardware feasibility. This behavior corroborates the acquisition tempering mechanism detailed in Sec. 4.3, confirming that the search process consistently identifies near-Pareto-optimal solutions across different qubit counts.

#### 4.3 Optimization Efficiency Analysis

This section assesses the efficiency of the pipeline in converting compute into progress. We first study *wall-clock efficiency*, breaking down end-to-end time per BO iteration into surrogate inference, surrogate retraining, candidate compilation/mapping, and VQC evaluation, and then compare total wall time and speedups against baselines. We then analyze *convergence and sample efficiency*, quantifying how quickly the best-so-far objective improves as a function of the number of circuit evaluations and elapsed time, under identical budgets.

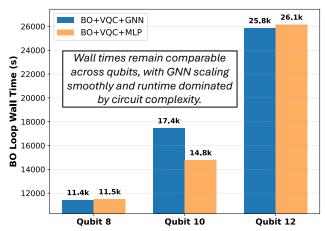

4.3.1 Wall-clock efficiency. As shown in Fig. 5, across 8, 10, and 12 qubits, the BO+VQC+GNN and the BO+VQC+MLP show comparable end-to-end runtimes, indicating that wall-clock cost is dominated by candidate training/evaluation of the hybrid VQC rather than the surrogate itself. The GNN-based pipeline scales smoothly as qubit count increases from 8 to 12, with only a modest rise in elapsed time consistent with deeper circuits and additional two-qubit operations; importantly, MC-dropout inference for the graph surrogate adds negligible overhead relative to the VQC training loop. Overall, the GNN surrogate delivers its structural advantages without imposing a practical time penalty over the MLP baseline; both methods' wall-clock behavior is chiefly governed by optimization of the quantum-classical model, with minor variability when transpiler/mapping steps are included.

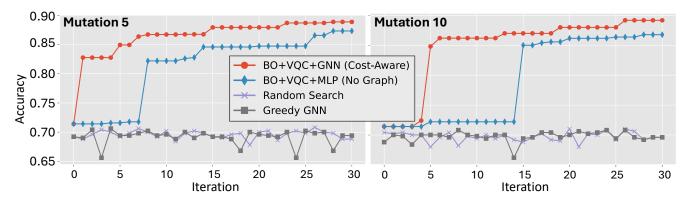

4.3.2 Convergence and sample efficiency. Across both mutation budgets, as shown in Fig. 6, the BO+VQC+GNN curve dominates the BO+VQC+MLP and other baselines throughout the search . In the 5-mutation setting (left panel), GNN starts ahead within the first ~5-10 iterations and maintains a consistent margin thereafter, indicating faster residual shrinkage and more reliable early selections. With 10 mutations (right panel), the advantage of GNN is even more pronounced: the cost aware curve lifts off earlier, climbs more steeply, and attains a slightly higher plateau, while the MLP curve improves more slowly and exhibits mild stalls. The comparison between panels shows that a larger mutation budget accelerates convergence for all methods but disproportionately benefits the graph surrogate, whose structure-aware scoring translates the added architectural diversity into higher-quality candidates more quickly.

#### 4.4 Surrogate Model Performance Evaluation

We evaluate whether the surrogate improves in two ways that matter for BO: (i) *residual convergence*, i.e., the shrinkage of pointwise prediction error as more evaluated circuits accumulate; and (ii) *ranking fidelity*, i.e., the degree to which the surrogate preserves the ordering of candidates well enough to select the right circuits at each iteration.

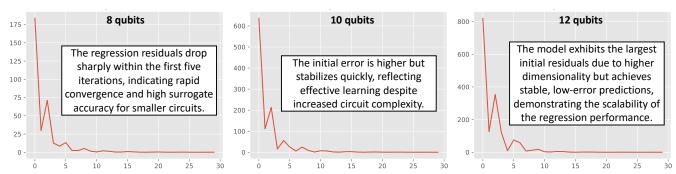

4.4.1 Residual Convergence. Fig. 7 illustrates the evolution of regression residuals across three circuit configurations with 8, 10, and 12 qubits, highlighting the surrogate model's convergence behavior and generalization capability. For 8 qubits, the residuals drop sharply in the first few iterations, which means that the surrogate converges quickly and is very accurate in lower-dimensional search spaces. This early stabilization shows that the model does a good

Table 1: Key hyperparameters and default configuration of the BO pipeline.

| Table 1: Key hyperparameters and default configuration of the BO pipeline. |                                                                                                  |  |  |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Component                                                                  | Setting/Value                                                                                    |  |  |  |

| Qubits/features                                                            | Q=5, 8, 10&12 (K_FEAT=Q)                                                                         |  |  |  |

| <b>Initial Evaluations</b>                                                 | 50 (INITIAL=50)                                                                                  |  |  |  |

| BO iterations                                                              | 100 (BO_ITERS=100)                                                                               |  |  |  |

| Parents/batch                                                              | $K=5, 8, 10\&12 \text{ (TOPK)}, N=5 \text{ (N_CANDS)}$                                           |  |  |  |

| Mutation                                                                   | $m_{\text{max}}=10; (\rho, \eta) = (0.10, 0.10)$                                                 |  |  |  |

| Surrogate (GIN)                                                            | 2 layers, hidden 128, dropout 0.3, global mean pool                                              |  |  |  |

| MC-dropout passes                                                          | $T=30 \text{ (MC\_SAMPLES=30)}$                                                                  |  |  |  |

| VQC candidate train                                                        | 3000 samples, 10 epochs, batch 128                                                               |  |  |  |

| Final train/test                                                           | 20 epochs, batch 256 on train+val; single test pass                                              |  |  |  |

| EI & tempering                                                             | $\alpha$ =0.5                                                                                    |  |  |  |

| Base cost weights                                                          | $W_{\text{DEPTH}} = 0.35, W_{2Q} = 0.35, W_{\text{TOTAL}} = 0.15, W_{\text{CZ}} = 0.15$          |  |  |  |

| Mapping cost weights                                                       | $W_{\text{MAP-DEPTH}} = 0.45, W_{\text{MAP-CX}} = 0.40, W_{\text{MAP-SWAP}} = 0.15$              |  |  |  |

| Gate times                                                                 | $t_{1Q} = t_{2Q} = 300 \text{ ns}; t_{\text{meas}} = 500 \text{ ns}$                             |  |  |  |

| Noise sweeps                                                               | $T_1 \in \{20, 50, 100, 200, 300, 400\} \ \mu s; T_2 \in \{30, 60, 120, 240, 360, 480\} \ \mu s$ |  |  |  |

Figure 4: Best-found 5-qubit architecture returned by BO+VQC+GNN. The circuit exhibits alternating single-qubit rotations (e.g.,  $R_X$ ,  $R_Y$ ,  $R_Z$ ,  $R_Z$ ) and selective two-qubit entanglers (e.g., RZZ/CZ/CX depending on the discovered pattern), forming a shallow, cost-efficient design. Reported costs: total gates = [108], CZ gates = [34], depth = [53]. This matches the frontier region where accuracy gains persist while additional two-qubit count yields diminishing returns.

Figure 5: Wall-time comparison of BO loops. Total BO loop time for BO+VQC+GNN versus BO+VQC+MLP across 8, 10, and 12 qubits, showing comparable efficiency despite richer graph computations due to batched surrogate inference.

job of capturing the structure–performance mapping for smaller circuits.

As the system size increases to 10 qubits, the initial residuals are comparatively higher due to the expanded circuit topology and parameter space. Nevertheless, the residuals quickly plateau to low values, suggesting effective adaptation of the surrogate network to moderately complex quantum architectures. In the case of 12 qubits, the model starts with the largest residual magnitude. This is because higher dimensionality and non-linear entanglement patterns make things harder. But it keeps getting closer to stable, low-error predictions, which shows how strong and scalable the surrogate model is as circuit sizes grow. The overall trend shows that the proposed surrogate keeps high regression fidelity even when quantum configurations are deeper and wider.

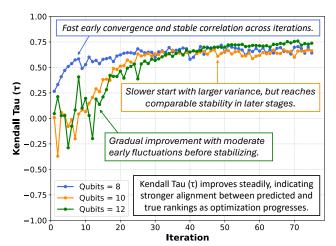

4.4.2 Ranking Fidelity. Fig. 8 reports Kendall's  $\tau$  between surrogate scores and observed validation performance over BO iterations for three circuit widths: 8-qubit, 10-qubit, and 12-qubit. Across all settings,  $\tau$  trends upward with iteration, indicating that the surrogate's pairwise ordering becomes more consistent with ground truth as data accumulates. The 8-qubit curve starts higher and stabilizes earlier, reflecting a simpler search space and fewer two-qubit interactions to model. The 10-qubit curve climbs more gradually and plateaus slightly later, suggesting a moderate increase in combinatorial complexity. The 12-qubit curve exhibits the lowest initial auand the largest early fluctuations, then improves steadily, consistent with the surrogate needing more observations before reliably ranking candidates in a higher-dimensional, more entangling search space. Practically, these dynamics mean BO can trust the surrogate's rankings earlier for 8 qubits, while 10-12 qubits benefit from a longer warm-up (more initial evaluations and/or a higher mutation budget) to reach similarly dependable selection behavior.

#### 4.5 Final Accuracy and Efficiency Trade-offs

Table 2 summarizes validation and test accuracies across qubit scales  $(Q \in \{8, 10, 12\})$ . BO+VQC+GNN consistently matches or exceeds all quantum search baselines and the flat-feature surrogate, with

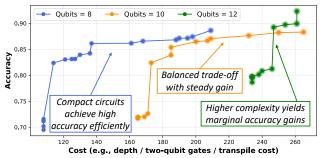

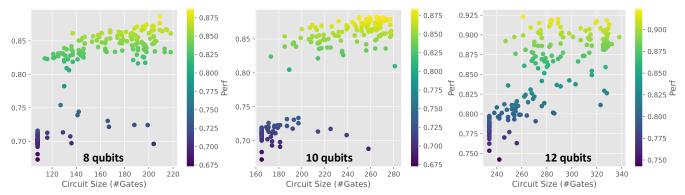

the largest margins at Q=12 where the learned, structure-aware surrogate continues to return high-performing architectures after transpiler and noise-aware tempering. The complementary sensitivity study in Table 3 shows that moderate mutation strength can improve exploration without destabilizing selection: for mutation Mut= 10, BO+VQC+GNN attains higher held-out performance at test time while keeping validation peaks competitive, indicating that our cost/noise-tempered acquisition does not overfit transient candidates. On efficiency, the wall-clock profile indicates that endto-end time scales smoothly with circuit complexity rather than exploding with qubit count: BO+VQC+GNN remains comparable across O=8, 10, 12, suggesting that surrogate scoring and candidate down-selection do not become bottlenecks relative to VQC training/evaluation (see Fig. 5). This aligns with the observation that runtime is dominated by circuit size/depth and evaluation, not by the GNN inference itself, which remains lightweight throughout the loop. Building on this analysis, Fig. 9 presents the Pareto frontiers of validation accuracy versus circuit complexity for O=8, O=10, and Q=12. The Q=8 frontier attains strong accuracy at comparatively low gate budgets, indicating that compact designs already capture most task signal and deliver an excellent accuracy-efficiency balance. The Q=12 frontier ultimately reaches the highest ceiling but exhibits diminishing returns at larger budgets, implying that the extra capacity beyond a mid-complexity regime yields only marginal improvements relative to its added cost. To visualize the tension between performance and circuit size, Fig. 10 scatters validation performance against gate count for all evaluated circuits. We consistently observe diminishing returns for very deep candidates, especially under noisy settings. This empirical trend is aligned with our cost-tempered acquisition (Eqs. (20)), which discourages overly entangling and poorly mappable designs. This reinforces that the proposed pipeline not only scales efficiently in computation but also identifies cost-optimal architectures that sustain strong accuracy under practical compilation and coherence constraints.

#### 4.6 Ablation and Sensitivity Analysis

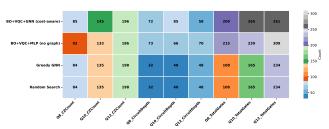

We probe the effect of three design knobs in our pipeline: (i) the mutation budget (how many edits are allowed per iteration), (ii) cost tempering and mapping penalties inside the acquisition (the weight  $\alpha$  and the inclusion of mapped-depth/CX/SWAP terms), and (iii) the surrogate architecture (graph-based vs. flat-feature). Unless stated otherwise, experiments follow the main BO protocol and reuse the same data splits. Starting with on how structural complexity changes between techniques when there are 8, 10, and 12 qubits (see Fig. 11). We use CZ count, circuit depth, and total gate count to do this. As expected, the CZ count and total gates for all approaches increase as the number of qubits goes up. This shows that the architectural search space is getting bigger. For the two baseline heuristics (Greedy GNN and Random Search), we fix the architectural budget (depth and entangler pattern) to remove circuit size as a confounding factor; hence, their gate counts coincide by design, and differences reflect parameter selection alone. In contrast, our target methods (BO+VQC+GNN and BO+VQC+MLP) actively search over architectures via mutation within a constrained family, allowing gate counts (CZ/total/depth) to vary as part of the optimization. The Greedy GNN/ Random Search baselines always make

Figure 6: Convergence of best-so-far validation accuracy under varying mutation rates. For Mutation 5 (left), both GNN- and MLP-based surrogates rapidly improve accuracy, with the cost-aware GNN achieving early and stable convergence. For Mutation 10 (right), higher mutation diversity delays improvement for the MLP baseline, while the GNN surrogate maintains steady progress, highlighting its robustness and structural generalization across broader search spaces.

Figure 7: Residual convergence behavior of the GIN surrogate across 8-, 10-, and 12-qubit configurations. Each plot shows the evolution of regression residuals over BO iterations. The 8-qubit surrogate achieves rapid error decay within the first few iterations, while the 10-qubit model stabilizes after a brief transient phase. The 12-qubit surrogate begins with higher initial residuals due to increased circuit dimensionality but converges to a similarly low-error regime, confirming the scalability and stability of the regression fidelity across circuit sizes.

Table 2: Classification accuracy (%) across methods and qubit counts. Validation and test accuracies for BO+VQC+GNN, BO+VQC+MLP, Greedy GNN, and Random Search confirm the consistent superiority of the proposed GNN-based search framework.

| Method         | Qubits = 8 |           | Qubits = 10 |           | Qubits = 12 |           |

|----------------|------------|-----------|-------------|-----------|-------------|-----------|

|                | val acc.   | test acc. | val acc.    | test acc. | val acc.    | test acc. |

| BO + VQC + GNN | 88.62%     | 88.45%    | 88.30%      | 89.20%    | 92.32%      | 94.25%    |

| BO + VQC + MLP | 87.53%     | 88.35%    | 88.51%      | 86.25%    | 93.17%      | 92.95%    |

| Greedy GNN     | 71.38%     | 73.40%    | 72.12%      | 73.50%    | 80.65%      | 83.35%    |

| Random Search  | 71.58%     | 72.05%    | 72.32%      | 70.90%    | 80.15%      | 83.55%    |

the smallest circuits (with the fewest gates and lowest depth), while the BO+VQC+MLP variation makes the most gates at 12 qubits. The cost-aware BO+VQC+GNN is in the middle of these two extremes. This means that explicit cost modeling slows down circuit expansion compared to MLP, but it doesn't compress as severely as the greedy heuristic. The slight non-monotonicity in circuit depth at 10 qubits indicates method-specific optimization trajectories that result in structurally diverse local optima. In general, these results show that there is a trade-off between compactness (Greedy) and learned cost-aware policies (BO+VQC+GNN) that balance complexity against downstream goals.

To further quantify this trade-off, Table 3 compares 10-qubit experiments under varying mutation limits 5, 10. Increasing the edit budget improves exploration without destabilizing selection:

BO+VQC+GNN yields higher test accuracy at Mut= 10 while keeping validation peaks comparable. In practice, Mut= 10 strikes a good exploration–stability balance; smaller budgets under-explore the neighborhood and saturate early, whereas larger budgets provide diminishing returns.

#### 4.7 Noise Robustness Analysis

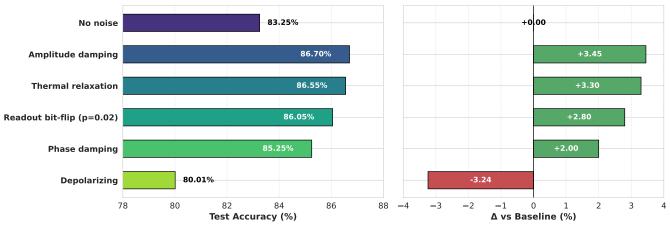

Across six noise scenarios, the learned circuits retain strong performance and, in several cases, even benefit from modest stochasticity. Using the same data split and training budget, the test accuracies are: no noise 83.25%, amplitude damping 86.70%, thermal relaxation 86.55%, readout bit-flip with  $p_{\text{ro}}$ =0.02 at 86.05%, phase damping 85.25%, and depolarizing 80.01% (see Fig. 12). Relative to the no–noise reference, the deltas are +3.45% (amplitude damping),

Table 3: Validation and test accuracies (%) under different mutation rates. The table compares the effect of mutation strengths 5 and 10 on performance for 10-qubit circuits, showing that moderate mutation yields optimal exploration-stability balance.

| Method         | Validation | Accuracy (best perf.) | Test Accuracy (unseen data) |        |  |

|----------------|------------|-----------------------|-----------------------------|--------|--|

|                | Mut=5      | Mut=10                | Mut=5                       | Mut=10 |  |

| BO + VQC + GNN | 89.17%     | 88.88%                | 90.10%                      | 93.20% |  |

| BO + VQC + MLP | 86.77%     | 87.32%                | 86.40%                      | 88.50% |  |

| Greedy GNN     | 71.02%     | 70.82%                | 72.20%                      | 73.40% |  |

| Random Search  | 70.82%     | 70.62%                | 73.50%                      | 72.40% |  |

Figure 8: Evolution of surrogate rank fidelity (Kendall– $\tau$ ) across BO iterations for 8-, 10-, and 12-qubit configurations. The metric measures how consistently the GIN surrogate preserves the ranking of candidate circuits relative to their true validation accuracies. A steady increase followed by an early plateau indicates improved surrogate reliability as more labeled circuits are incorporated, leading to more consistent acquisition and accelerated convergence.

Figure 9: Pareto frontiers of performance versus circuit cost. Non-dominated sets for 8-, 10-, and 12-qubit searches illustrate how accuracy scales with circuit complexity. Compact 8-qubit circuits reach high accuracy efficiently, 10-qubit designs show a balanced cost-performance trade-off, and 12-qubit configurations offer limited accuracy gains despite higher complexity, demonstrating diminishing returns in circuit expansion under the proposed BO+VQC+GNN approach.

+3.30% (thermal), +2.80% (readout bit–flip), +2.00% (phase), 0.00% (no noise), and -3.24% (depolarizing), indicating that most physically motivated channels leave accuracy largely intact or slightly improved, while fully depolarizing errors are the most detrimental.

These trends are consistent with the inductive bias of the pipeline and the character of each channel. Amplitude and thermal damping preferentially relax excited populations and can act as a mild regularizer on angle-embedded features, smoothing sharp decision boundaries and reducing overfitting; a small readout bit-flip rate behaves like measurement-level label noise that likewise regularizes the classifier head. Phase damping (pure dephasing) reduces coherence more directly and thus lowers accuracy modestly. In contrast, single-qubit depolarizing noise injects symmetric, state-independent perturbations after each gate, eroding signal uniformly across the circuit and limiting the advantage conferred by topology-aware search. Practically, circuits selected by our cost and noise-aware BO concentrate in a stable 85%–87% band under realistic  $T_1/T_2$ -like processes and moderate readout imperfections, with a pronounced drop only in the depolarizing case.

To further elucidate these behaviors, Fig. 13 presents contour plots of validation accuracy as a function of coherence times, highlighting the anisotropic sensitivity associated with each noise model. Starting with *Phase damping*, the accuracy improves primarily with increasing  $T_2$  (vertical gradient), while sensitivity to  $T_1$  is weak—consistent with pure dephasing, which is governed by  $T_2$ ; high-accuracy regions concentrate toward the top of the plot even when  $T_1$  is modest. While with *Thermal relaxation*, the accuracy exhibits a diagonal trend, requiring both  $T_1$  and  $T_2$  to be sufficiently large; contours bend along lines of approximately constant effective dephasing time, producing a broad ridge toward the top-right quadrant indicative of coupled amplitude loss and dephasing at finite temperature. And with Amplitude damping, the accuracy increases predominantly with  $T_1$  (horizontal gradient), with a comparatively flatter dependence on  $T_2$ ; plateaus emerge when  $T_1$  exceeds a problem-dependent threshold, at which point additional  $T_2$  gains yield diminishing returns. Taken together, the maps identify practical robustness regimes: (i) for phase damping, prioritize larger  $T_2$ ; (ii) for thermal noise, jointly improve  $T_1$  and  $T_2$ ; and (iii) for amplitude damping, emphasize  $T_1$ . The cost/decoherence-aware BO used in our pipeline aligns with these trends by favoring shallower, lower two-qubit count circuits that sit in higher-accuracy basins across the relevant  $T_1$ – $T_2$  ranges.

# 4.8 Comparison with Existing Quantum Architecture Search Approaches

Previous studies have explored the use of BO for quantum architecture search, predominantly employing Gaussian-process surrogates or handcrafted, kernel-based similarity measures over circuit strings and trees to enable sample-efficient exploration of discrete search spaces [3,18]. Independently, GNNs have been trained on graph- or DAG-based representations of quantum circuits to predict various

Figure 10: Accuracy-complexity trade-off across evaluated circuits. Scatter plots show validation accuracy versus total gate count for 8-, 10-, and 12-qubit configurations. Over-entangling designs exhibit diminishing performance gains, validating the integration of cost tempering within the acquisition strategy.

Figure 11: Complexity metric comparison under acquisition tempering. Heatmap of circuit cost components (depth, CZ count, total gates) across methods and qubit sizes (8-12). The cost-aware BO+VQC+GNN yields systematically lower mapped costs than flat-feature or random baselines.

performance metrics—such as accuracy, circuit depth, and compilation cost—by exploiting structural dependencies that conventional feature-based representations overlook [36].

To the best of our knowledge, these two directions—BO as the outer search strategy and GNNs as structure-aware predictors—have rarely been *explicitly integrated* such that a learned GNN provides both mean predictions and calibrated uncertainty for the *acquisition* step. Our work addresses this gap by embedding a lightweight GIN surrogate within the BO loop, quantifying epistemic uncertainty via MC dropout, and tempering the Expected Improvement criterion with hardware-realistic costs (depth, two-qubit count, routing) and a decoherence proxy. This integrated formulation achieves higher predictive accuracy and sample efficiency than flat-feature BO, while maintaining computational scalability.

#### 5 Conclusion

In this work, we presented an end-to-end framework for *automated* VQC discovery that couples graph-based BO with a lightweight, uncertainty-aware GIN surrogate. By encoding circuits as graphs and learning a structure-sensitive performance model, our pipeline identifies compact, selectively entangling designs that are both accurate and hardware-conscious. The acquisition function integrates standard EI, a cost tempering that penalizes depth and two-qubit content, and an optional decoherence proxy derived from  $T_1/T_2$ -informed gate times. Together, these ingredients shift search away from over-entangled, poorly mappable candidates and toward efficient circuits that retrain well on the full data split.

On a balanced NF-ToN-IoT-V2 task with leakage-free preprocessing and fixed splits, our BO+VQC+GNN framework achieved strong validation quality with fewer true evaluations than random or greedy strategies, and outperformed a flat-feature MLP surrogate in rank fidelity and wall-clock time-to-quality. Final test results show that the BO+VQC+GNN outperforms BO+VQC+MLP and other quantum baselines, while the Pareto analysis highlights favorable accuracy–complexity trade-offs: our frontier attains similar accuracy with fewer two-qubit gates and smaller depth. Noise robustness sweeps further indicate graceful degradation under reduced coherence times, with improvements in  $\overline{\rm Acc}$  and  $\mathcal{A}_\gamma$  when the decoherence-aware term is enabled during selection.

Limitations. Our experiments rely primarily on simulator-based evaluation (analytic expectations inside the BO loop), which can overestimate on-device performance. While cost-aware terms and post hoc noise sweeps mitigate this gap, broader backends and direct device runs remain for future work. Additionally, complexity is treated via a light penalty; an explicit multi-objective treatment could trace the frontier more uniformly.

Outlook. Promising directions include multi-fidelity BO that interleaves fast shot-free scoring with periodic shot/noise checks, richer operator sets, and data re-uploading with hardware-efficient templates, pretraining structure-aware surrogates on large corpora of circuit graphs, and direct tri-objective optimization over (accuracy, cost, robustness). Given its modular design, our pipeline can be reused across datasets and hardware targets with minimal changes: swap the feature selection, choose a backend, and re-run the same BO loop to obtain compact, robust, and interpretable quantum circuits.

Key takeaway. Automating circuit discovery with a structureaware, uncertainty-calibrated surrogate and physics-informed acquisition delivers circuits that are accurate, efficient, and robust, a practical step toward scalable quantum machine learning on nearterm architectures.

# Acknowledgments

This work was supported by the HRD Group of the Council of Scientific & Industrial Research (CSIR) provided CSIR Research Fellowships, and in parts by the NYUAD Center for Quantum and

Figure 12: Noise comparison across quantum noise channels (5-qubit case, N = 10,000). Test accuracies of BO+VQC+GNN under amplitude damping, phase damping, thermal relaxation, depolarizing, and readout bit-flip noise indicate that certain physical noise processes, such as amplitude and thermal relaxation, can yield marginal accuracy improvements relative to the noise-free baseline, whereas depolarizing noise causes mild degradation. Overall, the model demonstrates graceful performance variation and strong robustness across diverse noise regimes.

Figure 13: Noise robustness via coherence-time sweeps. Validation accuracy landscapes for phase damping, thermal relaxation, and amplitude damping across  $(T_1, T_2)$  grids highlight the dependence of model stability on qubit coherence properties. The results show that circuits guided by graph-based acquisition maintain higher resilience and smoother accuracy variations across decoherence regimes.

Topological Systems (CQTS), funded by Tamkeen under the NYUAD Research Institute grant CG008.

The authors also acknowledge the National Supercomputing Mission (NSM) for providing computing resources of "PARAM Shivay" at the Indian Institute of Technology (BHU), Varanasi, which is implemented by C-DAC and supported by the Ministry of Electronics and Information Technology (MeitY) and Department of Science and Technology (DST), Government of India.

#### References

- ALAMI, M. E., INNAN, N., SHAFIQUE, M., AND BENNAI, M. Comparative performance analysis of quantum machine learning architectures for credit card fraud detection. arXiv preprint arXiv:2412.19441 (2024).

- [2] BAPTISTA, R., AND POLOCZEK, M. Bayesian optimization of combinatorial structures. In Proceedings of the 35th International Conference on Machine Learning (10–15 Jul 2018), J. Dy and A. Krause, Eds., vol. 80 of Proceedings of Machine Learning Research, PMLR, pp. 462–471.

- [3] BENÍTEZ-BUENACHE, A., AND PORTELL-MONTSERRAT, Q. Bayesian parameterized quantum circuit optimization (bpqco): A task and hardware-dependent approach, 2024

- [4] BROCHU, E., CORA, V. M., AND DE FREITAS, N. A tutorial on bayesian optimization of expensive cost functions, with application to active user modeling and hierarchical reinforcement learning, 2010.

- [5] CEREZO, M., ARRASMITH, A., BABBUSH, R., BENJAMIN, S. C., ENDO, S., FUJII, K., McClean, J. R., MITARAI, K., YUAN, X., CINCIO, L., AND COLES, P. J. Variational quantum algorithms. *Nature Reviews Physics* 3, 9 (2021), 625–644.

- [6] CHEN, S. Y.-C., YANG, C.-H. H., QI, J., CHEN, P.-Y., MA, X., AND GOAN, H.-S. Variational quantum circuits for deep reinforcement learning. *IEEE Access* 8 (2020), 141007–141024.

- [7] CHILDS, A. M., SCHOUTE, E., AND ÜNSAL, C. M. Circuit transformations for quantum architectures. In 14th Conference on the Theory of Quantum Computation, Communication and Cryptography (TQC 2019) (2019), vol. 135 of LIPIcs, pp. 3:1-3:24.

- [8] CHITTY-VENKATA, K. T., AND SOMANI, A. K. Neural architecture search survey: A hardware perspective. ACM Computing Surveys 55, 4 (2022), 1–36.

- [9] CHOUDHARY, P. K., INNAN, N., SHAFIQUE, M., AND SINGH, R. Hqnn-fsp: A hybrid classical-quantum neural network for regression-based financial stock market prediction. arXiv preprint arXiv:2503.15403 (2025).

- [10] DAVE, K., INNAN, N., BEHERA, B. K., MUMTAZ, S., AL-KUWARI, S., FAROUK, A., ET AL. Optimizing low-energy carbon iiot systems with quantum algorithms: Performance evaluation and noise robustness. *IEEE Internet of Things Journal* (2025)

- [11] Du, Y., HSIEH, M.-H., LIU, T., AND TAO, D. Expressive power of parametrized quantum circuits. Phys. Rev. Res. 2 (Jul 2020), 033125.

- [12] Du, Y., Huang, T., You, S., HSIEH, M.-H., AND TAO, D. Quantum circuit architecture search for variational quantum algorithms. npj Quantum Information 8, 1 (2022), 62

- [13] DUTTA, S., INNAN, N., YAHIA, S. B., AND SHAFIQUE, M. Qas-qtns: Curriculum reinforcement learning-driven quantum architecture search for quantum tensor networks. arXiv preprint arXiv:2507.12013 (2025).

- [14] FARHI, E., GOLDSTONE, J., AND GUTMANN, S. A quantum approximate optimization algorithm, 2014.

- [15] FUNCKE, L., HARTUNG, T., JANSEN, K., KÜHN, S., AND STORNATI, P. Dimensional expressivity analysis of parametric quantum circuits. *Quantum 5* (Mar. 2021), 422.

- [16] GAL, Y., AND GHAHRAMANI, Z. Dropout as a bayesian approximation: Representing model uncertainty in deep learning. In *Proceedings of The 33rd International Conference on Machine Learning* (New York, New York, USA, 20–22 Jun 2016), M. F. Balcan and K. Q. Weinberger, Eds., vol. 48 of *Proceedings of Machine Learning Research*, PMLR, pp. 1050–1059.

- [17] HE, Z., CHEN, H., ZHOU, Y., SITU, H., LI, Y., AND LI, L. Self-supervised representation learning for bayesian quantum architecture search. *Physical Review A* 111, 3 (2025), 032403.

- [18] HE, Z., CHEN, H., ZHOU, Y., SITU, H., LI, Y., AND LI, L. Self-supervised representation learning for bayesian quantum architecture search. *Phys. Rev. A* 111 (Mar 2025), 032403.

- [19] Hubregtsen, T., Pichlmeier, J., Stecher, P., and Bertels, K. Evaluation of parameterized quantum circuits: on the relation between classification accuracy, expressibility, and entangling capability. *Quantum Machine Intelligence* 3, 1 (2021), 9.

- [20] IBM QUANTUM. DAGCircuit: Quantum circuit as a directed acyclic graph, 2025. Accessed: 2025-10-28.

- [21] IBM QUANTUM. Transpilation Optimizations with SABRE, 2025. Accessed: 2025-10-28.

- [22] INNAN, N., BEHERA, B. K., AL-KUWARI, S., AND FAROUK, A. Qnn-vrcs: A quantum neural network for vehicle road cooperation systems. *IEEE Transactions on Intelligent Transportation Systems* (2025).

- [23] INNAN, N., AND BENNAI, M. A variational quantum perceptron with grover's algorithm for efficient classification. Physica Scripta 99, 5 (2024), 055120.

- [24] INNAN, N., KASHIF, M., MARCHISIO, A., BENNAI, M., AND SHAFIQUE, M. Next-generation quantum neural networks: Enhancing efficiency, security, and privacy. In 2025 IEEE 31st International Symposium on On-Line Testing and Robust System Design (IOLTS) (2025). IEEE, pp. 1–4.

- [25] INNAN, N., KHAN, M. A.-Z., AND BENNAI, M. Financial fraud detection: a comparative study of quantum machine learning models. *International Journal of Quantum Information* 22, 02 (2024), 2350044.

- [26] INNAN, N., KHAN, M. A.-Z., AND BENNAI, M. Quantum computing for electronic structure analysis: Ground state energy and molecular properties calculations. *Materials Today Communications* 38 (2024), 107760.

- [27] INNAN, N., KHAN, M. A.-Z., PANDA, B., AND BENNAI, M. Enhancing quantum support vector machines through variational kernel training. *Quantum Information Processing* 22, 10 (2023), 374.

- [28] INNAN, N., SALEEM, A., MARCHISIO, A., AND SHAFIQUE, M. Quantum portfolio optimization with expert analysis evaluation. arXiv preprint arXiv:2507.20532 (2025).

- [29] INNAN, N., SIDDIQUI, O. I., ARORA, S., GHOSH, T., KOÇAK, Y. P., PARAGAS, D., GALIB, A. A. O., KHAN, M. A.-Z., AND BENNAI, M. Quantum state tomography using quantum machine learning. *Quantum Machine Intelligence 6*, 1 (2024), 28.

- [30] INNAN, N., SINGH, A., AND SHAFIQUE, M. Circuithunt: Automated quantum circuit screening for superior credit-card fraud detection. arXiv preprint arXiv:2508.21366 (2025).

- [31] JONES, D. R., SCHONLAU, M., AND WELCH, W. J. Efficient global optimization of expensive black-box functions. *Journal of Global Optimization* 13, 4 (1998), 455–492.

- [32] JOY, T. T., RANA, S., GUPTA, S., AND VENKATESH, S. Batch bayesian optimization using multi-scale search. Knowledge-Based Systems 187 (2020), 104818.

- [33] KENDALL, A., AND GAL, Y. What uncertainties do we need in bayesian deep learning for computer vision?, 2017.

- [34] LAKSHMINARAYANAN, B., PRITZEL, A., AND BLUNDELL, C. Simple and scalable predictive uncertainty estimation using deep ensembles, 2017.

- [35] LI, G., DING, Y., AND XIE, Y. Tackling the qubit mapping problem for nisq-era quantum devices. In Proceedings of the 24th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS '19) (New York, NY, USA, 2019), Association for Computing Machinery, pp. 1001–1014.

- [36] LI, S., TSUKAYAMA, D., SHIRAKASHI, J.-I., SHIBUYA, T., AND IMAI, H. Quantum architecture search with neural predictor based on zx-calculus. EPJ Quantum Technology 12, 1 (2025), 106.

- [37] LIU, Y., MENG, F., WANG, L., HU, Y., ZHANG, Z., AND YU, X. Output prediction of quantum circuits based on graph neural networks, 2025.

- [38] MARTYNIUK, D., JUNG, J., AND PASCHKE, A. Quantum architecture search: A survey. In 2024 IEEE International Conference on Quantum Computing and Engineering (QCE) (2024), vol. 01, pp. 1695–1706.

- [39] MOHANAD SARHAN, SIAMAK LAYEGHY, M. P. Nf-ton-iot-v2. https://www.kaggle.com/datasets/dhoogla/nftoniotv2. Accessed: 2025-04-23.

- [40] NGUYEN, V. Bayesian optimization for accelerating hyper-parameter tuning. In 2019 IEEE Second International Conference on Artificial Intelligence and Knowledge Engineering (AIKE) (2019), pp. 302–305.

- [41] PATHAK, P., OAD, V., PRAJAPATI, A., AND INNAN, N. Resource allocation optimization in 5g networks using variational quantum regressor. In 2024 International

- Conference on Quantum Communications, Networking, and Computing (QCNC) (2024), IEEE, pp. 101–105.

- [42] QIU, C., AND COAUTHORS. A beam search framework for quantum circuit mapping. Entropy 27, 3 (2025), 232.

- [43] SALMANI POUR AVVAL, S., ESKUE, N. D., GROVES, R. M., AND YAGHOUBI, V. Systematic review on neural architecture search. Artificial Intelligence Review 58, 3 (2025), 73.

- [44] SHIELDS, B. J., STEVENS, J., LI, J., PARASRAM, M., DAMANI, F., ALVARADO, J. I. M., JANEY, J. M., ADAMS, R. P., AND DOYLE, A. G. Bayesian reaction optimization as a tool for chemical synthesis. *Nature* 590, 7844 (2021), 89–96.

- [45] SHU, R., XU, X., YUNG, M.-H., AND CUI, W. Variational quantum circuits enhanced generative adversarial network, 2024.

- [46] SIM, S., JOHNSON, P. D., AND ASPURU-GUZIK, A. Expressibility and entangling capability of parameterized quantum circuits for hybrid quantum-classical algorithms. Advanced Quantum Technologies 2, 12 (2019), 1900070.

- [47] SNOEK, J., LAROCHELLE, H., AND ADAMS, R. P. Practical bayesian optimization of machine learning algorithms, 2012.

- [48] STEIN, C., AND FÄRBER, M. Incorporating quantum advantage in quantum circuit generation through genetic programming, 2025.

- [49] Su, J., Fan, J., Wu, S., Li, G., Qin, S., and Gao, F. Topology-driven quantum architecture search framework. Science China Information Sciences 68, 8 (2025), 180507.

- [50] WANG, H., DING, Y., GU, J., LIN, Y., PAN, D. Z., CHONG, F. T., AND HAN, S. Quantumnas: Noise-adaptive search for robust quantum circuits. In 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA) (2022), pp. 692– 708

- [51] Wu, W., Yan, G., Lu, X., Pan, K., And Yan, J. QuantumDARTS: Differentiable quantum architecture search for variational quantum algorithms. In Proceedings of the 40th International Conference on Machine Learning (23–29 Jul 2023), A. Krause, E. Brunskill, K. Cho, B. Engelhardt, S. Sabato, and J. Scarlett, Eds., vol. 202 of Proceedings of Machine Learning Research, PMLR, pp. 37745–37764.

- [52] XU, K., HU, W., LESKOVEC, J., AND JEGELKA, S. How powerful are graph neural networks? In *International Conference on Learning Representations (ICLR)* (2019).

- [53] YANG, K., LIU, L., AND WEN, Y. The impact of bayesian optimization on feature selection. Scientific Reports 14, 1 (2024), 3948.

- [54] ZHANG, S.-X., HSIEH, C.-Y., ZHANG, S., AND YAO, H. Differentiable quantum architecture search. Quantum Science and Technology 7, 4 (2022), 045023.