# LaMoSys3.5D: Enabling 3.5D-IC-Based Large Language Model Inference Serving Systems via Hardware/Software Co-Design

Qipan Wang Student Member, IEEE, Zhe Zhang, Shuangchen Li, Hongzhong Zheng Member, IEEE, Zheng Liang Student Member, IEEE, Yibo Lin Member, IEEE, Runsheng Wang Member, IEEE, Ru Huang Fellow, IEEE

Abstract—The success of large language models (LLMs) amplifies the need for high-throughput, energy-efficient inference at scale. 3D-DRAM-based accelerators provide high memory bandwidth and therefore an opportunity to accelerate the bandwidth-bound decode phase. However, how to adequately balance compute density for prefill with bandwidth/capacity for decode remains open. Moreover, most prior designs do not target end-to-end serving, leaving the co-design of dataflow, parallel mapping, and scheduling underexplored.

To bridge the gap, we present *LaMoSys3.5D*, to our knowledge the first scalable 3.5D-IC architecture for LLM serving. *LaMoSys3.5D* composes heterogeneous 3D-DRAM chiplets on a 2.5D interposer: compute-rich chiplets for prefill and bandwidth/capacity-rich chiplets for decode. To realize efficient serving, we adopt a hardware–software co-design spanning dataflow, parallel mapping, and introduce a thermal-aware modeling and hierarchical design-space exploration framework. Across diverse LLMs and workloads, *LaMoSys3.5D* improves throughput-per-watt over DGX-A100 systems by 62% and achieves a 4.87× better end-to-end latency (geo-mean) versus prior 3D designs. We further distill intriguing design guidelines for 3.5D-IC architectures and end-to-end inference serving.

Index Terms—Large Language Model, Inference Serving, 3.5D-IC, Chiplet Integration, Hardware/Software Co-Design

## I. INTRODUCTION

Large language models (LLMs) are permeating everyday applications [1]. Their rapid adoption drives up inference cost and creates a pressing need for *high-throughput*, *energy-efficient* serving at scale. LLM inference has two phases with distinct characteristics (Fig. 1(a)). *Prefill* is the forward pass

This work was supported in part by the National Natural Science Foundation of China (Grant No. 62125401, 62034007), the Natural Science Foundation of Beijing, China (Grant No. Z230002), the Grant QYJS-2023-2303-B, the Beijing Outstanding Young Scientist Program (JWZQ20240101004), and the 111 Project (B18001).

- Q. Wang is with the School of Advanced Interdisciplinary Studies and the School of Integrated Circuits, Peking University, Beijing 100871, China. Work done during an internship at Alibaba DAMO Academy.

- Z. Liang is with the Department of Electrical Engineering and Computer Science, University of California at Berkeley, Berkeley, CA 94720 USA.

- Z. Zhang, S. Li and H. Zheng are with the Alibaba DAMO Academy and Hupan Lab, China.

- Y. Lin, R. Wang, and R. Huang are with the School of Integrated Circuits, Peking University, Beijing 100871, China; also with the Beijing Advanced Innovation Center for Integrated Circuits, Beijing 100871, China; and the Institute of Electronic Design Automation, Peking University, Wuxi 214135, China.

Corresponding authors: Yibo Lin (yibolin@pku.edu.cn) and Runsheng Wang (r.wang@pku.edu.cn).

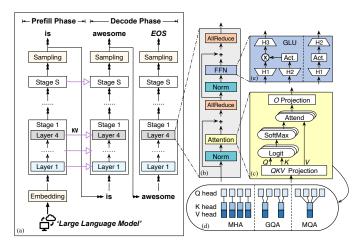

Fig. 1: LLM inference flow, including (a) the prefill and decode phases of the input sequence "Large Language Model", (b) architecture blocks of each transformer layer, (c) computation diagram of the self-attention block, (d) variants of attention operators, (e) variants of dense FFN operations.

over the prompt and is compute-dominated. *Decode* is an autoregressive loop that repeatedly accesses weights and the KV cache; it is bandwidth- and capacity-bound. Meeting these demands requires an inference hardware system that jointly optimizes compute and memory to sustain high throughput and energy-efficiency in both phases.

Recent reasoning-oriented models [2]—e.g., OpenAI o1 [3], DeepSeek-R1 [4], and QwQ [5]—prioritize decode speed, exposing limits of current hardware. HBM-based 2.5D ICs (e.g., GPU/TPU) dominate today, but HBM PHYs and routing consume substantial interposer area, constraining nearby logic. Some proposals offload decode to process-in-memory (PIM)type architectures; however, this reduces compute density and thus harms prefill performance. Hybrid-bonded (HB) 3D-DRAM offers an alternative: prototypes show higher memory bandwidth and lower energy/bit than HBM [6], [7]. Beyond a single 3D-DRAM chiplet, heterogeneous integration introduces a new degree of freedom: specialize computerich chiplets for prefill and bandwidth-/capacity-rich ones for decode. This motivates a 3.5D-IC architecture that balances compute and memory for efficient LLM serving; however, realizing this vision raises three challenges.

- (1) Dataflow design to exploit 3D bandwidth. Classical dataflow for DDR/HBM-based systems minimizes off-chip traffic by maximizing on-chip SRAM reuse. To harness the high bandwidth of 3D-DRAM, TETRIS [8] reduces SRAM buffer size and pushes part of the computation toward memory; H2-LLM [9] co-designs hardware and dataflow for a 3D-DRAM near-memory–processing (NMP) architecture; and 3D-TokSIM [10] couples 3D-DRAM with PIM and adopts a token-stationary schedule. However, these designs largely depend on approximate analytical models or heuristic search. Achieving an optimal dataflow for 3D-DRAM requires a complete specification of data reuse patterns and a scalable search over the whole mapping space.

- (2) Inference optimization on 3.5D-IC. Large-scale serving uses tensor and pipeline parallelism (TP/PP) and depends on efficient collective communications. Conventional GPU/TPU clusters adopt fully connected or ring topologies and high-speed fabrics (e.g., NVLink). Chiplet systems instead form side-by-side meshes over an interposer [11], [12], [13]. Despite high die-to-die bandwidth, jointly optimizing the parallel mapping and scheduling to minimize intra-/inter-chiplet communication for diverse LLM workloads on such a topology remains unsolved.

- (3) Thermal risks in 3.5D-IC. The multilayer stack and compact chiplet layouts in 3.5D-IC increase heat density and impede heat removal, exacerbating thermal issues[14]. Elevated temperature degrades performance (e.g., refresh-induced bandwidth loss), increases leakage power, and undermines reliability [15], [16]. Ignoring thermal effects during early design can lead to significant post-deployment inefficiencies. Therefore, thermal behavior should be modeled from the outset under realistic workloads, and its impact on performance and power should be quantified.

In response, we present *LaMoSys3.5D*, to our knowledge **the first 3.5D-IC architecture designed for efficient LLM serving.** We assemble heterogeneous 3D-IC chiplets side-by-side on a 2.5D interposer, combining 3D vertical bandwidth/capacity with 2.5D lateral scalability. Our contributions are:

- We analyze LLM serving demands and introduce a scalable 3.5D-IC architecture tailored to modern, PDdisaggregated serving.

- We define the complete dataflow–mapping space with 3D-DRAM, and propose a 3D-native  $D^3$  dataflow that finds near-optimal mappings.

- We develop novel parallel mapping strategies that reduce inter- and intra-chiplet communication cost.

- We build an end-to-end, temperature-aware simulation framework for 3.5D-IC LLM inference serving, and use it to conduct hardware—software co-design and designspace exploration (DSE).

Across diverse LLMs and workloads, LaMoSys3.5D improves throughput-per-watt over DGX-A100 systems by 62% and achieves a  $4.87\times$  better end-to-end latency (geo-mean) versus prior 3D designs. It also demonstrates high performance on workloads with long output sequences,  $17.0\times$  decode acceleration compared to A100, making it a promising candidate for future inference systems.

## II. BACKGROUND

### A. LLM Inference

Modern decoder-only LLMs use the Transformer architecture [17], which stacks identical layers (Fig.1(b)) of self-attention and feed-forward networks (FFNs)[18], implemented with either dense blocks[19], [20] (Fig.1(e)) or mixture-of-experts (MoE) modules[21]. During prefill, the model processes the input sequence in one forward pass to compute the distribution of the first output token; it also produces per-token key-value (KV) vectors that are stored as the KV cache for subsequent steps. During decode the model generates tokens autoregressively: at each step, it retrieves the KV cache, performs QKV projections, forms attention logits via  $QK^{\top}$ , applies SOFTMAX, attends to V, and performs FFN; the new K and V are appended to the cache.

We evaluate serving performance with four metrics: end-toend latency (E2E, total time to produce the response), time to first token (TTFT, dominated by prefill), time between tokens (TBT, average per-token latency during decode), and throughput (TPT, tokens per second). Service level objects (SLOs) vary by task: batch workloads (e.g., summarization) emphasize throughput, while interactive workloads (e.g., dialog) prioritize TTFT and TBT. Reasoning models further tighten TBT due to inference-time scaling and longer sequences.

# B. LLM Serving Optimization

Dynamic scheduling and parallelism are two common techniques that drive efficient LLM serving. ORCA [22] proposes continuous batching, which inserts new requests into a batch as soon as others finish, and selective batching, which batches only some operations while executing self-attention for requests in sequence. The compute and memory demands of modern LLMs make multi-device inference attractive, especially when one device cannot hold the model and its KV cache. Pipeline parallelism partitions layers into stages on distinct devices (Fig.1(a)); overlapping requests across stages to improve throughput. Tensor parallelism shards large tensor operations or attention heads across devices to accelerate, at the cost of inter-device communication and synchronization. For example, Megatron-LM[23] distributes parameters across model dimensions and requires two all-reduce collectives per layer—after self-attention and after the FFN (Fig. 1(b)). Logically, this is a reduce followed by a multicast.

## C. 3.5D-IC Overview

The term "3.5D-IC" [12] denotes packages that integrate one or more 3D-stacked dies within a 2.5D-IC system. Two packaging techniques enable this integration: hybrid bonding and the silicon interposer. HB provides ultra-fine-pitch dieto-die connections, often below 10 μm, enabling thousands of links per mm². For example, stacked embedding DRAM (SeDRAM)[6], [24], [7] uses HB to stack DRAM onto logic, achieving bandwidth and energy efficiency that surpass those of GDDR and HBM. Similarly, AMD's 3D V-Cache [25], [26] employs hybrid Cu–Cu bonding to stack an SRAM chiplet on a compute die. The 2.5D interposer connects chiplets, HBM,

and passive components [27] via TSVs and a back-end-of-line metal stack, linked with microbumps, enabling high-speed dieto-die communication across the package.

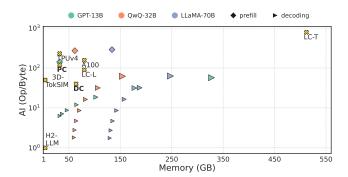

Fig. 2: AI and memory requirements for the prefill and decode phases of different LLMs. The batch size of decode ranges from 1 to 64, indicated by the size of the triangles.

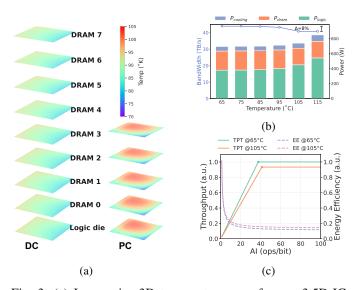

Fig. 3: (a) Layer-wise 3D temperature map for our 3.5D-IC running certain workload. (b) Total power (7 nm logic and 22 nm DRAM) and chiplet bandwidth versus temperature. (c) Temperature-aware roofline model.

TABLE I: Comparison of Different 3D-DRAM Dataflow.

| Name                  | Compute Element | Data Reuse Pattern | Mapping Strategy  |

|-----------------------|-----------------|--------------------|-------------------|

| TETRIS [8]            | Mac Tree        | Selective          | Analytical        |

| [28]                  | Systolic Array  | Input and Output   | Heuristic         |

| NicePIM [29]          | PIM             | Input and Output   | Heuristic         |

| H2-LLM [9]            | Mac Tree        | Selective          | Heuristic         |

| 3D-TokSIM [10]        | PIM Core        | Input and Output   | Analytical        |

| D <sup>3</sup> (Ours) | Systolic Array  | Selective          | Exhaustive Search |

# III. MOTIVATION

# A. Analysis of LLM Inference

Prefill and decode stress hardware in different ways. Fig.2 reports arithmetic intensity (AI; FLOPs per byte moved) for representative LLMs—GPT3-13B[19], QwQ-32B [30], [31], and LLaMA3-70B [20]—across batch sizes 1–64 with input length 4096 and output length 2048. A roofline view shows a

sharp phase asymmetry. Prefill has high AI and is compute-bound; decode has low AI and is bandwidth-/capacity-bound. Increasing batch size raises AI and improves utilization, but it also inflates DRAM capacity demand—especially for multi-head attention (MHA) models such as GPT-13B due to rapid KV-cache growth. In contrast, grouped-query attention (GQA)[32], used in LLaMA and QwQ, shrinks the cache footprint and eases bandwidth pressure (Fig.1(d)).

These observations motivate prefill-decode (PD) disaggregated serving: map compute-intensive prefill to compute-centric devices and memory-bound decode to bandwidth-/capacity-centric devices. Prior work explores this idea either with heterogeneous pairings (e.g., H100–A100 in Splitwise [33], NPU–Flash in Cambricon-LLM [34], CPU–PIM in CENT [35], and others [36], [37]) or by partitioning homogeneous clusters into dedicated prefill and decode pools (e.g., DistServe, Sarathi-Serve [38], [39]).

## B. Opportunities with HB-based 3D-DRAM

The rise of reasoning-oriented LLMs makes decode throughput the primary determinant of serving efficiency. We annotate arithmetic intensity (AI) and memory capacity for major platforms—A100, TPUv4, LLMCompass designs (*LC-L, LC-T*) [40], 3D-TokSIM [10], H2-LLM [9], and our 3D-IC chiplets (*PC, DC*). Systems with limited off-chip bandwidth—GDDR-based (e.g., *LC-T*) or HBM-based (e.g., *A100, TPUv4, LC-L*)—exhibit a high AI, pushing most decode workloads into the bandwidth-bound regime. As a result, compute is underutilized and throughput is capped.

Recent efforts integrate HB-enabled 3D-DRAM with NPUs for transformers [29], [28], [41], [9], [10]. As shown in Fig. 2, these prototypes raise the memory roofline and ease bandwidth pressure (e.g., 3D-TokSIM, H2-LLM). Beyond bandwidth, HB integration reduces the interposer footprint compared to HBM, enabling higher on-die compute density and heterogeneous integration.

Motivated by this, we instantiate a 3D-DRAM chiplet template and, by configuring hardware parameters, derive compute-rich chiplets for prefill and bandwidth-/capacity-rich chiplets for decode. We assemble them side-by-side on a 2.5D interposer to form a 3.5D-IC, combining 3D vertical bandwidth/capacity with 2.5D lateral scalability.

### C. Challenges Facing 3.5D-IC

a) (1) SRAM-centric dataflow misfit 3D-DRAM: Classical accelerator dataflow minimizes DRAM traffic by staging operands in SRAM to maximize reuse. For example, LLM-Compass [40] optimizes GEMM via exhaustive tiling and loop-order search under this SRAM-centric philosophy. In contrast, emerging 3D-DRAM approaches SRAM in bandwidth and energy consumptions (e.g., 0.66–0.88 pJ/bit [6], [7]). In many kernels, the cost of fetching data directly from 3D-DRAM can rival buffering them in SRAM. Building on this observation, TETRIS [8] reduces on-chip SRAM size and pushes part of the computation toward memory; H2-LLM [9] co-designs hardware and dataflow to exploit 3D-DRAM bandwidth with a prefill-aware dataflow; and 3D-TokSIM [10] combines 3D-DRAM with PIM and adopts a token-stationary

flow that keeps token-related data in PIM while streaming weights. Tab. I summarizes the compute element, data reuse pattern, and mapping strategies of representative works. However, these designs rely on approximate analytical models (e.g., TETRIS, 3D-TokSIM) or heuristic algorithms (H2-LLM) to search the mapping, which risks missing the optimum. A 3D-native dataflow that flexibly allocates data across SRAM and 3D-DRAM and enables a scalable search for (near-)optimal mappings remains unsolved.

b) (2) Mesh-topology-aware parallel execution.: CoWoS-class 2.5D technologies [11], [12] scalable die-to-die bandwidth, yet efficient inter-/intrachiplet communication for TP/PP remains open. TP/PP deployments commonly target uniform-cost topologies like rings or all-to-all. Our assembly instead forms a two-level mesh (intra- and inter-chiplet) with distance-dependent communication costs; standard ring all-reduce and related collectives become mismatched, inflating latency and KV traffic. Prior art does not close this gap. Gemini[42] maps CNN layers across chiplets in Simba-like systems using inter-/intra-layer partitioning. PALM[43] considers TP/PP mapping within two-level tiling structures for both training and inference. But these methods rely on heuristics without optimality guarantees and largely overlook KV-cache traffic. These observations call for TP/PP mappings that best suit the two-level mesh.

c) (3) Thermal risks in 3.5D-ICs.: The multi-layer stack configuration intensifies thermal risks [44]. Fig. 3(a) shows a 3.5D-IC thermal map with peak temperatures above  $100\,^{\circ}\mathrm{C}$ . When temperature exceeds  $85\,^{\circ}\mathrm{C}$ , JEDEC mandates higher refresh (lower tREFI), reducing effective DRAM bandwidth[16]. As shown in Fig. 3(b), a  $40\,^{\circ}\mathrm{C}$  rise (from  $65\,^{\circ}\mathrm{C}$  to  $105\,^{\circ}\mathrm{C}$ ) increases logic leakage by  $\sim\!20\%$  and lowers peak DRAM power by  $\sim\!10\%$  due to refresh, cutting usable bandwidth by  $\sim\!10\%$  for our 3D-IC. The roofline therefore shifts unfavorably (Fig. 3(c)), reducing throughput and worsening energy per operation.

Although prior work has addressed thermal-aware design, cooling, and runtime management for 2.5D/3D ICs [45], [46], [15], early-stage thermal evaluation for 3.5D-IC is still lacking, posing performance and reliability risks. This gap motivates workload-aware, transient thermal analysis integrated into early architecture design.

To address these issues, we first propose a 3D-native dataflow, then devise mesh-aware parallel mapping and scheduling strategies, and build a unified full-stack framework coupling hardware modeling, mapping optimization, and performance and thermal analysis. On this basis, we perform hierarchical, thermal-aware DSE across hardware (chiplet and system) and software (dataflow and parallel mapping).

### IV. 3.5D-IC ARCHITECTURE

## A. Overall Design

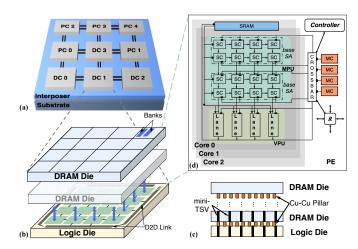

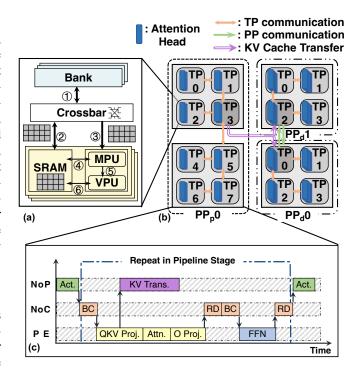

As shown in Fig. 4(a), multiple chiplets are arranged in a mesh [13] and interconnected via die-to-die (D2D) links. Each chiplet is implemented as a DRAM-on-logic 3D-IC: DRAM layers are stacked directly above the logic die using HB as

Fig. 4: Hardware template of the proposed LaMoSys3.5D.

shown by Fig. 4(b) and (c). The memory and logic dies may use different technology nodes; in all cases, the logic-die area is bounded by the DRAM die footprint, and total power is constrained by thermal headroom.

At the system level, we provision chiplets with similar functionality but different compute-memory ratios to compose scalable serving clusters. Prefill chiplets (PC) are computeleaning and require fewer memory banks/layers due to modest bandwidth and capacity demands. Decode chiplets (DC) are memory-leaning: they increase the number of banks/layers and allocate more area to memory controllers (MCs) while reducing compute. Distinct parallelism requirements in prefill and decode [47] are met by tailoring the number of PEs per chiplet. PC and DC variants share a unified core design and DRAM IP, enabling a PD-disaggregated serving system when clustered together. At the chiplet boundary, D2D links on all four edges connect to a network-on-package (NoP) over a passive interposer, following SIAM-style hierarchy [48]; we use AIB 2.0 [49] as the PHY, provisioned for up to 1 TB/s aggregate bandwidth.

## B. 3D-DRAM Design

We adopt a fine-grained die-stacked DRAM organization [7], [50]. The stack comprises  $N_{\text{layer}}$  DRAM dies, each implementing  $N_{\text{bank}}$  banks. Every bank exposes an  $N_{\text{io}}$ -bit TSV data interface, creating independent vertical channels that exploit bank-level parallelism. TSV fabric traverses the stack and terminates at MCs on the logic die via HB, enabling very wide interfaces and few-ns read/write latency in advanced nodes. DRAM efficiency is shaped by access scheduling and refresh policy. We employ first-come first-served (FCFS) scheduling with a closed-page policy [51]. A layer-interleaved strategy [52] staggers bank operations across layers to overlap activation and column access. Because capacitors leak, periodic refresh is required: the canonical retention window is 64 ms below 85 °C and halves for every 10 °C increase. We use distributed all-bank refresh [53], [54], scheduling refresh commands across banks/layers within the retention interval to minimize visible bandwidth loss.

## C. Processing Element (PE) Architecture

As shown in Fig. 4(d), each PE integrates a five-port router, a high-radix crossbar, a RISC-V controller,  $N_{\rm core}$  compute cores, and  $N_{\rm bank}$  MCs. The router coordinates data movement among PEs and the D2D endpoints; flit width is configurable to meet bandwidth targets. The crossbar provides low-latency connectivity among intra-PE endpoints (cores, MCs, controller). Every DRAM channel terminates at a dedicated MC, enabling independent, parallel accesses. Within each core, a matrix processing unit (MPU) is paired with a lightweight vector processing unit (VPU) that handles common elementwise/normalization kernels (e.g., activations, softmax, LayerNorm/RMSNorm) and participates in reductions, similar to Ascend's vector unit [55]. This consolidation keeps the PE description succinct while preserving the functionality required to sustain the MPU.

# D. MPU Design

Conventional systolic arrays (SAs) with  $SA_{\rm rows} \times SA_{\rm cols}$  cells deliver high throughput for large-batch GEMM by pipelining operand streams [56]. However, utilization collapses for small-batch GEMM—and especially for GEMV in decode (e.g., per-head attention)—because when the effective matrix height  $M < SA_{\rm rows}$ , only a fraction  $M/SA_{\rm rows}$  of rows is active. Elegant prior efforts alleviate this via heterogeneous datapaths (e.g., coupling SAs with MAC trees [37]) or reconfigurable sub-arrays like Planaria [57] and RSA [58]. While effective within their target regimes, these designs misalign with our 3D-DRAM design: (i) they underutilize abundant vertical bandwidth from DRAM channels, (ii) they introduce fine-grained control overheads that bloat area/latency. Consequently, we pursue a simpler, bandwidth-aware alternative.

To this end, we partition a large systolic array (SA) into multiple short—wide **baseSAs** (fewer rows, same columns), as shown in Fig. 4(c). This organization preserves high-throughput GEMM while better matching GEMV: additional baseSAs raise utilization when M is small or K is modest (e.g., 128 per head). Projection and logit layers—dominant decode bottlenecks—thereby see substantial speedups that scale with the number of simultaneously active baseSAs (e.g., input batch size). Each *baseSA* can fetch operands from SRAM or stream them directly from 3D-DRAM through the crossbar; control logic scales along the row dimension, keeping area overhead low. This design enables selective SRAM bypass and DRAM streaming and aligns with our dataflow.

### V. SOFTWARE FRAMEWORK

This section presents our software framework. We begin with the  $D^3$  (direct-dram-delivery) dataflow design intra PE (Sec. V-A), followed by the parallel mapping and scheduling scheme for serving (Sec. V-B). Then, we describe our performance simulator (Sec. V-C) and end with DSE methodology (Sec. V-D).

# A. Intra-PE Dataflow Design

For a general GEMM  $C \leftarrow A \times B + C$  with  $A \in \mathbb{R}^{M \times K}$ ,  $B \in \mathbb{R}^{K \times N}$ ,  $C \in \mathbb{R}^{M \times N}$ , all operands are tiled along (M, N, K)

Fig. 5: (a) Intra-PE data path and executions; (b) representative PP/TP mapping scheme with (TP, PP) = (8, 1) and (4, 2) for prefill and decode, respectively; (c) Timing of operations of one stage executed on PC.

# Algorithm 1 D<sup>3</sup> Intra-PE Dataflow Search

10:

end for

12: **return**  $(T_M^*, T_N^*, T_K^*, RU^*)$

11: end for

```

Require: Tensor sizes M, N, K, SRAM budget S_{\text{buf}}, cost model \mathcal{C}

```

```

1: \mathcal{L}_{\min} \leftarrow \infty, (T_M^*, T_N^*, T_K^*, RU^*) \leftarrow \bot

2: Enumerate candidate tiles \mathcal{T}_M, \mathcal{T}_N, \mathcal{T}_K

3: for (T_M, T_N, T_K) \in \mathcal{T}_M \times \mathcal{T}_N \times \mathcal{T}_K do

4: \mathcal{R} \leftarrow \{\text{IRU} \mid T_M T_K \leq S_{\text{buf}}\} \cup \{\text{WRU} \mid T_N T_K \leq S_{\text{buf}}\} \cup \{\text{ORU} \mid T_M T_N \leq S_{\text{buf}}\} \cup \{\text{ARU} \mid \sum_{\text{cyc}} T_M T_N \leq S_{\text{buf}}\}

5: for \text{RU} \in \mathcal{R} do

6: \ell \leftarrow \mathcal{C}(T_M, T_N, T_K, \text{RU})

7: if \ell < \mathcal{L}_{\min} then

8: \mathcal{L}_{\min} \leftarrow \ell; (T_M^*, T_N^*, T_K^*, RU^*) \leftarrow (T_M, T_N, T_K, \text{RU})

9: end if

```

during calculation. Prior SRAM-centric dataflow typically stage certain tiles in SRAM ( $\boxed{1} \rightarrow \boxed{2}$ ) to maximize operand reuse, with multiply–accumulate operations performed on the MPU and reductions in the VPU ( $\boxed{4} \rightarrow \boxed{5} \rightarrow \boxed{6}$ ) before writing back to DRAM, with the operations ( $\boxed{1}$ - $\boxed{6}$ ) defined in Fig. 5(a). While our D³ dataflow determines flexibly whether an operand tile is temporarily staged in SRAM for reuse ( $\boxed{1} \rightarrow \boxed{2} \rightarrow \boxed{4}$ ) or streamed directly from the stacked DRAM ( $\boxed{1} \rightarrow \boxed{3}$ ) to MPU. This enables direct-DRAM delivery for selected tiles (e.g., model weights) while staging only important

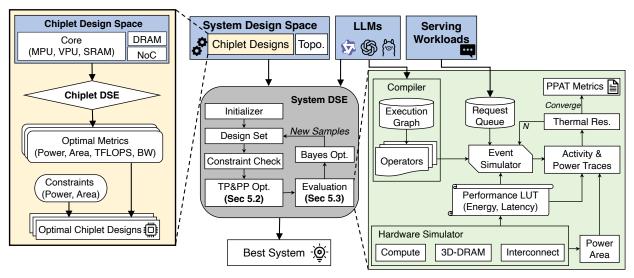

Fig. 6: Overview of our simulation and design framework.

tiles for reuse, reducing SRAM pressure without sacrificing throughput. We classify reuse policies as: (i) IRU (Input-Reuse): stage A-tiles; (ii) WRU (Weight-Reuse): stage Btiles; (iii) **ORU** (Output-Reuse): stage C-tiles/partial outputs; (iv) **ARU** (All-Reuse): stage (A, B, C) tiles simultaneously. A reuse policy is feasible if its SRAM footprint fits  $S_{\text{buf}}$ (e.g., IRU requires  $T_M T_K \leq S_{\mathrm{buf}}$ ). We employ exhaustive exploration rather than the analytical formulations as [8], [10] to identify the globally optimal mapping. The process is shown in Alg. 1: (i) enumerate candidate tile sizes; (ii) for each tiling, find feasible reuse policies R that satisfy the SRAM capacity constraint; (iii) simulate the latency of each pair (tiling, RU) with the simulator in §V-C0b; and (iv) select the best mapping  $(T_M^*, T_N^*, T_K^*, RU^*).$

## B. Serving Optimization

Then we perform serving-related optimization comprises (i) parallel mapping and (ii) dynamic scheduling across PEs/chiplets.

a) Parallel mapping.: Layers are partitioned into pipeline stages for both phases as shown in Fig. 1. We map each stage onto a subset of PEs distributed across chiplets. Within a stage, TP shards a layer across the selected PEs; because inter-PE communication is non-negligible, not every PE should participate in every stage. The assignment space is combinatorial—choosing TP out of  $N_{PE}^{p/d}$  PEs is  $\binom{N_{PE}^{\tilde{p}/d}}{N_{PE}}$  per layer—and further multiplies under PD disaggregation.

We propose to cast the mapping problem as a two-stage optimization. Stage 1 (TP grouping). For a candidate TP, we solve a small integer linear program (MILP) that clusters all PEs into groups of size TP and nominates a center PE per group. The algorithm is shown in Alg. 2. The objective is to minimize (i) intra-group all-reduce cost (approximated by the Manhattan diameter and center-based reductions) and (ii) inter-stage transport cost via center-to-center distance. Stage 2 (solve mapping). Given the TP groups, we assign pipeline stages to groups for both prefill and decode phases using simulated annealing. The objective is to minimize the sum of

# Algorithm 2 TP Grouping via MILP

**Require:** PE coordinates  $\mathcal{P} = \{(x_i, y_i)\}_{i=1}^P$ ; group size TP; weight  $w_{\mathrm{inter}}$  for inter-group costs

**Ensure:** Groups  $\mathcal{G} = \{G_1, \dots, G_K\}$  of size TP and pergroup centers  $(c_k^x, c_k^y)$

- 1:  $K \leftarrow |P/TP| \{ \text{max \#stages (groups)} \}$

- 2: Decision variables:

- $c_{i,k} \in \{0,1\}$  (PE i assigned to group k);  $m_x^k, M_x^k, m_y^k, M_y^k \in \mathbb{Z}$  (group k bounding box);

- 4: Constraints:

- Assignment:  $\sum_{k=1}^{K} c_{i,k} \leq 1, \forall i; \sum_{i=1}^{P} c_{i,k}$ TP,  $\forall k$

- Bounding box (x-dimension; y analogous). Let  $B_x \leftarrow$  $(\max_i x_i - \min_i x_i) + 1,$  $M_x^k \ge x_i - B_x(1 - c_{i,k}),$  $m_x^k \le x_i + B_x(1 - c_{i,k}), \ \forall i, k$

- 7: Centers  $c_k^x = \frac{1}{2}(M_x^k + m_x^k)$ ,  $\forall k$ 8: **Objective:** minimize  $J = \sum_k D_k + w_{\text{inter}} \cdot \sum_{\mathcal{A}} \text{DIST}(k, k+1)$ , For adjacent pairs  $\mathcal{A} = \{(k, k+1) \mid k = 1..K-1\}$

- Span upper bound (proxy for all-reduce cost):  $D_k \ge$

- $(M_x^k m_x^k) + (M_y^k m_y^k), \ \forall k$ Inter-group center distances.  $\mathrm{DIST}(k, k+1) \leftarrow \|c_k^x m_y^k\|_{\mathrm{C}}$  $c_{k+1}^{x} \| + \|c_{k}^{y} - c_{k+1}^{y}\|$ 11: **return**  $(\mathcal{G}, \{(c_{k}^{x}, c_{k}^{y})\}_{k=1}^{K})$

stage latency and inter-layer KV-transfer latency. Figure 5(b) illustrates one outcome ((TP,PP)=(8,1) for prefill and (4,2) for decode), consistent with observations in DistServe [47] that larger TP benefits prefill and deeper PP improves decode throughput. When memory capacity permits, data parallelism (DP) can also be activated to run multiple instances, thus adjusting the PD pool sizes flexibly as SplitWise [33].

b) Dynamic scheduling.: At runtime, we adopt iterationlevel dynamic scheduling in the spirit of ORCA [22], with selective batching for both pre-attention (QKV Proj.) and postattention (O Proj., FFNs). As illustrated in Fig. 5(c), upon receiving activations (Act.), each chiplet multicasts (MC) over the NoC to the first-stage PEs. As soon as QKV Proj. begins, the KV cache is forwarded over the NoC-NoP fabric to the paired decode PEs to hide transport stalls. The attention block (Attn.) and O Proj. follow; O Proj. triggers an all-reduce decomposed into a reduce (RD) and a subsequent multicast (MC). The dynamic scheduler overlaps these collectives with downstream compute to sustain utilization under variable request lengths. Together, the mesh-aware parallel mapping and runtime scheduler constitute our serving optimization.

#### C. System Simulator

Our end-to-end simulator (Fig. 6) integrates three levels: hardware characterization, operator modeling, and system simulation.

- a) Hardware level.: We build parameterized models for 3D-DRAM, PEs, and interconnects to provide area, power, and performance metrics for design exploration. The 3D-DRAM model considers the bank/layer size, timing constraints, and temperature-dependent refresh; PE models capture MPU and VPU pipelines and basic SRAM behaviors. Interconnect models include NoC and NoP delay/energy.

- b) Operator level.: We quantify the latency and energy of compute, memory, and communication operations under the proposed dataflow. For memory, a request of size DATA requires  $N_{\rm cmd} = \frac{DATA}{N_{\rm bank} \cdot N_{\rm lo} \cdot BL}$  commands per MC, assuming balanced distribution [59]. Each command incurs  $t_{\rm mem} = t_{RCD} + t_{CAS} + t_{RP} + BL \cdot N_{\rm cmd}$ , plus TSV delay under a layer-interleaving scheme for full-bus utilization. Refresh overhead is modeled as  $t_{\rm refresh} = \frac{t_{R/W}}{t_{RFI}} \cdot t_{RFC}$ , scaling with temperature. Energy is proportional to command count and refresh commands. For computation, we analytically evaluate cycle counts and MPU utilization following a ScaleSimstyle model [60]; results are stored in a lookup table (LUT) keyed by tensor shape and tiling strategy. For communication, given message size m and hop count h, we model delay as  $t_{\rm comm} = \alpha \cdot m + \beta \cdot h$ , where  $\alpha$  and  $\beta$  are calibrated link/router parameters [40], [43]. Energy scales with m and h.

- c) System level.: We represent batched LLM requests as DAGs of operators. Latency/energy are instantiated from LUT entries, and an event-driven simulator in SimPy [61] produces fine-grained timestamps for SLO evaluation. The simulator generates PE activity traces; combined with leakage models, these yield power traces that feed a thermal solver. Both transient and steady-state analyses are supported (steady state by default). DRAM static power and refresh are iteratively updated with temperature until convergence. We assume liquid cooling with parameters from [62] and employ temperature-aware flow-rate control, which adjusts coolant flow to trade off pumping power and effective thermal resistance.

## D. Design Space Exploration (DSE)

We design a hierarchical DSE framework (Fig. 6) with two stages: *chiplet-level exploration* and *system-level assembly*.

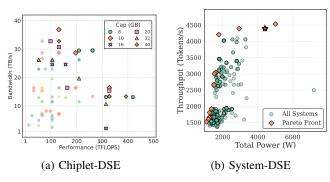

a) Chiplet level.: We sweep DRAM and PE parameters to identify feasible chiplets under area, power, and technology limits. Objectives include peak compute density (TFLOPS), DRAM bandwidth, and capacity. A multi-objective Bayesian Optimization finds Pareto-optimal designs. For each DRAM capacity, Pareto and near-Pareto candidates are selected as inputs to the next stage.

b) System level.: We assemble systems from candidate chiplets and jointly optimize the prefill/decode ratio, TP/PP degrees, placement, and runtime scheduling. We employ a constrained Bayesian-optimization loop (e.g., expected feasible improvement) that (i) initializes PD-balanced seed designs and prunes any violating packaging/technology limits (reticle area, package pins, rack/TDP power); (ii) tunes TP/PP on the two-level mesh (Sec. II-A); in this stage, chiplet placement is also adjusted to obtain a floorplan favorable to parallel mapping; (iii) evaluates each candidate with the event-driven simulator to obtain **PPAT** metrics—Performance (TTFT, TBT, throughput), Power (steady and peak), Area, and Thermal (steady), plus capacity; (iv) filters by SLO and safety constraints (e.g.,  $TTFT \le TTFT_{max}$ ,  $TBT \le TBT_{max}$ ,  $T_{\text{max}} \leq T_{\text{limit}}, P_{\text{peak}} \leq P_{\text{rack}}, \text{ capacity } \geq \text{KV footprint)}$  and picks new samples to maximize throughput-per-watt; and (v) iterates until convergence, returning the optimal system configuration.

This hierarchical framework links hardware-, architecture-, and system-level choices and yields globally optimized solutions for LLM serving.

TABLE II: Chiplet design parameters and value sets.

Distinctive Params. for PD: #105

| Parameters                      | Vals                                     | Parameters         | Vals                       |  |

|---------------------------------|------------------------------------------|--------------------|----------------------------|--|

| DRAM IO Width                   | [32, 64, 128, 256, 512]                  | DRAM Capacity/GB   | [1, 2, 4, 8, 16, 32]       |  |

| DRAM $N_{layer}$                | [1, 2, 3, 4, 5]                          | DRAM banks         | [8, 16, 32, 64, 128]       |  |

| Page Size                       | [1024, 2048, 4096, 8192]                 | Cores              | [1,2,4,8,10,16,24,32]      |  |

| PEs                             | [4, 6, 8, 9, 10, 12, 16, 18, 20, 24, 25] |                    |                            |  |

| Common Params: #10 <sup>5</sup> |                                          |                    |                            |  |

| Parameters                      | Vals                                     | Parameters         | Vals                       |  |

| SRAM banks                      | [4, 8, 16, 32]                           | SRAM capacities/Kb | [64,128,256,512,1024,2048] |  |

| SArows                          | [16, 32, 64, 128]                        | baseSArows         | [1, 2, 4, 8, 16]           |  |

|                                 |                                          |                    |                            |  |

| SAcols                          | [16, 32, 64, 128]                        | Vector registers   | [16, 32, 64, 128]          |  |

## VI. EVALUATION

# A. Experimental Setup

- a) Benchmarks.: We evaluate three dense models—GPT-13B, QwQ-32B, and LLaMA3-70B—adopting MHA or GQA as appropriate. Workloads come from three datasets: (i) Code (mean input/output lengths: 2071/25), production traces from Azure [33]; (ii) Reason (1473/1293), synthesized traces based on the DeepSeek-R1 report [63]; and (iii) LongBench (7108/5), targeting long-context tasks [64]. Each dataset uses a 200-request trace and captures a distinct task regime.

- b) System configurations.: LaMoSys3.5D logic dies use a 7 nm process and run at 800 MHz. Key design parameters appear in Tab. II. HB-related area figures are derived from our tape-out chips [65] and synthesized for 128/256/512/1024 pins. A representative system instantiates  $5 \times PCs$  and  $4 \times DCs$  with the floorplan in Fig. 4. Each PC integrates 16 PEs (16 cores/PE), 32 GB of four-stacked DRAM delivering 10.6 TB/s, and sustains 400 TFLOPS peak compute. Each DC integrates 32 PEs (8 cores/PE), 64 GB of eight-stacked DRAM at 26.2 TB/s, and the same peak compute. Die areas are  $546 \text{ mm}^2$  (PC) and  $584 \text{ mm}^2$  (DC); peak powers are 438 W and 638 W, yielding compute densities of  $\sim 1 \text{ TFLOPS/W}$ . DRAM energy is  $\sim 0.7 \text{ pJ/bit}$ . The intra-chiplet NoC and inter-chiplet die-to-die bandwidths are 200 GB/s and 800 GB/s, respectively.

- c) Baselines.: We compare LaMoSys3.5D against four serving platforms: A100 (six nodes: two prefill, four decode; each node has 4× A100 with 80 GB HBM3, connected by NVLink), TPU (eight nodes: four prefill, four decode; each node has 4× TPUv4 with 32 GB HBM3), LC-L (eight nodes: four prefill, four decode; 4× LC-L per node), and LC-T (eight nodes: four prefill, four decode; 2× LC-T per node). We also compare three 3D-DRAM architectures—(i) TETRIS [8], (ii) 3D-TokSIM [10], and (iii) 3D-LC [28]—using LLMCompass-type dataflows. When certain parameters are missing from the paper, we perform targeted calibration for fair comparison. All designs are normalized to a 7 nm logic process for consistency.

- d) Simulation.: We adapt CACTI-3DD [66] to model 3D-DRAM timing/physical parameters and calibrate against tape-out silicon. Logic components are modeled using a customized NeuroMeter [67] to obtain power/area for MPUs, VPUs, SRAM, and routers; metrics for other blocks (e.g., MC and RV controller) follow [50]. The NoC uses McPAT [68] to model the router and to derive link delays and bandwidth. The leakage model follows the calibrated McPAT [69]. For the NoP, we refer to HISIM studies [70], [71]. Thermal behavior is simulated with modified ATSim [72], with parameters from inhouse chips. Because most public results are architecture-level, we develop an in-house simulator following DistServe [47] and GenZ [73] to evaluate serving performance across all systems, and we search TP/PP settings to obtain the best configuration for each platform.

#### B. Baseline Comparison

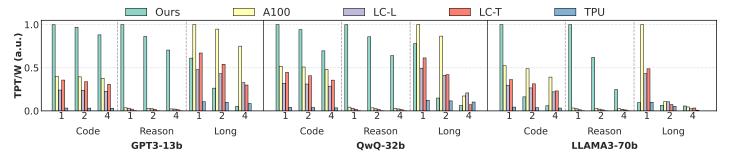

a) Comparison with Inference Systems: We evaluate the optimal LaMoSys3.5D architecture against baselines at request rates of 1, 2, and 4 reg/s. Fig. 7 reports throughput per watt (tokens/s/W), which jointly reflects performance and energy efficiency. Because runtime power for each system is unavailable, we use the published maximum design power for all systems-including ours-and sum over participating chips. LaMoSys3.5D reaches **0.75** tokens/s/W, exceeding A100 (**0.46**), TPUv4 (**0.05**), LC-L (**0.24**), and LC-T (**0.29**). Two factors drive this gain: (i) lower total power, primarily from reduced memory energy and smaller SRAM footprint, while compute efficiency remains comparable to A100 (about 1–1.2 TFLOPS/W); and (ii) higher throughput—LaMoSys3.5D averages 3,466 tokens/s versus 3,370 for A100 and 1,023 for TPUv4. LaMoSvs3.5D also delivers the lowest TBT across workloads, improving by 17× (geomean) over DGX-A100 and 73× over TPUv4. This stems from much higher per-device memory bandwidth (e.g., DC chiplet at 26.2 TB/s vs. A100 at  $\sim$ 2 TB/s) and the  $D^3$  dataflow that exploits 3D-DRAM bandwidth. By contrast, the TPUv4 is simulated following LLMCompass's default dataflow, which may be less efficient for GEMV-dominant decode on large systolic arrays. Prefill is modestly slower: average **TTFT** is  $\sim 2.13 \times A100$  due to fewer compute units. For reference, LC-L, LC-T, and TPUv4 exhibit  $\sim 1.63 \times$ ,  $\sim 2.33 \times$ , and  $\sim 3.63 \times$  A100's **TTFT**, respectively. Except for *LongBench* cases with input length >10,000, **TTFT** stays within typical SLOs (sub-second to a few seconds). For the *Reason* workload with long generations ( $\sim$ 1,300 tokens), TBT gains are even larger.

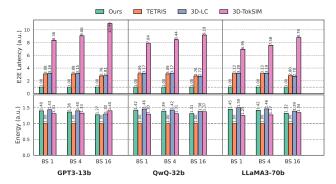

b) Comparison with 3D Architectures: We further compare LaMoSys3.5D with existing 3D-DRAM designs (TETRIS, 3D-LC, 3D-TokSIM). Since these target singletransformer acceleration, we evaluate mean end-to-end latency and energy across multiple models, with input/output lengths ranging from 64 to 8192, and batch sizes  $\{1,4,16\}$  (Fig. 8). Latency. LaMoSys3.5D achieves the lowest E2E latency. Averaged over all settings and normalized to LaMoSys3.5D, the mean latencies are  $2.99 \times$  (TETRIS),  $3.02 \times$  (3D-LC), and  $8.58 \times$  (3D-TokSIM), thanks to the  $D^3$  dataflow and its search over the full mapping space. Energy. TETRIS attains the lowest mean energy due to its DRAM-access-minimizing dataflow. Normalized to TETRIS, the mean energies are  $1.37 \times$ (LaMoSys3.5D),  $1.32\times$  (3D-TokSIM), and  $1.41\times$  (3D-LC). Memory dominates energy across designs, while compute energy is similar.

To conclude, *LaMoSys3.5D* delivers superior system-level throughput and energy efficiency versus inference baselines, and the best single-request latency among 3D designs—driven by high 3D-DRAM bandwidth and effective utilization via our dataflow and parallel mapping design. The results also indicate that thermal headroom is a first-order design constraint in 3.5D-ICs, necessitating the incorporation of power and thermal budgets across diverse workloads.

# C. Performance Analysis

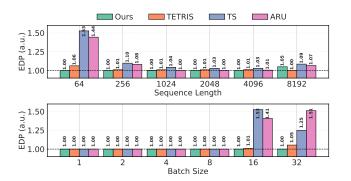

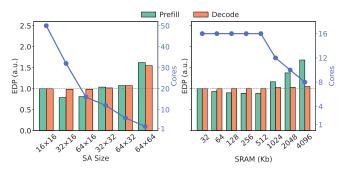

- a) Dataflow.: Fig. 9 compares energy-delay product (EDP) across four dataflows: (i) the proposed  $D^3$ ; (ii) TETRIS [8]; (iii) TS: token-stationary [10]; (iv) ARU: SRAM-reuse-centric. **Prefill**  $D^3$  achieves the lowest EDP; averages relative to  $D^3$  are  $1.01 \times$  (TETRIS),  $1.13 \times$  (TS), and  $1.09 \times$  (ARU). As sequence length grows, the EDP for all DRAM-involved flows converges because computation dominates. Decode EDP of all flows is comparable at small batch sizes. For larger batches (e.g., 16/32), TS and ARU degrade in both latency and energy due to limited SRAM capacity, which increases 3D-DRAM traffic.  $D^3$  sustains low EDP by allocating reuse across 3D-DRAM and SRAM flexibly, thus maintaining high vertical bandwidth utilization. Across regimes,  $D^3$  delivers the best EDP and scales more stably with batch size and sequence length. These results underscore that a single parameterized hardware template can instantiate compute-rich prefill chiplets and bandwidth-/capacity-rich decode chiplets, supporting heterogeneous specialization without sacrificing design coherence.

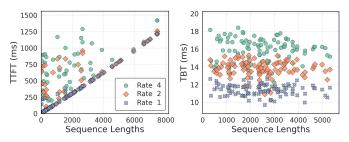

- b) Serving.: Figure 10 shows latency distributions under varying request rates. When rates are low, TTFT matches the ideal values, indicating high utilization (~80%). At higher rates, shorter requests suffer queuing delays behind longer ones, inflating TTFT. To mitigate this issue, techniques such as preemption and chunked prefill [38] can be adopted in the future. For decoding, TBT scales with batch size; longer outputs or higher request rates enlarge decoding batches, thus raising TBT. To optimize throughput while adhering to SLOs, it is advisable to enlarge the batch size without compromising TBT.

Fig. 7: Comparison of inference performance across systems. Labels '1,2,4' in the X axis represent the request rate.

Fig. 8: Comparison across 3D Architectures.

Fig. 9: Comparison of dataflow design.

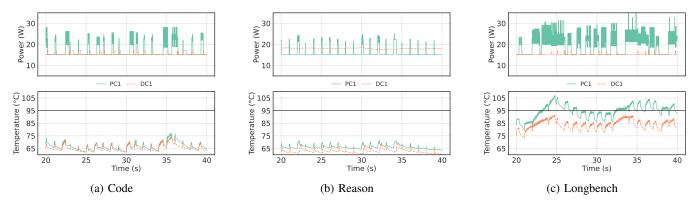

c) Thermals and Power.: We select one PE from a prefill chiplet (PC1) and one from a decode chiplet (DC1) and trace their power and center-point temperature over time under multiple workloads (Fig. 11). All results assume liquid cooling with an ambient temperature of 45 °C. For the PC, irregular input lengths create idle gaps and stalls; power spikes during active intervals and drops when idle, producing rapid

Fig. 10: Serving performance under different request rates.

temperature rises followed by gradual decay between bursts. In contrast, the DC operates nearly continuously with lower compute intensity; power varies less and temperature is more stable. Despite its lower power, the DC can match or exceed the PC's temperature because it integrates eight DRAM layers (vs. four on the PC), lengthening the heat path and increasing effective thermal resistance. Under *Reason* and *Code*, temperatures settle near  $\sim 70\,^{\circ}$ C; with *LongBench*, stronger prefill demand pushes temperatures toward  $\sim 100\,^{\circ}$ C. These results underscore the need for workload-aware, transient thermal evaluation early in architecture design (Sec III-C0c): power and thermal profiles vary sharply across workloads, and nominal or worst-case static assumptions can misestimate bandwidth, latency, and energy.

## D. DSE Analysis

In this subsection, we explore the architecture design space of *LaMoSys3.5D* and summarize several key architectural implications for future design. Since all evaluated models show consistent trends across architectural parameters, we present results for QwQ-32B as a representative case without loss of generality.

a) System design trade-off.: Figure 12(a) shows the performance—bandwidth distribution of chiplets with different capacities, revealing a clear trade-off between these two aspects. This observation validates the rationale in Sec. III: allocating higher bandwidth to decoding while dedicating more compute resources to prefill. After identifying feasible chiplet designs, we proceed to system-level optimization. Results are shown in Figure 12(b). We present throughput and power distributions, where Pareto-optimal designs are highlighted. Notably, power is included as an optimization target, explaining why some designs with large TTFT and TBT remain on the Pareto front. We select the design marked by as the final design choice for its larger memory capacity.

b) Core design.: Fig. 13(a) varies the systolic-array (SA) shape while fixing the number of baseSAs at 8 and holding PE area constant (core count scales accordingly). Smaller columns are preferred because they shrink the SA area and permit more cores per PE. Larger rows improve prefill by raising per-core throughput. Increasing the number of base SAs further boosts performance—most notably for Logit. Attend gains less when the head dimension N is small (e.g., 128) and the sequence length K is large, since partial-sum accumulation dominates. Projection speedups scale primarily with batch size. Fig. 13(b)

Fig. 11: Power and temperature traces for the LaMoSys3.5D running workload 'Code'(a), 'Reason'(b), 'Long'(c).

Fig. 12: DSE results for chiplet (a) and system (b).

Fig. 13: Impact of MPU size and SRAM buffer capacity on prefill and decoding performance.

sweeps per-core SRAM while adjusting core count to keep PE size fixed. Medium SRAM sizes are preferred in both phases:  $D^3$  has limited reliance on large buffer size, and smaller SRAM size reduces core area, enabling more cores per PE. Overall, balancing per-core capability and core count is crucial—over-sized or under-sized compute arrays and SRAM sizes both hurt performance; a balanced SA shape and medium SRAM per core work best.

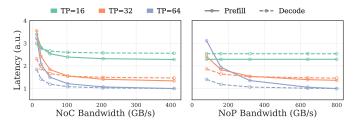

c) Communication design.: We further examine the impact of NoC/NoP bandwidth and parallel strategies on TTFT and TBT. Figure 14(a),(b) present normalized latency results for NoC and NoP, respectively. With sufficient bandwidth, a larger TP is preferred since it reduces per-PE computation. However, under limited bandwidth, a smaller TP is favored due to the high communication overhead of all-reduce. These results highlight the importance of co-optimizing TP and PP (Sec. V-A). Larger TP reduces compute but increases col-

Fig. 14: Impact of NoC/NoP bandwidth and TP strategy on prefill and decoding performance.

Fig. 15: Impact of number of cores and DRAM layers on throughput and temperature.

lective costs; with constrained NoC bandwidth, moderate TP minimizes TTFT. Increasing NoC/NoP bandwidth improves both TTFT and TBT, with TTFT being more sensitive to bandwidth, while a smaller TP is preferred under bandwidth constraints.

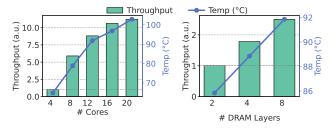

d) PE design.: Finally, we vary the number of cores per PE (for PC) and the number of DRAM layers (for DC). Fig. 15(a) and (b) report the throughput and maximum temperature. Throughput increases as cores/PE grow, but the gain tapers once cores > 16, when  $T_{\rm max}$  exceeds  $95\,^{\circ}{\rm C}$ ; the elevated temperature raises DRAM refresh activity, reducing effective memory bandwidth and throttling performance. Increasing the number of layers consistently improves throughput, and the associated temperature rise is modest. Thus, we recommend preferring more DRAM layers while capping the core count (e.g.,  $\leq 16$ ), as throughput is highly sensitive to tight thermal budgets.

## VII. RELATED WORK

## A. Efficient LLM Inference Serving

LLM inference is optimized at both engine and service layers [74], [56]. Engine-level techniques include graph optimization [75], operator fusion [76], [77], offloading [78], and fast decoding (e.g., speculative decoding) [79], [80]. Service systems focus on memory management [81], batching [22], [82], scheduling [22], [38], and distributed execution [33], [47]; notable systems include vLLM [81] and SGLang [83]. Architectural gains also come from model choices (e.g., GQA [32]) and compression (quantization [84], sparsity [85]). These advances complement our 3.5D-IC design.

# B. PIM- and NMP-based Transformer Accelerators

PIM/NMP architectures exploit internal memory bandwidth and reduce data movement, benefiting LLMs. HBM-PIM targets KV-cache processing in batched inference [86]. Recent designs combine 3D-DRAM with PIMs [87], [88], [89], [90], [91], [92], [10], [29], while 3D-DRAM NMP brings compute near memory [93], [94], [28]. Some target new regimes, e.g., speculative [95] and long-context [96]. Most, however, optimize kernels or edge scenarios rather than end-to-end serving.

### VIII. CONCLUSION

With the growing popularity of inference-time computing, there is an increasing demand for more powerful inference systems. In this work, we present our solution: *LaMoSys3.5D*, the **first 3.5D-IC architecture designed for efficient LLM serving**. We introduce a novel hardware design to optimize both prefill and decode phases and develop a software framework incorporating features such as dataflow and parallel mapping, thermal-aware modeling, and optimization. Across diverse LLMs and workloads, *LaMoSys3.5D* improves throughput-perwatt over DGX-A100 systems by 62% and achieves a 4.87× better end-to-end latency (geo-mean) versus prior 3D designs. It also demonstrates high performance on workloads with long output sequences, 17.0× decode acceleration compared to A100, making it a promising candidate for future inference systems.

#### REFERENCES

- J. Kaplan, S. McCandlish, T. Henighan, T. B. Brown, B. Chess, R. Child, S. Gray, A. Radford, J. Wu, and D. Amodei, "Scaling laws for neural language models," arXiv preprint arXiv:2001.08361, 2020.

- [2] A. Plaat, A. Wong, S. Verberne, J. Broekens, N. van Stein, and T. Back, "Reasoning with large language models, a survey," arXiv preprint arXiv:2407.11511, 2024.

- [3] A. Jaech, A. Kalai, A. Lerer, A. Richardson, A. El-Kishky, A. Low, A. Helyar, A. Madry, A. Beutel, A. Carney et al., "Openai o1 system card," arXiv preprint arXiv:2412.16720, 2024.

- [4] D. Guo, D. Yang, H. Zhang, J. Song, R. Zhang, R. Xu, Q. Zhu, S. Ma, P. Wang, X. Bi et al., "Deepseek-r1: Incentivizing reasoning capability in Ilms via reinforcement learning," arXiv preprint arXiv:2501.12948, 2025.

- [5] Q. Team, "Qwq-32b: Embracing the power of reinforcement learning," Mar. 2025.

- [6] B. Fujun, J. Xiping, W. Song, Y. Bing, T. Jie, Z. Fengguo, W. Chunjuan, W. Fan, L. Xiaodong, Y. Guoqing, F. Ni, L. Qiannan, L. Hua, W. Kexin, D. Huifu, B. Liang, J. Xuerong, L. Jin, L. Mei, W. Zhengwen, H. Sheng, Z. Jun, Z. Qiong, S. Peng, Y. Daohong, C. Kau, D. Yang, C.-S. Ho, S. Hongbin, L. Hangbing, L. Ming, K. Yi, and R. Qiwei, "A stacked embedded dram array for lpddr4/4x using hybrid bonding 3d integration with 34gb/s/1gb 0.88pj/b logic-to-memory interface," in 2020 IEEE International Electron Devices Meeting (IEDM), 2020, pp. 6.6.1–6.6.4.

- [7] S. Wang, X. Jiang, F. Bai, W. Xiao, X. Long, Q. Ren, and Y. Kang, "A true process-heterogeneous stacked embedded dram structure based on wafer-level hybrid bonding," *Electronics*, vol. 12, no. 5, p. 1077, 2023.

- [8] M. Gao, J. Pu, X. Yang, M. Horowitz, and C. Kozyrakis, "Tetris: Scalable and efficient neural network acceleration with 3d memory," in Proceedings of the Twenty-Second International Conference on Architectural Support for Programming Languages and Operating Systems, 2017, pp. 751–764.

- [9] C. Li, Y. Yin, X. Wu, J. Zhu, Z. Gao, D. Niu, Q. Wu, X. Si, Y. Xie, C. Zhang, and G. Sun, "H2-llm: Hardware-dataflow co-exploration for heterogeneous hybrid-bonding-based low-batch llm inference," in Proceedings of the 52nd Annual International Symposium on Computer Architecture, ser. ISCA '25. New York, NY, USA: Association for Computing Machinery, 2025, p. 194–210. [Online]. Available: https://doi.org/10.1145/3695053.3731008

- [10] Z. Wentao, L. Boya, W. Meng, C. Peiyu, Y. Fengyun, M. Yufei, J. Tianyu, H. Ru, and Y. Le, "3d-toksim: Stacking 3d memory with token-stationary compute-in-memory for speculative llm inference," in 2025 62th IEEE Design Automation Conference (DAC). IEEE, 2025, pp. 1–6.

- [11] TSMC, "The cowos®-s (chip on wafer on substrate with silicon interposer) platform," 2025. [Online]. Available: https://3dfabric.tsmc. com/english/dedicatedFoundry/technology/cowos.htm

- [12] C. S. Mandalapu, C. Buch, P. Shah, R. Topacio, P. Cheng, L. Wang, R. Swaminathan, A. Smith, J. Wuu, K. Mysore, and A. Alam, "3.5d advanced packaging enabling heterogenous integration of hpc and ai accelerators," in 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), 2024, pp. 798–802.

- [13] Y. S. Shao, J. Clemons, R. Venkatesan, B. Zimmer, M. Fojtik, N. Jiang, B. Keller, A. Klinefelter, N. Pinckney, P. Raina, S. G. Tell, Y. Zhang, W. J. Dally, J. Emer, C. T. Gray, B. Khailany, and S. W. Keckler, "Simba: Scaling deep-learning inference with multi-chip-module-based architecture," in *Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture*, ser. MICRO '52. New York, NY, USA: Association for Computing Machinery, 2019, p. 14–27. [Online]. Available: https://doi.org/10.1145/3352460.3358302

- [14] Y. Chen, V. Sankatali, S. Mishra, J. Ryckaert, J. Myers, and D. Biswas, "Thermal implications in scaling high-performance server 3d chiplet-based 2.5d soc from finfet to nanosheet," in 2024 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2024, pp. 45–50.

- [15] S. Pandey and P. R. Panda, "Neurotap: Thermal and memory access pattern-aware data mapping on 3d dram for maximizing dnn performance," ACM Trans. Embed. Comput. Syst., vol. 23, no. 6, Sep. 2024. [Online]. Available: https://doi.org/10.1145/3677178

- [16] L. Siddhu, R. Kedia, and P. R. Panda, "Leakage-aware dynamic thermal management of 3d memories," ACM Trans. Des. Autom. Electron. Syst., vol. 26, no. 2, Oct. 2020. [Online]. Available: https://doi.org/10.1145/3419468

- [17] A. Vaswani, N. Shazeer, N. Parmar, J. Uszkoreit, L. Jones, A. N. Gomez, Ł. Kaiser, and I. Polosukhin, "Attention is all you need," *Advances in neural information processing systems*, vol. 30, 2017.

- [18] P. Ramachandran, B. Zoph, and Q. V. Le, "Swish: a self-gated activation function," arXiv preprint arXiv:1710.05941, vol. 7, no. 1, p. 5, 2017.

- [19] J. Achiam, S. Adler, S. Agarwal, L. Ahmad, I. Akkaya, F. L. Aleman, D. Almeida, J. Altenschmidt, S. Altman, S. Anadkat et al., "Gpt-4 technical report," arXiv preprint arXiv:2303.08774, 2023.

- [20] A. Dubey, A. Jauhri, A. Pandey, A. Kadian, A. Al-Dahle, A. Letman, A. Mathur, A. Schelten, A. Yang, A. Fan et al., "The llama 3 herd of models," arXiv preprint arXiv:2407.21783, 2024.

- [21] A. Liu, B. Feng, B. Xue, B. Wang, B. Wu, C. Lu, C. Zhao, C. Deng, C. Zhang, C. Ruan et al., "Deepseek-v3 technical report," arXiv preprint arXiv:2412.19437, 2024.

- [22] G.-I. Yu, J. S. Jeong, G.-W. Kim, S. Kim, and B.-G. Chun, "Orca: A distributed serving system for transformer-based generative models," in 16th USENIX Symposium on Operating Systems Design and Implementation (OSDI 22), 2022, pp. 521–538.

- [23] M. Shoeybi, M. Patwary, R. Puri, P. LeGresley, J. Casper, and B. Catanzaro, "Megatron-lm: Training multi-billion parameter language models using model parallelism," arXiv preprint arXiv:1909.08053, 2019.

- [24] S. Wang, B. Yu, W. Xiao, F. Bai, X. Long, L. Bai, X. Jia, F. Zuo, J. Tan, Y. Guo, P. Sun, J. Zhou, Q. Zhan, S. Hu, Y. Zhou, Y. Kang, Q. Ren, and X. Jiang, "A 135 gbps/gbit 0.66 pj/bit stacked embedded dram with multilayer arrays by fine pitch hybrid bonding and mini-tsv," in 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2023, pp. 1–2.

- [25] R. Agarwal, P. Cheng, P. Shah, B. Wilkerson, R. Swaminathan, J. Wuu, and C. Mandalapu, "3d packaging for heterogeneous integration," in 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC). IEEE, 2022, pp. 1103–1107.

[26] A. Smith, E. Chapman, C. Patel, R. Swaminathan, J. Wuu, T. Huang,

- [26] A. Smith, E. Chapman, C. Patel, R. Swaminathan, J. Wuu, T. Huang, W. Jung, A. Kaganov, H. McIntyre, and R. Mangaser, "11.1 amd instincttm mi300 series modular chiplet package–hpc and ai accelerator for exa-class systems," in 2024 IEEE International Solid-State Circuits Conference (ISSCC), vol. 67. IEEE, 2024, pp. 490–492.

- [27] S. Naffziger, N. Beck, T. Burd, K. Lepak, G. H. Loh, M. Subramony, and S. White, "Pioneering chiplet technology and design for the amd epyc™ and ryzen™ processor families: Industrial product," in 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2021, pp. 57–70.

- [28] J. Sharda, P.-K. Hsu, and S. Yu, "Accelerator design using 3d stacked capacitorless dram for large language models," in 2024 IEEE 6th International Conference on AI Circuits and Systems (AICAS). IEEE, 2024, pp. 487–491.

- [29] J. Wang, M. Ge, B. Ding, Q. Xu, S. Chen, and Y. Kang, "Nicepim: Design space exploration for processing-in-memory dnn accelerators with 3-d stacked-dram," *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, vol. 43, no. 5, pp. 1456–1469, 2024.

- [30] J. Bai, S. Bai, Y. Chu, Z. Cui, K. Dang, X. Deng, Y. Fan, W. Ge, Y. Han, F. Huang et al., "Qwen technical report," arXiv preprint arXiv:2309.16609, 2023.

- [31] A. Yang, B. Yu, C. Li, D. Liu, F. Huang, H. Huang, J. Jiang, J. Tu, J. Zhang, J. Zhou et al., "Qwen2. 5-1m technical report," arXiv preprint arXiv:2501.15383, 2025.

- [32] J. Ainslie, J. Lee-Thorp, M. De Jong, Y. Zemlyanskiy, F. Lebrón, and S. Sanghai, "Gqa: Training generalized multi-query transformer models from multi-head checkpoints," arXiv preprint arXiv:2305.13245, 2023.

- [33] P. Patel, E. Choukse, C. Zhang, A. Shah, Í. Goiri, S. Maleki, and R. Bianchini, "Splitwise: Efficient generative Ilm inference using phase splitting," in 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA). IEEE, 2024, pp. 118–132.

- [34] Z. Yu, S. Liang, T. Ma, Y. Cai, Z. Nan, D. Huang, X. Song, Y. Hao, J. Zhang, T. Zhi, Y. Zhao, Z. Du, X. Hu, Q. Guo, and T. Chen, "Cambricon-llm: A chiplet-based hybrid architecture for on-device inference of 70b llm," 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 1474–1488, 2024. [Online]. Available: https://api.semanticscholar.org/CorpusID:272832035

- [35] Y. Gu, A. Khadem, S. Umesh, N. Liang, X. Servot, O. Mutlu, R. Iyer, and R. Das, "Pim is all you need: A cxl-enabled gpu-free system for large language model inference," in *Proceedings of the 30th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2*, ser. ASPLOS '25, 2025, p. 862–881.

- [36] Z. Zhu, H. Li, W. Ren, M. Wu, L. Ye, R. Huang, and T. Jia, "Leveraging compute-in-memory for efficient generative model inference in tpus," arXiv preprint arXiv:2503.00461, 2025.

- [37] J. Kim, H. Lee, G. Ko, G. Choi, S. Ham, S. Hong, and J.-Y. Kim, "Ador: A design exploration framework for llm serving with enhanced latency and throughput," arXiv preprint arXiv:2503.04253, 2025.

- [38] A. Agrawal, N. Kedia, A. Panwar, J. Mohan, N. Kwatra, B. Gulavani, A. Tumanov, and R. Ramjee, "Taming throughput-latency tradeoff in Ilm inference with sarathi-serve," in 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI 24), 2024, pp. 117–134.

- [39] C. Hu, H. Huang, L. Xu, X. Chen, J. Xu, S. Chen, H. Feng, C. Wang, S. Wang, Y. Bao, N. Sun, and Y. Shan, "Inference without interference: Disaggregate Ilm inference for mixed downstream workloads," arXiv preprint arXiv:2401.11181, 2024.

- [40] H. Zhang, A. Ning, R. B. Prabhakar, and D. Wentzlaff, "Llmcompass: Enabling efficient hardware design for large language model inference," in 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA). IEEE, 2024, pp. 1080–1096.

- [41] G. Singh and S. Vrudhula, "A dram-based near-memory architecture for accelerated and energy-efficient execution of transformers," in *Proceedings of the Great Lakes Symposium on VLSI 2024*, 2024, pp. 57–62.

- [42] J. Cai, Z. Wu, S. Peng, Y. Wei, Z. Tan, G. Shi, M. Gao, and K. Ma, "Gemini: Mapping and architecture co-exploration for large-scale dnn chiplet accelerators," in 2024 IEEE International Symposium on High-

- Performance Computer Architecture (HPCA). IEEE, 2024, pp. 156–171

- [43] J. Fang, H. Wang, Q. Yang, D. Kong, X. Dai, J. Deng, Y. Hu, and S. Yin, "Palm: A efficient performance simulator for tiled accelerators with large-scale model training," arXiv preprint arXiv:2406.03868, 2024.

- [44] W. Zhiqiang, D. Rui, Y. Rihong, K. S. Salvinder Singh, W. Shaofeng, and C. Chenxu, "A review of thermal performance of 3d stacked chips," *International Journal of Heat and Mass Transfer*, 2024.

- [45] Q. Wang, X. Li, T. Jia, Y. Lin, R. Wang, and R. Huang, "Atplace2.5d: Analytical thermal-aware chiplet placement framework for large-scale 2.5d-ic," in 2024 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). IEEE, 2024, pp. 1–8.

- [46] S. S. Salvi and A. Jain, "A review of recent research on heat transfer in three-dimensional integrated circuits (3-d ics)," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 11, no. 5, pp. 802–821, 2021.

- [47] Y. Zhong, S. Liu, J. Chen, J. Hu, Y. Zhu, X. Liu, X. Jin, and H. Zhang, "Distserve: Disaggregating prefill and decoding for goodputoptimized large language model serving," in 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI 24), 2024, pp. 193–210.

- [48] G. Krishnan, S. K. Mandal, M. Pannala, C. Chakrabarti, J.-S. Seo, U. Y. Ogras, and Y. Cao, "Siam: Chiplet-based scalable in-memory acceleration with mesh for deep neural networks," ACM Trans. Embed. Comput. Syst., vol. 20, no. 5s, Sep. 2021. [Online]. Available: https://doi.org/10.1145/3476999

- [49] W. Tang, S.-G. Cho, T. T. Hoang, J. Botimer, W. Q. Zhu, C.-C. Chang, C.-H. Lu, J. Zhu, Y. Tao, T. Wei, N. K. Motwani, M. Yalamanchi, R. Yarlagadda, S. Kale, M. Flanigan, A. Chan, T. Tran, S. Shumarayev, and Z. Zhang, "Arvon: A heterogeneous sip integrating a 14nm fpga and two 22nm 1.8tflops/w dsps with 1.7tbps/mm2 aib 2.0 interface to provide versatile workload acceleration," in 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2023, pp. 1–2.

- [50] Z. Chen, L. Liang, Q. Liu, Z. Li, F. Zhang, Y. Lu, and Z. Gu, "A high-throughput private inference engine based on 3d stacked memory," in *Proceedings of the 61st ACM/IEEE Design Automation Conference*, 2024, pp. 1–6.

- [51] S. Li, D. Reddy, and B. Jacob, "A performance & power comparison of modern high-speed dram architectures," in *Proceedings of the Interna*tional Symposium on Memory Systems, 2018, pp. 341–353.

- [52] Q. Zhu, B. Akin, H. E. Sumbul, F. Sadi, J. C. Hoe, L. Pileggi, and F. Franchetti, "A 3d-stacked logic-in-memory accelerator for applicationspecific data intensive computing," in 2013 IEEE international 3D systems integration conference (3DIC). IEEE, 2013, pp. 1–7.

- [53] JEDEC Solid State Technology Association, JEDEC Standard No. JESD79-4: DDR4 SDRAM Specification, JEDEC Standard, 2013. [Online]. Available: https://www.jedec.org/standards-documents/docs/jesd79-4

- [54] I. G. Thakkar and S. Pasricha, "Massed refresh: An energy-efficient technique to reduce refresh overhead in hybrid memory cube architectures," in 2016 29th International Conference on VLSI Design and 2016 15th International Conference on Embedded Systems (VLSID). IEEE, 2016, pp. 104–109.

- [55] H. Liao, J. Tu, J. Xia, H. Liu, X. Zhou, H. Yuan, and Y. Hu, "Ascend: a scalable and unified architecture for ubiquitous deep neural network computing: Industry track paper," in 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2021, pp. 789–801.

- [56] S. Kim, C. Hooper, T. Wattanawong, M. Kang, R. Yan, H. Genc, G. Dinh, Q. Huang, K. Keutzer, M. W. Mahoney, Y. S. Shao, and A. Gholami, "Full stack optimization of transformer inference: a survey," 2023. [Online]. Available: https://arxiv.org/abs/2302.14017

- [57] S. Ghodrati, B. H. Ahn, J. Kyung Kim, S. Kinzer, B. R. Yatham, N. Alla, H. Sharma, M. Alian, E. Ebrahimi, N. S. Kim, C. Young, and H. Esmaeilzadeh, "Planaria: Dynamic architecture fission for spatial multi-tenant acceleration of deep neural networks," in 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), 2020, pp. 681–697.

- [58] T. Tang, Hardware Modeling and Efficient Architectural Exploration for Machine Learning Accelerators. University of California, Santa Barbara, 2022.

- [59] S. Poddar, "Power modeling and analysis of exascale systems," 2016.

- [60] A. Samajdar, Y. Zhu, P. Whatmough, M. Mattina, and T. Krishna, "Scale-sim: Systolic cnn accelerator simulator," 2019. [Online]. Available: https://arxiv.org/abs/1811.02883

- [61] A. Meurer, C. P. Smith, M. Paprocki, O. Čertík, S. B. Kirpichev, M. Rocklin, A. Kumar, S. Ivanov, J. K. Moore, S. Singh, T. Rathnayake, S. Vig, B. E. Granger, R. P. Muller, F. Bonazzi, H. Gupta, S. Vats, F. Johansson, F. Pedregosa, M. J. Curry, A. R. Terrel, v. Roučka, A. Saboo, I. Fernando, S. Kulal, R. Cimrman, and A. Scopatz, "Sympy: symbolic computing in python," *PeerJ Computer Science*, vol. 3, p. e103, Jan. 2017. [Online]. Available: https://doi.org/10.7717/peerj-cs.103

- [62] D. Shin, J. Kim, N. Chang, J. Choi, S. W. Chung, and E.-Y. Chung, "Energy-optimal dynamic thermal management for green computing," in 2009 IEEE/ACM International Conference on Computer-Aided Design - Digest of Technical Papers, 2009, pp. 652–657.

- [63] DeepSeek. (2025) Overview of deepseek-v3 / r1 reasoning system. [Online]. Available: https://zhuanlan.zhihu.com/p/27181462601

- [64] Y. Bai, X. Lv, J. Zhang, H. Lyu, J. Tang, Z. Huang, Z. Du, X. Liu, A. Zeng, L. Hou et al., "Longbench: A bilingual, multitask benchmark for long context understanding," arXiv preprint arXiv:2308.14508, 2023.

- [65] D. Niu, S. Li, Y. Wang, W. Han, Z. Zhang, Y. Guan, T. Guan, F. Sun, F. Xue, L. Duan, Y. Fang, H. Zheng, X. Jiang, S. Wang, F. Zuo, Y. Wang, B. Yu, Q. Ren, and Y. Xie, "184qps/w 64mb/mm23d logic-to-dram hybrid bonding with process-near-memory engine for recommendation system," in 2022 IEEE International Solid-State Circuits Conference (ISSCC), vol. 65, 2022, pp. 1–3.

- [66] K. Chen, S. Li, N. Muralimanohar, J. H. Ahn, J. B. Brockman, and N. P. Jouppi, "Cacti-3dd: Architecture-level modeling for 3d die-stacked dram main memory," in 2012 Design, Automation & Test in Europe Conference Exhibition (DATE), 2012, pp. 33–38.

- [67] T. Tang, S. Li, L. Nai, N. Jouppi, and Y. Xie, "Neurometer: An integrated power, area, and timing modeling framework for machine learning accelerators industry track paper," in 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2021, pp. 841–853.

- [68] S. Li, J. H. Ahn, R. D. Strong, J. B. Brockman, D. M. Tullsen, and N. P. Jouppi, "Mcpat: An integrated power, area, and timing modeling framework for multicore and manycore architectures," in 2009 42nd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), 2009, pp. 469–480.

- [69] J. Zhai, C. Bai, B. Zhu, Y. Cai, Q. Zhou, and B. Yu, "Mcpat-calib: A risc-v boom microarchitecture power modeling framework," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 1, pp. 243–256, 2023.

- [70] Z. Wang, P. S. Nalla, J. Sun, A. A. Goksoy, S. K. Mandal, J.-s. Seo, V. A. Chhabria, J. Zhang, C. Chakrabarti, U. Y. Ogras, and Y. Cao, "Hisim: Analytical performance modeling and design space exploration of 2.5d/3d integration for ai computing," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, pp. 1–1, 2025.

- [71] CHIPS Alliance, "AIB Specification Repository," https://github.com/ chipsalliance/AIB-specification/tree/master, 2022.

- [72] Q. Wang, T. Zhu, Y. Lin, R. Wang, and R. Huang, "Atsim3.5d: A multiscale thermal simulator for 3.5d-ic systems based on nonlinear multigrid method," in 2025 3rd International Symposium of Electronics Design Automation (ISEDA). IEEE, 2025.

- [73] C. S. Xia, Y. Deng, S. Dunn, and L. Zhang, "Agentless: Demystifying Ilm-based software engineering agents," arXiv preprint arXiv:2407.01489, 2024.

- [74] Z. Zhou, X. Ning, K. Hong, T. Fu, J. Xu, S. Li, Y. Lou, L. Wang, Z. Yuan, X. Li et al., "A survey on efficient inference for large language models," arXiv preprint arXiv:2404.14294, 2024.

- [75] T. Dao, "Flashattention-2: Faster attention with better parallelism and work partitioning," arXiv preprint arXiv:2307.08691, 2023.

- [76] T. Dao, D. Fu, S. Ermon, A. Rudra, and C. Ré, "Flashattention: Fast and memory-efficient exact attention with io-awareness," *Advances in neural* information processing systems, vol. 35, pp. 16344–16359, 2022.

- [77] K. Hong, G. Dai, J. Xu, Q. Mao, X. Li, J. Liu, K. Chen, Y. Dong, and Y. Wang, "Flashdecoding++: Faster large language model inference on gpus," arXiv preprint arXiv:2311.01282, 2023.

- [78] Y. Sheng, L. Zheng, B. Yuan, Z. Li, M. Ryabinin, B. Chen, P. Liang, C. Ré, I. Stoica, and C. Zhang, "Flexgen: High-throughput generative inference of large language models with a single gpu," in *International Conference on Machine Learning*. PMLR, 2023, pp. 31094–31116.

- [79] Y. Leviathan, M. Kalman, and Y. Matias, "Fast inference from transformers via speculative decoding," in *International Conference on Machine Learning*. PMLR, 2023, pp. 19274–19286.

- [80] T. Cai, Y. Li, Z. Geng, H. Peng, J. D. Lee, D. Chen, and T. Dao, "Medusa: Simple Ilm inference acceleration framework with multiple decoding heads," arXiv preprint arXiv:2401.10774, 2024.

- [81] W. Kwon, Z. Li, S. Zhuang, Y. Sheng, L. Zheng, C. H. Yu, J. E. Gonzalez, H. Zhang, and I. Stoica, "Efficient memory management for large language model serving with pagedattention," in *Proceedings of the ACM SIGOPS 29th Symposium on Operating Systems Principles*, 2023.

- [82] A. Agrawal, A. Panwar, J. Mohan, N. Kwatra, B. S. Gulavani, and R. Ramjee, "Sarathi: Efficient Ilm inference by piggybacking decodes with chunked prefills," arXiv preprint arXiv:2308.16369, 2023.

- [83] L. Zheng, L. Yin, Z. Xie, C. Sun, J. Huang, C. H. Yu, S. Cao, C. Kozyrakis, I. Stoica, J. E. Gonzalez, C. Barrett, and Y. Sheng, "Sglang: Efficient execution of structured language model programs," 2024. [Online]. Available: https://arxiv.org/abs/2312.07104

- [84] E. Frantar, S. Ashkboos, T. Hoefler, and D. Alistarh, "Gptq: Accurate post-training quantization for generative pre-trained transformers," arXiv preprint arXiv:2210.17323, 2022.

- [85] X. Ma, G. Fang, and X. Wang, "Llm-pruner: On the structural pruning of large language models," *Advances in neural information processing* systems, vol. 36, pp. 21702–21720, 2023.

- [86] J. Choi, J. Park, K. Kyung, N. S. Kim, and J. H. Ahn, "Unleashing the potential of pim: Accelerating large batched inference of transformerbased generative models," *IEEE Computer Architecture Letters*, vol. 22, no. 2, pp. 113–116, 2023.

- [87] M. Zhou, W. Xu, J. Kang, and T. Rosing, "Transpim: A memory-based acceleration via software-hardware co-design for transformer," in 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, 2022, pp. 1071–1085.

- [88] G. Heo, S. Lee, J. Cho, H. Choi, S. Lee, H. Ham, G. Kim, D. Mahajan, and J. Park, "Neupims: Npu-pim heterogeneous acceleration for batched llm inferencing," in *Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3*, 2024, pp. 722–737.

- [89] Y. Ding, C. Liu, M. Duan, W. Chang, K. Li, and K. Li, "Haima: A hybrid sram and dram accelerator-in-memory architecture for transformer," in 2023 60th ACM/IEEE Design Automation Conference (DAC). IEEE, 2023, pp. 1–6.

- [90] M. Seo, X. T. Nguyen, S. J. Hwang, Y. Kwon, G. Kim, C. Park, I. Kim, J. Park, J. Kim, W. Shin et al., "Ianus: Integrated accelerator based on npu-pim unified memory system," in Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3, 2024, pp. 545–560.

- [91] J. Park, J. Choi, K. Kyung, M. J. Kim, Y. Kwon, N. S. Kim, and J. H. Ahn, "Attacc! unleashing the power of pim for batched transformer-based generative model inference," in *Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume* 2, 2024, pp. 103–119.

- [92] Y. Luo and S. Yu, "H3d-transformer: A heterogeneous 3d (h3d) computing platform for transformer model acceleration on edge devices," ACM Trans. Des. Autom. Electron. Syst., vol. 29, no. 3, 2024. [Online]. Available: https://doi.org/10.1145/3649219

- [93] H. Sharma, P. Dhingra, J. Doppa, U. Ogras, and P. P. Pande, "A heterogeneous chiplet architecture for accelerating end-to-end transformer models," ACM Transactions on Design Automation of Electronic Systems, 2023.

- [94] T. Kim, K. Choi, Y. Cho, J. Cho, H.-J. Lee, and J. Sim, "Monde: Mixture of near-data experts for large-scale sparse models," in *Proceedings of* the 61st ACM/IEEE Design Automation Conference, 2024, pp. 1–6.

- [95] C. Li, Z. Zhou, S. Zheng, J. Zhang, Y. Liang, and G. Sun, "Specpim: Accelerating speculative inference on pim-enabled system via architecture-dataflow co-exploration," in *Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3*, 2024, pp. 950–965.

- [96] H. Kwon, K. Koo, J. Kim, W. Lee, M. Lee, H. Lee, Y. Jung, J. Park, Y. Song, B. Yang et al., "Lol-pim: Long-context llm decoding with scalable dram-pim system," arXiv preprint arXiv:2412.20166, 2024.