# NysX: An Accurate and Energy-Efficient FPGA Accelerator for Hyperdimensional Graph Classification at the Edge

Jebacyril Arockiaraj arockiar@usc.edu University of Southern California Los Angeles, USA Dhruv Parikh dhruvash@usc.edu University of Southern California Los Angeles, USA

Viktor Prasanna prasanna@usc.edu University of Southern California Los Angeles, USA

### **Abstract**

Real-time, energy-efficient inference on edge devices is essential for graph classification across a range of applications. Hyperdimensional Computing (HDC) is a brain-inspired computing paradigm that encodes input features into low-precision, high-dimensional vectors with simple element-wise operations, making it well-suited for resource-constrained edge platforms. Recent work enhances HDC accuracy for graph classification via Nyström kernel approximations. Edge acceleration of such methods faces several challenges: (i) redundancy among (landmark) samples selected via uniform sampling, (ii) storing the Nyström projection matrix under limited on-chip memory, (iii) expensive, contention-prone codebook lookups, and (iv) load imbalance due to irregular sparsity in SpMV.

To address these challenges, we propose NysX, the first endto-end FPGA accelerator for Nyström-based HDC graph classification at the edge. NysX integrates four key optimizations: (i) a hybrid landmark selection strategy combining uniform sampling with determinantal point processes (DPPs) to reduce redundancy while *improving* accuracy; (ii) a streaming architecture for Nyström projection matrix maximizing external memory bandwidth utilization; (iii) a minimal-perfect-hash lookup engine enabling O(1)key-to-index mapping with low on-chip memory overhead; and (iv) sparsity-aware SpMV engines with static load balancing. Together, these innovations enable real-time, energy-efficient inference on resource-constrained platforms. Implemented on an AMD Zyng UltraScale+ (ZCU104) FPGA, NysX achieves 6.85× (4.32×) speedup and 169× (314×) energy efficiency gains over optimized CPU (GPU) baselines, while improving classification accuracy by 3.4% on average across TUDataset benchmarks, a widely used standard for graph classification.

### **CCS** Concepts

• Hardware  $\rightarrow$  Hardware accelerators; • Computer systems organization  $\rightarrow$  Parallel architectures; • Computing methodologies  $\rightarrow$  Machine learning.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

\*\*Conference'17, Washington, DC, USA, 1

# **Keywords**

Hyperdimensional computing, Graph classification, FPGA acceleration, Edge intelligence, Sparse computation

#### **ACM Reference Format:**

#### 1 Introduction

Graphs are a natural representation for capturing relationships between entities in diverse domains such as bioinformatics [5], chemistry [54], cybersecurity [17], and social network analysis [61]. Unlike Euclidean data such as images or sequences, graphs exhibit irregular structure and variable size, making them difficult to process using conventional machine learning techniques. As a result, graph classification has emerged as a critical task and has received significant attention from the scientific community in recent years [14]. At the same time, there is a growing demand to bring such capabilities onto the edge, where real-time decisions and limited energy budgets impose additional constraints [50, 65].

Graph Neural Networks (GNNs) are a class of models that extend deep learning to graphs through techniques such as iterative message passing and neighborhood aggregation, achieving high accuracy in tasks such as graph classification. However, they incur significant computational and energy costs, making them less suitable for resource-constrained edge devices [31].

Hyperdimensional Computing (HDC) [22] is a brain-inspired computing paradigm that represents information using low-precision vectors, often comprising thousands of dimensions. This representation provides inherent robustness to noise. Unlike deep neural networks, HDC does not require complex iterative training and often generalizes well with minimal data and computation, enabling successful applications across biosignal analysis, image classification, cybersecurity, and natural language understanding [10, 15, 18, 26, 27, 34, 40, 66]. The lightweight, low complexity operations make HDC a compelling alternative to deep learning for low-power, real-time, and edge inference [24, 63].

A key step in HDC is feature encoding, which converts raw input features into hypervectors (HVs). Prior works have focused on encoding-based optimizations for accuracy [56, 62]. Early graph-focused efforts [43] primarily captured graph topology and overlooked node labels or attributes, limiting expressiveness. Recent work [64] addresses this by enabling arbitrary kernel functions in the encoding stage, allowing HDC to capture complex, nonlinear graph structures. During training, a representative set of graphs

(landmarks) is selected to construct a codebook from their node features. During inference, given an input graph with adjacency matrix and node features, the model performs multi-hop propagation, generates integer codes for each node, hashes them into the codebook, and updates the query graph histogram. The histogram is then compared against landmark histograms to form a kernel score, which is projected via Nyström projection matrix into an HV for final classification.

By incorporating kernel methods into HDC encoding [64], the accuracy gap of HDC with GNN-based models for graph classification is significantly reduced. Despite the advantages, applying this method at the edge raises several non-trivial challenges. First, general-purpose CPUs and GPUs are throughput-oriented and optimized for large-batch workloads, leading to poor utilization and high energy cost per query in edge inference. Second, the effectiveness of the Nyström method heavily depends on the diversity and number of landmark samples. The landmark count directly dictates the computational cost of kernel evaluations during inference and the associated memory footprint, which becomes a bottleneck on edge devices with limited on-chip memory. Third, the inherent sparsity in the propagation kernel evaluation results in redundant operations, irregular memory access, and load imbalance across compute units. Fourth, the code-to-index lookup requires accessing hop-specific codebooks; these accesses are irregular and, when executed concurrently, they contend for memory access, making them computationally expensive and difficult to parallelize.

FPGAs are particularly well-suited for HDC inference as they can exploit fine-grained parallelism, mitigate irregular sparsity, and implement customized data paths with banked memory access. In this paper, we present the first FPGA accelerator for HDC-based graph classification, delivering real-time inference for edge deployment.

The key contributions of this work are:

- We propose a novel sampling method that combines uniform sampling with DPP to reduce the number of redundant landmarks while preserving diversity, reducing kernel evaluation overhead and memory footprint, while *improving* accuracy.

- Guided by our roofline analysis, we develop a streaming architecture that maximizes external memory bandwidth utilization by issuing contiguous reads matching the memoryinterface width and overlapping fetch and compute via a FIFO.

- We design a minimal-perfect-hash engine that maps computed codes (keys) to query histogram indices in O(1) time, enabling parallel histogram updates with negligible on-chip memory overhead.

- We design SpMV processing elements (PEs) that exploit the sparsity in adjacency and landmark histogram matrices, reducing memory footprint and energy consumption. We employ a static load-balancing mechanism that partitions rows across processing elements (PEs) to reduce the load imbalance introduced by irregular sparsity.

- Beyond the individual optimizations, we integrate them into NysX, the first end-to-end FPGA accelerator for Nyströmbased HDC graph classification at the edge, delivering realtime inference under tight memory and energy budgets.

We implement our design on the AMD Zynq FPGA and evaluate it across benchmark datasets from TUDataset, a widely used standard for graph classification tasks. Our accelerator achieves 6.85× (4.32×) speedup and 169× (314×) energy efficiency over CPU (GPU) baselines, while improving classification accuracy by up to 3.4%, on average.

## 2 Preliminaries

# 2.1 Background

- 2.1.1 Hyperdimensional Computing (HDC) Hyperdimensional Computing (HDC) is a brain-inspired paradigm that represents information as high-dimensional vectors, or hypervectors (HVs), typically with dimensionality  $d \sim 10^4$  [22, 28]. HVs are low-precision; in this work we assume bipolar HVs  $\mathbf{h} \in \{-1, +1\}^d$ . Representation learning in HDC utilizes a small set of inexpensive, element-wise operations, and noise-robust computations well-suited for hardware acceleration [19, 25]:

- Bundling (⊕): element-wise addition and thresholding, e.g.,

h = sign(h<sub>1</sub> + h<sub>2</sub>), to combine HVs while preserving similarity.

- Binding (⊗): element-wise multiplication, h = h<sub>1</sub> ⊙ h<sub>2</sub>, to produce dissimilar HVs for encoding associations [45].

- **Permutation** ( $\rho$ ): cyclic shift,  $\rho^i(\mathbf{h}) = [h_{(j+i) \mod d}]_{j=0}^{d-1}$ , to encode position or sequence information [21].

An HDC classifier stores *class prototypes* as bundled HVs of training samples belonging to the same class. During inference, a query HV is compared against prototypes using a similarity metric, and the class with maximum similarity is predicted. HDC thus provides single-pass training [16], and hardware-friendly bit-level parallelism, making it attractive for edge-deployed learning systems [23, 49].

- 2.1.2 Nyström Encoding for HDC Conventional HDC encodings rely on random projections [46, 53], which fail to capture complex data similarity. The Nyström method [30, 58] provides a principled approach to approximate a positive semi-definite kernel  $K(\cdot, \cdot)$  using a small set of  $s \ll n$  landmark samples drawn from the training data of size *n*. This enables HDC to incorporate rich kernel-based similarity functions, significantly improving classification accuracy across tasks [64]. Let  $Z = \{z_1, \dots, z_s\} \subset \mathcal{D}$  denote the landmark set,  $\mathbf{H}_Z \in \mathbb{R}^{s \times s}$  the landmark kernel with  $(\mathbf{H}_Z)_{ij} = K(z_i, z_j)$ , and  $C \in \mathbb{R}^{n \times s}$  with  $C_{ij} = K(x_i, z_j)$ . The Nyström approximation to the full  $n \times n$  kernel matrix is  $\hat{G} = C H_Z^+ C^T$ , where  $H_Z^+$  is the pseudoinverse of  $\mathbf{H}_Z$ . The embedding of a sample x is computed as  $\phi_{\text{nvs}}(x) = \Lambda^{-1/2} \mathbf{Q}^{\mathsf{T}} \mathbf{C}(x)$ , where  $\mathbf{H}_Z = \mathbf{Q} \Lambda \mathbf{Q}^{\mathsf{T}}$  is the eigendecomposition of  $H_Z$ , and  $C(x) \in \mathbb{R}^s$  is the kernel similarity vector between x and landmarks. The embedding  $\phi_{\text{nys}}(x)$  is projected to the HV space via random hyperplane projection matrix  $\mathbf{P}_{rp} \in \mathbb{R}^{d \times s}$ , and is bipolarized via sign function [7], yielding HVs compatible with HDC operations. Note, we define  $P_{nvs} = P_{rp}\Lambda^{-1/2}Q^{T}$  which directly projects C(x) to the HV space.

- 2.1.3 Propagation Kernel for Graph Classification The propagation kernel [41] computes similarity between graphs by iteratively propagating node features through the adjacency matrix and comparing histograms of propagated attributes. Let  $\mathbf{A} \in \{0,1\}^{N \times N}$  denote the

adjacency matrix,  $\mathbf{F} \in \mathbb{R}^{N \times f}$  the initial node features, and H the number of propagation hops. At hop t, node features are updated as  $\mathbf{M}^{(t+1)} = \mathbf{A}\mathbf{M}^{(t)}$ , where  $\mathbf{M}^{(0)} = \mathbf{F}$ , and a histogram  $\mathbf{h}^{(t)} \in \mathbb{Z}^{|\mathcal{B}^{(t)}|}$  is computed from  $\mathbf{M}^{(t)}$ . Given two graphs  $G_X$  and  $G_Z$ , their kernel similarity is defined as

$$K(G_X, G_Z) = \sum_{t=0}^{H-1} \left(\mathbf{h}_X^{(t)}\right)^{\top} \mathbf{h}_Z^{(t)}.$$

Each histogram  $\mathbf{h}^{(t)}$  is constructed by hashing node features into a vocabulary (codebook)  $\mathcal{B}^{(t)}$  of integer codes. The vocabulary  $\mathcal{B}^{(t)}$  is built during training using the landmark graphs. During inference, node feature vectors are projected and quantized, but if a code does not appear in  $\mathcal{B}^{(t)}$ , the update is skipped. For node i at hop t, with feature vector  $\mathbf{m}^{(t,i)} \in \mathbb{R}^f$  (the i-th row of  $\mathbf{M}^{(t)}$ ), the integer code is computed via Locality Sensitive Hashing (LSH) as,

$$c^{(t,i)} = \left\lfloor \frac{(\mathbf{m}^{(t,i)})^{\top} \mathbf{u}^{(t)} + b^{(t)}}{w} \right\rfloor,\,$$

where  $\mathbf{u}^{(t)} \in \mathbb{R}^f$  is a random projection vector,  $b^{(t)} \in \mathbb{R}$  a scalar offset, and w > 0 a fixed quantization width shared across hops. If  $c^{(t,i)} \in \mathcal{B}^{(t)}$ , the corresponding bin of  $\mathbf{h}^{(t)}$  is incremented; otherwise, no update is made. This process starts from a zero-initialized histogram at each hop and aggregates contributions across all nodes in the histogram vector to compute similarity between two graphs.

# 2.2 End-to-End Nyström-HDC Inference

Given a query graph  $G_X = (\mathbf{A}_X, \mathbf{F}_X)$ , inference uses hop-specific codebooks  $\{\mathcal{B}^{(t)}\}_{t=0}^{H-1}$ , landmark histogram matrices  $\{\mathbf{H}^{(t)}\}_{t=0}^{H-1}$  with  $\mathbf{H}^{(t)} \in \mathbb{R}^{s \times |\mathcal{B}^{(t)}|}$  (row i is the hop-t histogram vector of landmark  $z_i$  computed during training), LSH parameters  $\{(\mathbf{u}^{(t)}, b^{(t)})\}_{t=0}^{H-1}$  (with shared width w > 0), the Nyström projection matrix  $\mathbf{P}_{nys} \in \mathbb{R}^{d \times s}$ , and the class-prototype matrix  $\mathbf{G} = [\mathbf{g}_1; \dots; \mathbf{g}_C] \in \{-1, +1\}^{C \times d}$ , to encode  $G_X$  and classify it. At each hop, node features are propagated, node codes are computed in a vectorized fashion and binned (hashed) into a hop-specific histogram  $\mathbf{h}^{(t)}$ , which is then compared against all landmark histograms via a single matrix-vector product to yield a hop-wise similarity vector  $\mathbf{v}^{(t)} \in \mathbb{R}^s$ . Accumulating these over H hops produces the kernel-similarity vector  $\mathbf{C} \in \mathbb{R}^s$ , which is embedded to an HV and matched to class prototypes. Algorithm 1 describes the entire inference.

# 2.3 Problem Definition

Given a labeled graph dataset  $\mathcal{D}=\{(G_i,y_i)\}_{i=1}^n$  with  $G_i=(\mathbf{A}_i,\mathbf{F}_i)$  and labels  $y_i\in\{1,\ldots,C\}$ , graph classification seeks a mapping  $f:(\mathbf{A},\mathbf{F})\mapsto\{1,\ldots,C\}$ . At inference, a query graph  $G_x=(\mathbf{A}_x,\mathbf{F}_x)$  is assigned label  $\hat{y}=f(\mathbf{A}_x,\mathbf{F}_x)$ . We specifically target single-graph, real-time Nyström-HDC inference on resource-constrained edge FPGAs. For each query graph, we measure energy per graph (mJ) and end-to-end latency (ms) from input arrival to prediction. The goal is to minimize both metrics on average (across a given workload) while operating within the constraints of on-chip memory (BRAM/URAM), compute fabric (LUTs, DSPs), and external memory bandwidth (DDR), thereby enabling real-time Nyström-HDC graph classification on edge platforms.

We summarize the computational complexity of the operations in Algorithm 1 in Table 1. The table highlights that the per-graph

## Algorithm 1 End-to-End Inference for Nyström-HDC

**Require:**  $A_x \in \{0,1\}^{N \times N}; F_x \in \mathbb{R}^{N \times f}; \text{ hops } H; \text{ codebooks } \{\mathcal{B}^{(t)}\}; \text{ landmark histograms } \{H^{(t)} \in \mathbb{R}^{s \times |\mathcal{B}^{(t)}|}\}; \text{LSH params } \{(\mathbf{u}^{(t)}, b^{(t)})\} \text{ and width } w; \text{ Nyström projection } \mathbf{P}_{\text{nys}} \in \mathbb{R}^{d \times s}; \text{ class prototypes } \mathbf{G} \in \{-1, +1\}^{C \times d}$

**Ensure:** Query HV  $\mathbf{h} \in \{-1, +1\}^d$  and predicted class  $\hat{y}$  M←F<sub>X</sub> ▶ node features 2:  $\mathbf{C} \leftarrow \mathbf{0} \in \mathbb{R}^{s}$ ▶ similarity accumulator 3: **for** t = 0 **to** H - 1 **do**  $\mathbf{c} \leftarrow \left| \left( \mathbf{M}\mathbf{u}^{(t)} + b^{(t)} \mathbf{1}_N \right) / w \right| \in \mathbb{Z}^N$ ▶ LSH codes  $\mathbf{h}^{(t)} \leftarrow \mathbf{0} \in \mathbb{Z}^{|\mathcal{B}^{(t)}|}$ ▶ histogram for v = 1 to N do  $c \leftarrow \mathbf{c}[v]$ if  $c \in \mathcal{B}^{(t)}$  then  $j \leftarrow \text{INDEX}(\mathcal{B}^{(t)}, c); \mathbf{h}^{(t)}[j] \leftarrow \mathbf{h}^{(t)}[j] + 1$  $\mathbf{v}^{(t)} \leftarrow \mathbf{H}^{(t)} \mathbf{h}^{(t)} \in \mathbb{R}^{s}$  $C \leftarrow C + v^{(t)}$ ▶ accumulating into kernel similarity vector 10: if t < H - 1 then  $M \leftarrow A_x M$ ▶ propagate 13:  $\mathbf{y} \leftarrow \mathbf{P}_{\text{nys}} \mathbf{C} \in \mathbb{R}^d$ ;  $\mathbf{h} \leftarrow \text{sign}(\mathbf{y})$ ▶ encoding 14:  $\hat{y} \leftarrow \arg\max_{c \in \{1,\dots,C\}} \sin(\mathbf{h}, \mathbf{g}_c)$  > similarity against class prototypes

Table 1: Computational complexity of end-to-end Nyström-HDC inference for one query graph.

| Operation           | Expression                                                                                                                                                                         | Repetition | Complexity                              |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|--|

| Feature Propagation | $M \leftarrow AM$                                                                                                                                                                  | H-1        | $2 \phi_A N^2 f$                        |  |

| LSH Code Generation | $(\mathbf{M}\mathbf{u}^{(t)} + b^{(t)}1_N)/w$                                                                                                                                      | H          | 2Nf                                     |  |

| Codebook Lookup     | $c^{(t,i)} \in \mathcal{B}^{(t)}$                                                                                                                                                  | H          | $N \log  \mathcal{B}^{(t)} $            |  |

| Landmark Similarity | $\mathbf{v}^{(t)} = \mathbf{H}^{(t)} \mathbf{h}^{(t)}$                                                                                                                             | H          | $2\phi_{H^{(t)}}  \mathcal{B}^{(t)}  s$ |  |

| Nyström Projection  | $y = P_{nys}C$                                                                                                                                                                     | 1          | 2 sd                                    |  |

| Prototype Matching  | $sim(\mathbf{h}, \mathbf{g}_c)$                                                                                                                                                    | 1          | 2Cd                                     |  |

| Argmax              | $\operatorname{argmax}_c$                                                                                                                                                          | 1          | C                                       |  |

| Total               | $ \begin{array}{c} 2(H-1)\phi_A N^2 f + 2HNf + N\sum_{t=0}^{H-1} \log  \mathcal{B}^{(t)}  \\ + 2s\sum_{t=0}^{H-1} \phi_{H^{(t)}}  \mathcal{B}^{(t)}  + 2sd + 2Cd + C \end{array} $ |            |                                         |  |

Table 2: Memory consumption of parameters and inputs in end-toend Nyström-HDC inference.

| Component                                  | Dimensions                                                                                                                                                                                 | Memory                                                                                                                 |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Adjacency matrix $A_x$                     | $N \times N$                                                                                                                                                                               | $N^2 \cdot b_A$                                                                                                        |  |

| Node features $\mathbf{F}_{x}$             | $N \times f$                                                                                                                                                                               | $Nf\cdot b_F$                                                                                                          |  |

| Codebooks $\{\mathcal{B}^{(t)}\}$          | $ \mathcal{B}^{(t)} $ per hop                                                                                                                                                              | $\sum_{t=0}^{H-1}  \mathcal{B}^{(t)}  \cdot b_{\mathcal{B}^{(t)}}$ $\sum_{t=0}^{H-1} s \mathcal{B}^{(t)}  \cdot b_{H}$ |  |

| Landmark histograms $\{\mathbf{H}^{(t)}\}$ | $s \times  \mathcal{B}^{(t)} $ per hop                                                                                                                                                     | $\sum_{t=0}^{H-1} s  \mathcal{B}^{(t)}  \cdot b_H$                                                                     |  |

| Nyström projection P <sub>nys</sub>        | $d \times s$                                                                                                                                                                               | $ds \cdot b_P$                                                                                                         |  |

| Class prototypes G                         | $C \times d$                                                                                                                                                                               | $Cd \cdot b_G$                                                                                                         |  |

| Total                                      | $\begin{array}{l} N^{2}b_{A} + Nfb_{F} + \sum_{t=0}^{H-1}  \mathcal{B}^{(t)}   b_{\mathcal{B}^{(t)}} \\ +  \sum_{t=0}^{H-1} s   \mathcal{B}^{(t)}   b_{H} + dsb_{F} + Cdb_{G} \end{array}$ |                                                                                                                        |  |

cost is dominated by repeated propagation, codebook lookup, and landmark similarity computations across H hops, along with one-time costs from Nyström projection and prototype matching. Note that  $\phi_A$  and  $\phi_{H^{(t)}}$  refer to the average per-row density of the sparse matrices: adjacency matrix  $\mathbf A$  and landmark histogram matrix  $\mathbf H^{(t)}$ . We summarize the memory requirements for the input and the parameters in Table 2. For codebooks  $\mathcal B^{(t)}$ , the term  $b_{\mathcal B^{(t)}}$  reflects the combined storage of codes and their indices per entry, while

for matrices such as A, F,  $\mathbf{H}^{(t)}$ ,  $\mathbf{P}_{\mathrm{nys}}$ , and G,  $b_{(\cdot)}$  refers to their respective element-wise bit-widths.

# 3 Challenges and Key Innovation

We summarize the key challenges in accelerating Algorithm 1 on resource-constrained edge platforms, along with the innovations we introduce to address them.

Challenge #1 — High redundancy in landmark samples. Nyström based HDC typically selects landmarks via uniform sampling [64], giving every training graph an equal probability of being chosen. This often yields structurally similar landmarks, leading to redundancy. Since each query graph is compared against all landmarks during inference, such redundancy increases both the memory footprint and computation, scaling with O(sd). Our innovation: We introduce a novel hybrid Uniform + DPP sampling strategy (offline) that maintains landmark diversity during selection. This reduces redundant landmarks, lowers memory and bandwidth demand, and notably *improves* accuracy. See Section 4.1 for the method and Section 6.6.3 for empirical gains.

Challenge #2 — Large projection matrix size. The Nyström projection matrix dominates model parameters (over 90% in Table 2) and exceeds on-chip BRAM capacity on edge FPGAs (e.g., ZCU104 provides ~4.5 MB versus 7–16 MB required; Table 8). Consequently, the matrix must be streamed from off-chip DDR during inference, creating a bottleneck due to the limited external memory bandwidth. Our innovation: We first perform a roofline analysis (Section 5.2.5) and identify that the projection is a memory-bound problem. Guided by this, we design a streaming architecture that maximizes external memory bandwidth utilization by issuing contiguous reads matching the memory-interface width and overlapping fetch and compute via a FIFO. Implementation details are in Section 5.2.5.

Challenge #3 — Expensive codebook lookup. For every node and hop, the assigned code must be mapped through a hop-specific codebook to locate its histogram bin. Naïve implementations require repeated dictionary searches, which scale poorly and introduce conflicts when many nodes are processed in parallel. Our innovation: We design a novel lightweight minimal-perfect-hash (MPH) based lookup engine that delivers constant-time (O(1)) code-to-index mapping. The engine supports fully pipelined, concurrent lookups across multiple PEs by banking both hash tables and codebook storage, minimizing conflicts. Each PE updates a local histogram copy, updated concurrently, and merged. This approach adds negligible memory overhead compared to the codebook itself. See Section 5.2.2 for details.

Challenge #4 — Severe load imbalance in SpMV. Sparse matrix operations such as feature propagation (via A) and landmark histogram similarity computation (via  $\mathbf{H}^{(t)}$ ) can become bottlenecks despite their low computational cost. Irregular row sparsity often leaves some PEs idle while others stall on dense rows, leading to severe under-utilization of compute resources. Our innovation: We employ a static load balancing strategy based on precomputed schedule tables (Section 4.2). Rows with similar nonzero counts are grouped offline and assigned iteration-wise across P PEs, ensuring balanced work per cycle. At runtime, each PE fetches its assigned row index from the schedule table and proceeds without dynamic

scheduling overhead. This eliminates under-utilization and prevents sparse propagation from becoming a bottleneck, sustaining high PE throughput.

Beyond the above optimizations, our core contribution is the first end-to-end accelerator that integrates Nyström-based HDC with graph classification, delivering *improved* accuracy while achieving significant speedup and energy efficiency on resource-constrained FPGAs compared to much more powerful CPUs/GPUs, thereby enabling practical edge deployment across real-time applications.

# 4 Optimizations

# 4.1 Landmark Reduction via DPP Sampling

An important step in Nyström-based HDC encoding [64] is the selection of landmark graphs [32]. These landmarks serve as the representative subset used to construct the Nyström projection matrix, and during inference, every query graph must be compared against the landmarks. The quality and diversity of this landmark set, therefore, directly affect both the computational cost and the classification accuracy. Baseline approaches often rely on random uniform sampling [59], which does not guarantee diversity. As a result, graphs with a similar structure and node features may repeatedly be chosen as landmarks, increasing the projection cost while reducing accuracy due to bias toward certain structures. To address this, we adopt a diversity-aware selection method based on Determinantal Point Processes (DPPs) [29]. DPPs favor subsets with high pairwise dissimilarity, thereby improving diverse landmark coverage. In our approach, the DPP similarity kernel is built using the graph propagation kernel [41].

Unlike prior works [33], which target Euclidean data, where kernel evaluations reduce to dot products or distance computations, graph similarity requires propagation kernel evaluations that are substantially more expensive. Consequently, constructing the DPP kernel requires all pairwise kernel evaluation, and the DPP sampling further incurs determinant/eigen decomposition cost  $(O(s^3))$ . Thus, applying DPP directly to all training graphs is impractical. Therefore, we adopt a hybrid Uniform+DPP strategy that first reduces the candidate pool and then enforces diversity, making DPP-based landmark selection practical for Nyström-HDC on graph datasets.

## Algorithm 2 Hybrid Landmark Selection with DPP

**Require:** Graph set  $\mathcal{G}$ , target landmark count s

**Ensure:** Landmark set  $\mathcal{L}$

- 1: Draw candidate pool  $C \subset \mathcal{G}$  using uniform sampling

- 2: Compute similarity kernel K over  $\mathcal C$  using the propagation kernel

- 3: Apply DPP sampling on K to select s diverse landmarks

- 4: return £

As illustrated in Algorithm 2: first, we reduce the candidate pool by uniform sampling, and then apply DPP to select the final landmark set. This strategy retains the diversity benefits of DPP while keeping the landmark selection cost during training manageable. The impact is twofold. First, fewer redundant landmarks reduce the dimensionality s of the Nyström projection matrix  $\mathbf{P}_{\mathrm{nys}} \in \mathbb{R}^{d \times s}$ , which directly lowers both computation O(sd) in Table 1 and memory usage O(ds) in Table 2. Second, the improved diversity of landmarks enhances classification accuracy by avoiding

overrepresentation of similar graph patterns. Together, these benefits make DPP-based landmark selection a practical optimization for deploying Nyström-HDC [64] on edge FPGAs. This demonstrates the importance of algorithm—architecture co-design: by constraining landmark diversity at the algorithmic level, we directly reduce the projection matrix footprint and streaming latency, yielding a design that is both accurate and resource-efficient on an FPGA.

# 4.2 Static Load Balancing

Irregular sparsity in adjacency matrices (A) and landmark histograms  $(\mathbf{H}^{(t)})$  can cause severe PE underutilization. To avoid runtime scheduling overhead while maintaining balanced utilization, we design a lightweight *static iteration-wise load balancer* that maps rows to PEs offline, ensuring that during execution, all PEs remain evenly loaded.

Schedule table. Given N rows and P PEs, computation proceeds in N/P iterations. In each iteration, every PE processes exactly one row, with assignments specified by a precomputed  $N/P \times P$  schedule table. Each row of the table corresponds to one iteration, and each column to a PE; entry (i, j) gives the row index assigned to PE j in iteration i. The table is banked along columns, allowing PEs to fetch their assigned rows concurrently without conflict. At runtime, PE j fetches its row index, reads row\_ptr and col\_idx/val from CSR banks, and accumulates results directly into out[row\_id].

Offline construction. The table is constructed once per sparse operand using a simple nonzero-count grouping procedure:

- (1) Compute nnz[r] for each row.

- (2) Bucket rows into lists keyed by nnz.

- (3) Traverse buckets in increasing order of nnz, greedily allocating P rows at a time to form one iteration. If a bucket contains fewer than P rows, allocation continues with the next bucket until P rows are obtained.

This procedure groups rows with similar sparsity into the same iteration, yielding balanced PE utilization at each cycle. It runs in O(N) time, preserves the CSR layout, and produces a compact schedule table stored in BRAM.

Execution. At runtime, the controller issues iterations sequentially. Each PE reads its row index from the schedule table, performs CSR expansion, and writes directly to out[row\_id], with no dynamic scheduling or reassignment required.

# 5 Accelerator Design

## 5.1 NysX Overview

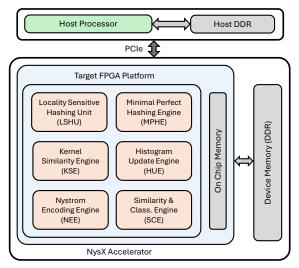

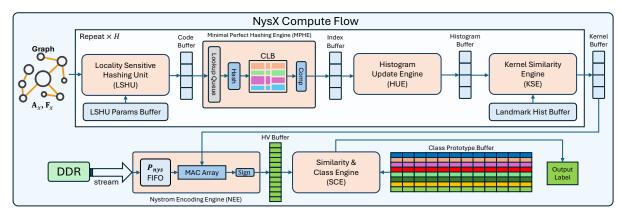

Figure 1 shows the overall architecture of **NysX**, our FPGA accelerator for Nyström-HDC graph classification. **NysX** is composed of six specialized compute engines interconnected via on-chip buffers: (i) the **Locality Sensitive Hashing Unit (LSHU)**, which generates integer codes for nodes at each hop. It combines dense and sparse matrix-vector multiplications with floor operation to produce integer code representations; (ii) the **Minimal Perfect Hashing Engine (MPHE)**, which maps integer codes to valid histogram indices in O(1) time using a Minimal Perfect Hash (MPH), facilitated via low-memory footprint hash level tables stored in on-chip memory; (iii) the **Histogram Update Engine (HUE)**, which accumulates counts into hop-specific histograms using the indices from MPHE, enabling efficient parallel histogram updates; (iv) the

Figure 1: Overview of the NysX FPGA accelerator. NysX comprises six compute engines: LSHU, MPHE, HUE, KSE, NEE, and SCE, interconnected via on-chip buffers.

Kernel Similarity Engine (KSE), which computes landmark similarities by multiplying the query histogram with buffered landmark histograms. Results are accumulated into the kernel vector C; (v) the Nyström Encoding Engine (NEE), which projects the kernel vector into the hyperdimensional space by multiplying with the Nyström projection matrix and applying a bipolarization step; and (vi) the Similarity & Classification Engine (SCE), which computes final class scores by comparing the encoded hypervector against class prototypes, followed by argmax selection of the predicted label. On-chip BRAM stores hash level tables, landmark histograms, and intermediate results. The Nyström projection matrix, due to its large size, is streamed from external DDR memory.

# 5.2 Architectural Components

5.2.1 Locality Sensitive Hashing Unit (LSHU) The LSHU is responsible for generating hop-specific codes. As depicted in Algorithm 1, Nystrom-HDC inference first computes the locality sensitive hash  $\left| \frac{\mathbf{M}\mathbf{u} + b\mathbf{1}_N}{\mathbf{u}} \right|$ , where  $\mathbf{M} = \mathbf{F}_x$  initially, and then propagates  $M \leftarrow AM$ , to generate code vector c. This requires storing intermediate feature matrices of size O(Nf). In our implementation, we restructure this computation into a sequence of matrix-vector products, computed via LSHU. Specifically, we first compute the projection  $\mathbf{c} = \mathbf{F}_x \mathbf{u}$ . Next, we iterate over the hop count to compute  $\mathbf{c} \leftarrow \mathbf{A}\mathbf{c}$ . This computes the required  $\mathbf{M}^{(k)}\mathbf{u}^{(k)}$  as  $\mathbf{A}^k\mathbf{F}_x\mathbf{u}^{(k)}$ . While both methods require access to  $F_x$ , the baseline requires storing the full feature matrix  $\mathbf{M}^{(k)} \in \mathbb{R}^{N \times f}$  as opposed to the intermediate vectors of length N required by our restructuring, significantly reducing the on-chip memory resources required during code generation. In terms of complexity, the baseline requires HNf + (H-1)f nnz $(A_x)$  operations, whereas our restructuring reduces this to  $HNf + \frac{H(H-1)}{2}$  nnz $(A_x)$ . This offers a clear advantage when f > H/2, which typically holds since hop counts are small  $(H \le 10)$  while feature dimensions are much larger (e.g.,  $f \approx 50$ ).

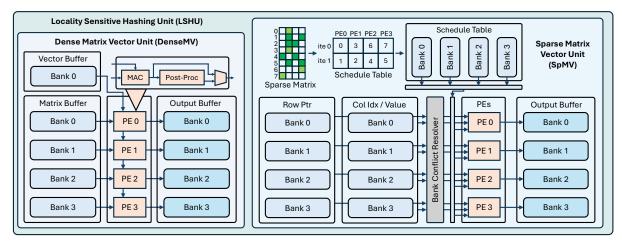

Figure 2: Locality Sensitive Hashing Unit (LSHU). It integrates a DenseMV unit (for Fu) and a SpMV unit (for Ac), with schedule tables, CSR arrays, and output buffers banked across BRAMs; a bank conflict resolver manages access overlaps, enabling concurrent output computation.

Real-world graphs are sparse [43], and the LSHU exploits this by storing A in CSR format and skipping zero entries, thereby reducing both the compute and memory bandwidth demand - critical under edge constraints. However, irregular sparsity causes load imbalance across PEs. To mitigate this, we employ static schedule tables (Section 4.2), which pre-assign rows to PEs based on nonzero counts, ensuring balanced utilization without runtime scheduling overhead. Figure 2 summarizes the architecture. The DenseMV unit performs feature projection, while the SpMV unit handles hop-wise propagation. For SpMV, schedule tables are banked and accessed concurrently by all PEs, enabling each PE to fetch its assigned rows in parallel. CSR arrays (row\_ptr, col\_idx, val) and outputs are also banked across BRAMs to reduce contention, with conflicts managed by a bank conflict resolver. Each PE includes a dedicated MAC unit with a private accumulator and writes results directly to its assigned output index, enabling parallel and energy-efficient sparse computation.

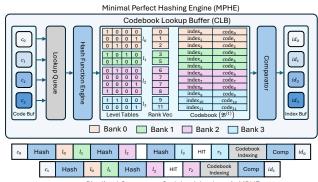

- 5.2.2 Minimal Perfect Hashing Engine (MPHE) We adopt a minimal perfect hash (MPH) scheme [36] to map codes (keys) in the codebook to indices  $\{0, \dots, |\mathcal{B}^{(t)}|-1\}$  with O(1) query time during inference. The scheme constructs the MPH as a cascade of levels  $A_0, A_1, \ldots$ , where each bit-array  $A_d$  is sized to balance memory against collision probability. During construction, keys hashing uniquely at level d set a 1 at position  $h_d(\text{key})$  and are removed, while colliding keys advance to the next level d+1. The final structure concatenates all bit-arrays with a lightweight rank vector. At query time, a key traverses the levels until it encounters a 1, and its index is computed as the cumulative number of 1s preceding that position. This yields a compact ( $\approx 3$  bits/key) structure supporting constant-time queries. The MPHE performs inference-time dictionary lookup from code → histogram index. Upstream, the LSHU produces a chunk of integer codes, which are enqueued into a lookup queue. Each lookup then proceeds as follows:

- (1) Hash generation. A Hash Function Engine computes two 64-bit hashes for the input code using a seeded integer hash function [57]. The level-d probe index is  $i_d \leftarrow h_d(\text{code}) \mod |A_d|$ , where  $|A_d|$  is the bit capacity of level table  $A_d$ .

- (2) Level table probe. Level tables  $\{A_d\}$  are stored on-chip as banks of 64-bit words; the bit at  $i_d$  is checked within its word. If it is 0, the code advances to the next level by generating the next hash in the sequence via a xorshift-based rehash generator [51].

- (3) Rank to MPH index. On a 1-bit hit at  $(d, i_d)$ , the engine retrieves the global index directly from the rank vector. Each entry in the rank vector stores the cumulative number of 1s up to the start of a word, aggregated across all levels. The final index is obtained by adding this value to the popcount of bits within the current word up to (and including) position  $i_d$ , and subtracting one for zero-based indexing.

- (4) Codebook verification. The MPH index addresses a compact codebook store that holds pairs (code, hist\_idx). The queried code is compared against the stored code. If they match, the corresponding hist\_idx is emitted as valid. If they differ, the lookup terminates, as a hit with mismatch implies the queried code is not in the original codebook. If all levels are probed with no hit, the code is deemed absent. No histogram update occurs for a queried code absent from the codebook.

Figure 3 illustrates the MPHE datapath: (a) a Lookup Queue collects codes from LSHU PEs; (b) a Hash Function Engine generates 64-bit hashes and level indices; (c) Level Tables  $A_d$  and Rank Vectors, each banked across BRAMs, are accessed in parallel; (d) an Index Buffer carries the computed MPH index; and (e) a banked Codebook returns the (code,hist\_idx) pair to a Compare Unit that verifies code presence. Level tables and rank vectors are placed in independent banks to support pipelined parallel lookups (Figure 3), while contention in codebook access is reduced through MPH hashing, pipelining, and banking. The pipeline roughly issues one index lookup per cycle, with O(1) cost bounded by the small number of level tables per codebook.

5.2.3 **Histogram Update Engine (HUE)** The Histogram Update Engine (HUE) maintains hop-specific query histogram vector  $\mathbf{h}^{(t)}$ , incrementing it based on the indices returned by MPHE. To maximize update parallelism, each PE in HUE keeps a private copy

Pipelined Concurrent Codebook Lookup via MPHE

Figure 3: Minimal Perfect Hashing Engine (MPHE). Codes from LSHU PEs are hashed and probed via banked codebook lookup buffer (CLB). Multiple lookups proceed in a pipelined manner (bottom), with O(1) query time.

of the histogram, allowing concurrent increments without contention. Once all codes in the current hop are processed, local histograms are merged into the global hop histogram through a reduction step. This two-stage strategy avoids write conflicts while still providing correct cumulative counts. Each histogram is stored in on-chip BRAM, with indexing controlled by MPHE outputs. The final merged histogram is forwarded to KSE for landmark similarity computation.

5.2.4 **Kernel Similarity Engine (KSE)** The Kernel Similarity Engine (KSE) computes hop-level landmark similarities by multiplying the query histogram  $\mathbf{h}^{(t)}$  with the precomputed landmark histograms  $\mathbf{H}^{(t)}$ , producing  $\mathbf{v}^{(t)} = \mathbf{H}^{(t)}\mathbf{h}^{(t)}$ . This operation is realized using a sparse matrix–vector (SpMV) unit, as  $\mathbf{H}^{(t)}$  is stored in CSR format and exhibits significant sparsity. Rows of  $\mathbf{H}^{(t)}$  are distributed across PEs, and static load balancing (Section 4.2) ensures uniform work assignment. The resulting vector  $\mathbf{v}^{(t)}$  is accumulated into the global kernel similarity buffer C, which aggregates contributions across all hops.

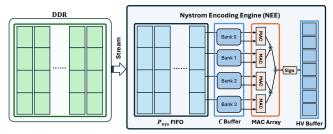

5.2.5 **Nyström Encoding Engine (NEE)** The Nyström Encoding Engine (NEE) generates the final hypervector through projection  $h = \mathrm{sign}(P_{\mathrm{nys}}C)$ , where  $P_{\mathrm{nys}}$  is the Nyström projection matrix, C is the similarity vector from the KSE compute engine. Storing  $P_{\mathrm{nys}}$  on-chip is infeasible for edge devices with limited on-chip memory; hence,  $P_{\mathrm{nys}}$  is streamed from external DDR during inference. Profiling shows that the NEE kernel dominates inference time (>90%), making it a critical kernel, and we analyze it using the roofline model [60].

**Roofline Analysis:** For the NEE projection  $P_{nys}C$ , while C is buffered on-chip, each multiply-accumulate reads one element of  $P_{nys}$  matrix and performs two floating-point operations. With 32-bit elements (4 bytes), this gives 2 ops per 4 bytes, which translates to an arithmetic intensity (AI) of 0.5 operations per byte (ops/byte). To illustrate machine balance, consider a design point with 32 MAC lanes clocked at 300 MHz, yielding a peak compute performance of 19.2 GOPS. The ZCU104's DDR4 interface provides a theoretical bandwidth of 19.2 GB/s [38]; even at 90% efficiency, sustained bandwidth is 17.3 GB/s. This corresponds to a machine balance of about 1.11 ops/byte. Since AI is less than machine balance, the kernel

Figure 4: Streaming Nyström Encoding Engine architecture.

falls into the memory-bound region of the roofline model. This implies that performance gains primarily come from improving data movement rather than simply adding more MAC lanes.

Streaming Architecture: Given that the NEE projection is memory-bound, this work adopts a streaming (dataflow) [42] architecture in which compute stages are connected via on-chip FIFOs to overlap data movement with execution. To maximize external memory bandwidth utilization, data transfers are aligned to the FPGA platform's native memory-port width, y bits. Accordingly, we organize  $P_{nys}$  into y-bit words and issue contiguous y-bit burst transfers. This maximizes effective bandwidth utilization, avoiding inefficiency from irregular or undersized accesses. We also enable multiple outstanding reads to keep the memory interface saturated despite variable off-chip DRAM latency. Incoming y-bit words are buffered in a deep on-chip FIFO, decoupling bursty DRAM traffic from the compute stage. Without this buffering, memory-interface stalls would propagate into the MAC pipeline, reducing throughput. Each y-bit word is unpacked into y/x operands, where x is the precision of the operand in bits, and is routed to y/x MAC lanes. This avoids hard-wiring the design to a single precision, keeps it scalable, and fully utilizes the memory interface width. As illustrated in Figure 4, each MAC lane performs a dot product between its assigned elements of P<sub>nvs</sub> and the corresponding entries of the similarity vector C, which is buffered on chip with cyclic partitioning to enable conflict-free parallel access across banks. After accumulation, results are bipolarized to  $\{-1, +1\}$ . This kernel fusion avoids storing high-precision intermediates, writing the final hypervector directly as integers and reducing the on-chip buffer by over 4× compared to floats.

5.2.6 Similarity & Classification Engine (SCE) The Similarity & Classification Engine (SCE) performs the final stage of inference by comparing the encoded hypervector h against the stored class prototypes  $\{g_c\}_{c=1}^C$ . This is implemented as a dense matrix–vector multiplication  $\mathbf{s} = \mathbf{Gh}$ , where  $\mathbf{G} \in \{-1, +1\}^{C \times d}$ . The computation is parallelized across PEs, each responsible for a block of rows in G. The output scores  $\mathbf{s}$  are written into an on-chip buffer, followed by a small argmax unit that identifies the predicted class  $\hat{y} = \arg\max_{c} s_c$ .

#### 5.3 Compute Flow

Figure 5 illustrates the end-to-end execution flow of **NysX**, tying together the specialized compute engines described earlier. The process begins with an input graph, represented by adjacency matrix  $A_X$  and feature matrix  $F_X$ . Inference proceeds hop-by-hop, with each hop producing a histogram vector that contributes to the global kernel similarity vector. At hop h, the *Locality Sensitive Hashing Unit (LSHU)* computes code vectors. First, a dense MV unit

Figure 5: NysX compute flow across hops: input graph  $\{A_x, F_x\}$  is processed by compute engines to produce class label.

projects features as  $\mathbf{c} \leftarrow \mathbf{F}_x \mathbf{u}^{(h)}$ . This is followed by sparse propagation  $\mathbf{c} \leftarrow \mathbf{A}_x \mathbf{c}$ , performed iteratively. Exploiting CSR format and static load balancing, each PE processes rows of  $\mathbf{A}_x$  with comparable nonzero counts, reducing idle time and ensuring balanced throughput. Floor operation then produces integer codes, which are enqueued for dictionary lookup.

Codes are passed to the Minimal Perfect Hashing Engine (MPHE), which maps each code to a histogram index via pipelined, O(1)lookups. Level tables, rank vectors, and codebook stores are banked in BRAM, enabling concurrent access across PEs. Verified histogram indices are forwarded to the Histogram Update Engine (HUE), where PEs increment local histograms in parallel before merging into the hop-global histogram buffer. Once a hop histogram is complete, the Kernel Similarity Engine (KSE) multiplies it with pre-stored landmark histograms. Implemented as a SpMV, this step accumulates partial results into the global kernel similarity vector C. After all hops finish, the Nyström Encoding Engine (NEE) consumes C from the kernel buffer. The projection matrix  $P_{\mathrm{nys}}$  is streamed from DDR through a FIFO into the MAC array, where they are multiplied with the corresponding elements of C to generate the output hypervector. The sign() function is fused directly into the MAC array, producing a bipolarized HV on the fly. Finally, the Similarity & Classification Engine (SCE) computes class scores by multiplying the encoded hypervector with class prototypes, followed by an argmax to select the predicted label.

### 6 Experimental Evaluation

### 6.1 Implementation Details

We implement the proposed accelerator on an AMD Zynq Ultra-Scale+ ZCU104 FPGA [4], representative of an edge-class FPGA. The accelerator is designed using AMD Vitis High Level Synthesis (HLS) and synthesized using AMD Vitis Unified IDE v2024.2 [2]. We instantiate 4 PEs in the LSHU, KSE, and HUE compute engines of the accelerator to conserve on-chip resources (LUT/DSP/BRAM) for the NEE compute engine, which dominates area and latency. Empirically, configurations with more than 4 PEs result in marginal speedup while increasing resource usage, so 4 PEs remain the best end-to-end trade-off on ZCU104. For NEE, P<sub>nys</sub> is streamed through a 512-bit AXI transfer width. This width is selected because Vitis HLS automatically widens burst ports up to 512 bits [3] and AXI

Table 3: Resource Utilization of the Proposed Design

| Resource   | Used   | Available | Utilization |

|------------|--------|-----------|-------------|

| LUT        | 71,900 | 230,400   | 31%         |

| FF         | 87,800 | 460,800   | 19%         |

| BRAM (18K) | 329    | 624       | 52%         |

| DSP        | 156    | 1,728     | 9%          |

| URAM       | 0      | 96        | 0%          |

SmartConnect inserts width converters to match the platform's native memory ports [1]. For a 32-bit precision, each transfer packs 16 FP32 values and drives 16 parallel MAC lanes. We employ a 512-entry, 16-FP32-wide stream FIFO to overlap data fetch and compute. Table 3 reports the resource utilization obtained through the Vitis Unified IDE, with an achieved frequency of 300 MHz.

#### 6.2 Datasets

We evaluate on eight benchmark datasets from the TUDataset [39], a widely used collection for graph classification, consistent with prior work [43, 64]. These datasets span diverse domains (e.g., bioinformatics, chemistry, and drug discovery) and vary in graph sizes and structures, providing a representative set for evaluating NysX. Table 4 summarizes their statistics.

**Table 4: Summary of Graph Classification Datasets**

| Task              | #Train | #Test | Avg. Nodes | Avg. Edges | Description             |

|-------------------|--------|-------|------------|------------|-------------------------|

| ENZYMES [5]       | 480    | 120   | 33         | 62         | Protein graphs          |

| NCI1 [55]         | 3288   | 822   | 30         | 32         | Chemical compounds      |

| D&D [12]          | 943    | 235   | 284        | 716        | Protein structures      |

| BZR [52]          | 324    | 81    | 36         | 38         | Drug activity graphs    |

| MUTAG [11]        | 150    | 38    | 18         | 20         | Mutagenicity prediction |

| COX2 [52]         | 373    | 94    | 41         | 43         | Drug activity graphs    |

| NCI109 [55]       | 3301   | 826   | 30         | 32         | Chemical compounds      |

| Mutagenicity [47] | 3469   | 868   | 30         | 31         | Mutagenicity prediction |

# 6.3 Baseline Platforms

We evaluate our FPGA accelerator against CPU and GPU baselines: the AMD Ryzen 5 5625U, a modern 6-core, 12-thread processor, and the NVIDIA RTX A4000, a workstation-class GPU with 6144 CUDA cores. All baselines are implemented in PyTorch (v2.4.1) with Python 3.8 and CUDA 12.1.

**Table 5: Specifications of Baseline Platforms**

|              | CPU                 | GPU                     | FPGA (Ours)        |

|--------------|---------------------|-------------------------|--------------------|

| Platform     | AMD Ryzen 5 5625U   | NVIDIA RTX A4000        | AMD ZCU104         |

| Technology   | TSMC 7nm            | Samsung 8nm             | TSMC 16nm          |

| Frequency    | 2.3 GHz (base)      | 1560 MHz                | 300 MHz            |

| Cores/SMs    | 6 cores, 12 threads | 48 SMs, 6144 CUDA cores | -                  |

| Peak Perf.   | 2.4 TFLOPS (FP32)   | 19.2 TFLOPS (FP32)      | 0.26 TFLOPS (FP32) |

| On-chip Mem. | 3 MB L2, 16 MB L3   | 6 MB L2 Cache           | 4.5 MB BRAM        |

| Memory BW    | 50 GB/s (DDR4)      | 448 GB/s (GDDR6)        | 19.2 GB/s (DDR4)   |

#### 6.4 Selection of Baseline Platforms

We select the Ryzen processor as representative of CPUs deployed in laptops and compact systems, while the RTX A4000 is a workstation-class GPU, commonly used as baselines in prior HDC works [6, 8, 13, 37]. Both baselines offer substantially higher peak compute and memory resources than our target edge FPGA, providing a conservative comparison. For fairness, GPU latency is measured after transferring all model parameters to device memory. This favors the GPU, which benefits from high-bandwidth GDDR6 memory, whereas on the FPGA, the Nyström projection matrix—the dominant model component—must be streamed from DDR during inference. Despite this disadvantage, NysX consistently achieves lower end-to-end inference latency. While workstation-class GPUs naturally draw more power, we report energy per inference (mJ/graph) to account for this.

### 6.5 Evaluation Metrics

We report four key metrics: (i) Classification accuracy (%): fraction of correctly predicted labels against ground truth; (ii) Latency (ms/graph): average end-to-end inference time per graph at batch size 1, measured from the arrival of the graph's adjacency and feature matrices to the prediction of class label; (iii) Power (W): average device power during steady-state inference, including static and dynamic components; (iv) Energy Efficiency (mJ/graph): Measured energy consumption in mJ per graph inference.

# 6.6 Results and Analysis

*6.6.1* **Latency** For FPGA, cycle-accurate latency is obtained from the integrated analyzer in the AMD Vitis Unified IDE v2024.2 toolchain, following HLS synthesis and implementation.

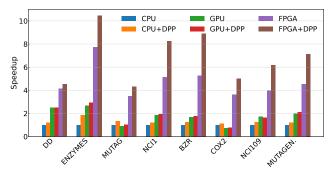

CPU and GPU latencies are measured using wall-clock timing in PyTorch with batch size set to one, consistent with real-time edge inference. Table 6 reports absolute latencies (ms/graph) for CPU, GPU, and FPGA with and without DPP-based landmark reduction, while Fig. 6 shows corresponding speedups normalized to the CPU baseline without DPP. Across all datasets, **NysX** consistently delivers lower latency than CPU and GPU baselines, despite both being more resource-rich and compute-capable. On average, FPGA latency is reduced by 4.5× relative to CPU and 2.2× relative to GPU. Incorporating DPP further reduces per-inference latency by 25 to 40% by pruning redundant landmarks, which reduces memory transfers of  $P_{\rm nys}$  and accelerates histogram updates. Overall, **NysX** achieves sub-millisecond inference on most datasets, with peak speedups of 8.9× over CPU and 3× over GPU.

6.6.2 **Energy Efficiency** Table 7 compares throughput, power, and energy efficiency across platforms. CPU power is measured with a plug-in power meter, model PM01-US, GPU power using the nvidia-smi [44] command line tool, and FPGA power from the AMD

Table 6: End-to-end latency (ms) per graph. Speedup in parentheses is relative to the CPU baseline (without DPP) for the same dataset.

| Dataset      | CPU          | CPU+DPP      | GPU          | GPU+DPP      | FPGA         | FPGA+DPP      |

|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| DD           | 7.47 (1.00x) | 6.11 (1.22x) | 3.00 (2.49x) | 3.00 (2.49x) | 1.80 (4.15x) | 1.65 (4.53x)  |

| ENZYMES      | 4.71 (1.00x) | 2.55 (1.85x) | 1.77 (2.66x) | 1.60 (2.94x) | 0.61 (7.72x) | 0.45 (10.47x) |

| MUTAG        | 5.13 (1.00x) | 3.87 (1.33x) | 5.80 (0.88x) | 4.90 (1.05x) | 1.47 (3.49x) | 1.19 (4.31x)  |

| NCI1         | 5.04 (1.00x) | 4.23 (1.19x) | 2.70 (1.87x) | 2.60 (1.94x) | 0.98 (5.14x) | 0.61 (8.26x)  |

| BZR          | 2.85 (1.00x) | 2.29 (1.24x) | 1.70 (1.67x) | 1.60 (1.78x) | 0.54 (5.27x) | 0.32 (8.89x)  |

| COX2         | 5.26 (1.00x) | 4.68 (1.12x) | 7.30 (0.72x) | 6.70 (0.79x) | 1.45 (3.63x) | 1.05 (5.01x)  |

| NCI109       | 4.26 (1.00x) | 3.44 (1.24x) | 2.50 (1.70x) | 2.60 (1.64x) | 1.07 (3.98x) | 0.69 (6.17x)  |

| Mutagenicity | 3.57 (1.00x) | 3.01 (1.19x) | 1.80 (1.98x) | 1.70 (2.10x) | 0.79 (4.52x) | 0.50 (7.13x)  |

Figure 6: Speedup over CPU baseline (no DPP) across datasets. See Section 4.1 for DPP-based landmark reduction strategy.

Vitis Unified IDE [2] post-implementation. Table 7 reports that our FPGA design delivers orders of magnitude lower energy per graph over CPU and GPU baselines, while also increasing throughput. Across the TU datasets, the FPGA energy is  $101\times$  to  $256\times$  lower than CPU and  $133\times$  to  $451\times$  lower than GPU, with throughput gains of  $3.2\times$  to  $7.2\times$  vs. CPU and  $1.8\times$  to  $6.4\times$  vs. GPU. These improvements arise from our architectural choices, such as DPP-based landmark reduction, bandwidth-aware streaming of  $P_{nys}$ , enabling extreme energy efficiency, which is critical for edge deployment.

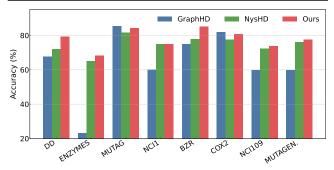

6.6.3 Impact of DPP on Accuracy and Memory Figure 7 reports classification accuracy across eight TU datasets [39], comparing NysX against state-of-the-art HDC baselines GraphHD [43] and NysHD [64]. GraphHD results are taken from prior work [43, 64], and we re-implement NysHD using the authors' open-source repository under identical experimental settings. Our design improves accuracy by 3.4% on average over NysHD, with the largest gains on BZR (8.0%) and DD (7.0%). We outperform both baselines on six of eight datasets; on COX2 and Mutag, GraphHD performs slightly better. This behavior reflects our hybrid uniform+DPP landmark selection. The uniform sampling introduces randomness and redundancy, which can have a considerable impact on small datasets. A full DPP-based sampling could reduce this impact, but it is computationally expensive due to eigendecomposition and full kernel matrix construction. Our hybrid approach preserves most of DPP's diversity benefits at substantially lower sampling cost.

Beyond accuracy, DPP reduces the model's memory footprint. During Nyström-HDC inference, parameters in Table 2 are required. Among them, the Nyström projection matrix  $P_{\rm nys}$  dominates both the storage and off-chip transfer volume. Table 8 shows that DPP-based landmark reduction lowers total memory required by 37% on average. Thus, by eliminating redundant landmarks, DPP reduces the memory footprint, lowering both the storage requirements and off-chip traffic while improving accuracy.

Table 7: Throughput, power, and energy efficiency with DPP on TU datasets. Energy ratios are normalized to FPGA (= $1\times$ ).

| Dataset      | Device      | Throughput<br>(graphs/s) | Power<br>(W) | Energy Efficiency<br>(mJ/graph) |

|--------------|-------------|--------------------------|--------------|---------------------------------|

|              | CPU         | 163                      | 25.2         | 154 (116×)                      |

| DD           | GPU         | 333                      | 59.0         | 177 (133×)                      |

|              | FPGA        | 606                      | 0.81         | 1.33 (1×)                       |

|              | CPU         | 392                      | 24.3         | 62 (194×)                       |

| Enzymes      | GPU         | 625                      | 61.0         | 98 (305×)                       |

|              | FPGA        | 2222                     | 0.71         | 0.32 (1×)                       |

|              | CPU         | 259                      | 25.3         | 98 (101×)                       |

| Mutag        | GPU         | 204                      | 60.0         | 294 (303×)                      |

| -            | FPGA        | 840                      | 0.81         | 0.97 (1×)                       |

|              | CPU         | 236                      | 25.5         | 108 (225×)                      |

| NCI1         | GPU         | 385                      | 61.0         | 159 (330×)                      |

|              | FPGA        | 1639                     | 0.79         | 0.48 (1×)                       |

|              | CPU         | 437                      | 24.6         | 56 (256×)                       |

| BZR          | GPU         | 625                      | 62.0         | 99 (451×)                       |

|              | FPGA        | 3125                     | 0.70         | 0.22 (1×)                       |

|              | CPU         | 214                      | 24.4         | 114 (127×)                      |

| COX2         | GPU         | 149                      | 61.0         | 409 (454×)                      |

|              | FPGA        | 952                      | 0.86         | 0.90 (1×)                       |

|              | CPU         | 291                      | 24.9         | 86 (156×)                       |

| NCI109       | GPU         | 385                      | 60.0         | 156 (284×)                      |

|              | FPGA        | 1449                     | 0.79         | 0.55 (1×)                       |

|              | CPU         | 332                      | 24.4         | 73 (184×)                       |

| Mutagenicity | GPU         | 588                      | 60.0         | 102 (255×)                      |

|              | <b>FPGA</b> | 2000                     | 0.79         | 0.40 (1×)                       |

Figure 7: Classification accuracy (%) on TU datasets.

Table 8: Memory consumption of model parameters with and without DPP.

| Dataset      | Memory w/o DPP (MB) | Memory w/ DPP (MB) |

|--------------|---------------------|--------------------|

| DD           | 12.50               | 9.15 (\ 26.8%)     |

| Enzymes      | 16.13               | 11.13 (\ 31.0%)    |

| Mutag        | 7.49                | 4.62 (\ 38.3%)     |

| NCI1         | 12.54               | 7.88 (\ 37.2%)     |

| BZR          | 11.78               | 7.02 (\ 40.4%)     |

| COX2         | 12.50               | 7.70 (\ 38.4%)     |

| NCI109       | 12.50               | 6.97 (\ 44.2%)     |

| Mutagenicity | 11.86               | 7.16 (\ 39.6%)     |

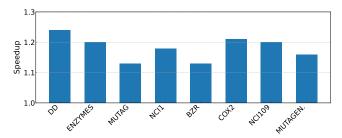

6.6.4 Impact of Load Balancing (LB) We quantify the benefit of the static, offline row scheduling in Section 4.2 by comparing FPGA latency with and without load balancing. Figure 8 reports speedup normalized to the *no-LB* case (=1). Across the TU datasets, we observe consistent gains of 1.13× to 1.24× (mean 1.19×). Datasets with broader per-row nnz variance (e.g., DD, COX2) benefit the most, due to reduced PE idling and fewer BRAM-port stalls in the

Figure 8: Effect of static load balancing in SpMV stages (LSHU/KSE): Speedup normalized to *no LB* case (=1).

SpMV engines. As the sparse matrices in CSR format are static, the schedule incurs zero runtime overhead and requires only a small BRAM schedule table.

#### 7 Related Works

Graph Classification with HDC: GraphHD [43], the first HDC approach for graph classification, encodes graph structure via PageRank, but does not exploit node attributes, limiting accuracy. NysHD [64] improves accuracy through Nyström kernel approximations; however, it incurs additional propagation kernel cost, relies on uniform landmark sampling leading to redundant landmarks, and does not exploit the sparsity in adjacency and histogram matrices. FPGA Acceleration of HDC: Prior hardware acceleration efforts for HDC have targeted domains such as biosignals [15], image descriptors [40], and activity recognition [27]. E<sup>3</sup>-HDC [48] accelerates random-projection encoding; FACH [20] accelerates similarity engines; DistriHD [35] scales HDC across FPGA clusters for image workloads. HyperGraf [9] applies HDC to graph reasoning tasks such as node classification. These works validate hardwareaccelerated HDC but target different encodings and tasks. To the best of our knowledge, NysX is the first to exploit FPGA to accelerate Nyström-based HDC for graph classification. Nyström and Kernel Methods: The Nyström method [58, 59] has long been used to efficiently approximate kernel matrices, with sampling strategies ranging from uniform sampling to determinantal point processes (DPPs) [29, 30, 33]. [64] extends this line of work to HDC, showing the benefits of integrating kernel functions for feature encoding. Building on this, we employ DPP-based landmark selection with propagation-kernel similarity, and introduce an FPGA accelerator that enables Nyström-HDC graph classification with low latency and energy consumption, while significantly improving accuracy.

# 8 Conclusion and Future Work

In this work, we presented  $\mathbf{NysX}$ , the first FPGA accelerator for Nyström-based HDC graph classification.  $\mathbf{NysX}$  integrates four key optimizations—DPP-based landmark sampling, a streaming projection design, O(1) minimal-perfect-hash lookups, and statically load-balanced SpMV—to achieve up to  $6.85\times$  and  $4.32\times$  lower latency than CPU and GPU baselines on ZCU104, while reducing energy per inference by  $169\times$  and  $314\times$ , respectively. Importantly,  $\mathbf{NysX}$  also improves classification accuracy by 3.4% on average compared to prior HDC methods. Looking ahead, we plan to extend these techniques to broader workloads and data modalities (e.g., image and text), as well as to other graph tasks such as node classification and link prediction.

#### References

- Advanced Micro Devices, Inc. 2023. AXI SmartConnect LogiCORE IP Product Guide (PG247). https://docs.amd.com/r/en-US/pg247-smartconnect Version 4.1.

- [2] Advanced Micro Devices, Inc. 2024. AMD Vitis Unified IDE, Version 2024.2. https://docs.amd.com/r/en-US/Vitis-Tutorials-AI-Engine-Development/ Vitis-Unified-Software-Development-Platform-2024.2-Documentation Release 2024.2.

- [3] Advanced Micro Devices, Inc. 2024. Vitis High-Level Synthesis User Guide (UG1399). https://docs.amd.com/r/en-US/ug1399-vitis-hls Version 2024.2.

- [4] AMD Xilinx. [n.d.]. Zynq UltraScale+ MPSoC ZCU104 Evaluation Kit. https://www.xilinx.com/products/boards-and-kits/zcu104.html. Accessed: Sep. 25, 2025.

- [5] Karsten M Borgwardt, Cheng Soon Ong, Stefan Schönauer, SVN Vishwanathan, Alex J Smola, and Hans-Peter Kriegel. 2005. Protein function prediction via graph kernels. *Bioinformatics* 21, suppl\_1 (2005), i47-i56.

- [6] Cheng-Yang Chang, Yu-Chuan Chuang, Chi-Tse Huang, and An-Yeu Wu. 2023. Recent Progress and Development of Hyperdimensional Computing (HDC) for Edge Intelligence. IEEE Journal on Emerging and Selected Topics in Circuits and Systems 13, 1 (2023), 119–136. https://doi.org/10.1109/JETCAS.2023.3242767

- [7] Moses S Charikar. 2002. Similarity estimation techniques from rounding algorithms. In Proceedings of the thiry-fourth annual ACM symposium on Theory of computing. 380–388.

- [8] Hanning Chen, Yang Ni, Ali Zakeri, Zhuowen Zou, Sanggeon Yun, Fei Wen, Behnam Khaleghi, Narayan Srinivasa, Hugo Latapie, and Mohsen Imani. 2024. HDReason: Algorithm-Hardware Codesign for Hyperdimensional Knowledge Graph Reasoning. arXiv:2403.05763 [cs.AR] https://arxiv.org/abs/2403.05763

- [9] Hanning Chen, Ali Zakeri, Fei Wen, Hamza Barkam, and Mohsen Imani. 2023.

HyperGRAF: Hyperdimensional Graph-Based Reasoning Acceleration on FPGA. 34–41. https://doi.org/10.1109/FPL60245.2023.00013

- [10] Sohum Datta, Ryan AG Antonio, Aldrin RS Ison, and Jan M Rabaey. 2019. A programmable hyper-dimensional processor architecture for human-centric IoT. IEEE Journal on Emerging and Selected Topics in Circuits and Systems 9, 3 (2019), 439–452.

- [11] Asim Kumar Debnath, Rosa L Lopez de Compadre, Gargi Debnath, Alan J Shusterman, and Corwin Hansch. 1991. Structure-activity relationship of mutagenic aromatic and heteroaromatic nitro compounds. correlation with molecular orbital energies and hydrophobicity. *Journal of medicinal chemistry* 34, 2 (1991), 786–797.

- [12] Paul D Dobson and Andrew J Doig. 2003. Distinguishing enzyme structures from non-enzymes without alignments. Journal of molecular biology 330, 4 (2003), 771–783.

- [13] Arpan Dutta, Saransh Gupta, Behnam Khaleghi, Rishikanth Chandrasekaran, Weihong Xu, and Tajana Rosing. 2022. HDnn-PIM: Efficient in Memory Design of Hyperdimensional Computing with Feature Extraction. In Proceedings of the Great Lakes Symposium on VLSI 2022 (Irvine, CA, USA) (GLSVLSI '22). Association for Computing Machinery, New York, NY, USA, 281–286. https://doi.org/10. 1145/3526241.3530331

- [14] Federico Errica, Marco Podda, Davide Bacciu, and Alessio Micheli. 2022. A Fair Comparison of Graph Neural Networks for Graph Classification. arXiv:1912.09893 [cs.LG] https://arxiv.org/abs/1912.09893

- [15] Lulu Ge and Keshab K Parhi. 2021. Seizure detection using power spectral density via hyperdimensional computing. In ICASSP 2021-2021 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP). IEEE, 7858-7862.

- [16] Alejandro Hernández-Cano, Namiko Matsumoto, Éric Ping, and Mohsen Imani. 2021. Onlinehd: Robust, efficient, and single-pass online learning using hyperdimensional system. In 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE). IEEE, 56–61.

- [17] Binbin Hu, Zhiqiang Zhang, Chuan Shi, Jun Zhou, Xiaolong Li, and Yuan Qi. 2019. Cash-Out User Detection Based on Attributed Heterogeneous Information Network with a Hierarchical Attention Mechanism. Proceedings of the AAAI Conference on Artificial Intelligence 33, 01 (Jul. 2019), 946–953. https://doi.org/10. 1609/aaai.y33i01.3301946

- [18] Mohsen Imani, Yeseong Kim, Sadegh Riazi, John Messerly, Patric Liu, Farinaz Koushanfar, and Tajana Rosing. 2019. A framework for collaborative learning in secure high-dimensional space. In 2019 IEEE 12th International Conference on Cloud Computing (CLOUD). IEEE, 435–446.

- [19] Mohsen Imani, Justin Morris, John Messerly, Helen Shu, Yaobang Deng, and Tajana Rosing. 2019. Bric: Locality-based encoding for energy-efficient braininspired hyperdimensional computing. In Proceedings of the 56th Annual Design Automation Conference 2019. 1–6.

- [20] Mohsen Imani, Sahand Salamat, Saransh Gupta, Jiani Huang, and Tajana Rosing. 2019. FACH: FPGA-based acceleration of hyperdimensional computing by reducing computational complexity (ASPDAC '19). Association for Computing Machinery, New York, NY, USA, 493–498. https://doi.org/10.1145/3287624.3287667

- [21] Aditya Joshi, Johan T Halseth, and Pentti Kanerva. 2016. Language geometry using random indexing. In *International Symposium on Quantum Interaction*. Springer, 265–274.

- [22] Pentti Kanerva. 2009. Hyperdimensional computing: An introduction to computing in distributed representation with high-dimensional random vectors. Cognitive computation 1, 2 (2009), 139–159.

- [23] Jaeyoung Kang, Behnam Khaleghi, Yeseong Kim, and Tajana Rosing. 2022. Xcelhd: An efficient gpu-powered hyperdimensional computing with parallelized training. In 2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC). IEEE, 220–225.

- [24] Behnam Khaleghi, Jaeyoung Kang, Hanyang Xu, Justin Morris, and Tajana Rosing. 2022. GENERIC: highly efficient learning engine on edge using hyperdimensional computing. In Proceedings of the 59th ACM/IEEE Design Automation Conference (San Francisco, California) (DAC '22). Association for Computing Machinery, New York, NY, USA, 1117–1122. https://doi.org/10.1145/3489517.3530669

- [25] Behnam Khaleghi, Jaeyoung Kang, Hanyang Xu, Justin Morris, and Tajana Rosing. 2022. Generic: highly efficient learning engine on edge using hyperdimensional computing. In Proceedings of the 59th ACM/IEEE Design Automation Conference. 1117–1122

- [26] Yeseong Kim, Mohsen Imani, Niema Moshiri, and Tajana Rosing. 2020. Geniehd: Efficient dna pattern matching accelerator using hyperdimensional computing. In 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE). IEEE, 115–120.

- [27] Yeseong Kim, Mohsen Imani, and Tajana S Rosing. 2018. Efficient human activity recognition using hyperdimensional computing. In Proceedings of the 8th International Conference on the Internet of Things. 1–6.

- [28] Denis Kleyko, Dmitri Rachkovskij, Evgeny Osipov, and Abbas Rahimi. 2023. A survey on hyperdimensional computing aka vector symbolic architectures, part ii: Applications, cognitive models, and challenges. Comput. Surveys 55, 9 (2023), 1–52

- [29] Alex Kulesza. 2012. Determinantal Point Processes for Machine Learning. Foundations and Trends® in Machine Learning 5, 2–3 (2012), 123–286. https://doi.org/10.1561/2200000044

- [30] Sanjiv Kumar, Mehryar Mohri, and Ameet Talwalkar. 2012. Sampling methods for the Nyström method. The Journal of Machine Learning Research 13, 1 (2012), 981–1006.

- [31] Liangzhen Lai and Naveen Suda. 2018. Enabling deep learning at the IoT edge (ICCAD '18). Association for Computing Machinery, New York, NY, USA, Article 135, 6 pages. https://doi.org/10.1145/3240765.3243473

- [32] Chengtao Li, Stefanie Jegelka, and Suvrit Sra. 2016. Fast DPP Sampling for Nyström with Application to Kernel Methods. arXiv:1603.06052 [cs.LG] https://arxiv.org/abs/1603.06052

- [33] Chengtao Li, Stefanie Jegelka, and Suvrit Sra. 2016. Fast DPP Sampling for Nyström with Application to Kernel Methods. https://doi.org/10.48550/arXiv. 1603.06052

- [34] Dehua Liang, Jun Shiomi, Noriyuki Miura, and Hiromitsu Awano. 2022. DistriHD: a memory efficient distributed binary hyperdimensional computing architecture for image classification. In 2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC). IEEE, 43–49.

- [35] Dehua Liang, Jun Shiomi, Noriyuki Miura, and Hiromitsu Awano. 2022. DistriHD: A Memory Efficient Distributed Binary Hyperdimensional Computing Architecture for Image Classification. 43–49. https://doi.org/10.1109/ASP-DAC52403.2022.9712589

- [36] Antoine Limasset, Guillaume Rizk, Rayan Chikhi, and Pierre Peterlongo. 2017. Fast and scalable minimal perfect hashing for massive key sets. arXiv preprint arXiv:1702.03154 (2017).

- [37] Fangxin Liu, Haomin Li, Ning Yang, Yichi Chen, Zongwu Wang, Tao Yang, and Li Jiang. 2024. PAAP-HD: PIM-Assisted Approximation for Efficient Hyper-Dimensional Computing. In 2024 29th Asia and South Pacific Design Automation Conference (ASP-DAC). 46–51. https://doi.org/10.1109/ASP-DAC58780.2024. 10473823

- [38] Alec Lu, Zhenman Fang, Weihua Liu, and Lesley Shannon. 2021. Demystifying the Memory System of Modern Datacenter FPGAs for Software Programmers through Microbenchmarking. In The 2021 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (Virtual Event, USA) (FPGA '21). Association for Computing Machinery, New York, NY, USA, 105–115. https://doi.org/10. 1145/3431920.3439284

- [39] Christopher Morris, Nils M. Kriege, Franka Bause, Kristian Kersting, Petra Mutzel, and Marion Neumann. 2020. TUDataset: A collection of benchmark datasets for learning with graphs. arXiv:2007.08663 [cs.LG] https://arxiv.org/abs/2007.08663

- [40] Peer Neubert and Stefan Schubert. 2021. Hyperdimensional computing as a framework for systematic aggregation of image descriptors. In Proceedings of the IEEE/CVF conference on computer vision and pattern recognition. 16938–16947.

- [41] Marion Neumann, Roman Garnett, Christian Bauckhage, and Kristian Kersting. 2016. Propagation kernels: efficient graph kernels from propagated information. Machine learning 102, 2 (2016), 209–245.

- [42] Tony Nowatzki, Vinay Gangadhar, Newsha Ardalani, and Karthikeyan Sankaralingam. 2017. Stream-Dataflow Acceleration. 45, 2 (June 2017), 416–429. https://doi.org/10.1145/3140659.3080255

- [43] Igor Nunes, Mike Heddes, Tony Givargis, Alexandru Nicolau, and Alex Veidenbaum. 2022. GraphHD: efficient graph classification using hyperdimensional

- computing. In Proceedings of the 2022 Conference & Exhibition on Design, Automation & Test in Europe (Antwerp, Belgium) (DATE '22). European Design and Automation Association, Leuven, BEL, 1485–1490.

- [44] NVIDIA Corporation. [n. d.]. NVIDIA System Management Interface (nvidia-smi). https://developer.nvidia.com/nvidia-system-management-interface. Accessed: Sept. 2025.

- [45] Tony A Plate. 1995. Holographic reduced representations. IEEE Transactions on Neural networks 6, 3 (1995), 623–641.

- [46] Ali Rahimi and Benjamin Recht. 2007. Random features for large-scale kernel machines. Advances in neural information processing systems 20 (2007).

- [47] Kaspar Riesen and Horst Bunke. 2008. IAM graph database repository for graph based pattern recognition and machine learning. In Joint IAPR international workshops on statistical techniques in pattern recognition (SPR) and structural and syntactic pattern recognition (SSPR). Springer, 287–297.

- [48] Mahboobe Sadeghipour Roodsari, Jonas Krautter, Vincent Meyers, and Mehdi Tahoori. 2024. E3HDC: Energy Efficient Encoding for Hyper-Dimensional Computing on Edge Devices. In 2024 34th International Conference on Field-Programmable Logic and Applications (FPL). 274–280. https://doi.org/10.1109/ FPL64840.2024.00045