# Artificial Intelligence-Driven Network-on-Chip Design Space Exploration: Neural Network Architectures for Design

Amogh Anshu N, Dept. of Electronics and Communication Engineering UVCE, Bangalore, India B P Harish, Dept. of Electronics and Communication Engineering UVCE, Bangalore, India D

Abstract—Network-on-Chip (NoC) design requires exploring a high-dimensional configuration space to satisfy stringent throughput requirements and latency constraints. Traditional design space exploration techniques are often slow and struggle to handle complex, non-linear parameter interactions. This work presents a machine learning-driven framework that automates NoC design space exploration using BookSim simulations and reverse neural network models. Specifically, we compare three architectures-a Multi-Layer Perceptron (MLP), a Conditional Diffusion Model, and a Conditional Variational Autoencoder (CVAE)—to predict optimal NoC parameters given target performance metrics. Our pipeline generates over 150,000 simulation data points across varied mesh topologies. The Conditional Diffusion Model achieved the highest predictive accuracy, attaining a mean squared error (MSE) of 0.463 on unseen data. Furthermore, the proposed framework reduces design exploration time by several orders of magnitude, making it a practical solution for rapid and scalable NoC co-design.

Index Terms—Network-on-Chip, Design Space Exploration, Artificial Intelligence, Neural Networks, MLP, CVAE, Diffusion Model

## I. INTRODUCTION

ITH the rise of multi-core and many-core processors, Network-on-Chip (NoC) architectures have become the backbone of on-chip communication systems [1]. However, designing an efficient NoC remains a major challenge due to the vast number of configuration parameters and their non-trivial interactions. Designers must often trade off latency, throughput, and power while designing routing algorithms, buffer sizes, virtual channels, for given traffic injection rates [2], [3].

Traditional NoC design methodologies rely heavily on bruteforce simulations or heuristic algorithms, which are computationally expensive and slow to converge, especially for large design spaces [4]. Furthermore, these approaches typically operate in the forward direction—predicting performance from given parameters—but this fails to address a more pressing inverse problem: given desired performance, what are the optimal parameters?

Recent advances in machine learning (ML) offer new tools for automating hardware design [5], [6]. However, most prior work in ML-for-NoC focuses on forward modeling or classification tasks with little attention given to design. [Moreover, few studies compare how different ML models handle the many-to-one mapping that arises in reverse prediction.

#### II. RELATED WORK

An extensive literature survey has been carried out and the state-of-art is presented under the following heads.

## A. Network-on-Chip Design Space Exploration

Traditional NoC design space exploration has relied primarily on simulation-based approaches combined with optimization heuristics. Early work on NoC topology optimization using genetic algorithms, [7], while subsequent research has explored various metaheuristic approaches including particle swarm optimization [8] and simulated annealing [9].

Several analytical models have been proposed to reduce simulation overhead. Queueing theory-based models for NoC performance prediction [10], and support vector regression-based models for latency modeling for NoC [11] have been presented. However, these analytical approaches often sacrifice accuracy for speed, particularly when modeling complex traffic patterns and buffer dynamics.

### B. Machine Learning in Hardware Design

The application of machine learning to hardware design optimization has gained significant traction in recent years. Neural network-based performance prediction for processor architectures have been developed [12]. Earlier literature suggests use of support vector machines for NoC optimization [13], focusing on forward prediction models. More recently, adaptive deep reinforcement learning has been applied to NoC routing algorithm design [14], that failed to address the reverse parameter prediction problem.

## C. Generative Models for Design Optimization

Generative models have shown promise in various design domains. Conditional Variational Autoencoders (CVAEs) have been successfully applied to circuit design [15]. Diffusion models, while newer, have demonstrated superior generation quality in image synthesis [16] and have begun finding applications in engineering design. However, no prior work has systematically compared these generative approaches for NoC parameter optimization, representing a significant gap that the proposed work addresses.

The contributions of the proposed work is summarized as follows:

- 1) Automated Simulation Framework: This paper presents a Python-based framework for large-scale BookSim simulations with efficient configuration generation, parallel execution, and performance parsing.

- 2) Reverse Parameter Prediction: This paper reformulates NoC optimization as a supervised learning problem that predicts parameters from target latency and throughput specifications.

- 3) Architecture Comparison: This paper implements and compares three distinct neural network architectures—MLP, Conditional Diffusion Model, and CVAE—providing insights into their relative strengths for NoC design optimization.

- 4) Comprehensive Evaluation: This paper demonstrates a framework that achieves fast and accurate reverse predictions, reducing manual exploration and paving the way for AI-guided NoC co-design.

The remainder of this paper is organized as follows: Section III describes the methodology and neural network architectures. While Section IV presents the results and analysis, Section V discusses implications and limitations. Section VI concludes with a roadmap for future work.

## III. METHODOLOGY

## A. Problem Formulation

This paper formulates the Network-on-Chip (NoC) design optimization as a reverse prediction problem. Given target performance specifications  $\mathbf{P} = [\text{latency}_{\text{target}}, \text{ throughput}_{\text{target}}]$ , we seek to predict optimal configuration parameters  $\mathbf{X} = [\text{num\_vcs}, \text{ vc\_buf\_size}, \text{ injection\_rate}, \text{ packet\_size}]$  that achieve the desired performance. The variable num\\_vcs refer to the number of virtual channels while vc\\_buf\\_size refers to the buffer size, injection\\_rate refers to the packet injection rate and packet\\_size refers to packet size.

Formally, we learn a mapping function  $f : \mathbf{P} \to \mathbf{X}$  such that when  $\mathbf{X}$  is used in a NoC simulation, the resulting performance  $\mathbf{P}'$  minimizes the distance  $\|\mathbf{P} - \mathbf{P}'\|$ .

## B. Automated Simulation Framework

This paper provides a framework that consists of four main components:

- 1. Configuration Generation: Systematic generation of BookSim configuration files with parameter combinations sampled from predefined ranges.

- 2. Parallel Execution: Multi-process simulation execution using Python's joblib library, with each process handling unique configuration files to avoid conflicts.

- 3. Output Parsing: Robust extraction of performance metrics from BookSim output using regular expressions, handling various output formats and error conditions.

- 4. Data Management: Structured storage of simulation results in pandas DataFrames with comprehensive metadata.

The framework handles over **150000** parameter combinations of 4X4 mesh topologies with dor routing function of BookSim 2.0 and uniform traffic across the following ranges:

• Number of Virtual Channels (num\_vcs): 2–20

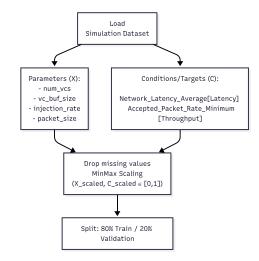

Fig. 1: Data preparation workflow: BookSim simulation outputs are cleaned, scaled, and split for supervised training

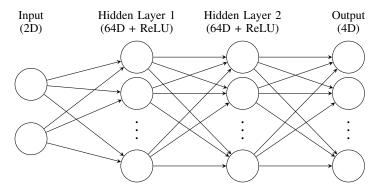

Fig. 2: MLP architecture for reverse NoC parameter prediction. The network maps 2D performance inputs to 4D configuration outputs.

• Buffer Size (vc\_buf\_size): 2–10

• Injection Rate: 0.001–0.1

• Packet Size: 2–10 flits

Fig 1 shows the data processing done post generation of training dataset obtained by multiple BookSim simulations

## C. Neural Network Architectures

#### 1) Multi-Layer Perceptron (MLP)

The baseline approach as shown in Fig 2 uses a simple feedforward neural network to directly learn the mapping from performance targets to NoC parameters. The architecture consists of:

## Input Layer (2 nodes) $\rightarrow$ Hidden Layer (64, ReLU) $\rightarrow$ Hidden Layer (64, ReLU) $\rightarrow$ Output Layer (4 nodes)

where ReLU refers to the Rectified Linear Unit activation function, defined as  $\text{ReLU}(x) = \max(0, x)$ .

Let  $\mathbf{y} \in \mathbb{R}^2$  denote the input vector representing the performance targets (i.e. latency and throughput), and  $\hat{\mathbf{x}} \in \mathbb{R}^4$  be the predicted NoC parameter vector. The MLP learns a function  $f_{\theta} : \mathbb{R}^2 \to \mathbb{R}^4$  parameterized by  $\theta$  such that:

$$\hat{\mathbf{x}} = f_{\theta}(\mathbf{y}) = W_2 \, \sigma(W_1 \, \sigma(W_0 \mathbf{y} + \mathbf{b}_0) + \mathbf{b}_1) + \mathbf{b}_2 \quad (1)$$

where  $W_i$  and  $\mathbf{b}_i$  are the weight matrices and biases for layer i,  $\sigma(\cdot)$  is the ReLU activation function and  $\theta$  is the set of all learnable parameters

The model is trained to minimize the mean squared error (MSE) between the predicted and true parameters:

$$\mathcal{L}_{\text{MSE}} = \frac{1}{N} \sum_{i=1}^{N} \left\| \hat{\mathbf{x}}^{(i)} - \mathbf{x}^{(i)} \right\|^2$$

(2)

where  $\mathbf{x}^{(i)}$  is the ground-truth parameter vector for the *i*-th sample in a dataset of size N.

## 2) Conditional Variational Autoencoder (CVAE)

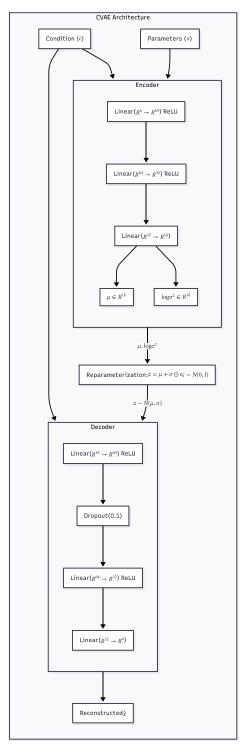

The CVAE [17] learns a latent representation of the parameter space conditioned on performance targets such as latency and throughput. Fig 3 shows the architecture of the proposed CVAE model.

Let  $\mathbf{x} \in \mathbb{R}^d$  denote a NoC parameter vector, and  $\mathbf{y} \in \mathbb{R}^2$  the corresponding performance targets. The goal is to model the conditional distribution  $p(\mathbf{x} \mid \mathbf{y})$ .

• **Encoder**: Maps the concatenated vector  $[\mathbf{x}, \mathbf{y}]$  to a latent Gaussian distribution:

$$q_{\phi}(\mathbf{z} \mid \mathbf{x}, \mathbf{y}) = \mathcal{N}(\mathbf{z} \mid \boldsymbol{\mu}_{\phi}(\mathbf{x}, \mathbf{y}), \operatorname{diag}(\boldsymbol{\sigma}_{\phi}^{2}(\mathbf{x}, \mathbf{y})))$$

(3)

where  $\mu_{\phi}$  and  $\sigma_{\phi}$  are neural networks parameterized by  $\phi$  where  $\phi$  is the set of learnable parameters.

• Reparameterization: A sample z is obtained via:

$$\mathbf{z} = \boldsymbol{\mu}_{\phi} + \boldsymbol{\sigma}_{\phi} \odot \boldsymbol{\epsilon}, \quad \boldsymbol{\epsilon} \sim \mathcal{N}(0, \mathbf{I})$$

(4)

• **Decoder**: Given the sampled latent code **z** and condition **y**, reconstructs the parameters:

$$p_{\theta}(\mathbf{x} \mid \mathbf{z}, \mathbf{y}) = \mathcal{N}\left(\mathbf{x} \mid \hat{\mathbf{x}}_{\theta}(\mathbf{z}, \mathbf{y}), \sigma^{2} \mathbf{I}\right)$$

(5)

where  $\hat{\mathbf{x}}_{\theta}$  is the decoder neural network.

• **Loss Function**: The objective combines a reconstruction term and a KL divergence regularization:

$$\mathcal{L}(\theta, \phi) = \mathbb{E}_{q_{\phi}(\mathbf{z}|\mathbf{x}, \mathbf{y})} \left[ \|\mathbf{x} - \hat{\mathbf{x}}_{\theta}(\mathbf{z}, \mathbf{y})\|^{2} \right] + \beta \cdot \text{KL} \left( q_{\phi}(\mathbf{z} \mid \mathbf{x}, \mathbf{y}) \| \mathcal{N}(0, \mathbf{I}) \right)$$

(6)

where  $\beta$  is a KL weight annealed during training to stabilize learning.

## 3) Conditional Diffusion Model

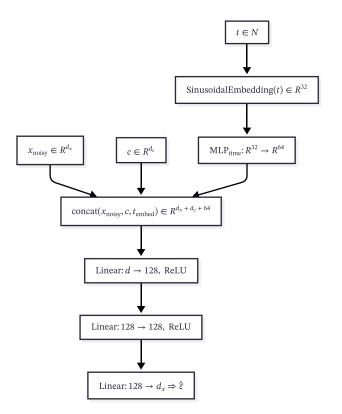

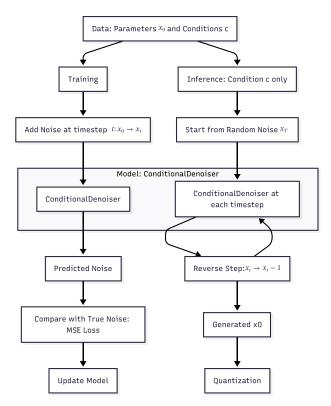

A denoising diffusion model's [16] conditional parameter generation is applied as shown in Fig 4. The model learns to denoise parameter configurations conditioned on target performance:

- Forward Process: Gradually adds Gaussian noise to parameter vectors over T=1000 timesteps.

- **Reverse Process**: A neural network learns to predict and remove noise conditioned on performance targets.

Fig. 3: Architecture of Conditional Variational Autoencoder (CVAE) with encoder-decoder design.

Architecture: Time embeddings combined with condition vectors, processed through multilayer perceptrons (MLPs).

Fig 5 shows the end-to-end training and inference flow of the conditional diffusion model.

Mathematically, let  $\mathbf{x}_0 \in \mathbb{R}^d$  denote a clean NoC parameter vector, and  $\mathbf{y} \in \mathbb{R}^2$  the target performance condition (e.g.,

Fig. 4: Conditional diffusion model: a denoising neural network learns to reverse noisy parameter vectors conditioned on performance metrics.

latency, throughput). The forward process corrupts  $\mathbf{x}_0$  with Gaussian noise as:

$$\mathbf{x}_t = \sqrt{\bar{\alpha}_t} \, \mathbf{x}_0 + \sqrt{1 - \bar{\alpha}_t} \, \boldsymbol{\epsilon}, \quad \boldsymbol{\epsilon} \sim \mathcal{N}(0, \mathbf{I})$$

(7)

where  $\alpha_t = 1 - \beta_t$  and  $\bar{\alpha}_t = \prod_{s=1}^t \alpha_s$  is the cumulative product of the noise scales.

A neural network  $\epsilon_{\theta}(\mathbf{x}_t, \mathbf{y}, t)$  is trained to predict the noise  $\epsilon$  via the loss:

$$\mathcal{L}_{\text{MSE}} = \mathbb{E}_{\mathbf{x}_0, \mathbf{y}, \boldsymbol{\epsilon}, t} \left[ \| \boldsymbol{\epsilon} - \boldsymbol{\epsilon}_{\theta}(\mathbf{x}_t, \mathbf{y}, t) \|^2 \right]$$

(8)

During generation, the reverse process recursively denoises samples from a Gaussian prior using:

$$\mathbf{x}_{t-1} = \frac{1}{\sqrt{\alpha_t}} \left( \mathbf{x}_t - \frac{1 - \alpha_t}{\sqrt{1 - \bar{\alpha}_t}} \, \boldsymbol{\epsilon}_{\theta}(\mathbf{x}_t, \mathbf{y}, t) \right) + \sqrt{\beta_t} \, \mathbf{z}, \quad \mathbf{z} \sim \mathcal{N}(0, \mathbf{I})$$

(9)

Sinusoidal time embeddings  $\gamma(t) \in \mathbb{R}^{d_t}$  are used to encode timestep information and are concatenated with  $\mathbf{x}_t$  and  $\mathbf{y}$  before input to the denoising network.

## D. Training and Evaluation

All models are trained using the Adam optimizer with learning rates tuned to individual architectures. We employ a 80% - 20% train - validation split and monitor convergence through validation loss. For discrete parameters (num\_vcs, vc\_buf\_size, packet\_size), we apply post-processing quantization / clamping to ensure valid configurations.

Fig. 5: End-to-end training and inference flow of the conditional diffusion model with noise schedule and iterative denoising.

## IV. RESULTS AND ANALYSIS

### A. Model Overview

Table I compares the architectural and operational features of the three models evaluated. The MLP acts as a deterministic baseline, while CVAE and diffusion are generative models capable of producing multiple parameter configurations for the same performance target. This ability is critical in reverse modeling where many-to-one mappings naturally arise due to hardware design degeneracy.

TABLE I: Model Architecture Comparison

| Feature                 | MLP               | CVAE                  | Diffusion             |

|-------------------------|-------------------|-----------------------|-----------------------|

| Architecture            | Feedforward MLP   | Conditional VAE       | Conditional DDPM      |

| Output Type             | Single prediction | Multiple samples      | Multiple samples      |

| Probabilistic           | No                | Yes                   | Yes                   |

| Discrete Param Handling | Post-hoc clamping | Post-hoc clamping     | Post-hoc quantization |

| Design Space Coverage   | Low               | Moderate              | High                  |

| Sampling Method         | -                 | Decoder with latent z | Iterative denoising   |

## B. Training and Validation Performance

All models were trained using MSE loss on parameter values, with results shown in Table II. The MLP achieves the lowest loss due to its direct mapping and absence of sampling variance. The CVAE exhibits comparable performance, though minor KL divergence instability was observed. The diffusion model shows slightly higher loss due to added noise during training but provides more flexible sampling at inference time.

TABLE II: Final Epoch Metrics of Training Loop

| Metric          | MLP    | CVAE   | Diffusion      |

|-----------------|--------|--------|----------------|

| Training Loss   | 0.0466 | 0.0470 | 0.0651 (noise) |

| Validation Loss | 0.0467 | 0.0471 | 0.0664 (noise) |

While these metrics reflect learning performance, in order to fully capture the real-world usefulness of the predicted parameters, BookSim-based simulations are considered.

## C. BookSim-Based Evaluation of Reverse Models

To evaluate the functional accuracy of the predicted NoC parameters, we simulate each model's output using BookSim and compare the resulting latency and throughput against the original target. Generative models (CVAE and diffusion) generate 10 samples per target, and the best-performing configuration is selected based on simulation error.

TABLE III: BookSim Evaluation of Reverse Models (100 Samples)

| Model       | MSE (Latency)         | MSE (Throughput)     | Total MSE            |

|-------------|-----------------------|----------------------|----------------------|

| MLP<br>CVAE | 2.824043<br>10.288263 | 0.000002<br>0.000004 | 1.412023<br>5.144134 |

| Diffusion   | 0.926223              | 0.000005             | 0.463114             |

As shown in Table III, the diffusion model achieves the lowest average MSE across both latency and throughput. It outperforms both MLP and CVAE by effectively exploring diverse configurations and selecting the most accurate match. The MLP, though computationally efficient, is constrained by its single prediction and performs poorly in scenarios with multiple valid designs. The CVAE, while generative, struggles with variance and conditioning, often producing suboptimal parameter sets.

#### D. Discussion

- MLP offers speed and simplicity but lacks flexibility in handling multiple valid outputs per target.

- **CVAE** demonstrates the value of sampling but suffers from high error variance and latent space instability.

- Diffusion balances diversity and accuracy, enabling it to better handle the many-to-one nature of the reverse mapping.

These results highlight the limitations of deterministic models in reverse prediction and demonstrate the potential of generative architectures in capturing design degeneracy. However, the reliance on post-hoc simulation for validation points to a key area for improvement, discussed further in Section VI.

## V. IMPLICATIONS AND LIMITATIONS

## A. Implications

Reverse design automation: This work demonstrates the feasibility of using AI models to infer NoC configuration parameters directly from target performance

- metrics, enabling faster and automated early-stage design exploration.

- Performance-aware evaluation: The integration of BookSim-based simulation into the evaluation process allows post-hoc validation of generated configurations, bridging the gap between model predictions and realworld NoC performance in terms of latency and throughput.

- Support for design diversity: Generative models such as the CVAE and diffusion models enable sampling of multiple valid configurations for the same performance target, which is critical in the presence of many-to-one mappings.

- Differentiable optimization: This work lays the foundation for incorporating differentiable surrogates or blackbox optimization into training, enabling end-to-end finetuning with respect to actual performance metrics.

#### B. Limitations

- Post-hoc performance evaluation: The models are trained using MSE loss on parameter values, while performance metrics are only evaluated post-training via Book-Sim. This introduces a mismatch between the training objective and deployment criteria.

- Non-differentiable simulation engine: BookSim is nondifferentiable and cannot be used for gradient-based optimization. This limits its integration in end-to-end training unless approximated by a differentiable surrogate model.

- Handling of discrete variables: NoC parameters such as buffer size and number of virtual channels are discrete by nature. Rounding and clamping which are used during inference can introduce errors in a best-case scenario or invalid configurations in a worst-case scenario.

- Underperformance of CVAE: Despite its generative capability, the CVAE model underperformed in simulation-based evaluation, likely due to posterior collapse or insufficient latent conditioning, warranting future investigation.

- Limited evaluation metrics: The current evaluation focuses solely on latency and throughput. Other critical design metrics such as power, area, and thermal constraints are not considered, limiting the framework's applicability in holistic NoC co-design.

## VI. FUTURE WORK

While the current framework evaluates the quality of reverse predictions using BookSim post hoc, future efforts can incorporate latency and throughput optimization directly into the training loop, either by using a BookSim surrogate model or by fine tuning with BookSim-in-the-loop.

## REFERENCES

- [1] L. Benini and G. De Micheli, "Networks on chips: A new SoC paradigm," *Computer*, vol. 35, no. 1, pp. 70–78, Jan. 2002.

- [2] W. J. Dally and B. Towles, "Route packets, not wires: On-chip interconnection networks," in *Proc. 38th Design Automation Conference (DAC)*, Las Vegas, NV, USA, Jun. 2001, pp. 684–689.

- [3] A. Hemani, A. Jantsch, S. Kumar, A. Postula, J. Öberg, M. Millberg, and D. Lindqvist, "Network on chip: An architecture for billion transistor era," in *Proc. IEEE NorChip Conference*, Nov. 2000, pp. 166–173.

- [4] N. Jiang, D. U. Becker, G. Michelogiannakis, J. Balfour, B. Towles, D. E. Shaw, J. Kim, and W. J. Dally, "A detailed and flexible cycle-accurate Network-on-Chip simulator," in *Proc. IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS)*, Austin, TX, USA, Apr. 2013, pp. 86–96.

- [5] A. Agnesina, K. Chandrasekar, B. Chatterjee, T. Krishna, and S. Mukhopadhyay, "Machine learning for design space exploration and optimization of manycore systems," *IEEE Transactions on Multi-Scale Computing Systems*, vol. 5, no. 2, pp. 131–138, Apr. 2019.

- [6] H. Sharma, J. Park, D. Mahajan, E. Amaro, J. K. Kim, C. Shao, A. Mishra, and H. Esmaeilzadeh, "From high-level deep neural models to FPGAs," in *Proc. 49th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO)*, Taipei, Taiwan, Oct. 2016, pp. 1–12.

- [7] Asadi, Y. A comprehensive study and holistic review of empowering network-on-chip application mapping through machine learning techniques. Discov Electron 1, 22 (2024). https://doi.org/10.1007/s44291-024-00027-w

- [8] Huang C, Zhang D, Song G. Low-power mapping algorithm for three-dimensional network-on-chip based on diversitycontrolled quantum-behaved particle swarm optimization. Journal of Algorithms and Computational Technology. 2016;10(3):176-186. doi:10.1177/1748301816649070

- [9] Yang, B., Guang, L., Säntti, T., Plosila, J. (2012). Parameter-Optimized Simulated Annealing for Application Mapping on Networks-on-Chip. In: Hamadi, Y., Schoenauer, M. (eds) Learning and Intelligent Optimization. LION 2012. Lecture Notes in Computer Science, vol 7219. Springer, Berlin, Heidelberg.

- [10] Sumit K. Mandal, Raid Ayoub, Michael Kishinevsky, and Umit Y. Ogras. 2019. Analytical Performance Models for NoCs with Multiple Priority Traffic Classes. ACM Trans. Embed. Comput. Syst. 18, 5s, Article 52 (October 2019), 21 pages. https://doi.org/10.1145/3358176

- [11] Z. -L. Qian, D. -C. Juan, P. Bogdan, C. -Y. Tsui, D. Marculescu and R. Marculescu, "A Support Vector Regression (SVR)-Based Latency Model for Network-on-Chip (NoC) Architectures," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 35, no. 3, pp. 471-484, March 2016, doi: 10.1109/TCAD.2015.2474393.

- [12] P. Mendez, O. Bai, S. Jain, and M. Qureshi, "Pythia: A customizable hardware prefetching framework using online reinforcement learning," in *Proc. 54th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO)*, Virtual Event, Oct. 2021, pp. 1121–1137.

- [13] Weng, Xiaodong, Yi Liu, Changqing Xu, Xiaoling Lin, Linjun Zhan, Shunyao Wang, Dongdong Chen, and Yintang Yang. 2023. "A Machine Learning Mapping Algorithm for NoC Optimization" Symmetry 15, no. 3: 593. https://doi.org/10.3390/sym15030593

- [14] Reshma Raj R.S., Rohit R., Mushrif Shaikh Shahreyar, Akash Raut, Pournami P.N., Saidalavi Kalady, Jayaraj P.B., DeepNR: An adaptive deep reinforcement learning based NoC routing algorithm, Microprocessors and Microsystems, Elsevier BV, 2022, https://doi.org/10.1016/j.micpro.2022.104485

- [15] R. Kawamata, S. Wakao and N. Murata, "Application of Conditional Variational Auto-Encoder to Magnetic Circuit Design with Magnetic Field Computation," 2019 22nd International Conference on the Computation of Electromagnetic Fields (COMPUMAG), Paris, France, 2019, pp. 1-4, doi: 10.1109/COMPUMAG45669.2019.9032766.

- [16] J. Ho, A. Jain, and P. Abbeel, "Denoising diffusion probabilistic models", Proc. Advances in Neural Information Processing Systems (NeurIPS), vol. 33, Dec. 2020, pp. 6840–6851.

- [17] D. P. Kingma and M. Welling, "Auto-Encoding Variational Bayes", arXiv preprint arXiv:1312.6114, 2014. [Online], https://arxiv.org/abs/1312.6114