# LAPA: Log-Domain Prediction-Driven Dynamic Sparsity Accelerator for Transformer Model

Huizheng Wang

School of Integrated Circuits

Tsinghua University

Beijing, China

wanghz22@mails.tsinghua.edu.cn

Hongbin Wang

School of Integrated Circuits

Tsinghua University

Beijing, China

wanghb24@mails.tsinghua.edu.cn

Shaojun Wei

School of Integrated Circuits

Tsinghua University

Beijing, China

wsj@tsinghua.edu.cn

Yang Hu

School of Integrated Circuits

Tsinghua University

Beijing, China

hu\_yang@tsinghua.edu.cn

Shouyi Yin

School of Integrated Circuits

Tsinghua University

Beijing, China

Shanghai Artificial Intelligence Laboratory

Shanghai, China

yinsy@tsinghua.edu.cn

Abstract-Attention-based Transformers have revolutionized natural language processing (NLP) and shown strong performance in computer vision (CV) tasks. However, as the input sequence varies, the computational bottlenecks in Transformer models exhibit dynamic behavior across stages, which calls for a cross-stage sparse acceleration strategy. Unfortunately, most existing sparse Transformer approaches are single-stage based, and their sparsity prediction mechanisms lead to significant power overhead when applied across multiple stages. To this end, this paper proposes a log-domain attention prediction algorithmarchitecture co-design, named LAPA. First, an asymmetric leading one computing (ALOC) scheme is designed to eliminate expensive multiplications. Next, a mixed-precision multi-round shifting accumulation (MRSA) mechanism is further proposed to mitigate the accumulation overhead. A data-feature dependent filter (DDF) strategy is designed to work in concert with the MRSA process. Finally, an elaborate accelerator is designed to translate the theoretical enhancement into practical hardware improvement. Experimental results show that LAPA achieves  $3.52\times$ ,  $3.24\times$  and  $2.79\times$  higher energy efficiency than the stateof-the-art (SOTA) works Spatten, Sanger and FACT, respectively.

Index Terms—Transformers, dynamic sparsity, low complexity.

#### I. INTRODUCTION

Benefiting from the powerful *self-attention* mechanism [1], Transformer models have achieved remarkable advances in a spectrum of tasks, spanning from text generation [2] to computer vision (CV) [3]. However, such enhanced performance comes with an overwhelming computation burden. For example, although the vision Transformer G with patch 14 (ViT-G/14) [4], achieves an accuracy of 90.45% on ImageNet [5], showing a significant gain than non-Transformer model BiT-L (87.54%) [6], the computation of the former is 21.3× that of the latter. Such significant computational workloads necessitate the design of accelerators tailored for Transformers.

Corresponding authors: Yang Hu (hu\_yang@tsinghua.edu.cn)

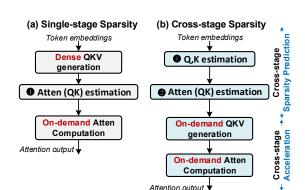

Fig. 1. Traditional single-stage sparsity and proposed cross-stage sparsity.

However, a key challenge in efficiently accelerating Transformers lies in the presence of dynamic computational bottlenecks [7-11]. Specifically, each attention block requires the computation of three matrices, i.e., Ouery (O), Key (K), and Value (V), to capture pairwise dependencies among tokens within a given sequence. To enable this, these matrices are first generated through a linear projection stage, commonly referred to as QKV generation. However, the computational complexity of QKV generation is  $O(SH^2)$ , while the subsequent attention computation incurs a complexity of  $O(S^2H)$ , where S denotes the sequence length and H is the hidden dimension. As a result, the dominant computation bottleneck varies with the input characteristics. For tasks involving long sequences [12] or high-resolution images [13], attention operations can account for 48.3% to 90.4% of the total computation. In contrast, for short-sequence tasks [14], the attention module contributes less than 20\%, with the linear projection becoming the primary computation bottleneck. Therefore, there is a pressing need for a versatile accelerator capable of efficiently handling both attention and linear projection computations.

Unfortunately, most existing efforts [15–21] on Transformer

sparsity focus exclusively on accelerating the attention, with limited consideration for the linear projection. To identify runtime attention sparsity, early approaches often relied on affine approximations. For instance, A<sup>3</sup> [22] employs progressive approximation, while ELSA [23] adopts hash-based techniques. However, these methods typically involve iterative processing, leading to significant latency overhead. To mitigate this, more recent works such as DOTA [24], Energon [25], and Sanger [26] adopt half-MSB-based computation (e.g., 4 bit). Nonetheless, these approaches suffer from substantial power consumption during prediction. In addition, methods like SpARC [27] and CLAT [28] simplify attention by clustering Queries. However, they rely on prior calibration, which restricts their applicability. Moreover, they cannot be extended to linear projection scenarios. While FACT [29] realizes the challenges of the dynamic computation bottleneck and attempts to address them, its symmetric leading-one scheme introduces significant estimation inaccuracies.

To this end, this paper proposes a Cross-Stage Sparsity (CSS) strategy. As depicted in Fig. 1, unlike traditional single-stage sparsity prediction, CSS first speculates the  $\hat{\mathbf{Q}}$  and  $\hat{\mathbf{K}}$  matrices. Based on these speculative representations, it then predicts the attention ( $\hat{\mathbf{Q}} \times \hat{\mathbf{K}}$ ), and generates a sparse attention mask. Finally, only a small subset of  $\mathbf{Q}$ ,  $\mathbf{K}$ , and  $\mathbf{V}$  is generated on demand according to the mask. This approach enables the pruning of both the linear projection and attention computation associated with unimportant QKV elements.

Despite its promise, leveraging the CSS strategy imposes several significant challenges: First, there is a lack of a low-power prediction paradigm well-suited for cross-stage **processing.** While prior works on attention sparsity have explored low-power designs, such as hash-based approximation [23] and half-MSB speculation [26, 30], these approaches are limited to single-stage optimization, specifically the attention acceleration. As a result, they fail to exploit critical optimization opportunities across stages, rendering their prediction paradigms ineffective in cross-stage scenarios. Second, there is a lack of a low-power token selection strategy tailored for cross-stage processing. As cross-stage sparsity reduces the cost of formal computation, token selection emerges as a main contributor to power consumption. Our characterization shows that existing methods, such as top-k sorting [30], can account for up to 30% of the total power overhead in cross-stage settings. This underscores the necessity for a more efficient and low-power token selection technique.

This paper proposes LAPA, a novel software-hardware codesign to accelerate both linear projection and attention in a cross-stage manner. Our contributions include:

- 1) An efficient asymmetric leading one computing (ALOC) scheme to eliminate costly multiplications, while preserving acceptable cross-stage estimation accuracy. Moreover, the pre-known nature of weights during inference is leveraged to further reduce leading-one conversion overhead.

- 2) A log-domain based multi-round shift accumulation (MRSA) scheme to progressively select the important token-pairs for decreasing overhead. To avoid accumulation

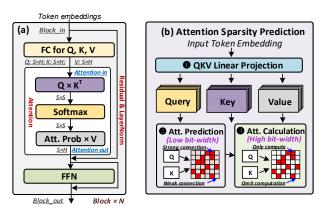

Fig. 2. The illustration for Transformer architecture and attention prediction.

becoming a bottleneck, MRSA employs a progressive multiround accumulation strategy combined with early-termination pruning, effectively reducing the overall accumulation overhead required for estimation.

- 3) Data-feature dependent filtering (DDF) mechanism. Leveraging the argmax property of softmax, DDF employs a simple threshold generation strategy to enable efficient pruning in MRSA, thereby reducing the estimation overhead.

- 4) Dedicated accelerator for practical acceleration. To translate the theoretical improvement into practical performance gains, we design a customized accelerator, LAPA, to support the proposed strategies. LAPA achieves  $3.52\times$ ,  $3.24\times$ , and  $2.79\times$  gains in energy efficiency over state-of-the-art (SOTA) Transformer accelerators, Spatten, Sanger and FACT.

#### II. BACKGROUND AND MOTIVATION

# A. Transformer Architecture

A typical Transformer architecture consists of multiple stacked blocks, as shown in Fig. 2 (a). Initially, the token embedding matrix  $\mathbf{X}$  is linearly projected into the query ( $\mathbf{Q}$ ), key ( $\mathbf{K}$ ) and value ( $\mathbf{V}$ ) as defined in Eq. (1). Then, the  $\mathbf{Q}$ ,  $\mathbf{K}$  and  $\mathbf{V}$  matrices are processed by the self-attention mechanism as shown in Eq. (2), where  $\mathbf{A}$  denotes the attention score matrix. Further, the attention output is computed by multiplying the  $\mathbf{S}$  with  $\mathbf{V}$ . Notably, both the QK and SV computations have a complexity of  $O(S^2H)$ . The resulting intermediate results are passed through an FFN with two fully connected layers, yielding the final outputs.

$$\mathbf{Q}, \mathbf{K}, \mathbf{V} = \mathbf{X} \mathbf{W}_{\mathbf{Q}}, \mathbf{X} \mathbf{W}_{\mathbf{K}}, \mathbf{X} \mathbf{W}_{\mathbf{V}}. \tag{1}$$

$$\mathbf{S} = \operatorname{softmax} \left( \mathbf{Q} \mathbf{K}^T / \sqrt{d_k} \right), \text{ where } \mathbf{A} = \mathbf{Q} \mathbf{K}^T.$$

(2)

# B. Dynamic Attention Sparsity

The quadratic complexity of self-attention arises from its fully-connected attention graph, where all Q-K pairs are computed. However, not all connections contribute equally to the final output [8]. Prior work [24] has shown that sparse attention graphs, by excluding weak connections, can achieve performance comparable to full attention. Therefore, leveraging input-dependent dynamic sparsity presents a promising approach to reduce the computational burden of self-attention.

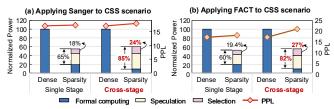

Fig. 3. Power breakdown for dense attention, single-stage sparsity attention, cross-stage sparsity attention on Llama 7B with Wikitext dataset, with TSMC 28nm CMOS. Directly applying (a) Sanger's (b) FACT's, prediction strategies to cross-stage sparsity prediction.

Fig. 2 (b) illustrates the traditional workflow for attention acceleration by leveraging dynamic sparsity. First, the Q, K, V matrices are computed in a dense manner ①. Next, in the prediction stage ②, approximation schemes (e.g., 4-bit MSB) are utilized to speculate the attention distribution and generate a mask identifying the important Q-K pairs. Finally, in the formal calculation stage ③, high-precision operations (e.g., 16bit) are applied selectively to these critical Q-K pairs based on the predicted mask. However, such single-stage sparsity enables acceleration only for the attention computation, but fails to optimize the QKV generation process.

# C. Motivation

As discussed in Section I, variations in sequence length can cause the computational bottleneck in Transformers to shift between the attention mechanism and the linear projection layers. Therefore, a versatile Transformer accelerator must be capable of efficiently accelerating both components. We propose the cross-stage sparsity (CSS) strategy, which extends traditional attention sparsity to the QKV linear projections, thereby enabling sparsity acceleration across both stages. However, through a careful re-examination of existing attention sparsity techniques [24, 26, 29, 30], we observe that naively applying their prediction paradigms to the cross-stage setting results in either substantial prediction power overhead or significant accuracy degradation.

Sanger [26] and FACT [29] are SOTA and representative accelerators targeting dynamic attention sparsity. Sanger employs 4-bit MSB prediction combined with static threshold comparison, while FACT utilizes log-domain shifting followed by top-k sorting. Fig. 3 evaluates the power consumption and perplexity (PPL, lower is better) when applying the speculation strategies of Sanger and FACT to cross-stage sparsity prediction. As revealed by Fig. 3(a), under single-stage sparsity, Sanger's strategy successfully reduces formal computing to approximately 20\% of that in the dense case, while maintaining comparable PPL. In this setting, the prediction overhead, comprising speculation, i.e.,  $\hat{\bf Q} \times \hat{\bf K}$  and token selection, accounts for around 65% of the total power. However, when applied to the cross-stage scenario, further reduction in formal computing leads to the prediction overhead rising to 85\%, with token selection alone contributing approximately 24%.

On the other hand, when applying the FACT approach to cross-stage sparsity prediction, the logarithmic-domain shifting method effectively reduces speculation overhead. However, due to its larger approximation error, it leads to a noticeable

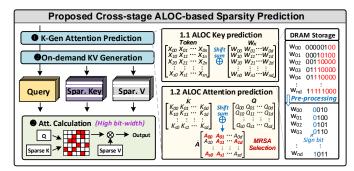

Fig. 4. Illustration of the ALOC-based Cross-stage sparsity (CSS) prediction.

degradation in PPL, approximately 20% higher than the dense baseline. To make things worse, it is observed that prediction overhead accounts for as much as 82% of the total power consumption, with token selection alone contributing 27%.

The significant power overhead presents a major obstacle to the effective implementation of cross-stage sparsity. Therefore, enabling efficient cross-stage sparsity prediction necessitates a low-power approximation paradigm, coupled with an equally energy-efficient token selection strategy.

#### III. ALGORITHM OPTIMIZATIONS OF LAPA

To address the severe power overhead challenges posed by supporting the CSS strategy, we propose three key techniques. First, ALOC is carefully designed to exploit the known-weight property in cross-stage scenarios, effectively reducing the overhead of leading-one conversion while maintaining high prediction accuracy. Secondly, MRSA adopts a multi-round filtering mechanism to progressively identify important tokens, thereby reducing power consumption. Finally, a simple yet effective thresholding scheme is introduced to further enhance the efficiency of MRSA.

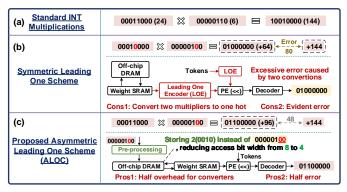

# A. Proposed Low-complexity ALOC Scheme

We design an asymmetric leading one computing (ALOC) scheme, where *asymmetric* refers to the transformation of only one operand into the logarithmic domain using a leading-one encoder (LOE) to extract its leading-one (LO) position. Based on this LO value, the original multiplication is approximated by low-power shift operations applied to the other operand, thereby eliminating the need for costly multipliers. Specifically, an INT-type number *y* can be expressed as in Eq. (3):

$$y = Sign \cdot M \cdot 2^{LO},\tag{3}$$

where M denotes the mantissa within [1,2), LO denotes the leading-one position of y within [0,W-1), and W denotes the bit-width. The corresponding multiplication is derived in Eq. (4a) and approximated as Eq. (4b). Since the bit width W is fixed, we can directly operate  $LO_y$  on x, to estimate the magnitude for the product of two numbers. Therefore, by incorporating shifting and the sign bit, the multiplication result can be predicted.

$$x \times y = \text{XOR}(S_x, S_y) \cdot \left(M_x \cdot 2^{LO_x}\right) \cdot \left(M_y \cdot 2^{LO_y}\right)$$

(4a)

$$\approx \text{XOR}(S_x, S_y) \cdot M_x \cdot 2^{LO_x + LO_y}$$

(4b)

Fig. 5. Comparison of the proposed ALOC with the vanilla symmetric leading one scheme used in [29].

Based on the ALOC scheme, the workflow of CSS is depicted in Fig. 4. As the weights are pre-known and fixed during inference, we pre-convert the  $W_K$  and  $W_O$  into LO format and store them. Then, in the Query and Key Prediction phase (1.1), no LOE is required, as the weights  $W_K$  and  $\mathbf{W}_{Q}$  have been converted into LO format. In the subsequent Attention Prediction phase (1.2), to avoid amplifying approximation error, we convert  $\hat{\mathbf{Q}}$  into log domain instead of  $\hat{\mathbf{K}}$ , then perform shifting and sum operations. As depicted in Fig. 5, compared to the vanilla symmetric leading one strategy used in FACT [29], the proposed ALOC offers three key advantages: a) Lower conversion overhead. This is because ALOC performs the leading-one conversion on only one multiplier, while the conventional approach needs to process both. b) Higher accuracy. This is because the error of the leading-one scheme originates from the loss of information carried by the bits following the most significant '1'. Since ALOC performs the leading-one conversion on only one multiplier, it introduces less error and achieves higher precision. c) Reduced memory access. The reduction in memory access stems from the fact that ALOC only requires loading a 4-bit LO value that has been offline converted, whereas the vanilla symmetric leading one scheme loads the full 8-bit operand.

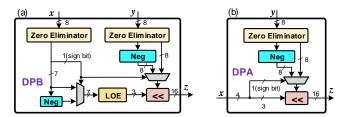

However, since the shifted results require sign detection and conversion into two's complement form for subsequent accumulation, the naive implementation of ALOC introduces significant bit-flipping overhead, which may even offset the benefits of the ALOC scheme. To efficiently support ALOC, we introduce two specialized types of processing elements (PEs) and a *sign pre-assign* mechanism. The architectural details are discussed in Section IV.

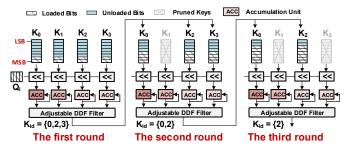

# B. Multi-round Shift Accumulation (MRSA)

The ALOC strategy reduces the cost of multiplications by leveraging low-cost shift operations. However, this optimization shifts the computational bottleneck to the addition tree, which incurs significant overhead. While directly applying low-bit quantization is a feasible solution, it is a coarse-grained approach that can significantly degrade model accuracy.

To address this limitation, we propose the mixed-precision MRSA strategy. Considering execution efficiency, MRSA is applied during the attention estimation stage. As illustrated

Fig. 6. Illustration for the proposed MRSA strategy with three filtering rounds.

in Fig. 6, for each query  $\hat{\mathbf{Q}}_i$  (in LO format), we identify significant Keys through multiple filtering rounds. Instead of employing the traditional one-shot top-k pruning [30] with low precision tensors, MRSA iteratively refines the selection via repeated filtering. Its workflow is exemplified in Fig. 6.

Initially, we utilize partial bits of Keys (e.g., high-order 2bit) to speculate  $\mathbf{Q}\mathbf{K}^T$  and select pairs with relatively large scores. It is worth noting that although the low-bit speculation is not highly accurate, it remains effective in identifying significantly different values, such as the top 50%. In the subsequent rounds, MRSA conducts incremental filtering based on the selected pairs from the previous round. As the remaining pairs tend to have closer scores, it uses higher precision (e.g., an additional 2 bits) to further compute the dot product of the remaining Q-K pairs. This filtering process is carried out iteratively until a predefined number of rounds is reached. After the last round, the ultimately selected keys in each row are utilized for performing on-demand QKV generation and high-precision sparse attention.

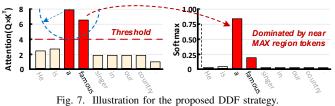

#### C. Adjustable Data-feature Dependent Filtering (DDF)

The MRSA employs mixed precision for multiple rounds of filtering, making it crucial to reduce the overhead of each comparison in each round. Instead of directly sorting all the scores, we introduce the concept of a spherical radius to pick up the important scores. This is based on the following observations. As Fig. 7 shows, the softmax would exponentially exaggerate the difference among the values of the inputs. Therefore, the output of the softmax operation is primarily determined by the input's maximum value and its neighboring values. That is to say, it is sufficient to selectively retain values that are close to the maximum. To this end, we design an efficient data-feature-dependent filtering mechanism, which employs a max-value-centric threshold. The threshold is formally defined in Eq. (5):

$$\phi_{i}^{r} = \max\left(\mathbf{A}_{i}^{r}\right) - \eta^{r} \times \left(\max\left(\mathbf{A}_{i}^{r}\right) - \min\left(\mathbf{A}_{i}^{r}\right)\right), \eta^{r} \in [0, 1],$$

(5)

where  $\mathbf{A}_i^r$  denotes the attention scores of the ith row. To flexibly balance accuracy and pruning ratio for different application demands, we introduce a parameter  $\eta^r$  to control the threshold, whose value range is [0,1]. By adjusting  $\eta^r$ , the threshold transits from  $\max{(\mathbf{A}_i^r)}$  to  $\min{(\mathbf{A}_i^r)}$ . Thus, we can control the pruning ratio in each round from 0% to 100%.

# Algorithm 1: Proposed CSS Mechanism. 1 Input: $\mathbf{x}_{i} \in \mathbb{R}^{1 \times H}$ , $\mathbf{W}_{Q}$ , $\mathbf{W}_{K} \in \mathbb{R}^{H \times H}$ , R; 2 Preprocessing: $\mathbf{E}^{\mathbf{W}_{Q}} \leftarrow \text{LOE}(\mathbf{W}_{Q})$ ; $\mathbf{E}^{\mathbf{W}_{K}} \leftarrow \text{LOE}(\mathbf{W}_{K})$ ; 3 $\hat{\mathbf{Q}}_{ij} \leftarrow \sum_{k} \left( \text{Sgn} \left( X_{i,k}, W_{k,j}^{Q} \right) \cdot X_{i,k} << E_{k,j}^{W_{Q}} \right)$ ; 4 $\hat{\mathbf{K}}_{ij} \leftarrow \sum_{k} \left( \text{Sgn} \left( X_{i,k}, W_{k,j}^{K} \right) \cdot X_{i,k} << E_{k,j}^{W_{K}} \right)$ ;

- 5  $\mathbf{E}^Q \leftarrow \text{LOE}(\hat{\mathbf{Q}});$

- 6 for  $r \leftarrow 0$  to  $\tilde{R}$  do

- $\hat{\mathbf{K}}^r \leftarrow \text{gather}\left(\mathbf{K}_{\text{id}}^r, \hat{\mathbf{K}}\right);$

- $$\begin{split} \hat{\mathbf{A}}_{ij}^r \leftarrow \sum_k \mathrm{Sgn}\left(\hat{Q}_{i,k}, (\hat{K}_{k,j}^r)^T\right) \cdot (\hat{K}_{k,j}^r)^T << E_{i,k}^Q; \\ \text{Estimate the } \phi_i^r \text{ using Eq. (5);} \end{split}$$

- $\mathbf{K}_{\mathrm{id}}^r \leftarrow \{k | \hat{A}_{i,k}^r > \phi_i^r\};$ 11 Output:  $\mathbf{K}_{\mathrm{id}}^R$ . // Mask matrices after R rounds

# D. Overall of LAPA's CSS Mechanism

Alg. 1 summarizes the LAPA's CSS prediction mechanism. Given an input token sequence X and projection weights  $W_Q$ and  $W_K$ , LAPA begins with offline preprocessing of  $W_Q$  and  $\mathbf{W}_K$ , converting them into the leading-one representation (line 2). During inference, approximate Q and K are generated via the ALOC strategy (line 3-4). The resulting  $\hat{\mathbf{Q}}$  is then further transformed into the leading-one format (line 5). Finally, the MRSA and DDF mechanisms are applied iteratively to compute the final mask matrix (line 6-10), which captures the dynamic sparsity pattern of the attention mechanism.

# IV. LAPA ACCELERATOR

# A. Overall Architecture

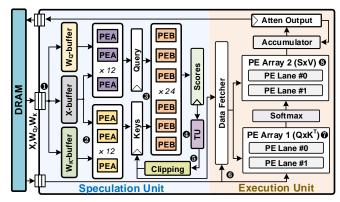

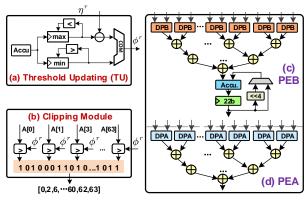

Fig. 8 illustrates the overall architecture of the LAPA accelerator, which consists of a speculation unit and an execution unit. These units jointly operate to support cross-stage sparsity prediction and on-demand QKV generation.

Overall dataflow: The overall processing workflow is head by head. When a head's processing starts, the weight matrices  $\mathbf{W}_{Q}$  and  $\mathbf{W}_{K}$  are fetched from external memory in the leading one format, while the input x is read in the standard 8-bit format (1). Then, 24 processing element A (PEA) individually computes  $Q = xW_Q$  and  $K = xW_K$  (2). As depicted in Fig. 8, each PEA computes 64 multiplications each time and adds up the results to obtain an inner-product result. Meanwhile, the K values generated by previous iterations are fetched to the K buffer. Next, the 24 PEBs calculate the approximated dot-production attention  $\hat{\mathbf{A}}_i^T = \mathbf{Q}_i \mathbf{K}^T$  with multiple rounds (3). The Threshold Updating (TU) module first provides a dynamic threshold  $\phi_i^r$  (**4**), which is then used by the Clipping module to identify the indices of significant

Fig. 8. High-level block diagram for LAPA accelerator.

keys  $(K_{id})$  through comparison (**6**). Based on the indices  $K_{id}$ generated from the speculation unit, the Data Fetcher in the execution unit selectively retrieves the important tokens from DRAM (6). The PE array 1 then on-demand computes the **K** and **V**, as well as the corresponding attention scores (**②**). These attention scores are subsequently normalized through the softmax module, and the PE array 2 performs the matrix multiplication with V to produce the final output (3).

#### B. Architecture Details

Based on our experiments, for MRSA, two filtering rounds performed by the TU module achieve the optimal balance between accuracy and computation cost, and are thus adopted in our design. In this case, the first round performs coarsegrained filtering with INT4 tensors, followed by fine-grained filtering with INT8 tensors on the selected keys. This mixedprecision approach requires both INT4 and INT8 arithmetic units. To improve processing efficiency and conserve on-chip resources, we propose the result-reusable mix-precision inner production unit (IPU).

The IPU contains multiple PEBs operating concurrently. To support both INT4 and INT8 processing, the PEB architecture is elaborated as depicted in Fig. 9 (c). This architecture not only facilitates mixed-precision processing but also diminishes computational complexity by reusing results. Each PEB equips 64 DPBs and each DPB is responsible for a 8 bit × 4 bit multiplication. Specifically,  $\mathbf{K}^T[7:4] << LOE(\mathbf{Q}_i)$  is first calculated and served as round-1 attention, then  $\mathbf{K}^T[3]$ :  $0] << LOE(\mathbf{Q}_i)$  is computed and added with the left-shifted round-1 attention to produce round-2 attention.

Sign pre-assign strategy: As discussed in Section III-A, naively implementing ALOC on hardware will incur severe bit-flipping overhead. To alleviate this, we propose a sign preassign strategy, with two types of PE support, as shown in Fig. 9 (c)(d), and detailed dot-product hardware shown in Fig. 10 (a)(b). Before shifting operations, the strategy involves using the sign bit of 'y' to determine whether to shift 'x' itself or its opposite number. By identifying the sign of results in advance, this avoids the need for sign conversion on the product, as the product typically owns a larger bit width, incurring higher bitflipping overhead.

Fig. 9. Architecture components: (a) Threshold Updating module. (b) Clipping module. (c) PEB. (d) PEA.

#### V. EVALUATION

# A. Experimental Setup

Algorithm Evaluation Setup. We evaluate the LAPA's mechanism on various LLMs for text generation: GPT2-XL [31], OPT1B3 [32], Bloom1B7 [33], Qwen7B [34] and Llama2-13B [35]. To assess the impact of our methods on model performance, we measure perplexity (PPL) on the Wikitext-2 [36] and Dolly [37] datasets, where lower perplexity values indicate better performance. All evaluations are conducted with Pytorch and the HuggingFace library.

Hardware Evaluation Details. We implement LAPA at the RTL level and synthesize it using Synopsys Design Compiler under a 28nm CMOS technology to estimate the area and power consumption of the logic components. The performance speedup is evaluated using an in-house cycle-level simulator, with HBM2 configured as the main memory. Power, area, and read/write bandwidth are further estimated using CACTI. To evaluate the cycle count and energy consumption of off-chip memory accesses, we employ Ramulator, driven by trace files generated from RTL-level simulations.

**Design Configurations**. We evaluate the model accuracy and pruning ratio by adjusting the parameter  $\eta^r$  (as Eq.(5)). For each round,  $\eta^r$  is adjusted from 0.2 to 0.8 with a step of 0.1. We then apply the successive halving method to accelerate this process. We evaluate two configurations: LAPA conservative (LAPA-C) and LAPA aggressive (LAPA-A). LAPA-C refers to settings with minimal performance degradation of at most 0.5% accuracy loss, while LAPA-A is a configuration trading a slight accuracy degradation for hardware benefits, allowing for on average 2% accuracy loss.

# B. Algorithm Performance

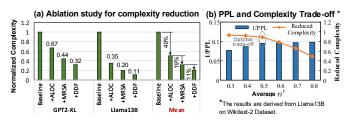

We first conduct ablation experiments to evaluate the low-complexity advantages of ALOC, MRSA, and DDF against a baseline scheme, which uses vanilla leading-one operations and one-shot top-k sorting for attention sparsity prediction. All operation complexities are normalized using an arithmetic complexity model [38]. As depicted in Fig. 11 (a), ALOC reduces complexity by 49% on average compared to the baseline, primarily due to its multiplier-free computation and

Fig. 10. The ALOC-based dot product (DP) hardware architecture.

half-conversion feature. MRSA achieves a 19% reduction, owing to its fine-grained multi-round filtering mechanism that enables early termination of redundant operations. DDF achieves on average 11% reduction, befitting from its sorting-free mechanism.

Fig. 11 (b) explores the impact of various threshold parameters  $\eta^r$  on model PPL and reduced complexity. Overall, a smaller  $\eta^r$  implies more pruning, which helps improve reduced complexity but lowers 1/PPL. However, we observe that when  $\eta^r$  drops below 0.5, the increase in reduced complexity becomes marginal, while 1/PPL decreases dramatically. This is because overly aggressive token pruning, which hurts certain critical tokens, thereby severely degrading the 1/PPL and hindering further complexity reduction. Therefore, to balance the trade-off, we prioritize setting  $\eta^r$  near 0.5.

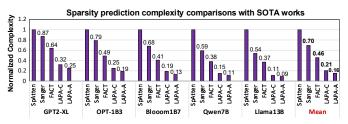

Fig. 12 compares the sparsity prediction complexity of LAPA-C, LAPA-A, Spatten, Sanger, and FACT under various LLM models. To ensure a fair comparison, we constrain the performance degradation of each work to within 2%, except for LAPA-C with 0.5% loss. Considering that Spatten employs multiplicative operations for attention prediction and relies on a computationally expensive top-k sorting mechanism to select key tokens, it incurs the highest computational complexity. Therefore, we use it as the baseline. In contrast, Sanger utilizes a one-shot threshold-based comparison instead of sorting, achieving an average reduction of 30% in computational complexity. Although FACT also adopts a log-domain multiplication-free prediction paradigm, it incurs significant conversion overhead due to the need to convert both operands, thereby limiting its complexity reduction to only 54%. In comparison, our proposed LAPA mechanism consistently achieves the greatest computation reduction across all models, averaging 79%. With slight accuracy loss, LAPA-A further achieves 84% complexity reduction.

# C. Hardware Evaluation

Table I shows the area and power breakdown of the proposed LAPA accelerator. It has a total area of  $3.208~\rm mm^2$  and power of  $474~\rm mW$  with an operating frequency of  $1\rm GHz$ , achieving an effective throughput of  $2892~\rm GOPS$ . Although the speculation unit accounts for approximately 52% of the overall area and 46% of the power consumption, it effectively predicts the dynamic sparsity hidden in the self-attention, leading to an average reduction of around 79% in the total computation. This, in turn, significantly reduces the area and power overheads of the execution unit. By incorporating a

Fig. 11. (a) Complexity reduction for the ALOC, MRSA and DDF. (b) Tradeoff between PPL and complexity.

Fig. 12. Comparison of complexity reduction with SOTA works.

speculation unit, the LAPA accelerator to strike an effective trade-off, leading to significant throughput improvement.

# D. Comparisons with SOTA accelerators

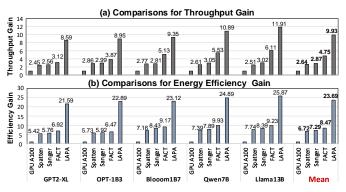

Fig. 13 compares the throughput and energy efficiency gains of LAPA against SOTA attention accelerators. The baseline is the Nvidia A100, which supports up to 50% structured sparsity. LAPA significantly outperforms all other designs, benefiting from its hardware-friendly ALOC strategy and finegrained multi-round filter strategy, which eliminates a large number of redundant operations with minimal overhead. On average, LAPA achieves throughput improvements of  $9.93\times$ ,  $3.76\times$ ,  $3.45\times$ ,  $2.1\times$  over A100 GPU, Spatten, Sanger and FACT, respectively. In terms of energy efficiency, LAPA achieves average gains of  $23.69\times$ ,  $3.52\times$ ,  $3.24\times$  and  $2.79\times$  over the same baselines. The gain in energy efficiency primarily stems from LAPA's adoption of the ALOC scheme, which eliminates the need for costly multiplication operations.

# VI. CONCLUSION

In this paper, we propose LAPA, a versatile Transformer accelerator that employs asymmetric log-domain multiplication-free computing, multi-round shift accumulation, and data-feature dependent filtering, to jointly realize cross-stage sparsity for both QKV linear and attention acceleration.

# ACKNOWLEDGMENTS

This work was supported in part by the National Science and Technology Major Project under Grant 2022ZD0115200; in part by the NSFC under Grant 62125403, Grant 92464302, Grant U24B20164 and Grant 92164301; in part by Shanghai Municipal Science and Technology Major Project; in part by the Natural Science Foundation of Jiangsu Province Basic Research Program under Grant BK20243042; in part by the Beijing National Research Center for Information Science and Technology; in part by the Northern IC Technology Innovation Center (Beijing) Co., Ltd under Grant QYJS20232801B;

Fig. 13. Normalized attention (a) speed up and (b) energy efficiency gain.

$\label{eq:table I} \textbf{TABLE I}$  Area and Power Breakdown for LAPA (Core Part) at 1GHZ.

| Units            | Parameters                                            | Area[mm <sup>2</sup> ] | Power[mW] |

|------------------|-------------------------------------------------------|------------------------|-----------|

| Speculation Unit | 24 64-input 8-bit PEAs                                | 0.283                  | 56.54     |

|                  | 24 64-input 8-bit PEBs                                | 0.356                  | 88.26     |

|                  | 1 TU unit, 1 Clipping unit                            | 0.175                  | 34.05     |

|                  | 512kB Buffer                                          | 0.874                  | 41.87     |

| Execution Unit   | 4 128-input 16-bit PE lines                           | 0.456                  | 106.54    |

|                  | 4 Softmax Modules                                     | 0.394                  | 48.42     |

|                  | 1 accumulator                                         | 0.108                  | 56.54     |

|                  | 256kB K/V Buffer                                      | 0.489                  | 26.43     |

| Others           | -                                                     | 0.073                  | 15.76     |

| Total            | TSMC 28nm: Area=3.208mm <sup>2</sup> , Power=474.41mW |                        |           |

and in part by the Beijing Advanced Innovation Center for Integrated Circuits.

# REFERENCES

- A. Vaswani, N. Shazeer, N. Parmar et al., "Attention is all you need," *Adv. Neural Inf. Process. Syst.*, vol. 30, 2017.

- [2] J. Devlin, M.-W. Chang, K. Lee, and K. Toutanova, "BERT: Pre-training of deep bidirectional Transformers for language understanding," arXiv preprint arXiv:1810.04805, 2018.

- [3] A. Dosovitskiy, L. Beyer, A. Kolesnikov, D. Weissenborn, X. Zhai, T. Unterthiner, M. Dehghani, M. Minderer, G. Heigold, S. Gelly, J. Uszkoreit, and N. Houlsby, "An image is worth 16x16 words: Transformers for image recognition at scale," arXiv preprint arXiv:2010.11929, 2020.

- [4] X. Zhai, A. Kolesnikov, N. Houlsby, and L. Beyer, "Scaling vision transformers," in *Proceedings of the IEEE/CVF conference on computer* vision and pattern recognition, 2022, pp. 12104–12113.

- [5] J. Deng, W. Dong, R. Socher, L.-J. Li, K. Li, and L. Fei-Fei, "Imagenet: A large-scale hierarchical image database," in 2009 IEEE conference on computer vision and pattern recognition. Ieee, 2009, pp. 248–255.

- [6] A. Kolesnikov, L. Beyer, X. Zhai, J. Puigcerver, J. Yung, S. Gelly, and N. Houlsby, "Large scale learning of general visual representations for transfer," arXiv preprint arXiv:1912.11370, vol. 2, no. 8, 2019.

- [7] S. Kim, C. Hooper, T. Wattanawong, M. Kang, R. Yan, H. Genc, G. Dinh, Q. Huang, K. Keutzer, M. W. Mahoney et al., "Full stack optimization of Transformer inference: A survey," arXiv preprint arXiv:2302.14017, 2023.

- [8] K. A. A. Fuad and L. Chen, "A survey on sparsity exploration in Transformer-based accelerators," *Electronics*, vol. 12, no. 10, p. 2299, 2023.

- [9] W. X. Zhao, K. Zhou, J. Li, T. Tang, X. Wang, Y. Hou, Y. Min, B. Zhang, J. Zhang, Z. Dong et al., "A survey of large language models," arXiv preprint arXiv:2303.18223, vol. 1, no. 2, 2023.

- [10] Z. Zhou, X. Ning, K. Hong, T. Fu, J. Xu, S. Li, Y. Lou, L. Wang, Z. Yuan, X. Li et al., "A survey on efficient inference for large language models," arXiv preprint arXiv:2404.14294, 2024.

- [11] H. Wang, Z. Wang, Z. Yue, Y. Long, T. Wei, J. Yang, Y. Wang, C. Li, S. Wei, Y. Hu et al., "MCBP: A Memory-Compute Efficient LLM Inference Accelerator Leveraging Bit-Slice-enabled Sparsity and Repet-

- itiveness," in *Proc. 58th IEEE/ACM Int. Symp. Microarchit. (MICRO)*, 2025, pp. 1592–1608.

- [12] Y. Tay, M. Dehghani, S. Abnar, Y. Shen, D. Bahri, P. Pham, J. Rao, L. Yang, S. Ruder, and D. Metzler, "Long range arena: A benchmark for efficient transformers," in *International Conference on Learning Representations*.

- [13] R. Rombach, A. Blattmann, D. Lorenz, P. Esser, and B. Ommer, "High-resolution image synthesis with latent diffusion models," in *Proceedings of the IEEE/CVF conference on computer vision and pattern recognition*, 2022, pp. 10684–10695.

- [14] P. Rajpurkar, J. Zhang, K. Lopyrev, and P. Liang, "Squad: 100,000+ questions for machine comprehension of text," arXiv preprint arXiv:1606.05250, 2016.

- [15] H. Wang, J. Fang, X. Tang et al., "SOFA: A compute-memory optimized sparsity accelerator via cross-stage coordinated tiling," in Proc. 57th IEEE/ACM Int. Symp. Microarchitecture (MICRO), 2024, pp. 1247– 1263.

- [16] Z. Song, C. Qi, Y. Yao, P. Zhou, Y. Zi, N. Wang, and X. Liang, "TSAcc: An Efficient Temporal-Spatial Similarity Aware Accelerator for Attention Acceleration," in *Proc. 61st ACM/IEEE Des. Autom. Conf.* (DAC), 2024, pp. 1–6.

- [17] J. Zhao, P. Zeng, G. Shen, Q. Chen, and M. Guo, "Hardware-software co-design enabling static and dynamic sparse attention mechanisms," *IEEE Transactions on Computer-Aided Design of Integrated Circuits* and Systems, 2024.

- [18] H. Wang, H. Xu, Y. Wang, and Y. Han, "CTA: Hardware-software codesign for compressed token attention mechanism," in *Proc. IEEE Int.* Symp. High Perform. Comput. Archit. (HPCA), 2023, pp. 429–441.

- [19] S. Hong, S. Moon, J. Kim, S. Lee, M. Kim, D. Lee, and J.-Y. Kim, "DFX: A low-latency multi-FPGA appliance for accelerating Transformer-based text generation," in *Proc. IEEE/ACM Int. Symp. Microarchit. (MICRO)*, 2022, pp. 616–630.

- [20] J. Park, M. Kang, Y. Han, Y.-G. Kim, J. Shin, and L.-S. Kim, "Token-picker: Accelerating attention in text generation with minimized memory transfer via probability estimation," in *Proc. 61st ACM/IEEE Des. Autom. Conf. (DAC)*, 2024, pp. 1–6.

- [21] H. Wang, H. Wang, Z. Yue, J. Liu et al., "BETA: A Bit-Grained Transformer Attention Accelerator With Efficient Early Termination," IEEE Trans. Circuits Syst. II, 2025.

- [22] T. J. Ham, S. J. Jung, S. Kim, Y. H. Oh, Y. Park, Y. Song, J.-H. Park, S. Lee, K. Park, J. W. Lee et al., "A<sup>3</sup>: Accelerating attention mechanisms in neural networks with approximation," in Proc. IEEE Int. Symp. High Perform. Comp. Architecture (HPCA), 2020, pp. 328–341.

- [23] T. J. Ham, Y. Lee, S. H. Seo et al., "ELSA: Hardware-software co-design for efficient, lightweight self-attention mechanism in neural networks," in Proc. IEEE Int. Symp. Comput. Architect., 2021, pp. 692–705.

- [24] Z. Qu, L. Liu, F. Tu, Z. Chen, Y. Ding, and Y. Xie, "DOTA: Detect and omit weak attentions for scalable transformer acceleration," in *Proc.* ACM Int. Conf. Architectural Support Program. Lang. Operating Syst., 2022, pp. 14–26.

- [25] Z. Zhou, J. Liu et al., "Energon: Toward efficient acceleration of Transformers using dynamic sparse attention," *IEEE Trans. Comput.-*Aided Design Integr. Circuits Syst., vol. 42, no. 1, pp. 136–149, 2022.

- [26] L. Lu, Y. Jin, H. Bi et al., "Sanger: A co-design framework for enabling sparse attention using reconfigurable architecture," in Proc. IEEE/ACM Int. Symp. Microarchitecture, 2021, pp. 977–991.

- [27] H. Cho, D. Kim, S.-E. Hwang, and J. Park, "Sparc: Token similarity-aware sparse attention transformer accelerator via row-wise clustering," in *Proceedings of the 61st ACM/IEEE Design Automation Conference*, 2024, pp. 1–6.

- [28] S. Lee, B. Kim, J. Park, and D. Jeon, "CLAT: A clustering-based attention Transformer accelerator for low-latency text generation in LLMs," *IEEE Trans. Circuits Syst. 1*, 2025.

- [29] Y. Qin, Y. Wang, D. Deng et al., "FACT: FFN-Attention co-optimized Transformer architecture with eager correlation prediction," in Proc. IEEE Annu. Int. Symp. Comput. Architect., 2023, pp. 1–14.

- [30] H. Wang, Z. Zhang, and S. Han, "Spatten: Efficient sparse attention architecture with cascade token and head pruning," in *Proc. IEEE Int.* Symp. on High Perform. Comput. Architecture (HPCA), 2021, pp. 97– 110.

- [31] A. Radford, J. Wu, R. Child, D. Luan, D. Amodei, and I. Sutskever, "Language models are unsupervised multitask learners," *OpenAI blog*, vol. 1, no. 8, p. 9, 2019.

- [32] S. Zhang, S. Roller, N. Goyal et al., "OPT: Open pre-trained Transformer

- language models," arXiv preprint arXiv:2205.01068, 2022.

- [33] T. Le Scao, A. Fan, C. Akiki, E. Pavlick et al., "Bloom: A 176B-parameter open-access multilingual language model," arXiv preprint arXiv:2211.05100, 2022.

- [34] J. Bai, S. Bai, Y. Chu, Z. Cui, K. Dang, X. Deng, Y. Fan, W. Ge, Y. Han, F. Huang et al., "Qwen technical report," arXiv preprint arXiv:2309.16609, 2023.

- [35] H. Touvron, L. Martin, K. Stone, P. Albert et al., "Llama 2: Open foundation and fine-tuned chat models," arXiv preprint arXiv:2307.09288, 2023

- [36] S. Merity, C. Xiong, J. Bradbury, and R. Socher, "Pointer sentinel mixture models," arXiv preprint arXiv:1609.07843, 2016.

- [37] M. Conover, M. Hayes, A. Mathur, J. Xie, J. Wan, S. Shah, A. Ghodsi, P. Wendell, M. Zaharia, and R. Xin, "Free dolly: Introducing the world's first truly open instruction-tuned LLM," *Company Blog of Databricks*, 2023.

- [38] R. P. Brent and P. Zimmermann, Modern computer arithmetic. Cambridge University Press, 2010, vol. 18.