# Performance Benchmarking of Tensor Trains for Accelerated Quantum-Inspired Homogenization on TPU, GPU, and CPU Architectures

Sascha H. Hauck<sup>1,2,\*</sup>, Matthias Kabel<sup>1</sup>, Nicolas R. Gauger<sup>2</sup>

<sup>1</sup>Fraunhofer ITWM, Department of Flow and Material Simulation, Kaiserslautern, Germany <sup>2</sup>University of Kaiserslautern-Landau (RPTU), Chair for Scientific Computing, Kaiserslautern, Germany

\*Corresponding author: sascha.hannes.hauck@itwm.fraunhofer.de

### Abstract

Recent advances in high-resolution CT-imaging technology are creating a new class of ultra-high resolved micro-structural datasets that challenge the limits of traditional homogenization approaches. While state-of-the-art FFT-based homogenization techniques remain effective for moderate datasets, their memory footprint and computational cost grow rapidly with increasing resolution, making them increasingly inefficient for industrial-scale problems. To address these challenges, the recently developed Superfast-Fourier Transform (SFFT)-based homogenization algorithm leverages the memory-efficient low-rank representations of Tensor Trains (TTs), which reduce the storage and computational requirements of large-scale homogenization problems. Developed for CPU usage, SFFT-based Homogenization efficiently handles high-resolution datasets, assuming the underlying data is well-behaved. In this work, we investigate the performance of fundamental TT operations on modern hardware accelerators using

the JAX framework. This benchmarking study, comparing CPUs, GPUs, and TPUs, evaluates execution times and computational efficiency. Building on these insights, we adapt the SFFT-based homogenization algorithm for usage on accelerators, achieving speed-ups of up to  $10\times$  relative to the CPU implementation, thus paving the road for the treatment of previously infeasible dataset sizes. Our results show that GPUs and TPUs achieve comparable performance in realistic scenarios, despite the relative immaturity of the TPU ecosystem, demonstrating the potential of both architectures to accelerate quantum-inspired techniques for industrial-scale simulations, particularly for homogenization problems.

**Keywords:** Homogenization; Quantum-Inspired; Tensor Network; Tensor Train (TT); Fast-Fourier Transform (FFT); Superfast-Fourier Transform (SFFT); Tensor Processing Unit (TPU); Hardware Acceleration; Polar Decomposition; JAX

### 1. Introduction

Homogenization theory provides a framework for predicting the macroscopic behaviour of materials with complex microstructures, including composites, polycrystals, and fibre-reinforced alloys [1–9]. Central to this approach is the cell problem, a partial differential equation defined over a representative volume element (RVE) that captures the essential features of the microstructure. Solving the cell problem allows one to determine the effective constitutive behaviour of the material. For most practical materials, however, analytical solutions are not feasible, necessitating computational techniques [10, 11].

Among these techniques, FFT-based homogenization has emerged as an efficient alternative to classical finite element methods (FEM). Introduced by Moulinec and Suquet in 1998 [12], this approach reformulates the cell problem as a Lippmann-Schwinger equation, which can

be solved iteratively using the Fast Fourier Transform (FFT). By discretizing the microstructure on a regular grid, FFT-based methods avoid the challenges of meshing and stiffness matrix assembly inherent to FEM, achieving rapid and accurate solutions for periodic microstructures [13].

Recent advances in CT-imaging technologies now enable the acquisition of microstructural datasets of unprecedented size, reaching tens of billions of voxels [14]. While such high-resolution data provide rich insights, they also pose a significant computational challenge for classical FFT-based homogenization, as inference times increase sharply with finer discretization according to the time-complexity of  $\mathcal{O}(N \log N)$  dictated by the FFT [12, 15].

A straightforward solution is the use of hardware accelerators. However, while the computational load makes GPUs and TPUs essential for large-scale homogenization, the extreme memory requirements of high-resolution data often exceed the capacity of modern accelerators. Efficient GPU-based FFT libraries exist [16], but FFT-based homogenization algorithms on GPUs typically target small-scale problems or rely on batching strategies for higher-resolution data, providing only moderate speed-ups [17–20]. For TPUs, a complete

FFT-based homogenization implementation is still missing, although initial FFT implementations show promising performance [21].

Alternative approaches, such as leveraging the Quantum Fourier Transform (QFT) on quantum hardware, could provide exponential speed-ups. However, these applications remain theoretical, as fault-tolerant quantum computers are required even for modest system sizes [22, 23].

To overcome the computational and memory limitations of classical FFT-based homogenization, a Tensor Train (TT)-based homogenization algorithm has recently been proposed. The Superfast Fourier Transform (SFFT)-based homogenization algorithm [24] employs the TT version of the QFT, breaking the exponential scaling barrier of FFT while dramatically reducing memory requirements. However, because this approach is still in an early stage of development, its applicability remains limited to comparatively simple underlying geometries.

In this paper, we make two primary contributions. First, we transfer the fundamental TT algebra to modern hardware accelerators, specifically GPUs and TPUs, using the JAX framework. We provide a rigorous evaluation of feasibility, highlighting the advantages and limitations of each platform, and report detailed benchmarking metrics, including speed and performance. Although libraries for GPU-accelerated TT algebra are already available [25], systematic benchmarking on TPU hardware has been lacking; this work presents the first such evaluation and includes a direct comparison between GPU and TPU performance, building on prior results that demonstrated the suitability of TPUs for DMRG algorithms [26]. Additionally, we provide the first practical implementation and systematic evaluation of Polar-based TT compression on modern hardware accelerators [26].

Second, we leverage the insights from the benchmarking procedure to tackle a realistic, high-resolution scenario of the SFFT-based Homogenization algorithm on hardware accelerators. Our analysis addresses not only the feasibility of running TT-based algorithms on GPUs and TPUs, but also a direct comparison of their performance in terms of computational efficiency and scalability. Importantly, the use of Tensor Trains now enables homogenization of massive datasets, previously infeasible on conventional accelerators, highlighting the potential of low-rank tensor techniques to overcome both memory and computational bottlenecks in industrial-scale simulations.

Together, these contributions establish a foundation for high-performance, large-scale tensor-based homogenization on modern accelerators, demonstrating both the practical viability and the performance benefits of TT-based approaches for high-resolution data.

The remainder of this paper is organized as follows. We begin in Section 2 with an introduction to Tensor Trains and their fundamental algebra. This is followed by a review of state-of-the-art FFT-based homogenization and the recently developed SFFT-based algorithm in Section 3. Section 4 presents a benchmark of the fun-

damental TT operations in terms of a rigorous performance analysis. The adaptation and application of the SFFT-based homogenization algorithm to GPUs and TPUs is discussed in Section 5. Finally, Section 6 provides a summary and highlights the main conclusions drawn.

#### 2. Tensor Train

Emerging independently within mathematics and physics, Tensor Networks (TNs) have evolved into a rich and versatile framework for representing and manipulating high-dimensional data [27–29]. These parallel developments have given rise to a broad family of complementary numerical methods. At their core, TNs express a high-order tensor as a network of interconnected lower-order tensors, linked through prescribed contraction patterns. When the underlying data exhibit suitable structure, such representations can dramatically reduce computational complexity and enable efficient algorithms for large-scale problems.

This work focuses on the Tensor Train (TT) format [30, 31], which can be viewed as a particularly simple yet powerful instance of a general tensor network. In the TT representation, a high-order tensor  $\mathcal{T}$  is factorized into a sequence of interconnected third-order tensors according to

$$\mathcal{T}(i_1, ..., i_n) = \sum_{\alpha_k} A_{\alpha_0}^{\alpha_1}(i_1) A_{\alpha_1}^{\alpha_2}(i_2) ... A_{\alpha_{n-1}}^{\alpha_n}(i_n)$$

$$= A_1(i_1) A_2(i_2) ... A_n(i_n), \tag{1}$$

where each physical index  $i_k$  runs from 0 to p-1. The novel low-order tensors  $A_k$  are called the *cores* of the TT and exhibit the shape  $(r_k \times p \times r_{k-1})$ . This highlights that the expressive power of the decomposition depends critically on the dimensions of the intermediate virtual spaces. The largest such dimension, known as the TT-rank r, plays a central role. It governs both the representational capacity of the model and the computational cost of algorithms operating within the TT format.

At a fundamental level, the power of TTs - and of TN representations in general - arises from their capacity to compress high-dimensional data while remaining amenable to efficient manipulation. To illustrate this, consider an n-th order tensor whose modes each have a (physical) dimension p. A naive storage scheme would require  $O(p^n)$  memory, which grows exponentially with n and rapidly becomes infeasible even for moderate dimensions. In contrast, representing the same tensor in the TT format leads to a linear scaling with both its dimensionality and the number of cores n, amounting to a memory need of  $O(npr^2)$ . A key caveat of this approach, however, is that this method introduces a novel dependence on the TT rank r. This reflects the need for an inherent structure in the data needed to obtain a small rank. Besides these memory improvements, their well-established mathematical foundation enables highly efficient computations, often yielding substantial speedups while keeping the tensor in its compressed form.

The magnitude of this acceleration is, once again, dictated by the rank of the TT representation. A detailed discussion of the fundamental operations in the TT format is provided in the following sections.

Building on this framework, the Tensor-Train Operator (TTO) extends the TT representation of Equation (1) by introducing an additional physical index to each core to encode operator-valued data

$$\hat{\mathcal{T}}(i_1, j_1, \dots, i_n, j_n) = \sum_{\tilde{\alpha}_k} \hat{G}_{\tilde{\alpha}_0}^{\tilde{\alpha}_1}(i_1, j_1) \cdots \hat{G}_{\tilde{\alpha}_{n-1}}^{\tilde{\alpha}_n}(i_n, j_n)$$

$$= \hat{G}_1(i_1, j_1) \cdots \hat{G}_n(i_n, j_n). \quad (2)$$

In this representation, each core's physical index pair  $(i_k, j_k)$  corresponds to the incoming and outgoing dimensions of the operator. Applying a TTO  $\hat{A}$  to a TT x, i.e., performing the contraction  $y = \hat{A}x$ , is analogous to a matrix-vector multiplication, with the TTO acting as a linear operator mapping one TT to another. Consequently, this structure forms a cornerstone of the TT formalism and underpins many standard algorithms for efficient data manipulation.

The algebraic operations within the TT formalism can be broadly classified into three main categories: elementary operations between individual TTs, techniques that improve stability and computational efficiency, and optimization-based methods for solving linear systems of equations directly in the TT format. Here, we focus exclusively on the first two classes of operations, as optimization-based methods fall outside the scope of this work. For a detailed treatment of the latter, we refer the reader to Ganahl et al. [26].

#### 2.1 Fundamental Algebra

The most commonly used operations on TTs include addition, multiplication, and linear transformations [32]. To provide a clear understanding of these operations, we first define the following TTs and TTO

$$x(i_1, \dots, i_n) = A_1(i_1) \cdots A_n(i_n),$$

(3)

$$y(i_1, \dots, i_n) = B_1(i_1) \cdots B_n(i_n),$$

(4)

$$z(i_1, \dots, i_n) = C_1(i_1) \cdots C_n(i_n),$$

(5)

$$\hat{A}(i_1, j_1, \dots, i_n, j_n) = \hat{D}_1(i_1, j_1) \cdots \hat{D}_n(i_n, j_n).$$

(6)

Constant multiplication, i.e. multiplying a TT x by a scalar c, is the simplest rudimentary operation. This can be readily implemented by a simple update rule for the first core

$$A_1(i_1) \to \tilde{A}_1(i_1) = c A_1(i_1).$$

(7)

Since the scalar only rescales a single core and does not alter the virtual dimensions of the TT representation, the TT rank remain unchanged.

Addition of two TTs, z = x + y, is performed via diagonalization. Specifically, the cores per physical index of the individual TTs are placed along the diagonal of a matrix to form the new cores

$$C_k(i_k) = \begin{pmatrix} A_k(i_k) & 0 \\ 0 & B_k(i_k) \end{pmatrix}, \quad k = 2, \dots, n-1,$$

for all internal cores. The first and last cores require special treatment due to one of their virtual dimensions being trivial. They can be built via a small adaptation of the above formula

$$C_1(i_1) = \begin{pmatrix} A_1(i_1) & B_1(i_1) \end{pmatrix}, \quad C_n(i_n) = \begin{pmatrix} A_n(i_n) \\ B_n(i_n) \end{pmatrix}.$$

The correctness of this construction follows directly from multiplying the corresponding TT cores of z. Because the block-diagonal construction stacks the cores of x and y along the virtual dimension, the TT ranks of z equal the sum of the corresponding ranks of the two summands.

Subtraction of two TTs, z=x-y, forms the next complex operation and is implemented in two steps. First, the second TT y is multiplied by the scalar (-1) using the update rule for constant multiplication in Equation (7), yielding  $\tilde{y}$ . The result can now be obtained in a second step by performing standard addition  $z=x+\tilde{y}$ . Since rank growth arises solely from the addition step, the rank of the resulting TT scales as the sum of the ranks of the original TTs.

Tensor multiplication, also known as the Hadamard product, between two TTs,  $z=x\otimes y$ , can be carried out by reordering the operation and the corresponding cores, yielding

$$z = [A_1(i_1) \cdots A_n(i_n)] \otimes [B_1(i_1) \cdots B_n(i_n)]$$

=  $[A_1(i_1) \otimes B_1(i_1)] \cdots [A_n(i_n) \otimes B_n(i_n)].$

Therefore, the cores of z can be identified as

$$C_k(i_k) = A_k(i_k) \otimes B_k(i_k), \quad k = 1, \dots, n.$$

Regarding the final rank, it becomes clear that it is equal to the product of the ranks of the multiplicands.

Contraction between a TT and a TTO,  $y = \hat{A}x$ , can be performed by summing over the connected physical indices

$$\begin{aligned} y_i &\equiv y(i_1, \dots, i_n) \\ &= \sum_{\{j_k\}} \left[ \hat{D}_1(i_1, j_1) \cdots \hat{D}_n(i_n, j_n) \right] \left[ A_1(j_1) \cdots A_n(j_n) \right] \\ &= \left[ \sum_{j_1} \hat{D}_1(i_1, j_1) A_1(j_1) \right] \cdots \left[ \sum_{j_n} \hat{D}_n(i_n, j_n) A_n(j_n) \right], \end{aligned}$$

where the newly formed cores can be expressed as

$$B_k(i_k) = \sum_{j_k} \hat{D}_k(i_k, j_k) A_k(j_k), \quad k = 1, \dots, n.$$

(8)

Since the virtual dimensions are not modified during the contraction, their corresponding spaces combine, causing the resulting rank to be equal to the product of the ranks of the involved TT and TTO. It is noteworthy that the contraction patterns in the TT format are quite simple. However, for moderately more complex TN structures, such as Projected Entangled Pair States (PEPS), the contraction problem is already #P-complete [33].

For completeness, we conclude this section by noting that alternative implementations exist for TT operations. In particular, it can be advantageous to convert

a TT into a TTO. This transformation can improve computational performance, especially when combined with optimization-based methods. Assume we have a TT y. It can be lifted to a TTO  $\hat{A}$ , following the format of Equation (2), by introducing delta functions:

$$\hat{D}_{\alpha_{k-1}}^{\alpha_k}(i_k, j_k) = B_{\alpha_{k-1}}^{\alpha_k}(i_k) \,\delta(i_k, j_k). \tag{9}$$

The resulting TTO cores  $\hat{D}_{\alpha_{k-1}}^{\alpha_k}(i_k, j_k)$  are sparse fourthorder tensors that can be interpreted as the tensor equivalent of a diagonal matrix. Applying the converted TTO defined in Equation (9) to a TT x produces the same result as the Hadamard product of x and y. Moreover, by leveraging optimization-based methods, the rank of the resulting TT exhibits improved scalability, as it is not fixed to the product of the ranks of x and y, but is only upper-bounded by it [24].

#### 2.2 Stability

The operations introduced in the previous section share a common feature: they generally increase the rank of the resulting TT, with the sole exception of trivial scalar multiplication. In practical algorithms, however, uncontrolled rank growth over successive operations can lead to numerical instability and rapidly negate the computational advantages of TN methods, resulting in prohibitive runtimes and excessive memory consumption. Before addressing strategies for mitigating rank inflation, we first discuss structural conditions that play a key role in maintaining numerical stability.

Orthogonalization of a TT is used to enforce additional orthogonality conditions on its component cores. This step is required not only as a precursor to compression algorithms but also to improve the overall numerical stability of the TT formalism. Let us consider a TT x defined according to Equation (3), whose cores do not initially satisfy any such criteria. The aim of orthogonalization is to restructure the underlying cores such that the TT assumes the form

$$x_i \equiv x(i_1, \dots, i_n)$$

=  $U_1(i_1) \cdots U_{m-1}(i_{m-1}) T(i_m) V_{m+1}(i_{m+1}) \cdots V_n(i_n)$

such that the left-isometry conditions

$$\sum_{i_k} \sum_{\alpha_{k-1}} U_{\alpha_{k-1}}^{\alpha_k}(i_k) U_{\alpha_{k-1}}^{\dagger \alpha_k'}(i_k) = \delta_{\alpha_k, \alpha_k'}$$

and the right-isometry conditions

$$\sum_{i_k} \sum_{\alpha_k} V_{\alpha_{k-1}}^{\dagger \alpha_k}(i_k) V_{\alpha'_{k-1}}^{\alpha_k}(i_k) = \delta_{\alpha_{k-1}, \alpha'_{k-1}}$$

are satisfied. The remaining tensor  $T(i_m)$  is called the orthogonality center and may be interpreted as the non-orthogonal residuum of the TT. This representation is commonly referred to as the canonical form of the TT x.

For simplicity, we restrict ourselves to the case  $m \in \{1, n\}$ , meaning that the orthogonality center is located at one of the boundary cores. This canonical form can

be constructed by applying a QR decomposition from left to right (or, equivalently, an RQ decomposition from right to left) to each core of the TT. In this process, the orthogonal matrix Q is retained, while the corresponding rectangular matrix R is absorbed into the next core, after which the procedure continues in the same manner:

$$x_{i} = A_{1}(i_{1}) A_{2}(i_{2}) \cdots A_{n-1}(i_{n-1}) A_{n}(i_{n}),$$

$$= Q_{1}(i_{1}) [R_{1} A_{2}(i_{2})] \cdots A_{n-1}(i_{n-1}) A_{n}(i_{n}),$$

$$= Q_{1}(i_{1}) Q_{2}(i_{2}) R_{2} \cdots A_{n-1}(i_{n-1}) A_{n}(i_{n}),$$

$$\cdots$$

$$= Q_{1}(i_{1}) Q_{2}(i_{2}) \cdots Q_{n-1}(i_{n-1}) [R_{n-1} A_{n}(i_{n})],$$

$$= Q_{1}(i_{1}) Q_{2}(i_{2}) \cdots Q_{n-1}(i_{n-1}) T(i_{n}).$$

Since the rectangular matrix in each step is in fact square, the TT ranks of the individual cores remain unchanged throughout the orthogonalization procedure.

Compression addresses the issue of rank growth that accumulates over successive operations and is therefore one of the most essential procedures in TN algorithms. Without compression, the ranks of intermediate TTs would quickly become prohibitively large, making computations infeasible.

Let us first discuss  $Compression\ via\ SVD$ . We begin by left-to-right orthogonalization of TT x. A Singular Value Decomposition is then applied to the orthogonality center (i.e., the last core):

$$T(i_n) \to Q_n \operatorname{diag}(\sigma_1, \sigma_2, ..., \sigma_l, ..., \sigma_q) V_n^{\dagger}(i_n)$$

$$\approx Q_n \operatorname{diag}(\sigma_1, \sigma_2, ..., \sigma_l) V_n^{\dagger}(i_n)$$

$$= \tilde{Q}_n V_n^{\dagger}(i_n).$$

Here, the smallest q-l singular values are truncated. Since the singular values are ordered in descending magnitude, this truncation provides a controlled reduction of the virtual dimension and thus limits the TT ranks. The truncated singular matrix is then absorbed into  $\tilde{Q}_n$ , which is subsequently multiplied into the next core to the left, while  $V_n^{\dagger}(i_n)$  remains as the newly updated core at the n-th position. This shifts the orthogonality center one position to the left, after which the same procedure is applied again. The process continues until the entire TT has been traversed. It is important to note that this procedure transforms the TT from a left-isometric representation with the center at the n-th core into a right-isometric representation with the orthogonality center at the first core.

Finding an appropriate number of singular values to retain can be approached in two general ways. The simple option is to prescribe a fixed number of singular values to keep. However, this strategy provides no guarantee that the truncated result remains a sufficiently accurate approximation of the original TT. A more reliable alternative is to determine the truncation adaptively such that the approximation  $\tilde{x}$  of a TT x satisfies

$$||x - \tilde{x}||_F \le \varepsilon ||x||_F,\tag{10}$$

where  $||\cdot||_F$  denotes the Frobenus norm. A sufficient condition for Equation (10) is that the root of the squared

sum over the smallest singular values  $\sigma_k$  does not exceed

$$\delta = \frac{\varepsilon}{\sqrt{1-n}}||x||_F,\tag{11}$$

which ensures that only the significant singular values are retained [32].

While SVD-based compression is widely employed, the SVD can become inaccurate under limited numerical precision, as may occur on certain accelerators or edge devices. In such cases, this procedure may yield erroneous results.

Compression via Polar Decomposition provides an alternative approach that is less sensitive to the conditioning of the input. As a result, it is particularly well-suited for systems with low-precision arithmetic. Instead of performing the SVD, the polar decomposition is employed on the orthogonality center

$$T(i_n) = U H$$

,

where U is isometric and H is positive semi-definite, with the singular values  $\sigma_k$  being intrinsic to H.

To extract the components of W associated with singular values above a certain  $\tilde{\delta}$ , we consider the Hermitian matrix  $H - \tilde{\delta}I$  and perform its polar decomposition

$$H - \tilde{\delta}I = U'H'.$$

The reasoning behind this being that the now newly formed unitary factor U' has eigenvalues (+1) for eigenvectors corresponding to  $\sigma_k > \tilde{\delta}$  and (-1) for  $\sigma_k \leq \tilde{\delta}$ . Subsequently, projectors onto the "above cutoff" and "below cutoff" subspaces are constructed as

$$P_{\pm} = \frac{1 \pm U'}{2}.$$

Through these, the truncated part of H can readily be obtained by projection onto the "above cutoff" subspace

$$H_{>\tilde{\delta}} = P_+ H P_+,$$

yielding the reduced orthogonality center

$$\tilde{T}(i_n) = U H_{\searrow \tilde{\delta}}.$$

At this stage,  $\tilde{T}(i_n)$  still retains the original number of columns and thus has no real compression yet. To construct real truncated factors F and G (with l < q columns and rows, respectively) such that  $\tilde{T}(i_n) = FG$ , an orthonormal basis  $C_+$  for the column space of  $P_+$  is computed via subspace iteration. The resulting factors can be obtained through

$$F = U C_+, \quad G = C_+^{\dagger} H,$$

producing the truncated representation without requiring an explicit SVD.

Comparing the two approaches, SVD-based compression is generally preferred due to its lower computational cost and faster convergence, provided that the SVD is numerically stable. In addition, SVD-based truncation yields a quasi-optimal rank approximation that satisfies

inequality (10) when an appropriate threshold  $\delta$  is chosen (e.g., as in Equation (11)).

By contrast, the polar-based algorithm relies on an absolute cutoff  $\tilde{\delta}$ , which can be problematic because the singular values themselves are not explicitly available. Nevertheless, by setting

$$\tilde{\delta} = \frac{\delta}{q},$$

where q is the total number of untruncated singular values, inequality (10) can still be strictly enforced. This results in more a conservative truncation, producing a TT rank that slightly exceeds the optimal SVD-based result.

A detailed comparison of the run-time performance between SVD- and polar-based compression methods is provided in Appendix C.

## 3. Fourier-based Homogenization

In recent years, computational homogenization - particularly Fourier-based methods - has seen substantial advances. We begin by reviewing the classical FFT-based scheme introduced by Moulinec and Suquet in 1998 [12], which underpins many modern extensions.

Building on this framework, new approaches have emerged that draw inspiration from quantum computing and TN techniques. These so-called quantum-inspired methods enable highly compressed representations of microstructural fields and open the door to novel acceleration strategies. Since our work develops this TN-based approach further, we focus here exclusively on the quantum-inspired formulation. Readers interested in the genuine quantum-computing extension are referred to the work of Liu et al. [23].

#### 3.1 FFT-based Homogenization

The primary objective of the FFT-based Homogenization is to determine the effective linearly elastic macroscopic stiffness tensor  $\mathbf{C}^{\text{eff}}$  of a composite, assuming the properties of the individual constituents are known. The stiffness tensor  $\mathbf{C}^{\text{eff}}$  is defined through the macroscopic stress-strain relationship

$$\sigma^{\text{eff}} = \mathbf{C}^{\text{eff}} \mathbf{E},\tag{12}$$

where  $\sigma^{\text{eff}}$  and **E** represent the macroscopic stress and strain tensors, respectively.

To solve the above equation, it is advantageous to perform the analysis at the local scale of the heterogeneities in the composite. Within this region, a representative volume element (RVE)  $\mathcal{V}$  is defined, which is assumed to be significantly smaller than the overall material length scale [11]. This approach, where a macroscopic problem is addressed by first solving a microscopic problem on an RVE, is referred to as the Corrector problem [34].

In this setting, assuming periodic boundary conditions on the RVE, the local strain field can be written as

$$\varepsilon(\mathbf{x}) = \mathbf{E} + \nabla^{\mathbf{S}} \mathbf{u}(\mathbf{x}),\tag{13}$$

where  $\nabla^{S}$  and  $\mathbf{u}(\mathbf{x})$  are the symmetrized nabla-operator and the local displacement field, respectively. By imposing the condition of a vanishing average

$$\frac{1}{|\mathcal{V}|}\int_{\mathcal{V}}\nabla\mathbf{u}(\mathbf{x})d\mathbf{x}=0,$$

it is assured that the macroscopic strain  ${\bf E}$  represents the mean strain over the RVE. Since the macroscopic strain is assumed to be known, the focus of the derivation shifts to finding a representation of the fluctuation term  $\nabla^S {\bf u}({\bf x})$ .

We continue the derivation by identifying that the local stress tensor must satisfy the force-equilibrium equation, given by

$$\nabla \sigma(\mathbf{x}) = \nabla \left\{ \mathbf{C}(\mathbf{x}) \left[ \mathbf{E} + \nabla^{\mathbf{S}} \mathbf{u}(\mathbf{x}) \right] \right\}$$

$$= 0.$$

(14)

To address the local problem, Equation (14) is reformulated through an isotropic reference material, characterized by a constant stiffness tensor  $\mathbf{C}_0$  [34], leading to

$$\nabla \left\{ \mathbf{C}_0 \left[ \mathbf{E} + \nabla^{\mathrm{S}} \mathbf{u}(\mathbf{x}) \right] + \tau(\mathbf{x}) \right\} = 0.$$

(15)

with the polarization tensor

$$\tau(\mathbf{x}) = [\mathbf{C}(\mathbf{x}) - \mathbf{C_0}] [\mathbf{E} + \nabla^{\mathrm{S}} \mathbf{u}(\mathbf{x})]. \tag{16}$$

The closed-form differential Equation (15) can be solved using a Green's function  $G_0$ , resulting in the following expression for the displacement gradient

$$\nabla^{S} \mathbf{u}(\mathbf{x}) = -\left(\Gamma_0 * \tau\right)(\mathbf{x}),\tag{17}$$

where  $\Gamma_0 = \varepsilon G_0 \nabla$  denotes the Green-Eshelby operator for strains [35]. It is important to note that the divergence operator  $\nabla$  plays a crucial role in defining the discretization scheme used [36], see Appendix A for a detailed discussion. By substituting the solution (17) into the strain expression (13), and applying the definition of the polarization tensor (16), we obtain the Lippmann-Schwinger equation

$$\varepsilon(\mathbf{x}) = \mathbf{E} - \{ \Gamma_0 * [(\mathbf{C} - \mathbf{C}_0) \varepsilon] \} (\mathbf{x}). \tag{18}$$

However, since the Green-Eshelby operator has a known analytical form in Fourier space, Equation (17) can be transformed accordingly, yielding

$$\mathcal{F}\left[\nabla \mathbf{u}\right](\mathbf{q}) = -\overline{\Gamma}_0(\mathbf{q})\,\overline{\tau}(\mathbf{q}) \tag{19}$$

where the Fast Fourier Transform  $\mathcal{F}[\cdot]$  is employed for efficient computation. Throughout this paper, variables in momentum space are denoted by a wide line above the symbol to distinguish them from their counterparts in spatial space.

Finally, the FFT-based Homogenization algorithm 1 is derived by incorporating the Fourier representation of the Green-Eshelby operator (19) into the Lippmann-Schwinger Equation (18). The algorithm iteratively refines the initial approximation of the local strain, conveniently initialized as the mean strain **E**, by accounting

**Algorithm 1:** FFT-based Homogenization Algorithm

for local variations in the material structure. The iterations continue until a predefined accuracy threshold  $\delta_{\rm tol}$  is achieved.

With the output obtained from algorithm 1, we can readily calculate the effective stiffness operator  $\mathbf{C}^{\text{eff}}$  through Equation (12). A detailed explanation of this procedure can be found in Appendix A. We conclude this Section by noting that the computational complexity of the FFT-based algorithm 1 is dominated by the FFT operations, scaling with  $\mathcal{O}\left(dN^d\log N\right)$ , where N is the number of discretization points per dimension d. Thus, improving the FFT-based Homogenization procedure relies on either enhancing the performance of FFT operations, such as through hardware acceleration, or circumventing the classical FFT entirely.

#### 3.2 Quantum-Inspired Homogenization

In the following, we provide a concise overview of the SFFT-based homogenization algorithm, which serves as the foundation for the implementations employed in our experiments. A detailed derivation and formal development of the method can be found in the original formulation [24]. For clarity and consistency throughout this work, the terms "SFFT-based algorithm" and "Quantum-Inspired algorithm" will be used interchangeably to refer to the same computational procedure.

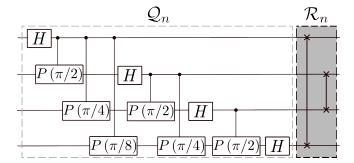

To construct the SFFT-based Homogenization algorithm, the operands and operators used in the classical FFT-based algorithm 1 must first be represented in TT and TTO format, respectively. A straightforward approach would employ the TT variant of the FFT. While this may reduce memory usage, it does not alleviate the computational bottleneck, as the complexity remains that of the classical FFT. We therefore replace the FFT with the *n*-qubit Quantum Fourier Transform (QFT), denoted  $\widetilde{\mathcal{F}}_n$ , to leverage its exponentially improved computational complexity, scaling as  $\mathcal{O}(d\log^2 N)$ . The standard QFT formulation, however, is unsuitable for a TTO representation due to exponential rank growth for increased resolution of the underlying domain. Fortunately, this limitation applies only to the standard QFT representation commonly found in the literature. By separating the QFT as  $\widetilde{\mathcal{F}}_n = \mathcal{R}_n \mathcal{Q}_n$  into a "heavylifting" component  $Q_n$  and a reordering contribution  $\mathcal{R}_n$  (see Figure 1), the circuit associated with  $\mathcal{Q}_n$  can be represented as a low-rank TTO [37]. Since the cir-

Figure 1: Quantum circuit for the four-qubit Quantum Fourier Transform,  $QFT_4 = \mathcal{R}_4 \mathcal{Q}_4$ .

cuit  $\mathcal{R}_n$  merely enforces a qubit reordering, it can be safely ignored, provided the new convention is consistently applied in momentum space. Due to its improved speed, the TTO representation of  $\mathcal{Q}_n$  is generally referred to as the "Superfast Fourier Transform" (SFFT), giving the method its name [38]. Thus, the algorithm will use both the SFFT  $\mathcal{S}$  as well as its inverse  $\mathcal{S}^{-1}$  instead of the regular FFT. Due to the close connection of the SFFT to quantum circuits, the associated TTO will have the same number of cores as the original QFT circuit has qubits. Further, the physical dimensionality of our operator will be associated with the dimensionality of the qubits, i.e. it will be set to p=2.

The remaining operands - namely, the local strain  $\varepsilon(\mathbf{x})$ , the mean strain  $\mathbf{E}$ , the Green-Eshelby operator  $\hat{\Gamma}_0(\mathbf{q})$  and the local and isotropic reference stiffnesses  $\mathbf{C}(\mathbf{x})$  and  $\mathbf{C}_0$  - must be transferred into TT format as well. This can be achieved in two steps. First, operands depending on the continuous variables  $\mathbf{x}$  and  $\mathbf{q}$  will be discretized in a binary fashion

$$t(x) \approx t \left( \sum_{j=1}^{n} b_j 2^{-j} \right) = \mathcal{T}(b_1 b_2 ... b_n),$$

(20)

with  $b_j \in \{0,1\}$ , resulting in a multi-index formulation. This binary-fraction approach is generally more effective than a standard discretization of the form  $t(x) \approx t \left[ (k-1) \Delta x \right] = F(k)$ , which relies on a single index variable k. The advantage stems from the ability to separate a greater number of tensor cores - one for each index - thereby enhancing the efficiency of the TT formulation. Additionally, the binary discretization naturally yields an n-th order tensor with physical index dimension p=2, consistent with the dimensionality of the physical indices of the SFFT.

Once the high-order tensor is obtained through application of Equation (20), the cores are separated by applying the Tensor-Cross-Approximation algorithm [32, 39]. In our multidimensional case, dimensions are processed sequentially, with cores grouped by dimension in their TT representations. For instance, in a 2D example with five cores per dimension, the first five cores correspond to the discretization of the x dimension, while the remaining five cores represent the y discretization points per spatial dimension d, corresponding to n cores - analogous to n qubits - per dimension.

For the special case of constant operands, the procedure to obtain a suitable TT is considerably simplified. Specifically, they can be represented directly as a rankone TT by first generating  $(2 \times 2)$  identity matrices and reshaping them into cores of shape  $(2 \times 1 \times 2 \times 1)$ . Each core is then replicated to obtain the required n cores per dimension. Multiplying one of the cores by the constant value of the corresponding operand yields the final TT representation. In the context of the algorithm's iterative procedure, two constant operands are adapted in this manner: the mean strain  $\mathbf{E}$  and the isotropic reference stiffness  $\mathbf{C}_0$ .

Until now, only the "inner" indices, arising from the spatial discretization of the problem, have been considered. In practice, however, we work with tensorial quantities defined in a multidimensional physical space rather than solely with discretization variables. For example, the strain in Voigt notation (see Appendix A) is represented as a vector, while the stiffness is represented as a matrix, introducing one and two additional "outer" indices, respectively. Consequently, these outer indices must be incorporated into the TT formalism. One approach is to treat each operand as a vector (or matrix) whose entries are stored in TT format. While this strategy is valid, greater improvements in both computational speed and memory efficiency are obtained by representing the full operand, including its outer indices, directly in TT form. To this end, we introduce a minor modification of the used TT representation discussed so far by inserting an additional core at the beginning of the TT. This core is allowed to deviate from the previous physical index dimensionality of p=2 and serves as a selector for the different components appearing in the Voigt representation. Thus, it encodes the algebraic structure of the Voigt mapping rather than information associated with the spatial discretization. For simplicity of notation and readability, we refrain from introducing a new abbreviation for this extended representation and continue to refer to it as TT(O) in the following.

The final operator that requires special treatment is the Green-Eshelby operator  $\overline{\varGamma}_0(\mathbf{q})$ . Since this operator resides in momentum space, it must be adapted to comply with the momentum space convention imposed by the SFFT. To achieve this, a reordering of the TT cores is necessary, which involves two steps:

- 1. The indices corresponding to each geometrical dimension d of the initial discretization tensor, obtained via Equation (20), must be reversed.

- 2. The cores need to be complex conjugated.

Applying these additional steps to operators in momentum space ensures consistency with the SFFT convention. After translating the original algorithm into TT format, the final result for the local strain field is obtained by contracting the TT into its full data representation. This contraction is performed by summing over all virtual dimensions of the TT, as defined in Equation (1). Combining all steps results in the final form of the SFFT-based homogenization algorithm, summarized in Algorithm 2.

# **Algorithm 2:** SFFT-based Homogenization Algorithm

In terms of computational speed, the SFFT-based algorithm achieves an exponential acceleration with respect to both the number of discretization points  $N=2^n$  and the geometric dimensionality d, compared to the classical FFT-based homogenization method, provided that the TT ranks remain manageable [24]. This caveat, i.e. the requirement of small ranks, depends crucially on the underlying geometry of the RVE. However, the geometry-dependent term can be precomputed during an offline phase, enabling an informed assessment of the algorithm's applicability prior to executing the full computation.

In the original formulation, after obtaining the TT(O) representations of all operands and operators, the TTs involved in the Hadamard multiplications within the algorithm were lifted to TTOs (see Section 2.1). This elevation enabled the use of optimization-based methods, which are computationally advantageous in CPUbased environments. In particular, this was beneficial for operations involving the high-rank Green-Eshelby operator, for which the adapted AMEn optimization algorithm was employed [40]. In the present work, we take a different approach. Since optimization methods will not be used, we do not elevate the corresponding TTs to TTOs. This leads to a modest reduction in memory consumption, which is better aligned with the limited memory capacity of modern accelerators. Moreover, optimization-based methods rely on repeated SVD computations, making them increasingly unstable under low-precision arithmetic. Avoiding this elevation therefore improves numerical robustness on accelerators. The validity of this modification will be demonstrated and discussed in detail in the numerical experiments presented in Section 5.

# 4. Benchmarking Fundamental Operations

For the simulations we restrict ourselves to combinations between three different hardware configurations and two different compute modes. Specifically, we are using an Dual Intel Xeon Gold 6240R CPU from Intel, an A100 GPU from NVIDIA as well as Googles TPU v4.8. Additional Information on the Hardware specifications used can be found in Appendix D.

For the compute modes, we distinguish between two implementations: (i) An implementation that stored the TT-cores as arrays in a list. The underlying array can either be a JAX [41] or NumPy array [42]. In the following it should be clear whether array-type is used. (ii) An implementation that stores the TT-cores as arrays within another (batched) array. This second version has the drawback that the cores might need to be padded in order to fit the dimensionality of the batched format. We will refer to the first mode as "list-format" while the latter one is called "batched-format". This distinction was made since they tackle different regimes and thus are expected to be the most efficient under different hardware conditions. While the first version is more memory efficient, the latter is tailored to the specific architecture of Googles TPU. However, our benchmarks showed that the list format outperforms the batched format for the high memory needs that we are interested in. To make the upcoming discussion concise, we will restrict ourselves to the discussion about the list-format. A detailed discussion about the differences as well as additional benchmarks on the batched variant can be found in Appendices B and E.

#### 4.1 Software Setup

Google's Tensor Processing Units (TPUs) are programmed through XLA [43], an optimizing compiler that lowers high-level operations (HLOs) to low-level operations (LLOs) executable on the hardware. While HLOs can be written manually, they are typically generated automatically by tracing computations expressed in higher-level programming interfaces—JAX being a prominent example. JAX transforms Python functions into a computation graph and delegates its compilation to XLA, which produces highly optimized GPU and TPU executables.

This compilation is performed just-in-time (JIT). The first invocation of a JIT-compiled function initiates tracing and compilation, making it substantially more expensive than subsequent executions. This initial overhead, commonly referred to as the warm-up phase, can dominate runtime and thereby diminish or even negate the performance benefits of JAX for short-lived programs.

To alleviate this issue, JAX offers persistent compilation, which allows compiled executables to be stored externally and reused across multiple program runs. This mechanism bypasses repeated warm-up overhead and enables stable performance from the first invocation. Since this feature—although still experimental at the time of writing—effectively eliminates warm-up costs for repeated executions, we omit warm-up time from the benchmarks presented in this section.

Originally TPUs were developed as linear algebra accelerators with the use case of performing faster neural network inference. Since speed is of the essence and weights within neural networks generally don't need high accuracy to reach their full potential [44], TPUs are optimized around the fast bfloat16 standard. For our analysis this accuracy is not sufficient. In fact, we will

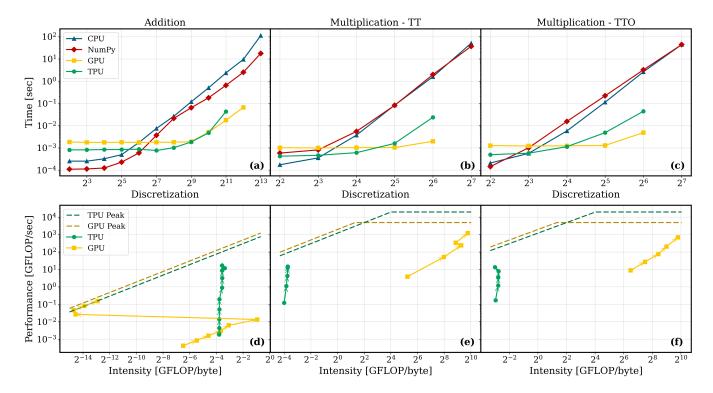

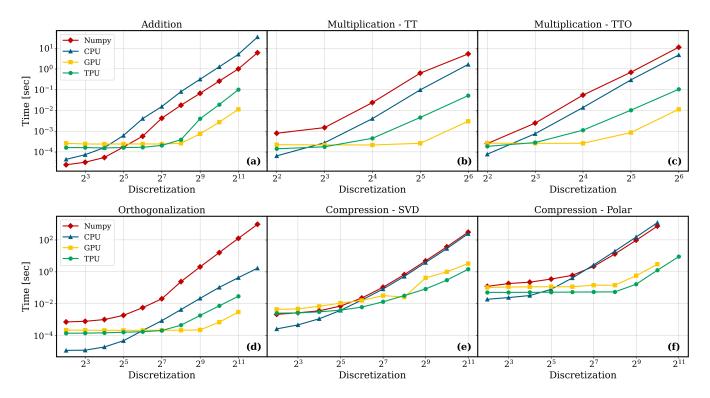

Figure 2: Parallelizable operations for TTs and TTOs. Columns correspond to the operation type: addition of two TTs (a,d), multiplication between two TTs (b,e), and contraction between a TT and a TTO (c,f). The first row shows runtime benchmarks, while the second row shows the Roofline model for GPU and TPU.

need to set the accuracy to its highest possible value of the complex64 standard in order to get accurate results for our use-case. It needs to be stressed that due to our high-accuracy needs, this analysis probes the unfavourable regime of TPUs and therefore can be through to be complementary to standard TPU use-cases.

To ensure a fair comparison to CPU and GPU, we will further adapt their accuracy to the complex64 standard as well. To benchmark the fundamental TT operations, we used Quantized TTs and TTOs with randomly initialized cores. We have obtained the data-points in our upcoming analysis by taking the mean over 100 successive runs per probed operation.

Iteration times were measured using Pythons time it library, averaging over 100 runs per operation. Performance on TPUs was obtained by collecting GFLOPS values through the JAX Profiler. For GPU benchmarking, we used the NVIDIA Tools Extension (NVTX), since in this context the JAX Profiler does not correctly account for computations executed in precompiled CUDA libraries, leading to significantly underestimated GFLOPS measurements.

For both accelerators, certain data points in the high-discretization regime could not be obtained due to out-of-memory (OOM) errors. In the performance benchmarks, OOM conditions arise even at lower discretization levels, because additional figures of merit must be tracked, further reducing the memory available for computation.

The figures in this section are organized as follows. The first row of both Fig. 2 and Fig. 3 shows the average execution time as a function of the number of discretiza-

tion points of the matrix represented by the underlying  $\operatorname{TT}$ . The second row depicts the corresponding Roofline model for both the GPU and  $\operatorname{TPU}$  [45], illustrating the achieved performance P in GFLOP/sec as a function of the arithmetic intensity I, measured in GFLOP/byte. The arithmetic intensity can be obtained through

$$I = \frac{P}{B},\tag{21}$$

by additionally measuring the achieved memory bandwidth B in byte/sec. For visual clarity, the datapoints belonging to a given device (GPU or TPU) are connected by arrows, indicating the progression from one discretization level to the next (i.e.  $2^2 \rightarrow 2^3 \rightarrow 2^4 \rightarrow \dots$ ).

The theoretical peak performance limits  $\hat{P}$  of both accelerators are indicated in the figures, providing a reference to assess whether each operation is memory-bound or compute-bound. According to the Roofline model [45], the achievable performance as a function of the arithmetic intensity I (in GFLOP/byte) is given by

$$\hat{P}(I) = \min(P_{\text{peak}}, I \cdot B_{\text{peak}}),$$

where  $P_{\text{peak}}$  denotes the compute peak (GFLOP/sec) and  $B_{\text{peak}}$  the memory bandwidth (byte/sec), see Appendix D for specific values. The *ridge point* of the Roofline, obtained according to Equation (21) as  $I_{\text{ridge}} = P_{\text{peak}}/B_{\text{peak}}$ , separates memory-bound operations (left of the ridge) from compute-bound operations (right of the ridge), highlighting the dominant performance bottleneck for each TT operation.

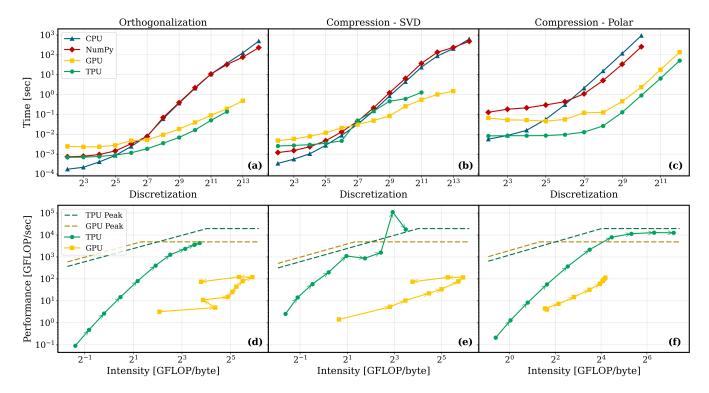

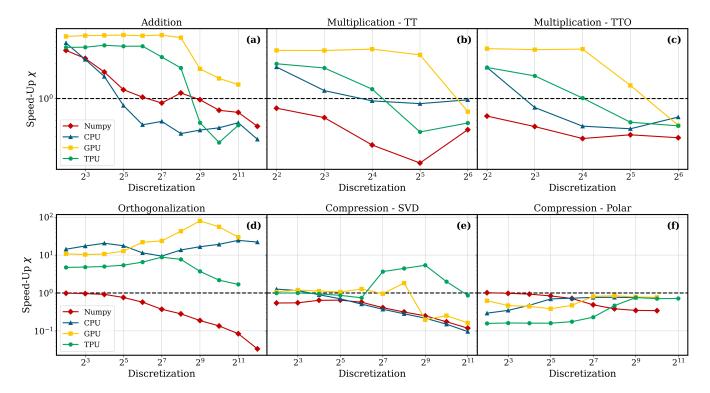

Figure 3: Serial operations for TTs. Columns correspond to the operation type: orthogonalization (a,d), SVD-based compression (b,e), and polar-based compression of a TT (c,f). The first row shows runtime benchmarks, while the second row shows the Roofline model for GPU and TPU.

#### 4.2 Parallelizable Operations

The first row of Figure 2 compares the four compute modes in terms of mean iteration times for three operations on a TT: (a) addition, (b) multiplication between two TTs, and (c) multiplication between a TT and a TTO. These operations are inherently core-to-core operations and therefore highly parallelizable, suggesting the potential for substantial speed-ups on GPU architectures. Indeed, both accelerators exhibit performance improvements of several orders of magnitude over the two CPU modes, which scale exponentially with discretization.

At lower discretization levels, the TPU implementation benefits from relatively low overhead, resulting in a notable speed advantage. However, as the discretization increases, the GPU demonstrates superior scalability, eventually surpassing the TPU in all three operations at the upper end of the probed discretization range.

The second row of Figure 2, which presents the corresponding Roofline model, reveals that TPU performance is strongly memory-bound. As discretization increases, the achieved arithmetic intensity remains nearly constant, while the achieved performance grows significantly. This nearly vertical trend indicates that performance scales almost linearly with memory traffic, highlighting that the TPU is not only limited by memory bandwidth rather than computational throughput but also wont leave this regime for higher discretizations.

For the GPU, the Roofline model reveals an interesting behaviour for the Addition operation shown in subplot (d). Both arithmetic intensity and performance initially increase with growing discretization. However,

after a discretization of 2<sup>7</sup>, a sudden drop in intensity is observed. This can likely be attributed to the L2 cache: for smaller matrices, the cache is large enough to hold all memory associated with the computation, including the input matrices, the output, and any intermediate data. Since Addition is a lightweight operation that generates relatively few additional intermediate values, the entire computation can fit within L2 for smaller discretizations. Once the matrix exceeds the L2 capacity, additional memory accesses must go to slower global memory, resulting in a decrease in arithmetic intensity. After the drop in Intensity, the Performance follows the possible peak performance almost perfectly, suggesting that for the given resources the addition operation optimally uses the available GPU resources. For the remaining subplots (e) and (f), the Roofline model is in the compute-bound regime while its trend for growing discretizations comes close to the maximal possible performance.

#### 4.3 Serial Operations

The first row of Figure 3 shows the execution time of the serial operations on a TT, i.e. (a) Orthogonalization, (b) Compression via SVD and (c) Compression via polar decomposition. The CPU-based implementations are mostly on par with each other, while the only difference occurs for smaller discretization, where the JAX-based approach has lower overhead. Additionally, the NumPy version performs better in case of the polar-based Compression for discretizations above 2<sup>6</sup>. The accelerators show a clear trend, where the TPU outperforms the GPU for the full regime in the case of Orthogonalization

and Polar based Compression. However, the plot seems to indicate tat the GPU implementation for the Orthogonalization has improved growth behaviour in comparison to the TPU. A noteworthy exception is the SVDbased compression in figure (b). Here the TPU speed breaks down around  $2^7$  discretization points. This happens because the SVD on TPU working on complex64 accuracy does not converge. This can be seen in Appendix E were the error plots show a failure of the TPUs SVD procedure in this case. During the evaluation similar problems occurred when testing other methods like the QR decomposition with lower accuracy arithmetic like float 32. Due to this non-convergence, the maximal number of iterations to obtain an SVD solution is reached, resulting in the sudden increase in execution time.

Similar behaviour can be observed in subplot (e) of the second row in Fig. 3. Here, the TPU performance fluctuates noticeably for discretizations beyond 2<sup>7</sup> and even exceeds the theoretical peak performance. This is likely caused by measurement inaccuracies in the JAX Profiler under this regime.

The trends for the remaining subplots, (d) and (f), corresponding to Orthogonalization and Polar compression respectively, are similar: they start in the memory-bound regime and gradually move toward higher arithmetic intensities and achieved performance as the discretization increases. While the compression operation approaches the boundary defined by the Roofline ridge point, the Polar-based compression algorithm transitions into the compute-bound regime, reaching values close to the theoretical upper limit achievable on the TPU.

GPU performance in the mostly serial regime is more variable, which is expected since GPUs are less efficient for predominantly serial workloads. However, subroutines within these operations - such as QR or SVD decompositions - may still exhibit partial parallelism and benefit from GPU acceleration. For subplots (d) and (e), the GPU Roofline model shows initial growth in intensity and performance with increasing discretization until a saturation point is reached. Beyond this point, the arithmetic intensity decreases significantly while performance drops only slightly. This suggests an implicit upper bound on the achievable performance for these mostly serial routines. The true peak performance in this regime lies well below the theoretical maximum, reflecting the limited parallelism. The observed deterioration in intensity can be attributed to a combination of increased memory traffic (e.g., due to padding for larger matrices) and low GPU occupancy, which causes the Streaming Multiprocessors (SMs) to remain idle while waiting for the few active threads to execute.

The last subplot (f) exhibits similar initial behaviour for the GPU but has not yet reached the point of intensity deterioration. Instead, the Roofline trajectory appears to converge near the boundary between the memory-bound and compute-bound regimes.

Overall, the data does not indicate a clear superiority of one accelerator over the other. The choice of hardware depends on the specific workload and the balance

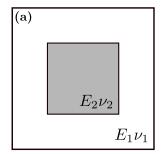

Figure 4: (a) 2D box geometry used in the experiments. Material parameters:  $E_1 = 29/3$  GPa and  $E_2 = 4/3$  GPa with Poisson ratios  $\nu_1 = \nu_2 = 1/3$  for the grey and white regions, respectively. (b) Local stress field  $\sigma_{yy}$  under tensile load obtained after running the quantum-inspired homogenization algorithm on a TPU.

between serial and parallelizable fundamental TT operations in a given application. However, both accelerators are orders of magnitudes faster than reference implementations performed on CPU.

# 5. Accelerated Quantum-Inspired Homogenization

In this section, we extend the insights obtained from the preceding analysis to a realistic application scenario involving the SFFT-based homogenization algorithm [24]. We benchmark the JAX list-based implementation on both GPU and TPU architectures, using the NumPy mode as a baseline reference. As in the original formulation of the SFFT-based scheme, we employ an adaptive-rank procedure.

Additionally, we include warm-up times in the final benchmarking procedure. This is necessary because, within the adaptive-rank setting, the final tensor ranks are not known a priori. Consequently, the shapes of intermediate tensors cannot be predetermined. These shapes emerge dynamically during the execution of the algorithm, and each newly encountered shape may trigger additional JIT compilations. Accounting for this overhead is essential for obtaining realistic performance measurements.

The benchmarking results for the fundamental TT operations in Section 4 indicate that the standard SVD-based compression becomes unreliable in highly discretized regimes due to ill-conditioning intrinsic to the underlying SVD algorithm. Motivated by this, we introduce two modifications to the original implementation of the SFFT-based homogenization algorithm to ensure numerical robustness.

First, instead of applying the AMEn algorithm, which relies heavily on repeated SVD operations, we compute the contraction between the Green-Eshelby operator  $\hat{\Gamma}$  and the polarization  $\hat{\tau}$  using standard TTO-multiplication (see Algorithm 2). Second, exclusively on TPU, we replace the conventional SVD-based compression with the Polar-based variant, which provides significantly improved stability in high-resolution regimes.

For the application of the homogenization algorithm, we restrict ourselves to the two-dimensional box geome-

try shown in Figure 4 (a). We further set the compression accuracy to  $\epsilon = 10^{-8}$  for all runs.

#### 5.1 Coarse-Graining Approach

Directly recompiling a jitted function for each rank that may arise during the simulation is inefficient, as the accumulated warm-up times would outweigh any potential speed-up. To mitigate this issue, we introduce a coarsegraining strategy for the TT-ranks.

Instead of allowing each core rank  $r_c$  to assume any positive integer value, we restrict it to the form  $r_c = n r_0$   $(n, r_0 \in \mathbb{N}^+)$ , where  $r_0$  is a prescribed minimal base rank and n denotes its multiplicity. These parameters are chosen to reduce the number of distinct tensor shapes encountered during execution, thereby minimizing recompilation events while still retaining the benefits of rank adaptivity. Selecting  $r_0$  equal to or larger than the naturally emerging maximal rank r would eliminate adaptivity entirely and effectively yield a fixed-rank method.

Coarse-graining is introduced through a lightweight modification of the compression algorithm. Instead of adapting the rank dimension iteratively during compression, we first set all singular values above the truncation threshold to zero and record the corresponding threshold index. After collecting these truncation indices across all cores, a separate coarse-graining function applies the truncation according to the aggregated parameters. This separation of responsibilities ensures that tensor shapes remain unchanged inside the jitted compression routine.

Importantly, no further modifications are required for other TT operations. Addition, multiplication, and related algebraic operations naturally yield new TTs whose intermediate ranks follow from the algebraic structure of the involved cores - the resulting ranks grow additively or multiplicatively in terms of the original ranks.

For our experiments, we set the minimal base rank to  $r_0 = 16$ . This value may be further refined by allowing  $r_0$  to depend on the discretization rather than treating it as a constant.

#### 5.2 Results

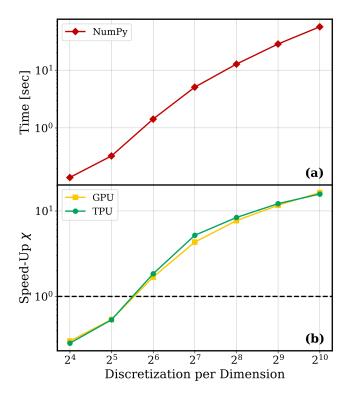

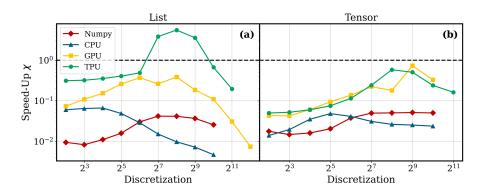

Running our adaptation of Algorithm 2 on different compute devices requires the same number of iterations to converge to the specified tolerance of  $\delta_{\rm tol}=10^{-4}$ . Consequently, the key performance metrics are the average time per iteration,  $\tau$ , of the SFFT-based homogenization algorithm, and the achieved speed-up  $\chi=\tau_{\rm cpu}/\tau_{\rm acc}$  to measure the accelerators performance. Figure 5(a) shows the reference implementation using the NumPy CPU mode, while Fig. 5(b) reports the speed-up obtained on GPU and TPU relative to the CPU implementation for increasing discretization sizes. A qualitative result for the local-stress field obtained on TPU is shown in Fig. 4 (b).

For small discretizations of approximately  $2^4-2^5$  points per dimension, the overhead introduced by

Figure 5: Benchmarking results for the SFFT-based homogenization algorithm: (a) average time per iteration on the CPU (NumPy), and (b) achieved speed-up on GPU and TPU (JAX) for increasing discretizations.

host—device memory transfers makes the CPU implementation preferable. Beyond this regime, both accelerators clearly outperform the CPU, achieving a maximum measured speed-up of over 10x at 2<sup>10</sup> points per dimension (or 1 million pixels). Higher discretization values could not be reached experimentally, as the accelerators encountered out-of-memory limitations. Even larger discretizations may be achievable by adapting the algorithm to incorporate batched processing, which would reduce memory load at the cost of some computational speed.

It is worth noting that both accelerators deliver comparable speed-ups, despite the GPU benefiting from a more mature software and hardware ecosystem, whereas TPU support and tooling are still under development [46]. Additionally, we employed the Polar-based compression on the TPU, while the GPU used the faster SVD-based compression. This suggests that, since the TPU already matches GPU performance using the more conservative Polar-based compression, future generations - once the current limitations of high-accuracy complex64 SVD are addressed - could potentially outperform current GPUs.

#### 6. Conclusion

In this work, we presented two major contributions advancing the practical use of Tensor Train methods on modern hardware accelerators and demonstrating their applicability to large-scale, quantum-inspired computational homogenization.

Our first contribution is a systematic, cross-platform

benchmarking study of fundamental Tensor Train operations on CPUs, GPUs, and TPUs using the JAX and NumPy framework. The results show that GPUs outperform TPUs primarily for highly discretized problems that are inherently parallelizable. For smaller problem sizes, as well as for operations with a more serial computational structure, TPUs consistently exhibit superior performance across the tested regime. While GPUs are predominantly compute-bound throughout the benchmark, TPU performance varies: it is strictly memory-bound for highly parallel operations, and transitions from memory-bound at small problem sizes to compute-bound at larger discretizations for more serial tasks. Despite being a less mature hardware platform, TPUs delivered notable performance in our tests. We did, however, observe persistent numerical instabilities on TPUs for certain linear-algebra routines (e.g., SVD) in complex64), though these limitations are expected to diminish as the TPU ecosystem continues to mature.

Our second contribution applied these insights to the implementation of the Quantum-Inspired (SFFT-based) Homogenization algorithm under realistic, high-memory conditions. Running a fully rank-adaptive algorithm in JAX required several modifications, including a coarse-graining strategy to mitigate the substantial warm-up costs associated with JIT compilation. Even under these constraints, GPU and TPU implementations achieved substantial and nearly identical speed-ups for practical use cases, saturating around one order of magnitude in the tested regime. Because the GPU version could employ fast SVD-based compression, while the TPU required the more stable but slower polar-based compression, we expect the TPU advantage to grow as its numerical libraries continue to improve.

A remaining practical limitation is the JAX warm-up time: each admissible coarse-grained rank triggers additional compilations during the early stages of the algorithm. However, upcoming JAX features enabling persistent caching of compiled functions, together with the possibility of treating JIT compilation as a preprocessing step, are expected to substantially reduce this overhead. At the time of writing, these features remain experimental. Further speed-ups are anticipated once the SVD-based routines, particularly those required in high-memory settings, become numerically robust on TPUs. This enables not only SVD-based compression but also the integration of optimization-based TT algorithms.

Overall, our findings establish a foundation for large-scale, high-performance homogenization on modern accelerators. They highlight the complementary strengths of GPUs and TPUs for different TT workloads and point toward a pathway for industrial-scale deployment of low-rank Tensor-Network techniques in computational materials science, bridging the gap between high-resolution experimental data and feasible computation.

Future work may extend these ideas in several promising directions. Higher-order tensor network architectures, such as Tree Tensor Networks or Projected Entangled Pair States, could further reduce memory footprints and enable even larger discretizations. Additionally, developing a batched, hardware-accelerated quantum-

inspired homogenization pipeline would allow the efficient processing of large ensembles of material samples, supporting upcoming data-driven applications.

# 7. Acknowledgment

The authors thank Dr. Mazen Ali for many valuable and insightful discussions. This research was supported in part through the use of Cloud TPUs provided by Google's TPU Research Cloud (TRC) program. Further, we thank BMWK for the financial support provided under the EniQmA project. The authors gratefully acknowledge funding from the German National High Performance Computing (NHR) association for the Center NHR South-West. To enhance readability and ensure comprehensiveness, portions of this manuscript were refined with the assistance of FhGenie.

# A. Extracting the Stiffness Tensor

Working with full tensor representations can be cumbersome both in terms of clarity and computational efficiency. We therefore adopt Voigt notation, representing stress and strain tensors as 3-dimensional vectors in 2D space, as shown in Table 1. This convention can be extended to the fourth-order stiffness tensor, which then becomes a  $3 \times 3$  matrix.

It should be noted that the factor of 2 for the offdiagonal strain components is included to ensure that the free energy of the system

$$F = \frac{1}{2} \sum_{i=1}^{3} \sum_{j=1}^{3} \sigma_{ij} \epsilon_{ij}$$

is correctly represented [47, 48]. This is purely a convention and could, in principle, be defined differently.

Using Voigt notation, the macroscopic strain-stress relationship (12) can be written as a simple matrix-vector product, greatly simplifying computations. By setting the mean strain vector  $\mathbf{E}$  such that only its k-th component is unity, we further obtain

$$\sigma_i^{\text{eff}} = \mathbf{C}_{ij}^{\text{eff}} \delta_{jk} = \mathbf{C}_{ik}^{\text{eff}},$$

allowing the k-th column of  $\mathbf{C}^{\text{eff}}$  to be read directly from the macroscopic stress vector. Repeating this procedure for all components of  $\mathbf{E}$  constructs the full effective stiffness matrix systematically.

To determine the macroscopic stress, the mean strains are provided as inputs to Algorithm 1. Since the output is formed by the local stresses, we can averaging over the RVE to obtain the needed macroscopic stresses

$$\sigma^{\text{eff}} = \frac{1}{|\mathcal{V}|} \int_{\mathcal{V}} \sigma_m(\mathbf{x}) \, d\mathbf{x} = \frac{1}{|\mathcal{V}|} \int_{\mathcal{V}} \mathbf{C}(\mathbf{x}) \, \varepsilon_m(\mathbf{x}) \, d\mathbf{x}.$$

#### B. Alternative Tensor Format

In this section we want to give additional benchmarking results obtained for the batched format and further compare them with the used list-based format in terms of achieved speed-up. For this, we define the speed-up  $\chi = \frac{\tau_{\rm batch}}{\tau_{\rm list}}$ , with the mean run times  $\tau_{\rm list}$  and  $\tau_{\rm batch}$  for the list-based and batched implementations, respectively.

The results for the absolute time obtained per benchmarked operation are shown in figure 6. It can be

Table 1: Voigt notation for stress and strain tensors for 2D geometries

| Tensor               | Full form                                                                                                  | Voigt form                                                                       |

|----------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Strain $\varepsilon$ | $\begin{bmatrix} \varepsilon_{xx} & \varepsilon_{xy} \\ \varepsilon_{xy} & \varepsilon_{yy} \end{bmatrix}$ | $egin{bmatrix} arepsilon_{xx} \ arepsilon_{yy} \ 2arepsilon_{xy} \end{bmatrix}$  |

| Stress $\sigma$      | $\begin{bmatrix} \sigma_{xx} & \sigma_{xy} \\ \sigma_{xy} & \sigma_{yy} \end{bmatrix}$                     | $\left[egin{array}{c} \sigma_{xx} \ \sigma_{yy} \ \sigma_{xy} \end{array} ight]$ |

seen that the general trend for the different operations and compute platforms follow a similar trend than the ones obtained for the list-based implementations shown in Fig. 3 and 2. Concerning the JAX-CPU and NumPy versions of the shown operations, it becomes clear that the JAX-implementation can be significantly faster in comparison to the list-based implementation. This shows the improvement that JAX can have on the optimization of the underlying code in the case of ever growing matrices. We can see further that the TPU seems to reach its maximal potential - indicated by a near zero gradient - for smaller discretizations as for the list-based approach. This is not seen for the GPU version, suggesting that in the batched format GPUs are superior.

The figure of merit that is most interesting for us is the obtained speed-up  $\chi = \tau_{\rm batch}/\tau_{\rm list}$  defined through the mean execution time  $\tau_{\rm list}$  and  $\tau_{\rm batch}$  for the list- and batched format, respectively. The results for the speed-up of the six fundamental Tensor Train operations are shown in Fig. 7. For all parallelizable operations shown in subplots (a)-(c), we see that the speed-up typically starts around  $\chi$  between 1 and 10 but slowly deteriorates such that in all but one case the speed-up is below the break-even point. This suggest that the list-based format is preferable for higher discretizations.

For the serial operations shown in subplots (d)-(f), the matter is slightly more complex. The Orthogonalization shown in subplot (d) shows significant speed-up that does only seem to deteriorate surely for the NumPy implementations. All other implementations stay above the break-even line without clear indication of them losing their speed-up edge. For the SVD-based compression subplot (e) shows a clear trend that the speed-up deteriorates across the full probed regime suggesting that the list-based format is superior in this case. The only exception being the discretization points above  $2^7$  for the TPU version. However, as already discussed earlier, this regime is prone to extremely high errors and is thus not representable. The last subplot (f) shows the speed-up for the Polar-based compression algorithm between the two implementations. Here the results are quite clear on that the speed-up stays below the break-even pint, even though its quite close to it.

All in all, the results presented in Fig. 7 show that the list-based implementation is superior for high discretizations.

# C. SVD- vs Polar-based Compression Benchmark

As suggested in the main text, the SVD-based Compression should be significantly faster than the Polar-based approach. However, only as long as the underlying matrix is well behaved. The results obtained for the relative speed-up  $\chi = \frac{\tau_{\rm Polar}}{\tau_{\rm SVD}}$  defined through the mean single iteration time for the SVD- and Polar-based compression,  $\tau_{\rm SVD}$  and  $\tau_{\rm Polar}$  respectively, for both the list-based and batched format are shown in Fig. 8. It can be seen that only the TPU implementation in the List format

Figure 6: Timing for the Tensor Variant

can cross the break-even point at  $\chi=1$ . Thus, only for this specific case we can actually get a faster implementation if one would choose the Polar-based variant. This however, only occurs at and after a discretization of  $2^7$ , which is the same discretization at which the SVD-based algorithm starts to fail anyway, see Appendix E. Thus, we can conclude that the SVD-based approach is preferable over the Polar-based algorithm as long as it is applicable. We can further see that the batched version has smaller variations in its speed-up factor and seems to even become stable for the JAX and NumPy based CPU implementations. Hence, our initial hypothesis on the SVD- and Polar-based conundrum are correct for all checked compute platforms.

## D. Hardware Specifications

The following tables summarize the hardware specifications of the compute nodes used in our experiments. The CPU and GPU nodes (see Tables 2 and 3) were part of the Beehive Cluster at Fraunhofer ITWM. Access to the TPU was provided through Google's TPU Research Cloud, with specifications listed in Table 4.

Table 2: CPU node hardware specifications.

| Component          | Specification                      |

|--------------------|------------------------------------|

| Cluster            | MPI3                               |

| Compute nodes      | 108 (Dell PowerEdge C6420)         |

| CPU                | Dual Intel Xeon Gold 6240R         |

| CPU cores per node | 48                                 |

| RAM per node       | 384 GB (8 GB per core)             |

| Storage            | 480 GB SSD                         |

| Network            | 10 GiB Ethernet, HDR100 Infiniband |

Since Google does not provide official peak through-

Table 3: NVIDIA A100 80GB PCIe system specifications [49].

| Component               | Specification                |

|-------------------------|------------------------------|

| Architecture            | Ampere                       |

| GPU Memory              | 80  GB HBM2e                 |

| Memory Bandwidth        | 1,935  GB/sec                |

| Peak Performance        | 9.7 TFLOP/sec (FP64)         |

|                         | 19.5 TFLOP/sec (FP32)        |

| Tensor Core Performance | 19.5 TFLOP/sec (FP64)        |

|                         | 156 TFLOP/sec (FP32)         |

|                         | 312 TFLOP/sec (BF16 or FP32) |

|                         | 624 TFLOP/sec (int8)         |

| Form Factor             | PCIe dual-slot air-cooled or |

|                         | single-slot liquid-cooled    |

| Interconnect            | PCIe Gen4 (64 GB/s)          |

| TDP                     | 300 W                        |

Table 4: TPU v4.8 system specifications [50, 51]

| Component                       | Specification      |

|---------------------------------|--------------------|

| TPU type                        | v4.8               |

| Peak performance                | 275 TFLOP/sec      |

|                                 | (BF16 or int8)     |

| HBM2 capacity & bandwidth       | 32 GiB, 1,200 GB/s |

| Power consumption (min/avg/max) | 90/170/192  W      |

| TPU-Pod size                    | 4,096 chips        |

| Interconnect topology           | 3D-Mesh            |

| Peak compute per Pod            | 1.1 EFLOP/sec      |

|                                 | (BF16 or int8)     |

| All-Reduce bandwidth per Pod    | 1.1 PB/sec         |

| Shared bandwidth per Pod        | 24 TB/sec          |

put values for complex64 arithmetic on TPU v4.8 systems, we estimate the corresponding performance based on the published BF16 peak. We therefore estimate an upper bound from the publicly documented BF16 tensor-core peak performance. A TPU v4-8 slice reaches

Figure 7: Speed-Up Factors (Speed-Up over List) between list vs batched format.

Figure 8: Speed-Up Factors between the Polar- and SVD-based Compression methods for both (a) the List-based implementation and (b) the batched implementation. The dashed-black line corresponds to the break-even point.

up to

$$P_{\rm BF16} = 275 \text{ TFLOP/sec.}$$

Assuming FP32 throughput is roughly half of BF16 throughput (a common precision-scaling heuristic for TPU MXUs), and using the standard cost of eight real floating-point operations per complex multiply—accumulate, we estimate

$$P_{\rm c64} \approx \frac{P_{\rm BF16}/2}{8} = 17,187 \ {\rm TFLOP/sec.}$$

This number serves only as a theoretical upper bound, complementary to the vendor peak-performance figures shown in Table 4.

#### E. Accuracy Results

Due to clarity we want to share the results obtained for the numerical accuracy obtained for the list-based implementation for the different probed operations. The figure of interest is the relative error defined through

$$\sigma_{\rm err} = \frac{||\alpha_{\rm JAX} - \alpha_{\rm NumPy}||_2}{||\alpha_{\rm NumPy}||_2},\tag{22}$$

where  $\alpha_{\rm JAX}$  is the result obtained by running either the JAX implementation on CPU, GPU or TPU. Analogously  $\alpha_{\rm NumPy}$  is the result obtained from the reference NumPy implementation performed on CPU.

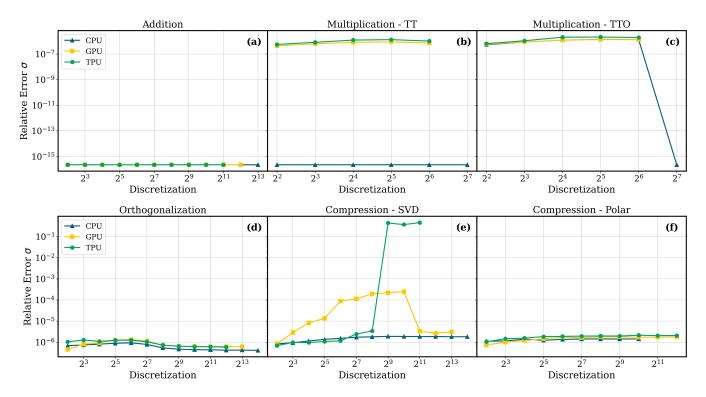

The results of the relative error  $\sigma$  for different compute platforms is shown in Fig. 9. Most results are either around machine precission or at least below  $10^{-6}$ . However, the only result that breaks with this is subplot (e) showing the SVD-based compression. First, the result for the GPU suggest an instability for the intermediate regime. This may occur because the GPU pads incoming matrices to specific sizes to make optimal use of them. However, if the padding is quite large, this may result in bad conditioning and worse performance

Figure 9: Relative Errors between the JAX and NumPy implementations on different Hardware.

of the SVD algorithm. The second problem arises from the TPU version of JAX. Here the error begins to rise around a discretization around  $2^7$  and breaks down complete around  $2^9$ . This suggests that the SVD algorithm didn't converge in this case and making the algorithm effectively unusable on TPU.

#### References

- [1] C. C. Mei, J.-L. Auriault, C.-O. Ng, Some applications of the homogenization theory, Adv. Appl. Mech. 32 (1996) 277–348.

- [2] P. D. Jablonski, J. A. Hawk, Homogenizing advanced alloys: Thermodynamic and kinetic simulations followed by experimental results, JMEPEG 26 (2016) 4–13.

- [3] Y. Wang, L. Hou, H. Su, Q. Tian, K. Yu, D. Eskin, L. Katgerman, L. Zhuang, Tuning homogenization of high-strength aluminum alloys through thermodynamic alloying approach, Mater. Des. 221 (2022) 110975.