# Algorithm-hardware co-design of neuromorphic networks with dual memory pathways

Pengfei Sun<sup>1†</sup>, Zhe Su<sup>2†</sup>, Jascha Achterberg<sup>3†</sup>, Giacomo Indiveri<sup>2</sup>, Dan F.M. Goodman<sup>1</sup>, Danyal Akarca<sup>1,4,5\*</sup>

\*Corresponding author(s). E-mail(s): d.akarca@imperial.ac.uk; Contributing authors: p.sun@imperial.ac.uk; zhesu@ini.ethz.ch; jascha.achterberg@dpag.ox.ac.uk; giacomo@ethz.ch; d.goodman@imperial.ac.uk;

<sup>†</sup>These authors contributed equally to this work.

#### Abstract

Spiking neural networks excel at event-driven sensing yet maintaining taskrelevant context over long timescales. However building these networks in hardware respecting both tight energy and memory budgets, remains a core challenge in the field. We address this challenge through novel algorithm-hardware co-design effort. At the algorithm level, inspired by the cortical fast-slow organization in the brain, we introduce a neural network with an explicit slow memory pathway that, combined with fast spiking activity, enables a dual memory pathway (DMP) architecture in which each layer maintains a compact low-dimensional state that summarizes recent activity and modulates spiking dynamics. This explicit memory stabilizes learning while preserving event-driven sparsity, achieving competitive accuracy on long-sequence benchmarks with 40-60% fewer parameters than equivalent state-of-the-art spiking neural networks. At the hardware level, we introduce a near-memory-compute architecture that fully leverages the advantages of the DMP architecture by retaining its compact shared state while optimizing dataflow, across heterogeneous sparse-spike and dense-memory pathways. We show experimental results that demonstrate more

<sup>&</sup>lt;sup>1</sup>Department of Electrical and Electronic Engineering, Imperial College London.

<sup>&</sup>lt;sup>2</sup>Institute of Neuroinformatics, University of Zurich and ETH Zurich.

<sup>3</sup>Centre for Neural Circuits and Behaviour, University of Oxford.

<sup>4</sup>Imperial-X, Imperial College London.

<sup>&</sup>lt;sup>5</sup>MRC Cognition and Brain Sciences Unit, University of Cambridge.

than a  $4\times$  increase in throughput and over a  $5\times$  improvement in energy efficiency compared with state-of-the-art implementations. Together, these contributions demonstrate that biological principles can guide functional abstractions that are both algorithmically effective and hardware-efficient, establishing a scalable co-design paradigm for real-time neuromorphic computation and learning.

# 1 Introduction

Brains solve temporal problems in real time and under tight energy budgets, that are unmatched in artificial systems. One hypothesis for the brain's superior temporal processing abilities is that their computation is both continuous time and event-driven, based on discrete sparse spiking. Spiking neural networks (SNNs) inherit these two core principles, making them a promising and biologically grounded complement to dense artificial neural networks (ANNs) [1, 2]. Yet one brain-like ability critically important for temporal processing remains hard to reproduce efficiently: retaining information over behaviorally relevant timescales. Standard leaky integrate-and-fire (LIF) neurons integrate spikes into a decaying membrane potential [3] which captures instantaneous evidence but progressively suppresses older inputs over time scales of milliseconds [4, 5]. Conversely, precise temporal codes (e.g., time-to-first-spike) preserve timing but do not carry graded intensity over long windows [6–8]. Another way of thinking about this is that a purely feedforward SNN typically captures either what happened or when it happened, but not both. The fundamental challenge is therefore maintaining long-range temporal context without sacrificing event-driven efficiency.

Several strategies have been explored to extend temporal capacity in SNNs [9]. One approach augments recurrence, often via heterogeneous time constants or adaptive thresholds [10–14], allowing activity to persist through feedback. Another exploits biologically inspired transmission delays (axonal, synaptic, or dendritic) to align spikes to task-relevant timescales and act as implicit temporal buffers [15–24]. Both strategies improve temporal integration, yet each imposes substantial implementation costs in hardware. Dense recurrence scales quadratically with layer width, erodes sparsity benefits, and requires continuous recirculation of activity which increases both the memory footprint and energy consumption. Long, learnable delays avoid explicit recurrence but can demand deep on-chip buffers and per-connection timing metadata, inflating area, power, and latency in neuromorphic implementations [25]. This creates a design challenge: temporal memory mechanisms must be sufficiently expressive to capture long-range dependencies while remaining compatible with efficient neuromorphic implementation. Addressing this requires reconsidering both algorithmic structure and hardware design [26, 27].

The mammalian cortex inspires a potential architectural solution. Cortical circuits maintain efficient long-range temporal context through dendritic branches that integrate inputs over a spectrum of timescales, while neuronal populations exhibit correspondingly heterogeneous temporal constants that shape fast somatic spiking without requiring dense global recurrence [24, 28, 29]. Recent evidence suggests that cortical networks dynamically recruit fast and slow computational pathways according

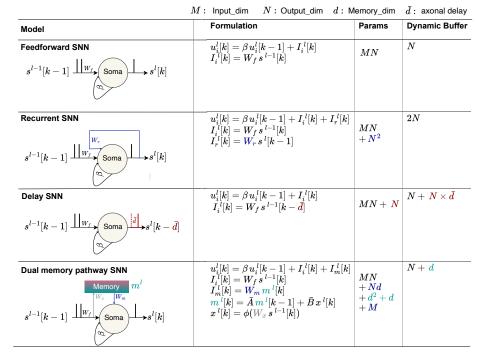

Fig. 1: From fast-slow cortical motifs to the dual memory pathway architecture. a Schematic comparison of Feedforward SNN, Recurrent SNN, Delay SNN, and the proposed Dual memory pathway SNN, highlighting their discrete-time formulations, parameter counts, and dynamic buffer requirements. M, N denote input/output widths and d the memory dimension ( $d \ll N$ ). b Dual memory pathway abstraction: at the algorithmic level (left), each layer maintains a shared, low-dimensional state that captures slow contextual dynamics and modulates fast spiking activity; at the hardware level (right), this separation is mirrored by a heterogeneous accelerator that keeps the compact state on-chip and fuses sparse and dense computations for efficient execution.

to task demands, revealing a functional organization built around multiple interacting timescales [30, 31]. We distill this into a functional abstraction: pair fast spiking dynamics with compact temporal memory. Following this abstraction, we introduce a memory-augmented spiking architecture in which each layer maintains a low-dimensional state vector  $m \in \mathbb{R}^d$ , with  $d \ll N$  for a layer of N spiking neurons. This state evolves under well-conditioned slow dynamics and feeds back as an additional input current to the neurons. Rather than storing full spike histories or broadcasting dense recurrent activity, the network compresses recent activity into a few slow modes and exposes that compressed context at each timestep.

To fully exploit the advantages afforded by this memory architecture, we introduce a digital near-memory-compute architecture that employs heterogeneous dataflow optimization to maximize arithmetic intensity. This design overcomes limitations of prior hardware, in which conventional recurrent SNN accelerators must scale both parameter storage and computation quadratically [32], while hardware supporting long learnable delays requires deep buffers in digital implementations [33] or large capacitors in mixed-signal designs [23], both significantly increasing energy consumption and chip area. The algorithmic structure we propose inherently enables a low-memory-footprint design that avoids these costs. Through algorithm-hardware co-design, we empirically observe that our system matches or outperforms recurrent and delay-based SNNs on event-driven auditory classification and long-horizon sequential inference, all while using only a small number of memory states. Post-layout simulations of the proposed hardware architecture in an advanced 22FDX technology demonstrate more than  $4 \times$  higher throughput and over  $5 \times$  better energy efficiency compared with SOTA designs.

Overall, we show how efficient temporal processing can be achieved through hardware-algorithm co-design inspired by circuit motifs in the brain. Imposing hardware considerations at the algorithmic level results in a network architecture with a temporal memory that is explicit and low-rank. By designing hardware around explicit memory and applying carefully orchestrated optimizations, we obtain a heterogeneous dataflow structure that efficiently integrates fast and slow memory. Jointly, this algorithm and hardware pairing achieves benchmark-beating temporal processing capabilities alongside SOTA energetic efficiency. We open-source the hardware architecture to enable community adoption and further co-design exploration.

#### 2 Results

# 2.1 Dual memory pathways for efficient temporal computation

Feedforward spiking networks (FSNNs) are computationally efficient but perform poorly on tasks requiring long temporal dependencies, as their leaky membranes encode only transient evidence and rapidly forget past inputs. Recurrent SNNs (RSNN) extend temporal integration by feeding activity back within each layer, enabling longer retention but at the cost of quadratic scaling and high memory traffic that erode event-driven efficiency. Recent delay-based SNNs (DSNN), particularly those with learnable axonal delays, address this limitation by distributing memory across time, achieving remarkable performance on neuromorphic benchmarks with only

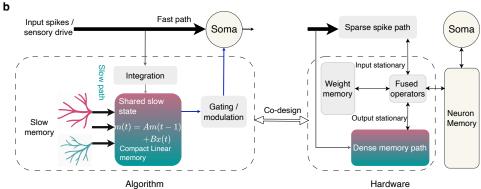

Fig. 2: Accuracy-efficiency across temporally structured benchmarks. a Test accuracy on PS-MNIST, SMNIST, SHD, and SSC for the proposed DMP-SNN. For all the datasets, the grey dashed circle highlights the two configurations of DMP-SNN: Solution I (parameter-efficient, matching state-of-the-art performance) and Solution II (accuracy-parameter trade-off, higher-capacity with low parameter cost). b Learning curves for baseline and the proposed DMP-SNN on PS-MNIST, S-MNIST, SHD, and SSC. Performance deviation represents standard error across n=5 independent runs. Under identical training settings and neuron counts, the DMP-SNN starts from a higher accuracy and converges rapidly, consistently outperforming baseline across datasets. c Comparison of DMP-SNN with recent strong SNN models. DMP-SNN matches or outperforms prior work while using a purely feedforward architecture and notably fewer parameters. We compared the recent FSNN[34], DSNN[17], RSNN[34], LSNN[14], GLIF [35], PLIF[10], ASRNN [13], SRNN[36], DH[24], TC-LIF[37], Rhythm[38].

linear parameter complexity  $(\mathcal{O}(N))$  [39]. However, these models rely on deep programmable buffers, which can increase hardware cost and latency. Here, we introduce the dual memory pathway (DMP) architecture for spiking neural networks (DMP-SNN), which replaces these costly mechanisms with a compact, shared slow state that summarizes recent activity and feeds back as an additional input current (see **Figure 1a**). Acting as an explicit low-dimensional working memory, at only 5% of the hidden

width, this state preserves the temporal context relevant to the task over behaviorally meaningful timescales while remaining fully compatible with efficient hardware implementation (**Figure 1b**).

We evaluated this dual memory pathway architecture on two classes of sequential benchmarks. The first class targets long-range visual integration. In Sequential MNIST (S-MNIST), each 28 × 28 image is presented as a 784-step pixel stream, requiring integration across hundreds of steps. In Permuted Sequential MNIST (PS-MNIST), a fixed random permutation destroys local spatial structure, so performance depends almost entirely on long-range temporal memory [40]. The second class targets event-based auditory classification [34]. The Spiking Heidelberg Digits (SHD) dataset encodes spoken digits as 700-channel spike trains generated by a cochlear model, and the Spiking Speech Commands (SSC) dataset similarly represents 35 spoken-word categories. Together, these benchmarks span dense, clocked sequences and irregular, event-driven input, and probe temporal dependencies on different timescales.

We benchmarked four spiking network architectures: FSNN, RSNN, DSNN, and our DMP-SNN (**Table 1**). FSNNs fail on long-range structure (11.3% on PS-MNIST). Recurrence in RSNNs improves temporal integration (71.0% on PS-MNIST; 71.4% on SHD) but scales as  $\mathcal{O}(N^2)$ . DSNNs perform well on auditory tasks (91% on SHD; 70% on SSC) by learning axonal timing, but require long programmable delays. The DMP-SNN reaches 99.3% on S-MNIST and 97.3% on PS-MNIST. Our method matches delay-based models on SHD and SSC, and in the single-layer SSC setting outperforms them. Figure 2a shows that even a small number of memory states yields consistent gains, and that once the state buffer length exceeds roughly 25% of the sequence, performance is already competitive, indicating that the relevant temporal information has been captured. Figure 2b illustrates the learning dynamics of the baseline model relative to the DMP-SNN, showing that memory-augmentation leads to both quicker convergence and higher accuracy. Cruicially, this is achieved using only a lowdimensional auxiliary state with  $\mathcal{O}(d)$  overhead, where  $d \ll N$  (typically 5–10% of the hidden width) can match or exceed SOTA performance with fewer parameters while providing long-timescale context (see solution I, the most parameter efficient solution, and solution II, the best performing solution, in Figure 2c) [13, 14, 24, 35, 38, 41, 42].

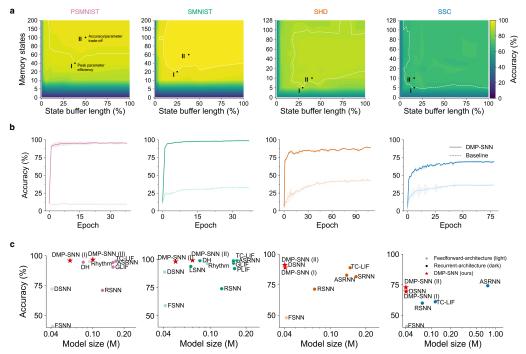

# 2.2 Context-dependent temporal demands reveal design trade-offs

We next examined how frequently the auxiliary memory must be updated within the dual pathway architecture. To do this, we imposed temporal sparsity by updating the membrane potential over fixed numbers of steps. We found that sequence-vision tasks (S-MNIST, PS-MNIST) were largely unaffected even at a skip length (dilation) of 10, whereas auditory tasks (SHD, SSC) degraded much sooner. Regular dense inputs therefore tolerate coarse updates, while irregular spike streams require tighter coupling (**Figure 3a**) which, foreshadowing our later results, is favorable for hardware since less frequent updates lower the switching activity and memory traffic with little loss on long-horizon vision benchmarks.

Recent spiking state-space architectures have attempted to remove the feedforward drive (fast pathway) entirely, compensating through residual connections and

Table 1: Performance on temporally structured benchmarks. Test accuracy (%) on PSMNIST, SMNIST, SHD, and SSC for four model families: FSNN, RSNN, DSNN, and the proposed DMP-SNN. For SSC, results are shown for networks with one and two hidden layers (1-layer / 2-layer). Beige rows mark DMP-SNN in three settings: Solution I (the most parameter-efficient, matching strong baselines), Solution II (accuracy-efficiency trade-off, achieving high accuracy and maintaining low parameter cost), and Peak accuracy. Chancelevel accuracy is shown for reference.

| Model                            | Parameters                  | Accuracy (%)          |

|----------------------------------|-----------------------------|-----------------------|

| PS-MNIST                         |                             |                       |

| FSNN                             | 42K                         | 11.30                 |

| RSNN                             | 122K                        | 71.00                 |

| DSNN                             | 43K                         | 72.06                 |

| DMP-SNN $(I)$                    | 61K                         | 95.50                 |

| DMP-SNN (II)                     | 102K                        | 96.65                 |

| DMP-SNN ( <b>Peak accuracy</b> ) | 202K                        | 97.32                 |

| S-MNIST                          |                             |                       |

| FSNN                             | 42K                         | 59.00                 |

| RSNN                             | 122K                        | 74.00                 |

| DSNN                             | 43K                         | 88.79                 |

| DMP-SNN $(I)$                    | 51K                         | 98.08                 |

| DMP-SNN (II)                     | 73K                         | 99.20                 |

| DMP-SNN ( <b>Peak accuracy</b> ) | 202K                        | 99.28                 |

| SHD                              |                             |                       |

| FSNN                             | 37K                         | 48.60                 |

| RSNN                             | 70K                         | 71.40                 |

| DSNN                             | 37K                         | 90.98                 |

| DMP-SNN $(I)$                    | 38K                         | 89.00                 |

| DMP-SNN (II)                     | 40K                         | 91.23                 |

| DMP-SNN ( <b>Peak accuracy</b> ) | 46K                         | 91.69                 |

| SSC                              |                             |                       |

| FSNN                             | 22K/39K                     | 26.08 / 38.50         |

| RSNN                             | 39K/72K                     | 50.90 / 60.00         |

| DSNN                             | 23K/39K                     | 60.01 / 69.40         |

| DMP-SNN $(I)$                    | 23K/40K                     | 65.09  /  69.50       |

| DMP-SNN $(II)$                   | $24\mathrm{K}/42\mathrm{K}$ | 65.37/72.90           |

| DMP-SNN ( <b>Peak accuracy</b> ) | $24\mathrm{K}/42\mathrm{K}$ | 65.37  /  72.90       |

| Chance level: 10.00 (S-MNIST     | / PS-MNIST), 5.0            | 00 (SHD), 2.90 (SSC). |

additional mapping layers. Although this approach is also effective, it substantially increases model complexity - often by up to  $3\times$  in parameters - and imposes additional residual computations that raise hardware cost [43–46]. In contrast, removing the feed-forward pathway in our model caused accuracy to drop to chance across all datasets, irrespective of memory size. This indicates that the slow memory state alone cannot sustain task performance. Instead, the explicit temporal state serves as a lightweight

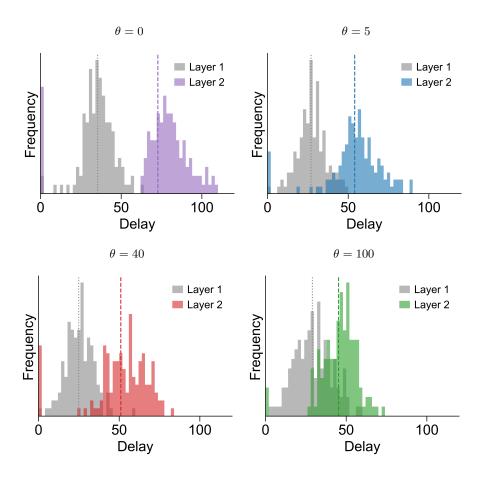

Fig. 3: Context-dependent temporal demands. a Task-dependent slow memory: increasing the memory-update interval (dilation) leaves S/PS-MNIST largely unchanged but degrades SHD/SSC, indicating that auditory streams require finergrained long-term context, whereas long-horizon vision tolerates coarser, less frequent updates. b Accuracy versus parameter budget and memory dimension saturates once task-relevant timescales are captured, indicating that capacity should be co-tuned rather than maximised. Bubble size denotes the number of feedforward neurons; colours indicate the state buffer length  $\theta$ . c Increasing the state buffer length ( $\theta$ ) in the DSNN accelerates convergence, consistent with long-range context being carried by the slow memory state. d Effect of delay distribution with longer state buffer size. As  $\theta$  grows, probability mass shifts towards shorter delays, the long-delay tail contracts, and overall dispersion decreases—indicating that a longer window partially substitutes for explicit axonal delays.

contextual modulator that reinforces stimulus-driven spiking rather than acting as a standalone recurrent mechanism. Consistent with this, model capacity on the SHD dataset improved with larger hidden width and memory dimension until task-relevant timescales were captured, beyond which gains saturated (**Figure 3b**). These results suggest that neuron count, memory size and temporal horizon should be co-tuned to

achieve balanced temporal modelling without excessive computational or hardware overhead.

We next hypothesized that the explicit state already carries long-range context, and therefore should also reduce the need for long axonal delays. Delays are known to align spikes to task-relevant timescales and to improve neuromorphic speech tasks, but long delays require deep buffers that scale with the maximum delay and specialized timing support [47, 48]. Consistent with our hypothesis, we found that combining heterogeneous axonal delays with our memory-augmented neurons improved accuracy for small memory states and, importantly, shifted the learned delays towards shorter horizons. With memory dimension d=5 and a maximum delay window  $\theta=5$ , accuracy increased by 2% despite the tight delay budget, and enlarging the delay window mainly accelerated optimization rather than being strictly required (**Figure 3c-d**). The learned axonal delay distributions are shown in **Supplementary Figure 1**.

Together, this points to a hardware-favourable hybrid solution in which the shared temporal state supplies the long-range component without per-connection buffering, while short delays provide fine timing alignment. In this regime, long programmable delays become optional rather than structural, and the network retains the benefits of delay coding, such as robustness to low-precision weights and discretisation [39], and fast motion detection [49], while easing mapping to heterogeneous neuromorphic hardware.

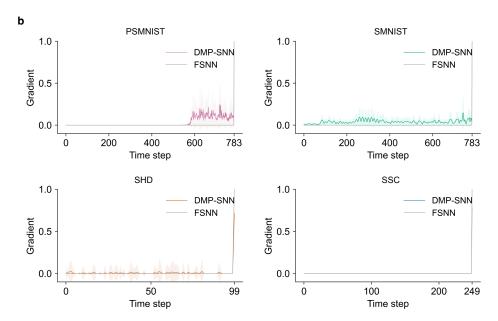

# 2.3 Dual memory networks enhance long-term credit assignment

To assess whether the proposed architecture also facilitates long-range credit assignment, we used last-timestep supervision and quantified how the loss at the final step back-propagates to the first layer over time. In this regime the network must retain task-relevant information across the entire sequence. As shown in **Supplementary Figure 2**, gradients in the first layers remained non-negligible over the full 784 steps of S-MNIST and over 200 steps of PS-MNIST, while accuracies stayed high (98.7% and 96%, respectively). On SHD the network still propagated useful signal (accuracy about 60%), whereas SSC proved more challenging, consistent with its more noisy, multiscale temporal structure [50].

A direct comparison with a purely feedforward SNN shows that once the membrane time constant is the only source of memory, gradients vanish rapidly and performance collapses, whereas the slow-memory variant continues to backpropagate through time. This supports the interpretation that adding a slow, local pathway preserves history without having to enlarge the neuron's intrinsic time constant, and that it can be used as a drop-in component to strengthen existing spiking models that already exploit heterogeneous temporal dynamics.

# 2.4 Hardware implementation of dual memory demonstrates superior throughput and energy efficiency

So far we have shown how the DMP-SNN achieves impressive algorithmic performance alongside excellent parameter number scaling on neuromorphic benchmarks.

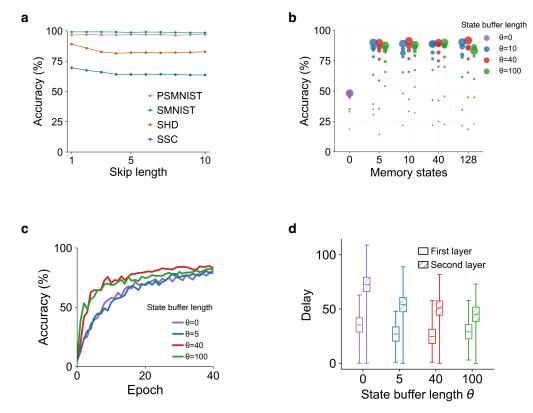

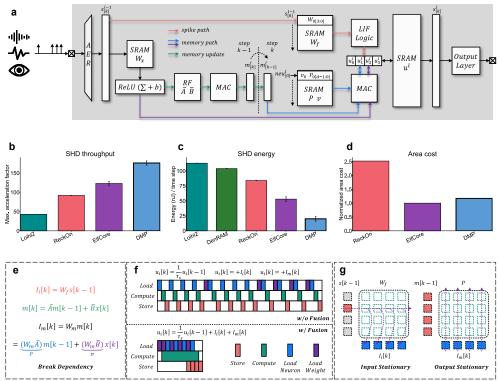

4: Hardware design for the dual memory pathway architecture. a Hardware architecture for end-to-end temporal, event-based sensory data inference. Four parallel data paths (spike integration, two memory integration paths, and memory update) are shown in distinct colours, enabled by dependency breaking. Dual register slots are allocated for m[k] (memory update) and m[k-1] (memory integration). Four additional register slots temporarily store consecutive neuron membrane potentials  $u_l$  for fused LIF operations and vector–matrix multiplications before writing back to neuron SRAM. Weight matrix access patterns differ between spike and memory integration to enhance arithmetic intensity. b DMP-SNN attains the highest throughput per sample by breaking computation dependencies. c DMP-SNN provides up to  $5\times$  higher energy efficiency compared with delay-based hardware designs. d DMP-SNN offers 2× greater area efficiency than recurrent SNN architectures, enabled by its reduced parameter-memory footprint. e Dependency breaking between slow memory update and memory integration enables parallel computation. Precomputed weight memories P and v are stored in SRAM. f Comparison of data flow with and without fine-grained operator fusion. The example illustrates updates and integrations of four postsynaptic neuron membrane potentials. Operator fusion allows single-access SRAM reads for neuron states, requiring minimal additional register area while significantly increasing arithmetic intensity. g Heterogeneous operand-stationary schemes are adopted: input-stationary (column-stationary) and output-stationary (row-stationary) access patterns are used for sparse spike integration and dense vector-matrix multiplications, respectively, further improving arithmetic intensity.

However, these do not yet realize all strengths of DMP-SNN, as it was conceived in a co-optimization process to be particularly amenable to hardware implementations. We now introduce a new hardware architecture to realize the full benefits of DMP-SNN.

Our hardware architecture is a digital near-memory-compute architecture that allows the co-optimization of dataflow corresponding to the dual memory pathways of the algorithm, instead of the default naive dataflow of existing architectures that would simply integrate the heterogeneous data flows of our algorithm. The end-toend inference micro-architecture for DMP-SNN with a single hidden layer, based on digital near-memory-compute, is depicted in **Figure 4a**. On a high level, this architecture supports four parallel computation paths and integrates postsynaptic operations through fine-grained operator fusion and heterogeneous operand stationarity. These design choices break temporal dependencies to balance latency across paths, maximize arithmetic intensity by fusing operators in hardware, and adapt dataflow to handle variable sparsity patterns, collectively minimizing off-chip memory traffic. This modular design scales naturally with task complexity, enabling flexible trade-offs between temporary storage and parallel throughput. The input stage receives task-agnostic binary spike addresses generated by neuromorphic vision or auditory sensors following the address-event representation (AER) protocol [51], while the outputs correspond either to classification or regression results, or to spike streams propagated to downstream layers. In the following we first describe the benchmarking results and the following section 2.4.1 then further details the architectural innovations that made the benchmarking results possible.

We benchmarked DMP-SNN on this co-designed hardware platform against other leading neuromorphic hardware platforms, namely Loihi2 [33], ReckOn [32], Elf-Core [52], and DenRAM [23]. Our architecture achieves more than 4× higher throughput than digital delay-based hardware like Loihi2, and over 1.9× higher throughput than recurrent architectures including ReckOn (Figure 4b). These gains arise from compact slow-memory operations and parallelisation strategies that eliminate data dependencies. Further, DMP-SNN delivers over 5× higher energy efficiency than both digital delay-based hardware (Loihi2) and analogue delay-based designs (DenRAM) (Figure 4c), primarily by eliminating the synaptic-delay buffer overhead (e.g., capacitor arrays in analogue implementations). The integration of operator fusion and heterogeneous operand stationarity yields an additional 2.5× improvement in energy efficiency over ElfCore, as confirmed in the ablation (see Method, Experimental setup). Finally, **Figure 4d** shows that DMP-SNN incurs only a minor area overhead relative to ElfCore due to intermediate accumulation buffers, yet achieves more than 2× higher area efficiency than ReckOn, owing to the removal of recurrent weight-matrix storage. Further details of the hardware validation procedure are provided in **Methods**.

Overall, the experimental results demonstrate that DMP-SNN attains high computational efficiency on conventional digital hardware, surpassing architectures fabricated on more advanced technology nodes and even designs leveraging emerging memristive devices.

### 2.4.1 Specific hardware optimizations for DMP-SNN

Our hardware architecture realizes the full efficiencies of the DMP-SNN architecture at the level of advanced data and operator handling optimizations.

Dataflow-dependency optimization. Although the compact slow memory state introduces little parameter overhead, its long integration path leads to an imbalanced data flow: the fast spike-integration path can start immediately, whereas the memory-integration path cannot. Therefore, accelerating the memory-integration path is necessary to eliminate the throughput bottleneck. Because the slow memory update is itself a linear operation, the memory integration with the postsynaptic neuron does not need to wait for the update to complete. Instead, the procedure can be divided into two fully parallel stages, as shown in **Figure 4e**. The term on the right, vx[k], still depends on the scalar x[k]. However, computing the vector–matrix product Pm[k-1] requires approximately the same amount of time as computing x[k] and then forming vx[k]. As a result, the computational balance among the critical paths is maintained. In practice, the accumulation of x[k] can be fused with the neuron update  $u_i$ , ensuring that the scalar x[k] becomes available concurrently with the binary spike vector from the upstream layer.

Operator-fusion optimization. According to the roofline model [53], operating in the compute-bound region maximizes arithmetic intensity and hence improves efficiency. In state-of-the-art end-to-end neuromorphic hardware [32, 52], a finite-state machine typically iterates over all neurons to perform leaky updates before spike integration, incurring at least two memory accesses per neuron. The DMP-SNN model introduces an additional access for the memory-integration path, further complicating efforts to maximize arithmetic intensity. The hardware implementation fuses leaky updates, spike integration, and memory integration into a single process, as illustrated in **Figure 4f**. By using temporary register slots for intermediate accumulation, the design reduces memory access to only one per neuron for the entire sequence of computations, thereby enabling operation in the compute-bound regime.

Operand-stationarity optimization. The DMP-SNN algorithm must simultaneously handle spike integration, corresponding to a sparse vector-matrix multiplication (weight accumulation), and memory integration, corresponding to a dense vector-matrix multiplication. Existing state-of-the-art hardware, such as Kraken [54], which combines sparse spike-based integration with dense ternary CNN computation, and ElfCore [52], which integrates sparse spike accumulation with dense eligibilitytrace propagation. To optimize both dataflows, DMP-SNN adopts heterogeneous operand stationarity [55]. For spike integration, we employ input stationarity to reduce weight-memory access when the input vector is sparse. For memory integration, we adopt output stationarity, minimizing neuron-memory access (only one access per neuron) when the input vector is dense. In this scheme,  $W_f$  is indexed by the nonzero entries of the spike vector, whereas P and v are indexed by postsynaptic neuron addresses. As illustrated in Figure 4g, four consecutive neuron states  $u_i$  (or more) are preloaded into register slots for intermediate accumulation. To preserve efficient sparse access for  $W_f$ , the memory pointers are incremented in a skipped manner based on these four postsynaptic neuron indices.

# 3 Discussion

Our work addresses a persistent tension: spiking models require access to long behavioral timescales, yet the mechanisms that typically provide this context - such as dense recurrence or long learnable delays - are precisely those that burden hardware [32]. These mechanisms distribute state across many connections, increase memory traffic, and demand deep buffers, causing temporal capability and implementation efficiency to diverge [25]. Here we show that this tension is not inherent and can be resolved through hardware-algorithm co-design. If temporal context is made explicit, compact, and local to each layer, then long-range processing can coexist with hardware efficiency rather than compete with it [2].

On the algorithm level, we draw on a widespread cortical motif in which fast somatic spiking is shaped by slower, local dendritic integration [30, 31]. We abstract the biologically observed fast-slow separation into an engineering design principle: a second state that is proximal to the layer but not per-synapse. Each layer maintains a low-dimensional slow state that summarises recent activity and feeds back as an additional current. Being layer-shared, the state's cost scales linearly rather than quadratically with network width; because its dynamics are well conditioned [56, 57], it offers a more stable gradient pathway than the decaying membrane. Under strict last-timestep supervision, this configuration sustained useful gradients over hundreds of steps on S-/PS-MNIST, whereas a purely feedforward SNN did not, indicating that long-term credit assignment is carried by the explicit slow state rather than by inflating neuronal time constants.

The hardware mirrors this separation. Instead of forcing sparse spike accumulation and dense linear updates through a single uniform core, we implement two coupled paths: one for spike-driven computation and one for the shared state. Keeping the state on-chip, decoupling update from consume, and adopting distinct dataflow policies for sparse and dense kernels increase arithmetic intensity without extra off-chip traffic. Post-layout results in 22 nm confirm that this mapping holds in silicon: performance matches or exceeds recurrent and delay-based baselines at lower energy and higher throughput, with only a modest area overhead from the additional state. In practice, these hardware gains arise directly from the same design principle used at the algorithmic level: isolate slow information, keep it compact, and move it through a dedicated path.

Finally, our results suggest a clear algorithm-hardware design principle for long-timescale spiking: make the slow state explicit, shared and low-rank; keep the fast path spike-driven; and execute the two in parallel on hardware. Under this formulation, long temporal horizons no longer compete with efficiency, and the biological fast-slow motif provides a high-level design pattern rather than a loose analogy. This establishes a scalable template for neuromorphic systems in which temporal competence and deployment practicality reinforce each other, rather than exist in trade-off.

## 4 Methods

### Spiking neurons

We model spiking neurons as leaky–integrate–and–fire (LIF) units. For neuron i in layer l at discrete time step k, the membrane potential is  $u_i^l[k]$ . Its dynamics are governed by the membrane decay  $\beta$  and the input current  $I_i^l[k]$ , with the discrete-time update

$$u_i^l[k] = \beta u_i^l[k-1] + I_i^l[k],$$

(1)

The input current is

$$I^{l}[k] = W_f \, s^{l-1}[k] \tag{2}$$

where  $W_f$  denotes feedforward synaptic weights and  $s^{l-1}[k]$  the presynaptic spike vector from layer l-1.

A spike is emitted when the membrane exceeds threshold:

$$s_i^l[k] = \Theta(u_i^l[k] - \theta_u), \tag{3}$$

where  $\Theta(\cdot)$  is the Heaviside step function (1 if its argument is positive and 0 otherwise), and  $\theta_u$  is the membrane threshold.

Building on this vanilla LIF neuron, we consider two variants that extend temporal capacity. **LIF with axonal delays** models transmission delays as a temporal shift of presynaptic spikes, i.e.,  $s^{l-1}[k] \to s^{l-1}[k-\bar{d}]$ . **LIF with recurrent connections** augments the update by adding an additional recurrent term within the layer.

### Slow memory pathway

We implement the slow pathway using a state-space model that captures long-term dependencies through well-conditioned linear dynamics. This design builds on the Legendre Memory Unit (LMU) framework [56, 58], which formulates a continuous-time memory as a linear time-invariant (LTI) system. The LMU combines a single-input delay network (DN) with a nonlinear dynamical system, efficiently encoding recent input history through orthogonalized basis functions derived from Legendre polynomials. The delay network projects the input onto a set of orthogonal basis functions derived from Legendre polynomials, providing an efficient representation of temporal context for subsequent nonlinear computation. The DN orthogonalizes the input signal over a sliding window of length  $\theta$  (we denote it as state buffer length), while the nonlinear system leverages this orthogonalized memory to compute various functions over time. Mathematically, given an input scalar function x(t), the state update can be described as follows:

$$m'(t) = Am(t) + Bx(t) \tag{4}$$

where  $m(t) \in \mathbb{R}^d$  denotes the memory state vector with dimension d, and A and B are state-space matrices. Following the use of Padé approximation [57, 59], the state-space matrices can be expressed as follows:

**Table 2:** Dimensions of tensors in the DMP-SNN at layer  $l.\ M$  is the presynaptic width, N the number of postsynaptic neurons, and d the memory dimension.

| Symbol         | Role                                  | Dimension                 |

|----------------|---------------------------------------|---------------------------|

| $s^{l-1}[k]$   | Presynaptic spikes                    | $\{0,1\}^{M}$             |

| $u^{l}[k]$     | Membrane potentials (postsynaptic)    | $\mathbb{R}^N$            |

| $m^{l}[k]$     | Slow memory state                     | $\mathbb{R}^d$            |

| $x^{l}[k]$     | Memory input                          | $\mathbb{R}^1$            |

| $I^{l}[k]$     | Input current                         | $\mathbb{R}^N$            |

| $I_m^{\ l}[k]$ | Memory current                        | $\mathbb{R}^N$            |

| $W_f$          | Feedforward $(s \rightarrow u)$       | $\mathbb{R}^{N \times M}$ |

| $W_m$          | Memory readout $(m \rightarrow u)$    | $\mathbb{R}^{N 	imes d}$  |

| $ar{A}$        | Memory transition (state matrix)      | $\mathbb{R}^{d \times d}$ |

| $ar{B}$        | Memory input map $(x \rightarrow m)$  | $\mathbb{R}^{d 	imes 1}$  |

| $W_x$          | Spike compression $(s \rightarrow x)$ | $\mathbb{R}^{\;1	imes M}$ |

| b              | Bias for $x$                          | $\mathbb{R}^1$            |

| $W_r$          | Recurrent $(s \rightarrow u)$         | $\mathbb{R}^{N \times N}$ |

| $ar{d}^{\;l}$  | Axonal delays (per output channel)    | $\mathbb{R}^{N}$          |

$$A = [a]_{ij} \in \mathbb{R}^{d \times d}, \quad a_{ij} = (2i+1) \begin{cases} -1 & \text{if } i < j \\ (-1)^{i-j+1} & \text{if } i \ge j \end{cases}$$

$$B = [b]_i \in \mathbb{R}^{d \times 1}, \quad b_i = (2i+1)(-1)^i, \quad i, j \in [0, d-1]$$

(5)

This continuous-time system can be converted to discrete-time k with a time resolution  $\Delta t$ :

$$m^{l}[k] = \bar{A}m^{l}[k-1] + \bar{B}x^{l}[k]$$

(6)

Here,  $\bar{A}$  and  $\bar{B}$  are the discretized versions <sup>1</sup> of A and B, which are usually frozen during training.

# Dual memory pathway for SNNs (DMP-SNN)

Each layer maintains a low-dimensional slow state  $m^l[k] \in \mathbb{R}^d$  that summarises recent activity and feeds back as an additional current. As suggested by Chilkuri et al. [60], we compress presynaptic spikes into a scalar drive:

$$x^{l}[k] = f_x(W_x s^{l-1}[k] + b) (8)$$

Where  $f_x$  is the mapping function. The shared memory is updated by

$$m^{l}[k] = \bar{A} m^{l}[k-1] + \bar{B} x^{l}[k].$$

(9)

(7)

$<sup>^1</sup>$  Using zero-order hold (ZOH) method, exact discretization gives  $\bar{A}=e^{A\Delta t}\quad\text{and}\quad \bar{B}=A^{-1}(e^{A\Delta t}-I)B.$

**Table 3:** Hyperparameter settings for different datasets.

| Parameter               | SHD | SSC       | S/PS-MNIST | Description                         |

|-------------------------|-----|-----------|------------|-------------------------------------|

| Input channels          | 140 | 140       | 1          | Number of input units               |

| Simulation Time Steps   | 100 | 250       | 784        | Simulation Time steps               |

| Output neurons          | 20  | 35        | 10         | Number of classes                   |

| Hidden Spiking Neurons  | 128 | 128       | 200        | Size of hidden layer                |

| Memory states           | 10  | 10        | 40         | Dimension of Memory states          |

| State buffer length     | 40  | 40        | 300        | Sliding window of length $(\theta)$ |

| Number of Hidden Layers | 2   | 1 and $2$ | 2          | Number of hidden layers             |

| $\theta_u$              |     | 10        |            | Spiking threshold                   |

| $rac{f_x}{ar{d}}$      |     | ReLU      |            | Non-linear function                 |

| $ar{d}$                 |     | learnable |            | Axonal delays                       |

The membrane update is

$$u^{l}[k] = \beta u^{l}[k-1] + I^{l}[k] + I^{l}_{m}[k]$$

(10)

The input current I and memory input  $I_m$  are given by:

$$I^{l}[k] = W_{f}s^{l-1}[k], (11)$$

$$I_m^l[k] = W_m m^l[k] \tag{12}$$

where  $W_m$  represents the weights from memory. This formulation couples a fast spiking pathway with a slow memory that evolves stably over long timescales. The full detailed equation is listed in Table 2. We used the network parameters given in Table 3 for all experiments, unless otherwise specified. Our method is trained via the SpikingJelly and SLAYER frameworks [61, 62] and utilizes the mean membrane potential of the last layer as the output.

#### Analysis of the gradient of DMP-SNN

We analyse temporal credit assignment under last-timestep supervision. For a hidden layer l, let  $u^l[k] \in \mathbb{R}^N$  and  $m^l[k] \in \mathbb{R}^d$  denote the membrane potentials and slow memory at discrete time k, respectively. Ignoring input-driven terms (which act as biases and do not affect state–state Jacobians), the dynamics within the layer can be written as

$$u^{l}[k+1] = \beta u^{l}[k] + W_{m} m^{l}[k+1], \tag{13}$$

$$m^{l}[k+1] = \bar{A} \, m^{l}[k],$$

(14)

with leak factor  $\beta \in (0,1)$ , memory readout matrix  $W_m \in \mathbb{R}^{N \times d}$ , and state-transition matrix  $\bar{A} \in \mathbb{R}^{d \times d}$  arising from the state space construction.

It is convenient to group membrane and memory into a joint state

$$z^{l}[k] = \begin{bmatrix} u^{l}[k] \\ m^{l}[k] \end{bmatrix} \in \mathbb{R}^{N+d}.$$

Equations (13)–(14) define a linear time-invariant update

$$z^l[k+1] = F \, z^l[k], \qquad F = \begin{bmatrix} \beta I_N & W_m \bar{A} \\ 0 & \bar{A} \end{bmatrix},$$

where  $I_N$  denotes the  $N \times N$  identity matrix. Over a temporal horizon from k to T, the same-layer Jacobian is therefore

$$\frac{\partial z^{l}[T]}{\partial z^{l}[k]} = F^{T-k}. (15)$$

Because F is block upper-triangular, its eigenvalues are

$$\operatorname{spec}(F) = \{\beta \text{ (multiplicity } N)\} \cup \operatorname{spec}(\bar{A}),$$

where spec( $\bar{A}$ ) = { $\lambda_i(\bar{A})$ } denotes the spectrum of  $\bar{A}$  and  $\lambda_i(\bar{A})$  is the *i*-th eigenvalue of  $\bar{A}$ . The eigenvalue  $\beta$  arises from the membrane block  $\beta I_N$  and the remaining eigenvalues arise from the memory block  $\bar{A}$ . For a purely feedforward SNN (FSNN), the state reduces to the membrane only,  $z^l[k] = u^l[k]$ , and  $F = \beta I_N$ , so that

$$\frac{\partial u^l[T]}{\partial u^l[k]} = \beta^{T-k} I_N,$$

and all gradient components decay at rate  $|\beta|^{T-k}$ . In the DMP-SNN, the modes associated with the membrane block still decay at this fast rate, but the memory block  $\bar{A}$  contributes additional modes whose decay is governed by  $|\lambda_i(\bar{A})|^{T-k}$ . Because the slow memory feeds back into the membrane via the term  $W_m m^l[k]$  in Eq. (13), these memory modes are continuously injected into the membrane dynamics and appear as slow components in  $u^l[T]$ . By construction, the spectral radius  $\rho(\bar{A})$  is close to one [56], so these memory-aligned modes carry gradients over substantially longer horizons.

Intuitively, the DMP-SNN therefore provides two distinct temporal scales for credit assignment: a fast mode, inherited from the leaky membrane, and a slow mode, inherited from the well-conditioned memory dynamics. Empirically, this leads to a broad temporal tail in the gradient profile over k for the DMP-SNN, whereas the FSNN exhibits a sharp peak near k = T and rapid decay towards earlier time steps (Supplementary Figure 2).

### Dilated slow memory

Dilated slow memory updates the memory-driven input only every fixed number of time steps, thereby skipping intermediate computations on hardware. The memory-driven input to neuron n at time step k is

$$I_m^l[k] = W_m m^{(l)}[k_d], \quad k_d = \lfloor k/d_s \rfloor d_s$$

(16)

where  $d_s$  is the skip length (dilation factor),  $m^l[k_d]$  denotes the memory vector subsampled every  $d_s$  steps (i.e.,  $[m[0], m[d_s], m[2d_s], \ldots, m(\lfloor k/d_s \rfloor d_s)]^{\top}$ ). Between updates (when  $k \mod d_s \neq 0$ ), the membrane potential evolves without the memory injection.

#### Hardware baselines

SOTA hardware implementations of efficient long-term memory for temporal signal processing include:

Loihi2 [33]: An end-to-end framework that enables event-based SNN training with synaptic delays on GPUs and deployment on Intel's Loihi2 neuromorphic chip. It represents the state-of-the-art in digital hardware implementations featuring synaptic delays.

DenRAM [23]: An analog feed-forward SNN with dendritic compartments integrated with resistive RAM (RRAM) in 130 nm technology, supporting both synaptic delays and weights. It represents the state-of-the-art analog hardware approach using memristor-based delayed synapses.

ReckOn [32]: A spiking RNN processor that supports task-agnostic online learning over multi-second timescales. It represents the state-of-the-art in digital spiking RNN implementations.

ElfCore [52]: A feed-forward SNN processor equipped with a local self-supervised learning engine for multilayer temporal learning without labeled inputs. It represents the state-of-the-art in digital hardware integrating both sparse spike and dense trace data paths.

#### Experimental setup

The DMP-SNN architecture was implemented in an advanced 22FDX technology node, and evaluated through post-layout simulations using QuestaSim and Innovus. For the ablation study, we also developed a modified ElfCore-based architecture designed for heterogeneous dataflow acceleration but lacking operator fusion and heterogeneous operand stationarity [52].

Performance results for both architectures were averaged over inference runs on 10 samples from the SHD dataset. Reference comparison points include Loihi2, DenRAM with memristor-based synaptic delay, and ReckOn. All reference metrics were obtained from their respective publications and normalized for technology node and operating voltage under comparable SHD accuracy.

The comparison metrics include the maximum acceleration factor, which denotes how much faster the computing core can process a single time step relative to real time (1 ms for the SHD dataset). The energy per time step quantifies the average energy consumed to process one inference sample.

# 5 Data availability

The spiking data used in this study are publicly available and open source. The dataset for SHD and SSC belong to Spiking Heidelberg Datasets, which can be accessed via <a href="https://zenkelab.org/datasets/">https://zenkelab.org/datasets/</a>. The S-MNIST and PS-MNIST are derived from the original MNIST dataset (<a href="http://yann.lecun.com/exdb/mnist/">https://yann.lecun.com/exdb/mnist/</a>).

# 6 Code availability

The source code for the algorithm and hardware implementation code will be made publicly accessible after review.

Acknowledgements. This project was funded by the Advanced Research + Invention Agency (ARIA), was partially supported by the HORIZON EUROPE EIC Pathfinder Grant ELEGANCE (Grant No. 101161114), and has received funding from Swiss National Science Foundation (SNSF 200021E\_222393). D.A. is funded by an Imperial College Research Fellowship, Schmidt Sciences Fellowship and Templeton World Charity Foundation, Inc (funder DOI 501100011730) under the grant TWCF-2022-30510. J.A. is funded by a Career Development Research Fellowship of St John's College, Oxford. For the purpose of open access, the authors have applied a Creative Commons Attribution (CC BY) license to the text, figures and code relating to this paper.

**Declarations.** The authors declare no competing interests.

### References

- [1] Maass, W.: Networks of spiking neurons: the third generation of neural network models. Neural networks **10**(9), 1659–1671 (1997)

- [2] Roy, K., Jaiswal, A., Panda, P.: Towards spike-based machine intelligence with neuromorphic computing. Nature **575**(7784), 607–617 (2019)

- [3] Gerstner, W., Kistler, W.M.: Spiking neuron models. Spiking neuron models: Single neurons, populations, plasticity, 157 (2002)

- [4] Li, G., Deng, L., Tang, H., Pan, G., Tian, Y., Roy, K., Maass, W.: Brain-inspired computing: A systematic survey and future trends. Proceedings of the IEEE (2024)

- [5] Yu, Z., Sun, P., Goodman, D.F.: Beyond rate coding: Surrogate gradients enable spike timing learning in spiking neural networks. arXiv preprint arXiv:2507.16043 (2025)

- [6] Mostafa, H.: Supervised learning based on temporal coding in spiking neural networks. IEEE transactions on neural networks and learning systems 29(7), 3227–3235 (2017)

- [7] Comşa, I.-M., Potempa, K., Versari, L., Fischbacher, T., Gesmundo, A., Alakuijala, J.: Temporal coding in spiking neural networks with alpha synaptic function: learning with backpropagation. IEEE transactions on neural networks and learning systems **33**(10), 5939–5952 (2021)

- [8] Sun, P., Wu, J., Zhang, M., Devos, P., Botteldooren, D.: Delay learning based on temporal coding in spiking neural networks. Neural Networks 180, 106678 (2024)

- [9] Gast, R., Solla, S.A., Kennedy, A.: Neural heterogeneity controls computations in spiking neural networks. Proceedings of the National Academy of Sciences 121(3), 2311885121 (2024)

- [10] Fang, W., Yu, Z., Chen, Y., Masquelier, T., Huang, T., Tian, Y.: Incorporating learnable membrane time constant to enhance learning of spiking neural networks. In: Proceedings of the IEEE/CVF International Conference on Computer Vision, pp. 2661–2671 (2021)

- [11] Perez-Nieves, N., Leung, V.C., Dragotti, P.L., Goodman, D.F.: Neural heterogeneity promotes robust learning. Nature communications **12**(1), 5791 (2021)

- [12] Shaban, A., Bezugam, S.S., Suri, M.: An adaptive threshold neuron for recurrent spiking neural networks with nanodevice hardware implementation. Nature Communications 12(1), 4234 (2021)

- [13] Yin, B., Corradi, F., Bohté, S.M.: Accurate and efficient time-domain classification with adaptive spiking recurrent neural networks. Nature Machine Intelligence **3**(10), 905–913 (2021)

- [14] Bellec, G., Salaj, D., Subramoney, A., Legenstein, R., Maass, W.: Long short-term memory and learning-to-learn in networks of spiking neurons. Advances in neural information processing systems **31** (2018)

- [15] Sreenivasan, K.K., D'Esposito, M.: The what, where and how of delay activity. Nature reviews neuroscience 20(8), 466–481 (2019)

- [16] Izhikevich, E.M.: Polychronization: computation with spikes. Neural computation **18**(2), 245–282 (2006)

- [17] Sun, P., Chua, Y., Devos, P., Botteldooren, D.: Learnable axonal delay in spiking neural networks improves spoken word recognition. Frontiers in Neuroscience 17, 1275944 (2023)

- [18] Wang, X., Lin, X., Dang, X.: A delay learning algorithm based on spike train

- kernels for spiking neurons. Frontiers in neuroscience 13, 252 (2019)

- [19] Yu, Q., Gao, J., Wei, J., Li, J., Tan, K.C., Huang, T.: Improving multispike learning with plastic synaptic delays. IEEE Transactions on Neural Networks and Learning Systems **34**(12), 10254–10265 (2022)

- [20] Grappolini, E., Subramoney, A.: Beyond weights: deep learning in spiking neural networks with pure synaptic-delay training. In: Proceedings of the 2023 International Conference on Neuromorphic Systems, pp. 1–4 (2023)

- [21] Hammouamri, I., Hassani, I.K., Masquelier, T.: Learning delays in spiking neural networks using dilated convolutions with learnable spacings. In: ICLR (2024)

- [22] Patiño-Saucedo, A., Yousefzadeh, A., Tang, G., Corradi, F., Linares-Barranco, B., Sifalakis, M.: Empirical study on the efficiency of spiking neural networks with axonal delays, and algorithm-hardware benchmarking. In: 2023 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5 (2023). https://doi.org/10.1109/ISCAS46773.2023.10181778

- [23] D'agostino, S., Moro, F., Torchet, T., Demirağ, Y., Grenouillet, L., Castellani, N., Indiveri, G., Vianello, E., Payvand, M.: Denram: neuromorphic dendritic architecture with rram for efficient temporal processing with delays. Nature communications 15(1), 3446 (2024)

- [24] Zheng, H., Zheng, Z., Hu, R., Xiao, B., Wu, Y., Yu, F., Liu, X., Li, G., Deng, L.: Temporal dendritic heterogeneity incorporated with spiking neural networks for learning multi-timescale dynamics. Nature Communications 15(1), 277 (2024)

- [25] Patino-Saucedo, A., Meijer, R., Yousefzadeh, A., Gomony, M.-D., Corradi, F., Detteter, P., Garrido-Regife, L., Linares-Barranco, B., Sifalakis, M.: Hardwareaware training of models with synaptic delays for digital event-driven neuromorphic processors. arXiv preprint arXiv:2404.10597 (2024)

- [26] Wu, Y., Zhao, R., Zhu, J., Chen, F., Xu, M., Li, G., Song, S., Deng, L., Wang, G., Zheng, H., et al.: Brain-inspired global-local learning incorporated with neuromorphic computing. Nature Communications 13(1), 65 (2022)

- [27] Zheng, Z., Wei, J., Xu, Y., Li, C., Lu, T., Guo, Q., Ji, X., Guo, H., Wang, G., Deng, L.: Modeling macroscopic brain dynamics with brain-inspired computing architecture. Nature Communications 16(1), 9424 (2025)

- [28] London, M., Häusser, M.: Dendritic computation. Annu. Rev. Neurosci.  $\mathbf{28}(1)$ , 503-532 (2005)

- [29] Murray, J.D., Bernacchia, A., Freedman, D.J., Romo, R., Wallis, J.D., Cai, X., Padoa-Schioppa, C., Pasternak, T., Seo, H., Lee, D., et al.: A hierarchy of intrinsic timescales across primate cortex. Nature neuroscience 17(12), 1661–1663 (2014)

- [30] Sartzetaki, C., Zonneveld, A.W., Oyarzo, P., Gifford, A.T., Cichy, R.M., Mettes, P., Groen, I.I.: The human brain as a dynamic mixture of expert models in video understanding. bioRxiv, 2025–10 (2025)

- [31] Cook, J., Akarca, D., Costa, R.P., Achterberg, J.: Brain-like processing pathways form in models with heterogeneous experts. In: The Thirty-ninth Annual Conference on Neural Information Processing Systems (2025). https://openreview.net/forum?id=Qm6ah1hpFA

- [32] Frenkel, C., Indiveri, G.: Reckon: A 28nm sub-mm2 task-agnostic spiking recurrent neural network processor enabling on-chip learning over second-long timescales. In: 2022 IEEE International Solid-State Circuits Conference (ISSCC), vol. 65, pp. 1–3 (2022). https://doi.org/10.1109/ISSCC42614.2022.9731734

- [33] Mészáros, B., Knight, J.C., Timcheck, J., Nowotny, T.: A Complete Pipeline for deploying SNNs with Synaptic Delays on Loihi 2 (2025). https://arxiv.org/abs/ 2510.13757

- [34] Cramer, B., Stradmann, Y., Schemmel, J., Zenke, F.: The heidelberg spiking data sets for the systematic evaluation of spiking neural networks. IEEE Transactions on Neural Networks and Learning Systems (2020)

- [35] Yao, X., Li, F., Mo, Z., Cheng, J.: Glif: A unified gated leaky integrate-and-fire neuron for spiking neural networks. Advances in Neural Information Processing Systems **35**, 32160–32171 (2022)

- [36] Pagkalos, M., Chavlis, S., Poirazi, P.: Introducing the dendrify framework for incorporating dendrites to spiking neural networks. Nature Communications 14(1), 131 (2023)

- [37] Zhang, S., Yang, Q., Ma, C., Wu, J., Li, H., Tan, K.C.: Tc-lif: A two-compartment spiking neuron model for long-term sequential modelling. In: Proceedings of the AAAI Conference on Artificial Intelligence, vol. 38, pp. 16838–16847 (2024)

- [38] Yan, Y., Yang, Q., Wu, Y., Liu, H., Zhang, M., Li, H., Tan, K.C., Wu, J.: Efficient and robust temporal processing with neural oscillations modulated spiking neural networks. Nature communications **16**(1), 8651 (2025)

- [39] Sun, P., Achterberg, J., Su, Z., Goodman, D.F.M., Akarca, D.: Exploiting heterogeneous delays for efficient computation in low-bit neural networks (2025). https://arxiv.org/abs/2510.27434

- [40] LeCun, Y., Bottou, L., Bengio, Y., Haffner, P.: Gradient-based learning applied to document recognition. Proceedings of the IEEE 86(11), 2278–2324 (2002)

- [41] Sun, P., Wu, J., Zhang, M., Devos, P., Botteldooren, D.: Delayed memory unit: modeling temporal dependency through delay gate. IEEE transactions on neural

- networks and learning systems (2024)

- [42] Fan, L., Shen, H., Lian, X., Li, Y., Yao, M., Li, G., Hu, D.: A multisynaptic spiking neuron for simultaneously encoding spatiotemporal dynamics. Nature Communications **16**(1), 7155 (2025)

- [43] Du, Y., Liu, X., Chua, Y.: Spiking structured state space model for monaural speech enhancement. In: ICASSP 2024 - 2024 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), pp. 766–770 (2024). https://doi.org/10.1109/ICASSP48485.2024.10448152

- [44] Liu, Z., Datta, G., Li, A., Beerel, P.A.: Lmuformer: Low complexity yet powerful spiking model with legendre memory units. In: The Twelfth International Conference on Learning Representations

- [45] Stan, M.-I., Rhodes, O.: Learning long sequences in spiking neural networks. Scientific Reports 14(1), 21957 (2024)

- [46] Sun, P., Jiang, W., Devos, P., Botteldooren, D.: Parallel delayed memory units for enhanced temporal modeling in biomedical and bioacoustic signal analysis. IEEE Transactions on Audio, Speech and Language Processing 33, 4797–4807 (2025) https://doi.org/10.1109/TASLPRO.2025.3633044

- [47] Hammouamri, I., Khalfaoui-Hassani, I., Masquelier, T.: Learning delays in spiking neural networks using dilated convolutions with learnable spacings. arXiv preprint arXiv:2306.17670 (2023)

- [48] Sun, P., Wu, J., Devos, P., Botteldooren, D.: Towards parameter-free attentional spiking neural networks. Neural Networks 185, 107154 (2025)

- [49] Grimaldi, A., Perrinet, L.U.: Learning heterogeneous delays in a layer of spiking neurons for fast motion detection. Biological Cybernetics 117(4), 373–387 (2023)

- [50] AlKilany, A., Goodman, D.F.: Neuromodulation enhances dynamic sensory processing in spiking neural network models. bioRxiv, 2025–07 (2025)

- [51] Su, Z., Ramini, S., Coffen Marcolin, D., Veronesi, A., Krstic, M., Indiveri, G., Bertozzi, D., Nowick, S.M.: An ultra-low cost and multicast-enabled asynchronous noc for neuromorphic edge computing. IEEE Journal on Emerging and Selected Topics in Circuits and Systems 14(3), 409–424 (2024) https://doi.org/10.1109/ JETCAS.2024.3433427

- [52] Su, Z., Indiveri, G.: Elfcore: A 28nm neural processor enabling dynamic structured sparse training and online self-supervised learning with activity-dependent weight update. In: 2025 IEEE European Solid-State Electronics Research Conference (ESSERC), pp. 13–16 (2025). https://doi.org/10.1109/ESSERC66193.2025. 11214101

- [53] Verhelst, M., Benini, L., Verma, N.: How to keep pushing ml accelerator performance? know your rooflines! IEEE Journal of Solid-State Circuits 60(6), 1888–1905 (2025) https://doi.org/10.1109/JSSC.2025.3553765

- [54] Potocnik, V., Di Mauro, A., Lamberti, L., Kartsch, V., Scherer, M., Conti, F., Benini, L.: Circuits and systems for embodied ai: Exploring uj multi-modal perception for nano-uavs on the kraken shield. In: 2024 IEEE European Solid-State Electronics Research Conference (ESSERC), pp. 1–4 (2024). https://doi.org/10. 1109/ESSERC62670.2024.10719476

- [55] Kwon, H., Chatarasi, P., Pellauer, M., Parashar, A., Sarkar, V., Krishna, T.: Understanding reuse, performance, and hardware cost of dnn dataflow: A datacentric approach. In: Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture, pp. 754–768 (2019)

- [56] Voelker, A., Kajić, I., Eliasmith, C.: Legendre memory units: Continuous-time representation in recurrent neural networks. Advances in neural information processing systems **32** (2019)

- [57] Gu, A., Dao, T., Ermon, S., Rudra, A., Ré, C.: Hippo: Recurrent memory with optimal polynomial projections. Advances in neural information processing systems **33**, 1474–1487 (2020)

- [58] Gu, A., Goel, K., Re, C.: Efficiently modeling long sequences with structured state spaces. In: International Conference on Learning Representations

- [59] Padé, H.: Sur la représentation approchée d'une fonction par des fractions rationnelles. In: Annales Scientifiques de l'Ecole Normale Supérieure, vol. 9, pp. 3–93 (1892)

- [60] Chilkuri, N.R., Eliasmith, C.: Parallelizing legendre memory unit training. In: International Conference on Machine Learning, pp. 1898–1907 (2021). PMLR

- [61] Fang, W., Chen, Y., Ding, J., Yu, Z., Masquelier, T., Chen, D., Huang, L., Zhou, H., Li, G., Tian, Y.: Spikingjelly: An open-source machine learning infrastructure platform for spike-based intelligence. Science Advances 9(40), 1480 (2023)

- [62] Shrestha, S.B., Orchard, G.: Slayer: Spike layer error reassignment in time. Advances in neural information processing systems **31** (2018)

# **Supplementary Information**

# Supplementary Figures

Supplementary Figure 1: Effect of longer state buffer length on axonal delay distributions

A longer state buffer length  $(\theta)$  partially absorbs the temporal span that would otherwise be handled by longer axonal delays. The panels show the learned delay distributions as  $\theta$  increases while all other settings are held the same. As  $\theta$  grows, the probability mass shifts toward shorter delays.

# Supplementary Figure 2: Vanilla spiking neurons struggle with long-term credit assignment

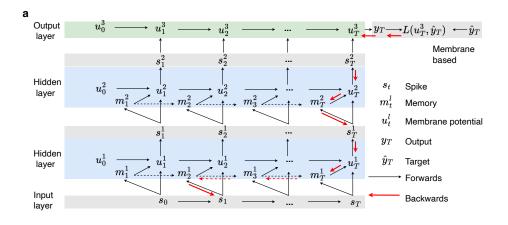

To clearly assess long-range credit assignment, we adapt the strictly last-timestep supervision. We examined how gradients propagate through time in the dual-memory pathway spiking network (DMP-SNN) and feedforward SNN (FSNN). **a**, Computational graph unrolled through time for a spiking neuron during backpropagation through time (BPTT). Red arrows denote the slow gradient pathway visualised in **b**.

$\mathbf{b}$ , Normalised gradient magnitude traced from the terminal loss back to the first hidden layer for PS-MNIST, S-MNIST, SHD, and SSC. Solid lines show the mean and shaded regions indicate the s.e.m. across a random batch (batch size = 256). Under this strict supervision regime, the DMP-SNN maintains a broad temporal tail, reflecting stable long-range credit assignment through its slow memory pathway, whereas the feedforward baseline decays rapidly, relying solely on fast membrane dynamics.