# BitStopper: An Efficient Transformer Attention Accelerator via Stage-fusion and Early Termination

Huizheng Wang

School of Integrated Circuits

Tsinghua University

Beijing, China

wanghz22@mails.tsinghua.edu.cn

Hongbin Wang

School of Integrated Circuits

Tsinghua University

Beijing, China

wanghb24@mails.tsinghua.edu.cn

Shaojun Wei

School of Integrated Circuits

Tsinghua University

Beijing, China

wsj@tsinghua.edu.cn

Yang Hu

School of Integrated Circuits

Tsinghua University

Beijing, China

hu\_yang@tsinghua.edu.cn

Shouyi Yin

School of Integrated Circuits

Tsinghua University

Beijing, China

Shanghai Artificial Intelligence Laboratory

Shanghai, China

yinsy@tsinghua.edu.cn

Abstract—Attention-based large language models (LLMs) have transformed modern AI applications, but the quadratic cost of self-attention imposes significant compute and memory overhead. Dynamic sparsity (DS) attention mitigates this, yet its hardware efficiency is limited by the added prediction stage and the heavy memory traffic it entails. To address these limitations, this paper proposes BitStopper, a fine-grained algorithm-architecture codesign that operates without a sparsity predictor. First, a bitserial enable stage fusion (BESF) mechanism is proposed to reuse and minimize the memory access by progressively terminating trivial tokens and merging the prediction stage into the execution stage. Second, a lightweight and adaptive token selection (LATS) strategy is developed to work in concert with the bit-level sparsity speculation. Third, a bit-level asynchronous processing (BAP) strategy is employed to improve compute utilization during the on-demand bit-grained memory fetching. Finally, an elaborate architecture is designed to translate the theoretical complexity reduction into practical performance improvement. Extensive evaluations demonstrate that, compared to state-of-theart (SOTA) Transformer accelerators, BitStopper achieves 2.03× and 1.89× speedups over Sanger and SOFA, respectively, while delivering  $2.4 \times$  and  $2.1 \times$  improvements in energy efficiency.

Index Terms—LLM, attention sparsity, stage fusion, bit-grained processing, asynchronous processing.

#### I. INTRODUCTION

Large language models (LLMs) now underpin a wide range of applications, from automated content generation [1], [2] to conversational assistants [3], [4]. With the rapid advances of GPT-series models [5]–[7], improving the inference efficiency of LLMs has become a current research priority.

LLMs derive much of their effectiveness from the self-attention mechanism [8], which captures global dependencies throughout the entire sequence. In each self-attention module, the Query (Q), Key (K), and Value (V) matrices serve to encode the pairwise dependencies between tokens. Despite its strong modeling capabilities, the attention mechanism remains

Corresponding authors: Yang Hu (hu\_yang@tsinghua.edu.cn)

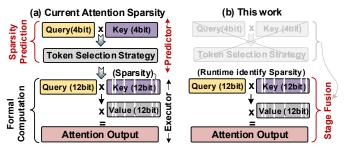

Fig. 1. Workflow comparison of (a) traditional DS works and (b) this work, where runtime identifies sparsity directly during *formal computation* without an extra sparsity predictor.

computationally inefficient: its quadratic scaling with sequence length and the predominance of low-intensity element-wise operations impose substantial overhead. As a result, the attention has been widely demonstrated as the principal bottleneck to efficient LLM inference [9]–[13].

To mitigate the inefficiencies inherent in attention, *dynamic sparsity (DS) attention* [14]–[25] has emerged as a widely adopted approach. As shown in Fig. 1 (a), the DS generally incorporates an initial *prediction stage* in which a low-bitwidth predictor approximates the attention matrix to identify and eliminate low-correlation Q-K pairs. Afterward, the remaining Q-K pairs are processed by an executor operating at higher precision, which we refer to as *formal computation stage*.

However, upon revisiting current DS approaches, we observe that they largely target two issues: 1) Reducing the prediction workload; 2) Streamlining the identification of essential tokens. For example, methods such as Energon [16], FACT [18], ELSA [15] and SOFA [19] aim to lower prediction cost through schemes such as iterative score refinement, log-domain shifting, binary hashing and distributed sorting. In parallel, designs like DOTA [17], Sanger [20] and LeOPArd [21] simplify the identification of influential tokens by relying on fixed, empirically derived or heuristic threshold values.

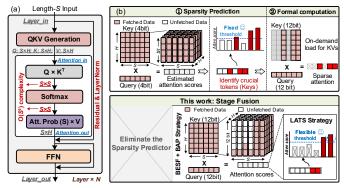

Fig. 2. (a) Architecture of Transformer-based LLMs. (b) The workflow of the current DS works. (c) Illustration of the BitStopper, featuring stage-fusion.

Unfortunately, our analysis shows that the additional sparsity predictor is what largely offsets the advantages of DS, an issue overlooked in prior works. For instance, although SOFA [19] successfully mitigates the computation overhead via logarithmic-domain processing, it nevertheless must fetch the entire set of Key vectors, causing the prediction stage to dominate the total power consumption by exceeding 75%. Although TokenPicker [26] and SpAtten [22] attempt to address the prediction-stage I/O burden by employing progressive quantization, their relatively coarse segmentation granularity limits the achievable benefits. Likewise, SpARC [27] and CLAT [28] partially mitigate this burden via offline clustering, yet the substantial calibration overhead limits their practical deployment. Overall, current DS approaches remain constrained by an external sparsity predictor whose heavy memory-access demands fundamentally restrict efficiency.

**Our insights**: The root cause of the unjustifiable prediction cost stems from the severe decoupling between the sparsity predictor and the attention executor. This separation prevents the computational and memory access efforts expended in the predictor from being leveraged by the subsequent executor.

Inspired by bit-serial computing [29]–[32], we propose a bit-serial enabled stage fusion (BESF) strategy to eliminate the extra sparsity predictor. The idea is to interleave prediction with execution and reduce memory traffic by incrementally processing Key vectors at the bit-plane level. Specifically, BESF begins with the most significant bit of each Key vector to estimate  $\mathbf{Q} \times \mathbf{K}^T$  correlations. Once a token (i.e., a vector of Key) is judged unimportant, the system immediately halts further bit-plane loading for that token. As a result, the executor only completes the remaining computation for the surviving Q-K pairs and produces the final output by accumulating their partial results.

Despite its promise, designing a BESF-style DS accelerator is far from trivial. It faces two key challenges: 1) The absence of adaptive and accurate token selection policies suited to bit-granular scores. 2) On-demand and fine-grained processing exposes memory-access latency frequently, which may degrade hardware utilization.

To address the above challenges, this paper introduces BitStopper, a novel software-hardware co-design to accelerate attention at the bit granularity. Our contributions includes:

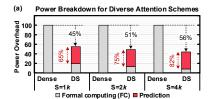

Fig. 3. (a) Comparison of power distribution between dense attention and DS attention on TSMC 28 nm. (b) Accuracy of various token-selection strategies.

- 1) Bit-serial enabled Stage Fusion (BESF) Strategy to eliminate the need for an additional prediction stage. Leveraging the bit-serial computing, we dedicate the BESF strategy, which seamlessly fuses the prediction stage into the formal computation stage, removing the prediction overhead.

- 2) Lightweight Adaptive Token Selection (LATS) strategy for bit-grained speculation while ensuring pruning accuracy. We first introduce the *bit-level uncertainty margin*, which enables the assessment of inner product fluctuation ranges. Leveraging this, the LATS is designed to identify trivial tokens in an adaptive, progressive, bit-grained manner.

- 3) Bit-level asynchronous processing (BAP) to enhance hardware utilization. To address resource underutilization from fine-grained bit-level computation, we propose an efficient asynchronous execution scheme that breaks the strict sequential dependency of traditional bit-serial processing, effectively hiding the DRAM access latency.

- 4) Custom accelerator design for practical acceleration. To translate the theoretical improvement into practical performance gains, we design a customized accelerator, BitStopper, to support these proposed strategies. BitStopper achieves  $2.4\times$  and  $2.1\times$  improvements in energy efficiency over state-of-theart (SOTA) DS accelerators, Sanger and SOFA, respectively.

#### II. BACKGROUND AND MOTIVATION

#### A. Transformer Architecture

Fig. 2 (a) presents the standard Transformer structure, composed of three stages: QKV generation, self-attention and feed-forward network (FFN). First, a length-S sequence embedded and projected into the Query (Q), Key (K), Value (V) spaces. The self-attention mechanism then computes contextual dependencies through the operation in Eq. (1). The resulting attention outputs are subsequently processed by an FFN with two fully connected layers to produce the final representation.

$$\mathbf{O} = \operatorname{softmax}\left(\mathbf{A}/\sqrt{d_{\mathrm{h}}}\right) \times \mathbf{V}, \text{ where } \mathbf{A} = \mathbf{Q}\mathbf{K}^{T}.$$

(1)

# B. Dynamic Sparsity in Self-Attention

Although self-attention allows a model to examine interactions across all tokens in a sequence, only a subset of these interactions carries meaningful contextual information [26], [33]–[36]. Common function words, for example "a" or "the", often contribute negligibly to contextual reasoning and consequently receive extremely small softmax weights in Eq. (1). This imbalance in token significance has motivated a line of DS work that attempts to exploit attention sparsity at runtime. As shown in Fig. 2(b), DS works typically follow a two-step workflow. During the *sparsity prediction stage*, a

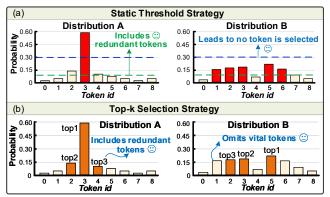

Fig. 4. Fundamental limitations of current token selection strategies.

low-precision approximation of  $\mathbf{Q}\mathbf{K}^T$  (e.g., 4-bit) is computed to identify informative Q-K pairs via top-k ranking or thresholding. During the subsequent *formal computation stage*, the final attention computation is carried out at higher precision (e.g., 12-bit) on only the retained Q-K pairs.

#### C. Motivation

However, upon re-examining existing DS methods, we identify two significant limitations:

- 1) Prohibitive Sparsity Prediction Overhead: As revealed by Fig. 3 (a), while DS lowers the overall power usage by exploiting token sparsity relative to dense attention, the cost incurred by its sparsity-prediction stage ultimately emerges as the primary source of total power consumption. For a 2k-length input, the prediction stage, which performs the approximate evaluation of  $\mathbf{Q}\mathbf{K}^T$  and identifies important tokens, draws nearly  $3\times$  more power than the formal computation stage. This excessive cost largely stems from the need to access and process the entire Key matrix (size  $S\times H$ ). Moreover, this burden remains irreducible by sparsity, as the Key tensor must be fully accessed. When the sequence length increases to 4k, the power ratio of prediction escalates to a staggering  $4.7\times$ .

- 2) Inflexible Token Selection Strategies: Fig. 4 illustrates the inflexibility of current token selection strategies using two different attention distributions. For the predefined threshold comparison in Fig. 4 (a), a high threshold (blue line) effectively identifies the critical token (token 3) in Distribution A (Dist A) but fails to select any vital tokens in Dist B. In contrast, a lower threshold (green) captures vital tokens in Dist B, but also retains irrelevant tokens (i.e., 2, 4) in Dist A. Additionally, Fig. 4 (b) depicts the limitations of current topk selection. For example, with top-3 selection, unnecessary tokens (i.e., 2, 4) are retained in Dist A, whereas important tokens in Dist B, such as tokens 1 and 6, are mistakenly filtered out. Further, Fig. 3 (b) depicts how the accuracy of both approaches declines as the number of Qs increases. It is evident that both strategies suffer from evident accuracy loss due to their static nature, which fails to adapt to the diverse distribution of attention scores ( $\mathbf{Q}_i \mathbf{K}^T$ ) across different Qs.

# III. ALGORITHM OPTIMIZATIONS OF BITSTOPPER

To address the issues of high prediction overhead and rigid token-selection behavior, we propose three key techniques.

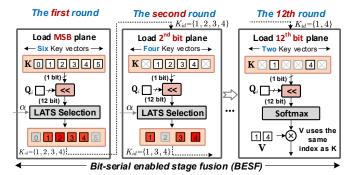

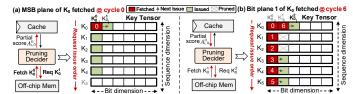

Fig. 5. Illustration of the bit-serial enabled stage fusion (BESF) mechanism.

First, the BESF mechanism fuses the prediction stage into execution stage to eliminate redundant computation and reduce memory traffic. Second, the lightweight and adaptive LATS scheme enhances the identification of critical tokens across diverse distributions. Finally, the BAP strategy improves the hardware efficiency of bit-grained processing.

### A. Bit-Serial Enabled Stage Fusion (BESF) Mechanism

The BESF builds on the observation that attention scores often exhibit large disparities, meaning that weak QK interactions can be dismissed using only a small portion of the bit information. This allows high-precision processing to be reserved exclusively for genuinely influential Q-K pairs.

Leveraging this property, BESF performs bit-incremental pruning: it derives coarse attention estimates from high-order bit planes and progressively refines the candidate set as lower-order bits are revealed. This incremental narrowing enables early termination of redundant IO and computation cost. Meanwhile, the partial results produced in low-bit prediction can be reused during the formal computation stage, thereby eliminating the standalone prediction overhead.

Fig. 5 outlines the overall procedure. 1) For each query  $\mathbf{Q}_i$  (with 12-bit quantization), BESF begins by computing approximate dot-product scores using only the MSB of the Keys. Keys (e.g.,  $\{1,2,3,4\}$ ) whose potential max scores exceed an initial threshold are retained for further distingish. Subsequent rounds evaluate additional bit planes, repeatedly filtering the retained set based on the updated partial scores. In the illustrated example, the retained set  $\{1,2,3,4\}$  is tightened to  $\{1,3,4\}$  and eventually to surviving Keys  $\{1,4\}$  after multiple refinement rounds. Once the sparse  $\mathbf{S}$  is generated, full-precision  $\mathbf{S} \times \mathbf{V}$  computation (12-bit) is performed using the Vs corresponding to the indices of the selected final Keys.

# B. Lightweight Adaptive Token Selection (LATS) Strategy

However, it remains difficult to pinpoint potentially important Keys at each bit round in a lightweight manner that can still adapt to the shifting distribution of attention scores.

To this end, we propose the LATS strategy. We begin by analyzing the mathematical behavior of the softmax function and show that it naturally supports lightweight max-oriented decision processes. Consider a two-element vector  $[a_0, a_1]$  passed through the softmax, where  $a_1$  is the larger value and can be expressed as  $a_1 = a_0 + \delta$ . From Eq. (2), the probability

Fig. 6. Illustration for bit margin of dot-product  $\mathbf{Q}_i \times \mathbf{K}_i^T$   $(\mathbf{A}_{i,j})$ .

assigned to  $a_0$  diminishes exponentially as the gap  $\delta$  increases. This reveals a fundamental property: within any input vector, an element's softmax probability is tightly linked to its distance from the maximum. A larger deviation from the maximal input results in a proportionally smaller impact on the output distribution.

softmax

$$(a_0) = \frac{e^{a_0}}{e^{a_0} + e^{a_0 + \delta}} = \frac{1}{1 + e^{\delta}} = e^{-\delta} \cdot \frac{1}{1 + e^{-\delta}} < e^{-\delta}$$

(2)

Building on this observation, we design an adaptive thresholding scheme that derives its decision boundary from the max attention score at each bit prediction round. Its formulation is given in Eq. (3), where  $A_{i,:}^r$  denotes the attention score at the r-th prediction round and  $\eta_i$  is the threshold for the i-th Query. In each round, the attention scores are compared against  $\eta_i$  and only the Keys with scores exceeding this threshold are preserved. Based on extensive experiments, we set the default radius to 5. To accommodate diverse accuracy–efficiency trade-offs, we further incorporate a hyperparameter  $\alpha \in [0,1]$  which scales the threshold and thereby controls the pruning aggressiveness of each round. Because the pruning threshold  $\eta_i$  is directly inferred from the underlying attention distribution, the method naturally adapts to score variations and achieves high accuracy in selecting vital tokens.

$$\eta_i = \max(A_i^r) - \alpha \times radius, \ \alpha \in [0, 1].$$

(3)

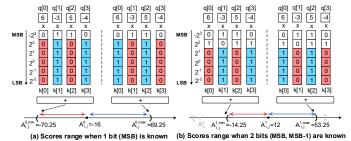

However, a subsequent challenge lies in how to accurately estimate the possible values of the dot product  $\mathbf{Q}_i \mathbf{K}_j^T$  (i.e.,  $A_{i,j}$ ), with only partial bits of the Key vectors. To this end, we introduce a *bit-level uncertainty margin*, which quantifies the potential variation introduced by the remaining (unprocessed) bits. Specifically, for an N-bit integer  $c_{N-1}c_{N-2}...c_0$  with 2's complement number format, its value x is:

$$x = -c_{N-1}2^{N-1} + \sum_{i=0}^{N-2} c_i 2^i.$$

(4)

In this format, all bits except the sign bit  $(c_{N-1})$  contribute a non-negative value, meaning that each additional bit can only increase or maintain the magnitude of the number. Based on this, Fig. 6 (a)(b) examplifies the bit margin. In this example,  $\mathbf{Q}_i$  retains all six bits, while  $\mathbf{K}_j$  has a fraction of 6 bits: 1 bit in Fig. 6 (a) and 2 bits in Fig. 6 (b). For elements of  $\mathbf{Q}_i$  that are positive, setting the unknown bits of  $\mathbf{K}_j$  to 1 (shown in blue), or to 0 (shown in red) if the element of  $\mathbf{Q}_i$  is negative, yields a potential maximum score  $A_{i,j}^{r,\max}$ , as it accounts only for positive contributions. Conversely, flipping the unknown bits yields the potential minimum score  $A_{i,j}^{r,\min}$ .

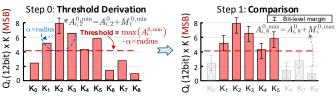

Fig. 7. Illustration of the bitwise LATS strategy.

Using the concept, we first utilize the low bound  $A_{i,:}^{r,\min}$  to derive the  $\eta_i$ . Then, when making pruning decisions for a  $\mathbf{K}_j$ , its potential maximum score  $A_{i,j}^{r,\max}$  at the r-th round is compared with the threshold  $\eta_i$ . As exemplified in Fig.7, for speculation by the MSB of Keys (i.e., r=0), during *Threshold Derivation*, the max (i.e.,  $A_{i,2}^{0,\min}$ ) among all lower bounds is selected, which is then subtracted by  $\alpha \times radius$  to derive the threshold. In subsequent *Comparison*, all upper bounds, i.e.,  $A_{i,j}^{0,\max}$ , are compared with this threshold to decide on pruning.

# C. Bit-Level Asynchronous Processing (BAP) Strategy

The BESF workflow determines token pruning decisions from incrementally accumulated partial scores, which are computed as successive bit planes of each Key vector become available. For any token that remains unpruned, the system will retrieve the next bit plane from DRAM to further refine its score. However, when these off-chip memory fetches are issued and serviced strictly in sequence, the resulting exposed access latency can leave the compute units idle, ultimately degrading overall hardware utilization.

To address this issue, we propose a bit-level asynchronous processing (BAP) strategy. Here, *asynchronous* indicates bit planes are no longer bound to arrive or be processed in a fixed order. Instead, computation proceeds whenever the required data becomes available.

As shown in Fig. 8, the BAP procedure begins by fetching only the most significant bit planes of the Key vectors, which provide the initial information needed for score estimation. As soon as one of these bit planes is returned from DRAM, its partial dot-product contribution is computed to determine whether the corresponding Key remains a candidate. If the Key survives this test, the following bit plane of the same Key is requested. Meanwhile, BAP stores intermediate results in a small on-chip buffer. Otherwise, BAP immediately moves on to the first bit plane of the next Key. When a later bit plane arrives (e.g., the loaded  $K_0^1$  in Fig. 8 (b)) arrives from DRAM, the previously buffered partial score  $(A_{i,0}^0)$  is retrieved and updated with the newly computed partial score, after which the BAP strategy repeats the same process. By continuously alternating between score refinement and new bit-plane requests, the compute units remain active even under long off-chip latency, substantially improving utilization during bit-level sparsity prediction.

#### IV. BITSTOPPER ACCELERATOR

# A. Overall Architecture

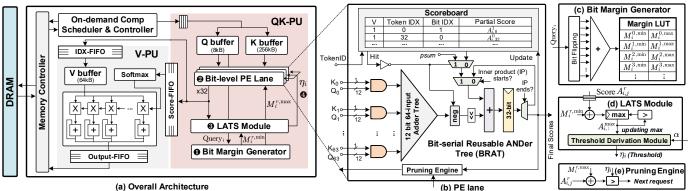

Fig. 9 (a) depicts the overall architecture of the BitStopper, which incorporates two major components:

1) Query-Key Processing Unit (QK-PU): This unit performs the sparse  $\mathbf{QK}^T$  computation directly, eliminating the

Fig. 8. Bit-level asynchronous processing (BAP) strategy.

need for an external sparsity predictor. It integrates 32 bit-level PE lanes, a LATS Module and a Bit Margin Generator, which collaboratively support the BESF, LATS and BAP strategies.

2) Value Processing Unit (V-PU): The V-PU computes the final attention results from the Value vectors aligned with the Keys preserved by the QK-PU. It integrates a softmax module and a multiply-accumulate (MAC) array, which performs a weighted summation over the corresponding Value vectors. To ensure efficient pipelining, the MAC array is designed to perform 64 INT12 MAC operations in a single cycle.

**Overall Dataflow**: In BitStopper, self-attention is performed with a 12-bit per tensor quantization, where each Key vector is decomposed into twelve 1-bit planes. For a given Query  $\mathbf{Q}_i$ , the QK-PU first employs the BESF to obtain the sparse attention scores, with the aid of LATS and BAP strategies. Then, the V-PU generates the final attention outputs. As depicted in Fig. 9 (a), its detailed process is as follows:

First ( $\mathbf{0}$ ), before the  $\mathbf{Q}_i \mathbf{K}^T$  computation, the Bit Margin Generator initializes twelve margin pairs  $(M_i^{r,\min}, M_i^{r,\max})$ , where  $r \in [0, 11]$ , based on the input  $\mathbf{Q}_i$ . Each pair corresponds to a specific bit plane. These bit margin pairs are then stored in a lookup table (LUT), as shown in Fig. 9 (c). Following this (2), 32 PE lanes perform the dot product for  $\mathbf{Q}_i \mathbf{K}^T$  and in an asynchronous manner in parallel. Then (3), the LATS Module, as depicted in Fig. 9 (d), calculates the pruning threshold  $\eta_i$ using the maximum value among the all current minimum score margins  $A_i^{\min}$  with the LATS logic (Eq. (3)). Finally ( $\bullet$ ), the pruning threshold  $\eta_i$  is broadcast to all PE lanes, enabling the evaluation of whether the score of the token jsatisfying  $A_{i,j}^{r,\max} > \eta_i$ , as depicted in Fig. 9 (e). If true, the PE lane requests the next bit plane for further computation. Otherwise, the token j is immediately pruned. This process is repeated until the LSB is reached. The remaining scores are sent to the V-PU to produce final attention outputs.

#### B. Microarchitecture of Bit-level PE Lane

Fig. 9 (b) presents the microarchitecture of the bit-level PE lane. To support LATS and BAP execution, the PE lane incorporates two key modules in addition to a bit-serial reusable ANDer tree (BRAT): 1) The Pruning Engine evaluates intermediate results and determines both the pruning outcome and the next bit plane to be retrieved. 2) The Scoreboard stores the partial scores  $S_{i,j}^r$  for tokens that remain unpruned, allowing subsequent rounds to reuse these values efficiently.

These modules collaborate to enable efficient early pruning. The process begins with the BRAT computing the partial dot product  $\Delta A_{i,j}^r$  from a 12-bit vector  $\mathbf{Q}_i$  and the 1-bit plane vector  $\mathbf{K}_j^r$ . In parallel, the Scoreboard is accessed with the token index j. If a partial score  $(A_{i,j}^{r-1})$  from the prior bit plane

TABLE I HARDWARE CONFIGURATIONS OF BITSTOPPER

| Main Memory         | HBM2; 8 channels $\times$ 128-bit at 2Gbps; each channel provides 32GB/s bandwidth.                             |

|---------------------|-----------------------------------------------------------------------------------------------------------------|

| On-chip Buffer      | 320KB SRAM for Key and Value buffers;<br>8KB Q buffer.                                                          |

| QK-PU               | 32 Bit-level PE Lanes An LATS module; A Bit Margin Generator                                                    |

| - Bit-level PE Lane | $64$ -dim $\times$ 12-bit $\times$ 1-bit Bit-serial Resuable ANDer tree; $64$ entry $\times$ 45-bit Scoreboard. |

| V-PU                | Single 1-D 64 way 12bit ×12bit MAC array;<br>A 18-bit input, 18-bit output LUT-based Softmax.                   |

is available, it is retrieved and added with the newly computed value to form the updated partial score  $A^r_{i,j}$  (i.e.,  $A^{r-1}_{i,j}+\Delta A^r_{i,j}$ ). Otherwise, if no prior entry exists, this indicates that the current bit plane is the MSB. In this case, the partial score  $\Delta A^r_{i,j}$  is directly written into Scoreboard, and the Hit signal is deasserted to show that no value can be reused.

Following this, the Pruning Engine performs the pruning operation. It receives the upper margin  $M_i^{r,\max}$  along with the partial score  $A_{i,j}^r$ , and checks whether the condition  $A_{i,j}^r+M_i^{r,\max}>\eta_i$  is satisfied. If the condition is met, it proceeds to fetch the next bit plane of  $\mathbf{K}_j$ , i.e.,  $\mathbf{K}_j^{r+1}$  and updates the partial score stored in the Scoreboard. Otherwise, it issues an eviction signal to remove the token's entry from Scoreboard and then requests the next Key vector from DRAM.

As shown in Fig. 9 (d), the LATS module first retrieves the stored scores from the register and combines them with the min margin  $M_i^{r,\mathrm{min}}$  to derive their lower bounds. Using these bounds together with the preset ratio parameter  $\alpha$ , the Threshold Derivation module applies the LATS logic as defined in Eq. (3) to compute the threshold  $\eta_i$ . Once computed, the derived threshold is broadcast to all bit-level PE lanes.

#### V. EVALUATION

#### A. Experimental Setup

Algorithm Evaluation. We evaluate our pruning strategy on two representative LLMs: OPT1B3 [37] and Llama2-7B [38]. Model quality is assessed via perplexity (PPL) on the Wikitext-2 dataset [39] and Dolly [40], where lower PPL indicates better performance. All evaluations are conducted using Pytorch and the HuggingFace library [41]. To accommodate outlier values, we employ INT12 quantization, which serves as the accuracy baseline and is derived via post-training quantization (PTQ).

Baseline and prior-art accelerators. We compare BitStopper with three DS accelerators for attention: 1) Baseline: a dense version based on BitStopper without sparsity modules. 2) Sanger [20]: a coarse-grained accelerator with 4-bit sparsity predictor. 3) SOFA [19]: which uses a top-k-based predictor and employs cross-stage tiling to minimize DRAM access. However, it relies on costly retraining to recover accuracy. 4) TokenPicker [26]: which utilizes 4-bit chunk progressive pruning with post-exp probability. For fairness, all designs are normalized to a 28nm process and evaluated under identical conditions: PE arrays occupy the same area as BitStopper and work in 1GHz, on-chip SRAM is set to 328kB.

**Hardware Evaluation**. Table I depicts the hardware configuration of the BitStopper accelerator. Each QK-PU comprises

Fig. 9. (a) Overview of the BitStopper accelerator. (b) PE lane architecture. (c) Bit margin generator. (d) LATS module. (e) Pruning engine.

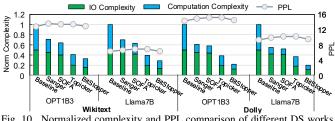

Fig. 10. Normalized complexity and PPL comparison of different DS works.

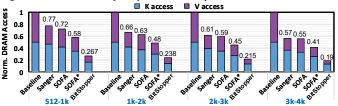

Fig. 11. Normalized off-chip memory access comparison for Llama-7B model. SOFA\* performs additional fine-tuning on Dolly and Wikitext datasets.

32 PE lanes, with each lane processing 64 bits of a Key vector per cycle to fully utilize HBM2 bandwidth. BitStopper is implemented in RTL and synthesized using Synopsys DC under 28nm CMOS to estimate logic area and power (Fig. 14). The speedup is evaluated via an in-house developed cycle-level simulator. The energy and area of on-chip buffers and scoreboard are estimated through CACTI [42]. To get the number of cycles and energy of off-chip accesses, we use Ramulator [43] with trace files generated in RTL simulation.

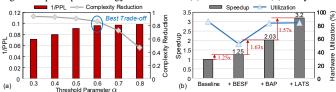

Configurations. We evaluate the PPL with varying pruning ratio by tuning the parameter  $\alpha$  from 0.2 to 0.8 in step of 0.1. We then apply the successive halving method to expedite the process. For all hardware evaluations, sequence lengths are set to 1k for OPT1.3B and 2k for LLaMA2-7B for the Wikitext dataset, while they are set to 2k and 4k for Dolly.

#### B. Complexity Reduction Comparisons

Fig. 10 compares the normalized complexity of different DS works under comparable PPL. Sanger predicts sparsity using an extra 4-bit predictor with static thresholding, whereas SOFA relies on a log-domain predictor combined with top-k sorting. As shown, while Sanger and SOFA successfully alleviate computation complexity by an average of 69% and 65% (blue part) through token sparsity, respectively, they fail to realize evident memory access reduction (green part). Such IO burden becomes more prohibitive in long sequence scenarios (see Dolly task). This is because their sparsity predictions have

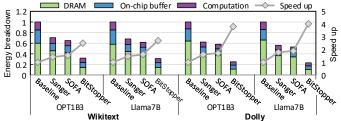

Fig. 12. Speedup and energy breakdown in (a) Wikitext-2 and (b) Dolly tasks.

Fig. 13. 1/PPL (higher is better) and complexity reduction versus pruning parameter  $\alpha$ . The results are derived from Llama7B on the Dolly dataset. (b) Speedup breakdown and hardware utilization.

to fetch full-size  $(S \times H)$  Key matrix, resulting in a heavy IO burden. While TokenPicker removes the extra predictor, its post-exp decision incurs significant computational overhead. Further, its coarse 4-bit chunk granularity misses finergrained redundancy, leaving substantial optimization potential untapped. By contrast, BitStopper's BESF and LATS strategies substantially reduce both IO and computation complexity while preserving comparable PPL. These gains stem from finegrained, stage-fusion bit early stopping and adaptive decision-making, which eliminate more invalid processing.

Fig. 11 compares DRAM access reduction across different designs and sequence lengths. For fairness, we set the precision of QKV to 12 bits and allows almost +0.1 PPL on Wikitext-2 and Dolly tasks. BitStopper consistently outperforms Sanger and SOFA\*, achieving average reductions of  $2.9\times$  and  $2.1\times$ . This benefit stems from the synergy between the LATS and BAP strategies, which dynamically adjust thresholds and eliminate redundant memory accesses at fine granularity. In contrast, Sanger's coarse-grained filtering prevents early termination of trivial Key accesses, while SOFA's fixed top-k selection lacks adaptability, degrading inference accuracy without fine-tuning. Notably, BitStopper achieves a  $2.8\times$  greater memory access reduction than unfinetuned SOFA.

## C. Performance Evaluation

Fig. 12 compares the throughput and energy consumption. The energy is broken down into computation, on-chip buffer,

and off-chip memory. Sanger (67%) and SOFA (62%) exhibit higher DRAM overheads due to additional prediction units, leading to substantial unreusable memory access. In contrast, BitStopper limits this overhead to 38% via bit-grained stage-fusion strategy. In terms of speedup, as the sequence length increases, BitStopper's speedup becomes more pronounced. This is because longer sequences contain more redundancy, and the distribution disparity among different queries increases. BitStopper's LATS strategy is well-suited to handle such scenarios. In contrast, static strategies in Sanger and SOFA result in redundant computation and memory access. Overall, BitStopper achieves average speedups of  $3.2\times$ ,  $2.03\times$ , and  $1.89\times$ , and energy efficiency improvements of  $3.7\times$ ,  $2.4\times$  and  $2.1\times$ , compared to Baseline, Sanger, and SOFA, respectively.

Fig. 13 (a) analyzes how different pruning parameters  $\alpha$  affect PPL and reduced complexity. Overall, a smaller  $\alpha$  delivers more pruning, yielding greater complexity reduction but lowering 1/PPL. As observed, when  $\alpha$  falls below 0.6, the reduction in complexity begins to plateau, while 1/PPL drops sharply. This is because overly aggressive token pruning, which removes certain critical tokens, thus severely degrading the 1/PPL and hindering further complexity reduction. To strike a balanced trade-off between accuracy and efficiency, we thus prioritize setting the value of  $\alpha$  near 0.6.

Fig. 13 (b) presents a breakdown of the speedup achieved by BitStopper, using a baseline dense attention accelerator derived from BitStopper but excluding all sparse processing modules. While the incorporation of BESF yields a modest throughput improvement, compute unit utilization remains limited to 48% due to unhidden memory access latency, thereby capping the overall speedup at  $1.25\times$ . With the integration of BAP, asynchronous out-of-order execution effectively mitigates memory latency, increasing compute unit utilization to 83% and enhancing the speedup by  $1.63\times$ . Finally, LATS reduces memory accesses and computations for irrelevant tokens, lowering dynamic power consumption and achieving a  $1.57\times$  speedup.

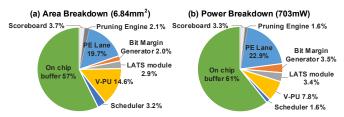

# D. Area and Power

Fig. 14 presents the area and power breakdown of the Bit-Stopper accelerator. Occupying 6.84 mm² and consuming 703 mW, it achieves a peak energy efficiency of 11.36 TOPS/W. The newly added Bit Margin Generator and LATS modules adaptively respond to attention distribution and enhance token pruning, incurring only 4.9% area and 6.9% power overhead. Additionally, the integration of the Scoreboard and Pruning Engine into PE lanes enables stage fusion, adding 5.8% area and 4.9% power overhead. Despite the modest hardware cost, the elimination of the sparsity predictor and reduced off-chip memory access lead to significant efficiency gains. BitStopper thus represents a deliberate trade-off, achieving substantial energy efficiency improvements with minimal resource overhead.

#### VI. RELATED WORKS

Numerous attention accelerators [14]–[22], [24]–[26], [34], [36], [44]–[46] have been proposed. Early works, such as A<sup>3</sup> [14] and ELSA [15] accelerate computation via approximation

Fig. 14. Area/Power of BitStopper at TSMC 28nm, 1GHz.

techniques. Recent efforts have shifted to jointly optimizing computation and memory. Energon [16] and SOFA [19] adopt fine-grained filtering and tiling to alleviate memory overhead. However, they still rely on extra sparsity predictors, which become de facto latency and power bottlenecks after sparsification. Although the more recent BETA [46] introduces bit-level filtering, it likewise retains an additional sparsity predictor. Further, the absence of a bit-uncertainty margin renders its pruning decisions highly inaccurate. BitStopper is the first to explicitly identify and address this issue. It removes the need for external predictors by fine-grained, bit-serial computation, while leveraging efficient bit-level early termination and reuse.

Although TokenPicker [26] also adopts bit-chunk reuse to alleviate memory access, BitStopper differs in several key aspects: 1) Simpler decision strategy. BitStopper employs a lightweight, max-based decision, whereas TokenPicker relies on a more complex Softmax-based selection. 2) Broader applicability. Its simplified decision logic allows BitStopper to operate in both Prefill and Decoding, whereas TokenPicker is restricted to Decoding only. 3) Finer granularity. BitStopper operates at a bit-level reuse granularity, while TokenPicker is constrained to 4-bit chunks, making it conceptually closer to previous works such as SpAtten [22] and Energon [16].

#### VII. CONCLUSION

This paper presents BitStopper, a bit-grained, stage-fusion accelerator that eliminates the extra sparsity predictor via bit-level reuse opportunities. A lightweight adaptive token selection strategy improves pruning accuracy, while bit-level asynchronous processing enhances hardware utilization. Experimental results show that BitStopper delivers superior efficiency compared with existing attention sparsity accelerators.

#### ACKNOWLEDGMENTS

This work was supported in part by the National Science and Technology Major Project under Grant 2022ZD0115200; in part by the NSFC under Grant 62125403, Grant 92464302, Grant U24B20164 and Grant 92164301; in part by Shanghai Municipal Science and Technology Major Project; in part by the Natural Science Foundation of Jiangsu Province Basic Research Program under Grant BK20243042; in part by the Beijing National Research Center for Information Science and Technology; in part by the Northern IC Technology Innovation Center (Beijing) Co., Ltd under Grant QYJS20232801B; and in part by the Beijing Advanced Innovation Center for Integrated Circuits.

#### REFERENCES

- [1] J. Wei, Y. Tay, R. Bommasani *et al.*, "Emergent abilities of large language models," *arXiv preprint arXiv:2206.07682*, 2022.

- [2] A. Yuan, A. Coenen, E. Reif, and D. Ippolito, "Wordcraft: Story writing with large language models," in *Proc. Int. Conf. Intell. User Interfaces*, 2022, pp. 841–852.

- [3] R. Thoppilan, D. De Freitas, J. Hall *et al.*, "Lamda: Language models for dialog applications," *arXiv preprint arXiv:2201.08239*, 2022.

- [4] T. Zhang, F. Ladhak, E. Durmus et al., "Benchmarking large language models for news summarization," Trans. Assoc. Comput. Linguistics, vol. 12, pp. 39–57, 2024.

- [5] A. Radford, J. Wu, R. Child, D. Luan, D. Amodei, and I. Sutskever, "Language models are unsupervised multitask learners," *OpenAI blog*, vol. 1, no. 8, p. 9, 2019.

- [6] K. S. Kalyan, "A survey of GPT-3 family large language models including ChatGPT and GPT-4," *Natural Lang. Proces. J.*, vol. 6, p. 100048, 2024.

- [7] J. Ye, X. Chen, N. Xu, C. Zu, Z. Shao, S. Liu, Y. Cui, Z. Zhou, C. Gong, Y. Shen et al., "A comprehensive capability analysis of GPT-3 and GPT-3.5 series models," arXiv preprint arXiv:2303.10420, 2023.

- [8] A. Vaswani, N. Shazeer, N. Parmar et al., "Attention is all you need," Adv. Neural Inf. Process. Syst., vol. 30, 2017.

- [9] H. Wang, Z. Wang, Z. Yue, Y. Long, T. Wei, J. Yang, Y. Wang, C. Li, S. Wei, Y. Hu et al., "MCBP: A Memory-Compute Efficient LLM Inference Accelerator Leveraging Bit-Slice-enabled Sparsity and Repetitiveness," in Proc. 58th IEEE/ACM Int. Symp. Microarchit. (MICRO), 2025, pp. 1592–1608.

- [10] S. Kim, C. Hooper, T. Wattanawong, M. Kang, R. Yan, H. Genc et al., "Full stack optimization of Transformer inference: A survey," arXiv preprint arXiv:2302.14017, 2023.

- [11] K. A. A. Fuad and L. Chen, "A survey on sparsity exploration in Transformer-based accelerators," *Electronics*, vol. 12, no. 10, p. 2299, 2023.

- [12] W. X. Zhao, K. Zhou, J. Li, T. Tang, X. Wang, Y. Hou, Y. Min, B. Zhang, J. Zhang, Z. Dong et al., "A survey of large language models," arXiv preprint arXiv:2303.18223, vol. 1, no. 2, 2023.

- [13] Z. Zhou, X. Ning, K. Hong, T. Fu, J. Xu, S. Li, Y. Lou, L. Wang, Z. Yuan, X. Li et al., "A survey on efficient inference for large language models," arXiv preprint arXiv:2404.14294, 2024.

- [14] T. J. Ham, S. J. Jung, S. Kim, Y. H. Oh, Y. Park, Y. Song, J.-H. Park, S. Lee, K. Park, J. W. Lee et al., "A<sup>3</sup>: Accelerating attention mechanisms in neural networks with approximation," in Proc. IEEE Int. Symp. High Perform. Comput. Archit. (HPCA), 2020, pp. 328–341.

- [15] T. J. Ham, Y. Lee, S. H. Seo et al., "ELSA: Hardware-software co-design for efficient, lightweight self-attention mechanism in neural networks," in Proc. IEEE Int. Symp. Comput. Architect., 2021, pp. 692–705.

- [16] Z. Zhou, J. Liu et al., "Energon: Toward efficient acceleration of Transformers using dynamic sparse attention," *IEEE Trans. Comput.-*Aided Design Integr. Circuits Syst., vol. 42, no. 1, pp. 136–149, 2022.

- [17] Z. Qu, L. Liu, F. Tu, Z. Chen, Y. Ding, and Y. Xie, "DOTA: Detect and omit weak attentions for scalable transformer acceleration," in *Proc.* ACM Int. Conf. Architectural Support Program. Lang. Operating Syst., 2022, pp. 14–26.

- [18] Y. Qin, Y. Wang, D. Deng et al., "FACT: FFN-Attention co-optimized Transformer architecture with eager correlation prediction," in Proc. IEEE Annu. Int. Symp. Comput. Archit. (ISCA), 2023, pp. 1–14.

- [19] H. Wang, J. Fang, X. Tang et al., "SOFA: A compute-memory optimized sparsity accelerator via cross-stage coordinated tiling," in Proc. 57th IEEE/ACM Int. Symp. Microarchit. (MICRO), 2024, pp. 1247–1263.

- [20] L. Lu, Y. Jin, H. Bi et al., "Sanger: A co-design framework for enabling sparse attention using reconfigurable architecture," in Proc. IEEE/ACM Int. Symp. Microarchit. (MICRO), 2021, pp. 977–991.

- [21] Z. Li, S. Ghodrati, A. Yazdanbakhsh et al., "Accelerating attention through gradient-based learned runtime pruning," in Proc. IEEE Annu. Int. Symp. Comput. Archit. (ISCA), 2022, pp. 902–915.

- [22] H. Wang, Z. Zhang, and S. Han, "Spatten: Efficient sparse attention architecture with cascade token and head pruning," in *Proc. IEEE Int.* Symp. High Perform. Comput. Archit. (HPCA), 2021, pp. 97–110.

- [23] L. Liu, Z. Qu, Z. Chen, F. Tu, Y. Ding, and Y. Xie, "Dynamic sparse attention for scalable transformer acceleration," *IEEE Transactions on Computers*, vol. 71, no. 12, pp. 3165–3178, 2022.

- [24] T. Yang, F. Ma, X. Li, F. Liu et al., "DTATrans: Leveraging dynamic token-based quantization with accuracy compensation mechanism for efficient Transformer architecture," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 42, no. 2, pp. 509–520, 2022.

- [25] H. Fan, T. Chau, S. I. Venieris, R. Lee, A. Kouris, W. Luk, N. D. Lane, and M. S. Abdelfattah, "Adaptable butterfly accelerator for attention-based nns via hardware and algorithm co-design," in *Proc. IEEE/ACM Int. Symp. Microarchit. (MICRO)*, 2022, pp. 599–615.

- [26] J. Park, M. Kang, Y. Han et al., "Token-picker: Accelerating attention in text generation with minimized memory transfer via probability estimation," in Proc. 61st ACM/IEEE Des. Autom. Conf., 2024, pp. 1–6.

- [27] H. Cho, D. Kim, Hwang et al., "SpARC: Token Similarity-Aware Sparse Attention Transformer Accelerator via Row-wise Clustering," in Proc. 61st ACM/IEEE Des. Autom. Conf. (DAC), 2024, pp. 1–6.

- [28] S. Lee, B. Kim, J. Park, and D. Jeon, "CLAT: A clustering-based attention Transformer accelerator for low-latency text generation in LLMs," *IEEE Trans. Circuits Syst.* 1, 2025.

- [29] J. Lee, C. Kim, S. Kang, D. Shin, S. Kim, and H.-J. Yoo, "UNPU: A 50.6 TOPS/W unified deep neural network accelerator with 1b-to-16b fully-variable weight bit-precision," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2018, pp. 218–220.

- [30] D. Kam, M. Yun, S. Yoo, S. Hong, Z. Zhang, and Y. Lee, "Panacea: Novel DNN Accelerator using Accuracy-Preserving Asymmetric Quantization and Energy-Saving Bit-Slice Sparsity," in *Proc. IEEE Int. Symp. High Perform. Comput. Archit.* (HPCA), 2025, pp. 701–715.

- [31] D. Im, G. Park, Z. Li, J. Ryu, and H.-J. Yoo, "Sibia: Signed bitslice architecture for dense DNN acceleration with slice-level sparsity exploitation," in *Proc. IEEE Int. Symp. High Perform. Comput. Archit.* (HPCA), 2023, pp. 69–80.

- [32] C. Guo, C. Wei, J. Tang, B. Duan, S. Han, H. Li, and Y. Chen, "Transitive Array: An Efficient GEMM Accelerator with Result Reuse," in *Proc.* IEEE Annu. Int. Symp. Comput. Archit. (ISCA), 2025, pp. 990–1004.

- [33] Z. Song, C. Qi, Y. Yao, P. Zhou, Y. Zi, N. Wang, and X. Liang, "TSAcc: An Efficient Temporal-Spatial Similarity Aware Accelerator for Attention Acceleration," in *Proc. 61st ACM/IEEE Des. Autom. Conf.* (DAC), 2024, pp. 1–6.

- [34] J. Zhao, P. Zeng, G. Shen, Q. Chen, and M. Guo, "Hardware-software co-design enabling static and dynamic sparse attention mechanisms," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, 2024.

- [35] H. Wang, H. Xu, Y. Wang, and Y. Han, "CTA: Hardware-software codesign for compressed token attention mechanism," in *Proc. IEEE Int.* Symp. High Perform. Comput. Archit. (HPCA), 2023, pp. 429–441.

- [36] S. Hong, S. Moon, J. Kim, S. Lee, M. Kim, D. Lee, and J.-Y. Kim, "DFX: A low-latency multi-FPGA appliance for accelerating Transformer-based text generation," in *Proc. IEEE/ACM Int. Symp. Microarchit.* (MICRO), 2022, pp. 616–630.

- [37] S. Zhang, S. Roller, N. Goyal et al., "OPT: Open pre-trained Transformer language models," arXiv preprint arXiv:2205.01068, 2022.

- [38] H. Touvron, L. Martin, K. Stone, P. Albert et al., "Llama 2: Open foundation and fine-tuned chat models," arXiv:2307.09288, 2023.

- [39] S. Merity, C. Xiong, J. Bradbury, and R. Socher, "Pointer sentinel mixture models," arXiv preprint arXiv:1609.07843, 2016.

- [40] M. Conover, M. Hayes, A. Mathur, J. Xie, J. Wan, S. Shah, A. Ghodsi et al., "Free dolly: Introducing the world's first truly open instruction-tuned LLM," Company Blog of Databricks, 2023.

- [41] T. Wolf, L. Debut, V. Sanh *et al.*, "Transformers: State-of-the-art natural language processing," in *Proc. Conf. Empirical Methods Natural Lang. Process.*: Syst. Demonstrations, 2020, pp. 38–45.

- [42] R. Balasubramonian, A. B. Kahng, N. Muralimanohar et al., "CACTI: New tools for interconnect exploration in innovative off-chip memories," ACM Trans. Archit, Code Optim., vol. 14, no. 2, pp. 1–25, 2017.

- [43] H. Luo, Y. C. Tuğrul, F. N. Bostancı, A. Olgun et al., "Ramulator 2.0: A modern, modular, and extensible DRAM simulator," *IEEE Comput. Archit. Lett.*, vol. 23, no. 1, pp. 112–116, 2023.

- [44] B. Li, S. Pandey, H. Fang, Y. Lyv, J. Li, J. Chen, M. Xie, L. Wan, H. Liu, and C. Ding, "FTRANS: Energy-efficient acceleration of Transformers using FPGA," in *Proc. ACM/IEEE Int. Symp. Low Power Electron. Des.*, 2020, pp. 175–180.

- [45] S. Liu, P. C. Kuve, and A. Karanth, "HSCONN: Hardware-Software Co-Optimization of Self-Attention Neural Networks for Large Language Models," in *Proc. Great Lakes Symp. VLSI* 2024, 2024, pp. 736–741.

- [46] H. Wang, H. Wang, Z. Yue, J. Liu et al., "Beta: A bit-grained transformer attention accelerator with efficient early termination," *IEEE Trans. Circuits Syst. II*, 2025.