# A 33.6-136.2 TOPS/W Nonlinear Analog Computing-In-Memory Macro for Multi-bit LSTM Accelerator in 65 nm CMOS

Junyi Yang<sup>®</sup>, Graduate Student Member, IEEE, Xinyu Luo<sup>®</sup>, Ye Ke<sup>®</sup>, Zheng Wang, Member, IEEE, Hongyang Shang<sup>®</sup>, Shuai Dong<sup>®</sup>, Zhengnan Fu<sup>®</sup>, Xiaofeng Yang<sup>®</sup>, Hongjie Liu<sup>®</sup>, and Arindam Basu<sup>®</sup>, Senior Member, IEEE

Abstract—The energy efficiency of analog computing-inmemory (ACIM) accelerator for recurrent neural networks, particularly long short-term memory (LSTM) network, is limited by the high proportion of nonlinear (NL) operations typically executed digitally. To address this, we propose an LSTM accelerator incorporating an ACIM macro with reconfigurable (1-5 bit) nonlinear in-memory (NLIM) analog-to-digital converter (ADC) to compute NL activations directly in the analog domain using: 1) a dual 9T bitcell with decoupled read/write paths for signed inputs and ternary weight operations; 2) a read-word-line underdrive Cascode (RUDC) technique achieving 2.8× higher read-bitline dynamic range than single-transistor designs (1.4× better over conventional Cascode structure with 7× lower current variation); 3) a dual-supply 6T-SRAM array for efficient multi-bit weight operations and reducing both bitcell count (7.8x) and latency (4×) for 5-bit weight operations. We experimentally demonstrate 5-bit NLIM ADC for approximating NL activations in LSTM cells, achieving average error <1 LSB. Simulation confirms the robustness of NLIM ADC against temperature variations thanks to the replica bias strategy. Our design achieves 92.0% onchip inference accuracy for a 12-class keyword-spotting task while demonstrating 2.2× higher system-level normalized energy efficiency and 1.6× better normalized area efficiency than stateof-the-art works. The results combine physical measurements of a macro unit-accounting for the majority of LSTM operations (99% linear and 80% nonlinear operations)—with simulations of the remaining components, including additional LSTM and fully connected layers.

Index Terms—Computing-In-Memory, Nonlinear ADC, Inmemory ADC, LSTM, Read word-line Underdrive, SRAM.

#### I. INTRODUCTION

Conventional von Neumann-based deep neural network (DNN) accelerators face critical performance bottlenecks due to extensive data movement between processor and memory [1], [2]. Computing-in-memory (CIM), which integrates processor and memory together, has gained popularity as a solution to address these issues [3], [4], [5], [6]. It is a better architecture for the massively parallel execution of multiply-accumulate (MAC) operations, enabling computations to be

This work was supported by ITF MSRP grant ITS/018/22MS. (Corresponding authors: Arindam Basu) Arindam Basu is with Department of Electrical Engineering and the State Key Laboratory of Terahertz and Millimeter Waves, City University of Hong Kong, Hong Kong, China (e-mail: arinbasu@cityu.edu.hk). Junyi Yang, Xinyu Luo, Ye Ke, Hongyang Shang, Shuai Dong, Zhengnan Fu are with Department of Electrical Engineering, City University of Hong Kong, Hong Kong, China. Zheng Wang is with the Shenzhen Institutes of Advanced Technology, Chinese Academy of Sciences, Shenzhen 518055, China. Xiaofeng Yang and Hongjie Liu are with Reexen Technology, Shenzhen 518000, China.

performed directly within the memory unit itself. This design effectively eliminates the need for data movement between the processor and memory, thereby enhancing efficiency. Among the reported CIM accelerators, analog computing in-memory (ACIM) utilizing CMOS-based memory devices, such as static random access memory (SRAM), has demonstrated significant potential in enhancing energy and area efficiencies [2], [7], [8]. However, SRAM-based ACIM faces challenges due to multi-bit weight, limited signal margin of read bitline voltage ( $V_{RBL}$ ) and analog-to-digital converter (ADC) overhead [3], [9], [10]. These challenges require urgent attention to enhance the performance of ACIM systems.

Challenge one: Multi-bit ternary weight and signed input. One of the current challenges for ACIM is to support multi-bit weights [11], [12]. In many SRAM-based ACIM scheme, multibit weights are typically stored in a group of SRAM cells because each SRAM cell can only store one digital bit. To implement multi-bit weights, the first method is to change the amplitude of the read word line (RWL) signals using digital-to-analog converters (DACs) [11], [12], which increases hardware overhead and suffers from NL relationship from RWL-voltage to  $V_{RBL}$  [11]. The second method is to change the pulse width of RWL [13], [14]. However, this approach results in a decrease in throughput by  $2^{n_w-1}$ times (where  $n_w$  denotes weight precision). The third method, utilized in [9], [15], avoids a decrease in throughput but requires  $2^{n_w}-1$  cells for  $n_w$ -bit weight, leading to substantial hardware overhead. Another issue is the handling of signed inputs. Currently, many CIMs [2], [4], [5], [6], [11], [12] support only unsigned inputs, as they target convolutional neural networks (CNNs) and multi-layer perceptrons (MLPs) with ReLU-generated non-negative values. However, for recurrent neural networks (RNNs) and attention-based neural network, the inputs are signed. Therefore, it is crucial to design CIM systems that can effectively support signed inputs to meet the requirements of these more complex neural network architectures.

Challenge two: Limited signal margin and linearity. Boosting MAC operations via multiple RWLs improves EE and throughput but widens MAC voltage range, reducing signal margin under fixed dynamic range (DR) of  $V_{RBL}$  [9]. To address this limitation, a source degeneration architecture is employed to enhance the signal margin and increase the voltage swing range [10]. This approach achieves a signal

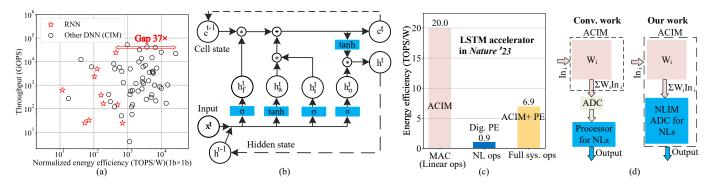

Fig. 1. Limitations and solutions of current CIM for RNNs: (a) A survey of RNN accelerators and other CIM-based DNN accelerators (All energy efficiencies are normalized to 1-bit input and 1-bit weight, according to this formula [18]: Normalized EE=EE × input precision × weight precision). (b) One LSTM cell with a large number of nonlinear activations.(c) Energy efficiency of various sub-parts of the LSTM accelerator in previous work (*Nature'23*, [19]). (d) Architecture comparison of our proposed method with the conventional method for LSTM accelerator.

margin that is 1.44× larger than that of conventional 6T-SRAM cells while maintaining the same precision in MAC operations.

Challenge three: ADC for ACIM. Designing an efficient ADC for ACIM presents significant challenges due to the significant overhead in both area and energy consumption [12], [16]. In-memory (IM) ADC is proposed to reduce the overhead of traditional ADC and convert analog MAC signals to digital code simultaneously [9], [13], [17]. However, IM ADC incurs a substantial area overhead for calibration, since the number of bitcells needed for calibration is equivalent to that of the ADC, effectively doubling the memory requirement [9].

Most importantly, this improvement of efficiencies by CIM does not extend to the full system when implementing RNNs, such as long short-term memory (LSTM) networks. Fig. 1(a) illustrates normalized energy efficiency (EE) based on input and weight resolutions and throughput of current RNN accelerators [19]-[28] in comparison to those of recent CNN and MLP accelerators using CIM. With the CNN accelerator achieving a normalized EE of 25840 TOPS/W [29] compared to just normalized 696.5 TOPS/W [27] for the RNN accelerator, this 37× gap highlights the limitation of current CIM in improving the EE of RNN accelerators. The limitation in EE improvements for RNNs, particularly LSTM, stem from the high proportion of nonlinear (NL) operations as shown in Fig. 1(b) typically executed digitally. These NL operations, such as the sigmoid and hyperbolic tangent functions used as activation functions, are computationally intensive and can become a significant bottleneck in the overall processing efficiency. For example, [19] conducted a comparative analysis about the EEs of various sub-parts of an ACIM-based LSTM accelerator as depicted in Fig. 1(c). In this system, the linear operations (MAC) are executed by ACIM with high EE (20 TOPS/W), while the NL operations are performed by the digital processor resulting in a low EE (0.9 TOPS/W). The overall EE of the system (6.9 TOPS/W) is diminished by a factor of 2.9 in comparison to 20 TOPS/W due to the significantly lower EE associated with the NL operations in the LSTM cell. Addressing the computational bottleneck induced by NL operations is critical, especially since compact LSTM architectures demonstrate superior parameter efficiency over Transformer-based networks while maintaining competitive performance in sequential modeling tasks such as speech recognition [27] and char prediction [24].

There are several methods to calculate NL operations in LSTM cell, such as piecewise linear approximations [27], [30], [31], cordic [32], lookup table [33], quadratic polynomial approximation [34]. However, these methods all compute each NL operation serially in the digital domain, which increases system latency and reduces energy efficiency.

Recent studies [35], [36] have attempted to compute NL activation functions in the analog domain. A resistive randomaccess memory (RRAM)-based NL ADC was proposed in [35] to approximate the NL activation function; however, this work only validated the accuracy of the NL functions in the presence of RRAM programming errors, without integrating it directly with a MAC unit in silicon. This is primarily due to the difficulty of integrating RRAM arrays with complex CMOS peripheral circuits. Additionally, two major drawbacks are noted: the significant programmed error and stuck-at-fault ratio of RRAM devices considerably degrade network accuracy (88.5% for 12-class under 5-bit ADC, Google Speech Commands Dataset (GSCD)), and the charge-domain in-memory computing architecture adopted employs integrators that account for more than half of the total system power, thereby reducing overall energy efficiency. In [36], analog circuitry utilizing Taylor approximation to fit nonlinear activation functions was introduced. While this approach has been validated at the module level, it has not been integrated with CIM array to demonstrate overall performance in silicon. Moreover, the module occupies a considerable area of 1218  $\mu m^2$ , making it impractical to integrate one module per CIM column to achieve parallel computation. Another limitation is that its output remains in the analog domain, which the authors claim can help to remove AD/DA overheads and be passed directly to the next layer. However, this is only true for small networks where direct connections can be made-in most practical cases, the output has to be stored in local memory for further digital processing (such as element wise products in LSTM) or data staging (creating feature maps in CNN for use by the next layer) [19]. This necessitates an additional ADC to quantize the output signal for communication with the external digital controller. This extra ADC not only increases system overhead

but also further degrades the accuracy of the NL approximation due to quantization errors. Further, this method [36] uses sub-threshold techniques for log-conversion-when used in an array, such approaches are known to suffer from exacerbated mismatch due to the exponential dependence of the output current on threshold voltage mismatch. Some other works [37], [38] have designed ADCs with programmable range to better match with the distribution of MAC values; however, they cannot be programmed to perform arbitrarily nonlinear operations. Consequently, it is imperative to explore alternative approaches that can perform NL operations more efficiently to enhance the overall efficiency of LSTM accelerators.

To address the aforementioned issues, the main contributions of this work are summarized as follows:

- 1) A dual 9T bitcell is proposed to support signed inputs and ternary weights, combined with a dual-supply 6T-SRAM for efficient implementation for multi-bit weights, which reduces bitcell count by 7.8× and latency by 4× compared to prior methods [9], [13] for 5-bit weight operations.

- 2) We propose a read-word-line under drive Cascode (RUDC) technique that increases DR of  $V_{RBL}$  by 2.8× versus prior work [9] and 1.4x versus conventional Cascode structure with 7× improvement of discharge current linearity.

- 3) We propose an innovative SRAM-based reconfigurable nonlinear in-memory (NLIM) ADC that directly computes LSTM activation functions (sigmoid/tanh) in the analog domain as illustrated in Fig. 1(d). The hardware-implemented NLIM ADC exhibits an error of less than 1 LSB when approximating the sigmoid and tanh functions, overcoming digital computation bottlenecks while maintaining temperature robustness due to replica bias. Our NLIM ADC (including the NL controller) achieves a 3.3x improvement in normalized area over the SAR ADC in [39] with an NL processor. It also achieves a 3.7× improvement compared to the linear inmemory ADC in [9] with an NL processor.

- 4) Our keyword-spotting (KWS) system achieves 92% (better than previous SOTA: 91.8% [40]) on-chip inference accuracy (12-class, GSCD), enabled by quantization and hardware nonidealities aware training, with 2.2× higher system-level normalized EE and 1.6× better normalized area efficiency than SOTA RNN accelerators [26], [28].

# II. MACRO STRUCTURE

To solve the above challenges, 1) we propose dual 9T SRAM bitcell to implement signed input and dual-supply 6T-SRAM array to implement multi-bit weight efficiently. 2) We utilize RUDC to enhance DR of  $V_{RBL}$  and linearity of discharge current of bitcell. 3) We propose NLIM ADC to reduce the huge hardware overhead of ADC calibration bitcells and enables the parallel computation of NL operations in the analog domain.

# A. Proposed System Architecture and Application

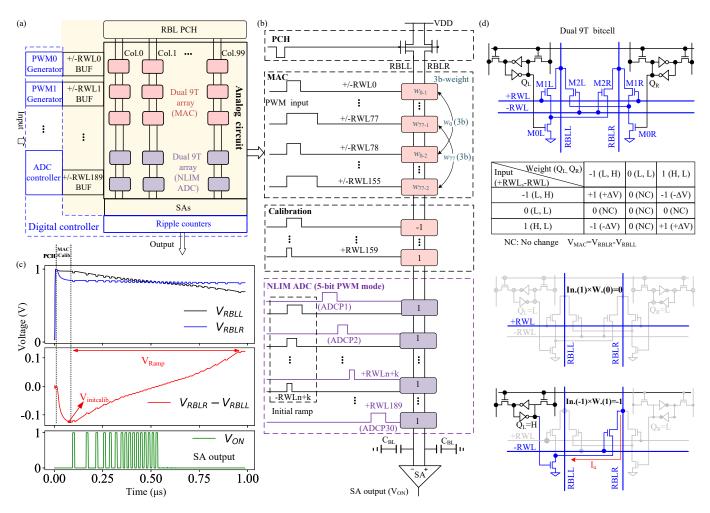

The top-level schematic of the CIM and NLIM ADC based on SRAM is depicted in Fig. 2(a), which includes  $160 \times 100$ dual 9T SRAM bitcells for MAC and calibration,  $30 \times 100$ bitcells for references of the reconfigurable NLIM ADC, sense amplifiers(SAs), RWL buffers, pulse-width modulation (PWM) generators, NLIM ADC controller, and ripple counters. To clearly demonstrate how it works, the timing of MAC operations using PWM mode for multi-bit input and a set of NLIM ADC timing diagram are shown in Fig. 2(b). PWM inputs, calibration inputs, and intial ramp inputs of NLIM ADC part are applied simultaneously (Fig. 2(b)) to create  $V_{MAC} = V_{RBLR} - V_{RBLL}$  on the bitlines (using current-mode operation). Fig. 2(c) shows voltage waveforms of two  $V_{RBL}s$ and their difference based on post-layout simulation. After MAC, calibration, and initial ramp,  $V_{MAC}$  is in the position of  $V_{initcalib}$  in Fig. 2(c). Next, the NLIM ADC part creates a reference decreasing voltage on RBLL every clock cycle using ADC pulses (ADCP1-ADCP30 in Fig. 2(b)), which effectively increases the ramp voltage  $(V_{Ramp})$  (Fig. 2(c)). The NLIM ADC controller is used to generate the RWLs pulse of the NLIM ADC part shared by all columns of NLIM ADC. Therefore, each of the 100 SAs can simultaneously compare  $V_{RBLL}$  with  $V_{RBLR}$ . The ripple counters convert the output thermometer code of the SAs into binary codes. The system clock frequency in our implementation is 100 MHz.

# B. Dual 9T SRAM-based In-Memory Ternary Multiplication and Accumulation

A dual 9T SRAM bitcell has been employed for the implementation of the macro as illustrated in Fig. 2(d) (top). This bitcell facilitates ternary multiplication of a signed input with a ternary weight using a decoupled read path, which includes the six blue NMOS transistors (three transistors on each side as depicted in Fig. 2(d)).

For positive inputs, the high voltage is applied to the +RWL, while for negative inputs, the high voltage is applied to the -RWL. Ternary weights (-1( $Q_L$ =L,  $Q_R$ =H); 0(( $Q_L$ =L,  $Q_R=L$ )) and +1(( $Q_L=H, Q_R=L$ ))) can be stored in the dual 6T-SRAM bitcells. Fig. 2(d) (bottom) depicts two possible multiplication cases with different input and weight values. When the weight is 0 ( $Q_L$ =L,  $Q_R$ =L), no current discharges the RBLL or RBLR, regardless of the inputs. Conversely, when the weight is -1/1, either RBLL or RBLR is discharged via the corresponding NMOS transistor, where the gate is linked to +RWL/-RWL with a high voltage. The ternary multiplication result is encoded in the voltage difference  $(V_{RBLR}-V_{RBLL})$ as shown in the table in Fig. 2(d). The layout of the dual 9T bitcell occupies 3.6  $\mu m \times 1.9 \mu m$ . To ensure a fair comparison, we normalize the bitcell size in Tab. I, taking into account the precision of inputs and weights as well as the process node. After size normalization, our bitcell demonstrates comparative advantages in normalized size, data type support, and DR of  $V_{RBL}$  as shown in Tab. I.

Accumulation occurs due to all bitcells in a column simultaneously discharging the bitline capacitor  $C_{BL}$ . The MAC value is directly proportional to the voltage drop induced by the capacitor discharge process as described in the formula:

$$V_{MAC} = V_{RBLR} - V_{RBLL} = \frac{TI_u}{C_{BL}} \sum_{i=0}^{n_{row}-1} \mathrm{In}_i \, W_i \quad , \quad \text{where} \quad T \text{ and } I_u \text{ are the clock period and the unit discharge current}$$

of a single bitcell.

Fig. 2. Hardware block diagram: (a) Macro architecture in the test chip (BUF: buffer). (b) Circuit timing diagram of one column (PCH: precharge). (c) Voltage waveforms diagrams of RBL and outputs of SA based on post-layout simulation. (d) In-memory ternary multiplication of proposed dual 9T SRAM bitcell.

TABLE I

COMPARISON OF DIFFERENT SRAM BITCELLS FOR ACIM

(TCASI'25 [13], JSSC'22 [9], JSSC'23 [39])

|                                   | This work          | TCASI'25              | JSSC'22               | JSSC'23      |  |

|-----------------------------------|--------------------|-----------------------|-----------------------|--------------|--|

| SRAM cell                         | Dual 9T            | Dual 10T              | 8T                    | 9T1C         |  |

| Cell size (µm²)                   | 6.84/65 nm         | 7.22/65 nm            | 7.22/65 nm 3.24/65 nm |              |  |

| Weight Type                       | Ternary(2b) 69     | Ternary(2b)           | Binary (1b)           | Binary (1b)  |  |

| Input Type                        | Ternary(2b) 69     | Ternary(2b)           | Binary (1b)           | Unsigned(2b) |  |

| Norm. cell size*<br>(65 nm, µm²)  | 1.71 small 6       | 1.81 moderate         | 3.24 large 😕          | 2.2 moderate |  |

| Dyn. range<br>of V <sub>RBL</sub> | large 😺<br>( RUDC) | moderate<br>(Cascode) | small                 | small        |  |

<sup>\*</sup>Norm. cell size=Cell size/input precision/weight precision/AR (AR=(65/Technology)2)

# C. Dual-supply for Implementation of Multi-bit Weight

We employ dual-supply 6T-SRAM array denoted as ( $V_{\rm MSB}$ ) for the Most Significant Bit (MSB,  $W_{i-b2}$ ) and  $V_{\rm LSB}$  for the Least Significant Bit (LSB,  $W_{i-b1}$ ) to facilitate the mapping of the MSB and LSB of weights to two discharge current  $I_{MSB}$  and  $I_{LSB}$  ( $I_{MSB} = n_{BWR}I_{LSB}$ ), where  $n_{BWR}$  denotes the bit weighting ratio (BWR) and is selected according to the desired weight resolution. Fig. 3(b) shows a case for 3-bit

TABLE II Configuration settings for 3-bit and 5-bit weight in the proposed approach (1-bit input)

|                                               | 3-bit weight | 5-bit weight |

|-----------------------------------------------|--------------|--------------|

| Bitcell number                                | 2            | 4            |

| Latency (clk number)                          | 1            | 2            |

| $n_{BWR} (I_{MSB}/I_{LSB})$                   | 2            | 4            |

| $\Delta VDD_{CORE} (V_{MSB} - V_{LSB}) $ (mV) | 30           | 60           |

weights and  $n_{BWR}=2$  where the weight is represented as 2 bits, excluding the sign bit ( $W_i:W_{i\_b2}W_{i\_b1}$ ). The MAC and calibration arrays of the 6T-SRAM bitcells consists of 160 rows, which are evenly divided into two arrays: the upper 80 rows are powered by  $V_{\rm MSB}$  for MSB weights, while the lower 80 rows are powered by  $V_{\rm LSB}$  for LSB weights.

For subthreshold MOSFETs  $(M_{MSB}, M_{LSB})$  in Fig. 3(b)), the 2:1 ratio  $(I_{MSB}/I_{LSB})$ , i.e.  $n_{BWR}=2$  requires  $\Delta VDD_{CORE}=V_{MSB}-V_{LSB}=\frac{U_T}{\kappa}\ln 2\approx 26$  mV, where  $U_T$  is thermal voltage (26 mV @300 K,  $\kappa\approx 0.7$  is the inverse of sub-threshold slope factor). Utilizing this voltage difference and the fixed  $(V_{LSB}=0.42~{\rm V})$ , we can readily determine the appropriate  $V_{MSB}$ . To estimate the effect of mismatch, we performed two Monte Carlo simulations for the

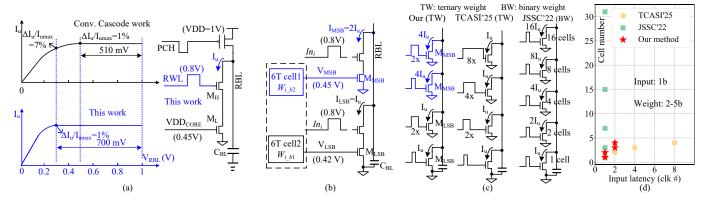

Fig. 3. (a) RUDC for enhanced linearity and DR. (b) Implementation of multi-bit weight using dual-supply for 6T-SRAM array. (c) Three methods (proposed, TCASI'25 [13], JSSC'22 [9]) for implementing 5-bit signed weight. (d) Comparison of input latency and cell number for implementing multi-bit weight.

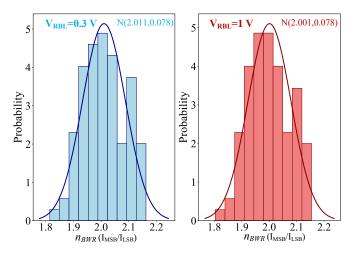

Fig. 4. Monte Carlo simulations for the ratio  $n_{BWR}=2$  under the conditions of  $V_{MSB}=0.45~{

m V}$  and  $V_{LSB}=0.42~{

m V}$ .

TABLE III WEIGHT VALUE STORED PER BITCELL (FOR 5-BIT WEIGHTS) IN THE PROPOSED APPROACH

| Signed 5-bit weight | Weight values of bitcells in different rows |          |          |          |  |

|---------------------|---------------------------------------------|----------|----------|----------|--|

|                     | Bitcell0                                    | Bitcell1 | Bitcell2 | Bitcell3 |  |

| 11111 (-15)         | -1                                          | -1       | -1       | -1       |  |

| 11110 (-14)         | -1                                          | -1       | -1       | 0        |  |

| 00000 (0)           | 0                                           | 0        | 0        | 0        |  |

| 01111 (+15)         | 1                                           | 1        | 1        | 1        |  |

ratio  $n_{BWR}=2$  under the conditions of  $V_{MSB}=0.45~{\rm V}$  and  $V_{LSB}=0.42~{\rm V}$  with  $V_{RBL}=0.3~{\rm V}$ , 1 V respectively. The results in Fig. 4 show that the mean and standard deviation of  $n_{BWR}$  change very little as  $V_{RBL}$  varies. The  $n_{BWR}$  follows a normal distribution N(2.011, 0.078) ( $V_{RBL}=0.3~{\rm V}$ ) with the variation seen to degrade classification accuracy by only 0.21%. We also experimentally verified that these two voltage values ( $V_{MSB}=0.45~{\rm V}$ ,  $V_{LSB}=0.42~{\rm V}$ ) enable the MAC values of the MSB and LSB arrays to be approximately doubled when the weights and input values of both arrays are identical. More accurate ratios can be obtained by calibration as described in Section III-C.

Fig. 3(c) shows three methods for implementing 5-bit weight ( $n_{BWR}=4$  in this case) using PWM input and

multi-cell. While PWM methods incur penalties in latency, multi-cell methods incur penalties in area. Tab. II shows the different settings of MSB and LSB bitcell power supplies for these two cases (3-bit/5-bit weight). To clearly illustrate how our four bitcells achieve the representation of a 5-bit weight, several examples of signed 5-bit weights are presented in Tab. III, which shows the distinct ternary weight values stored in the four bitcells according to different numerical values of the 5-bit weight. Fig. 3(d) compares the number of bitcells and the latency required to achieve 2 to 5 bits of weight with those reported in the previous two articles [9], [13]. Dual-supply for 6T-SRAM array are leveraged for multi-bit weights, achieving reductions in cell number/area by 7.8×/3.7× compared to [9] and latency by 4× compared to [13], respectively, when implementing 5-bit weights.

Another method for implementing multi-bit weights using binary capacitors was proposed in references [38], [41]. However, this approach presents issues of large area occupied by capacitors (e.g. [38] uses  $\approx 17\%$  of bitcell array), limited resolution and limited configurability. In comparison to these methods, despite requiring an additional power supply, our design offers key advantages over these methods by eliminating the need for large capacitors and enabling flexible configuration of the supported weight bit-width. Since the power drawn by this supply is less than 3  $\mu\mathrm{W}$ , we estimate a simple reference generator with buffer will suffice to provide this adding negligible overheads in power and area. Note that our dual-supply approach is applicable to other bitcell designs as well. If signed inputs are not necessary, we can use foundry supplied 8T cells with smaller footprint.

# D. RWL Underdrive enabled Cascode for enhanced DR and Linearity

Word line underdrive is typically used in SRAM for improving static noise margin. In this work, we achieve high linearity of  $I_u$  and large DR of  $V_{RBL}$  by RUDC technique—the supply voltages for RWL is set to  $V_{RWL}=0.8$  V, while  $V_{RBL}$  precharging voltage is set at VDD=1 V and gate voltage of  $M_L$  is at  $VDD_{core}=0.45$  V as shown in Fig. 3(a). The minimum RBL voltage for which  $M_H$  acts as a Cascode is given by  $V_{min}=V_{RWL}-V_{T1}$  where  $V_{T1}$  denotes the threshold voltage

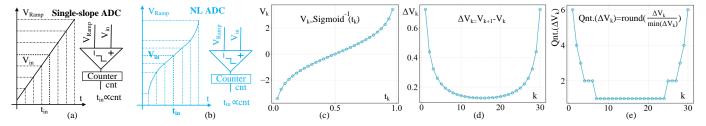

Fig. 5. (a) Traditional single-slope ADC. (b) Our Ramp NL ADC. (c) The inverse of the sigmoid function. (d) The value of each step of the ramp voltage  $V_k$  denoted by  $\Delta V_k$ . (e) Integer quantized  $\Delta V_k$  for implementation in hardware.

of  $M_H$ . Lower  $V_{RWL}$  leads to higher  $V_{RBL}$  swing and the lowest RWL voltage is limited by the requirement to keep the lower NMOS  $M_L$  in saturation. We obtain DR of 700 mV on the RBL for a 1% variation in  $I_u$  (Fig. 3(a))–7× reduction than the variation observed in  $I_u$  over the same range for the conventional case. For a 1% current variation, the conventional Cascode method achieves a DR of only  $\approx 510$  mV, while our method reaches  $\approx 700$  mV, necessitating a DR reduction by a factor of 1.4× (700/510) for the conventional approach to limit current variations to the same level. Single transistor (in 8T bitcell) based discharge paths have an even smaller DR of  $\approx 250$  mV [9]. Our DR (700 mV) and voltage signal margin (DR/column~#, 3.68 mV) is 2.8×/1.9× higher than the values of single transistor architecture (8T bitcell in [9], DR = 250 mV, voltage signal margin =1.95 mV).

#### III. NONLINEAR IN-MEMORY ADC

#### A. Implementation of NLIM ADC in Hardware

A traditional single-slope ADC is shown in Fig. 5(a). Its output is produced by a comparator whose negative input is connected to a time-varying ramp signal,  $V_{Ramp}(t) = \frac{1}{k}t$ , and the positive input is connected to  $V_{in}$ , where f(t) = kt is linear. The threshold crossing time of comparator  $t_{in}$  ( $t_{in} = kV_{in} = f(V_{in})$ ) can be obtained using a counter in Fig. 5(a).  $t_{in}$  is the output of activations, which is proportional to the counter value. Compare above two equations, we can conclude  $V_{Ramp}(t) = f^{-1}(t)$ .

For Ramp NL ADC depicted in Fig. 5(b), the principle is exactly the same as that of the linear one with the only difference that  $V_{Ramp}(t) = f^{-1}(t)$  is a NL curve rather than a line.  $t_{in}$  still equals  $f(V_{in})$  when  $V_{Ramp}(t) = V_{in}$ , where f() is NL activation, such as sigmoid, tanh. Take the sigmoid function  $(f(t) = 1/(1+e^{-t}))$  and n-bit NLIM ADC as an example. To extract the step of the generated ramp voltages, we first obtain the inverse of the sigmoid function  $(f^{-1}(t) = \ln \frac{t}{1-t})$  as depicted in Fig. 5(c). This function is exactly the  $V_{Ramp}$  that needs to be generated during the conversion process. The methodology for generating the NL curve of  $V_{Ramp}$  using NLIM ADC is presented in the following text (5 steps).

- 1)  $2^n 1$  equidistant sample points  $(t_k, V_k)$  are extracted from the inverse sigmoid characteristic curve shown in Fig. 5(c) (here n=5).

- 2) The voltage differences  $\Delta V_k = V_{k+1} V_k$  are computed and plotted in Fig. 5(d).

- 3) Each  $\Delta V_k$  is quantized using the relation  $Qnt.(\Delta V_k) = round(\frac{\Delta V_k}{min(\Delta V_k)})$ , where  $min(\Delta V_k)$  represents the minimum voltage difference. The resulting quantized values are shown in Fig. 5(e).

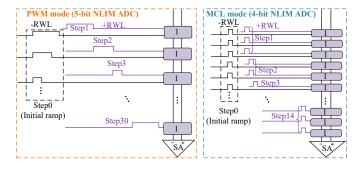

- 4) Our NLIM ADC generates ramp voltage  $V_{Ramp}$  with step size:  $\Delta V_{Ramp}^k = \frac{I_u T}{C_{BL}} Qnt.(\Delta V_k)$ . Two operating modes are implemented (Fig. 6): 1) PWM Mode: single bitcell per step, where pulse width  $T_{PWM} = Qnt.(\Delta V_k)T$  controls  $\Delta V_{Ramp}^k$ ; 2) Multi-Cell (MCL) Mode: multi-bitcells  $(n_{cell} = Qnt.(\Delta V_k))$  activated per step controlling  $\Delta V_{Ramp}^k$ , each step for one clock cycle. Tab. IV presents a comparison of the two NLIM ADC operating modes (5-bit and 4-bit resolutions) in terms of latency and bitcell number.

- 5) The ramp voltage generated at the p-th clock cycle  $(V_{Ramp}^p)$  is given by the following equation.

$V_{Ramp}^{p} = V_{initcalib} + \sum_{k=1}^{p} \Delta V_{Ramp}^{k}$   $= -\frac{I_u T}{2C_{BL}} \sum_{k=1}^{2^n-2} Qnt.(\Delta V_k) + \frac{I_u T}{C_{BL}} \sum_{k=1}^{p} Qnt.(\Delta V_k) \quad (3)$ where  $V_{initcalib}$  is the initial voltage of  $V_{Ramp}$  as shown in Fig. 2(c), which can be efficiently generated using only  $2^{n-1} - 1$  bitcells (15 for the 5-bit case depicted) with identical pulse width as the first 15 bitcells of NLIM ADC as depicted in Fig. 6 (PWM mode). In this configuration, all 15 -RWL signals are activated simultaneously, causing RBLR (in Fig. 2(c)) to discharge and generate the  $V_{initcalib}$ . Then, +RWL signals are enabled sequentially in a step-by-step fashion, allowing the RBLL to discharge producing an increasing voltage difference between the two RBLs named  $V_{Ramp}$  in Fig. 2(c).

As derived from Equation (3), our architecture can generate NL characteristic curves of varying shapes by programming different voltage values, approximating various activations. The NLIM ADC design maintains full flexibility to operate in linear mode (where all  $Qnt.(\Delta V_k)$  values are identical) when needed. The implementation utilizes 30 rows of bitcells, supporting ADC resolutions configurable from 1 to 5 bits.

Tab. V presents a comprehensive comparison between our NLIM ADC and state-of-the-art ADC implementations [9], [39], [1]. To ensure a fair comparison of area efficiency across different MAC array sizes, ADC resolutions, and technology nodes, we normalized the area of all ADCs. The total area of each ADC design is first divided by the number of columns in the MAC array to represent the area per column. This per-column ADC area is then normalized to an equivalent 5-bit resolution in a 65 nm technology node using the scaling formula provided in Tab. V.

For a comprehensive comparison, we also include the area of the NL control logic. In our design, the total area of the

Fig. 6. PWM mode and multi-cell mode for implementation of NLIM ADC.

TABLE IV

COMPARISON OF DIFFERENT MODES AND RESOLUTIONS.

| Resolution of NLIM ADC (mode) | 5-bit<br>(PWM ) | 5-bit<br>(MCL) | 4-bit<br>(PWM) | 4-bit<br>(MCL) |

|-------------------------------|-----------------|----------------|----------------|----------------|

| Cell number                   | 30              | 56             | 14             | 20             |

| Latency (clock # )            | 56              | 30             | 20             | 14             |

TABLE V COMPARISON OF RECENT ADC IN ACIM

|                                       | This work | JSSC'23 [39] | JSSC'22 [9] | JSSC'23 [1] |  |

|---------------------------------------|-----------|--------------|-------------|-------------|--|

| ADC type                              | Ramp(IM)  | SAR          | Ramp(IM)    | Flash       |  |

| Technology                            | 65 nm     | 28 nm        | 65 nm       | 28 nm       |  |

| Resolution                            | 1-5b      | 6b           | 1-5b        | 4b          |  |

| Linearity                             | Linear/NL | Linear       | Linear      | Linear      |  |

| Neuro #/ADC                           | 1         | 4            | 1           | 16          |  |

| MAC array size                        | 160×100   | 128×128      | 64×128      | 256×80      |  |

| Total ADC area $(A_{ADC}, \mu m^2)$   | 25650     | 6704.2       | 32995       | 7030.8      |  |

| One ADC area (Norm.)* ( $\mu m^2$ )   | 256.5     | 141.1        | 257.8       | 947.2       |  |

| NL area<br>(Norm.) (μm <sup>2</sup> ) | 26.8      | 783.4        | 783.4       | 783.4       |  |

| One ADC+ NL area (Norm.) $(\mu m^2)$  | 283.3     | 924.5        | 1041.2      | 1730.6      |  |

<sup>\*</sup> One ADC area (Norm.)= $A_{ADC}/n_{col}/2^{n-5}xAR$ . ( $n_{col}$  is column # of MAC array. n is maximum resolution of ADC. AR=(65/Technology)<sup>2</sup>.

NL controller is divided by the number of columns, as a single controller is shared across all columns. For other linear ADCs, we add the area of one NL processor (783.4  $\mu m^2$  in 65 nm based on [42]).

Finally, we compared the combined normalized area of one ADC plus the corresponding NL unit. As shown in Tab. V, the total normalized one ADC area plus NL area of our design is 3.3× better than that of the most area-efficient prior work [39] and 3.7× better than that of the linear in-memory ADC in [9].

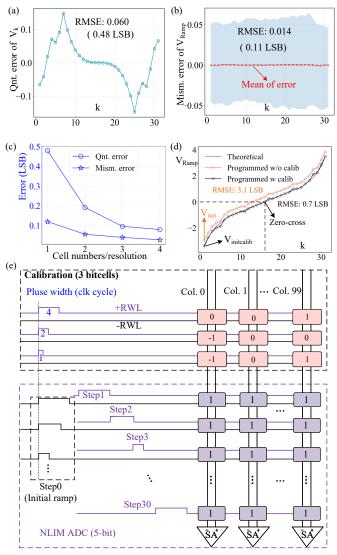

#### B. Error Analysis and Calibration within Hardware

The generation of  $V_{Ramp}$  requires quantization of  $\Delta V_k$  as defined in Equation (3), which introduces quantization error. As shown in Fig. 7(a), the quantization error of  $\Delta V_k$  leads to an root-mean-square error (RMSE) of 0.060 (0.48 LSB) generated in  $V_k$  for the 5-bit NLIM ADC when approximating a sigmoid function. The specific shape of the quantization error curve depends on the function being approximated, but we found the error to be < 1 LSB for all common NL activations. Our analysis of Equation (3) further reveals that statistical variations among bitcells producing  $I_u$  contribute

Fig. 7. Quantization of  $V_k$  and mismatch errors of  $V_{Ramp}$  are shown in (a) and (b). (c) Errors with different resolutions. (d) Zero-cross method for calibration. (e) Detailed timing diagram of calibration.

to an additional error named mismatch error. To characterize the mismatch error, we conducted extensive Monte Carlo simulation and developed comprehensive variation model for  $I_u$ , and then incorporated this model into Equation (3) to generate  $V_{Ramp}$  with  $I_u$  mismatch. We perform 1,000 simulation runs to statistically quantify the distribution of mismatch error (Fig. 7(b)). As demonstrated in Fig. 7(c), both quantization error and mismatch error exhibit an inverse relationship with the number of cells per resolution with quantization error being dominant.

The generated  $V_{Ramp}$  deviates from its ideal characteristic due to aforementioned errors. To mitigate this, a zero-crossing calibration technique is employed to adjust the initial voltage  $V_{init}$ , as illustrated in Fig. 7(d). The calibration process for the 5-bit ADC (PWM mode) is detailed in Fig. 7(e), where the initial ramp, calibration, and MAC operations occur simultaneously.

A negative  $V_{init}$  is established by simultaneously enabling 15 -RWL pulses in Fig. 7(e), leveraging the positive weights

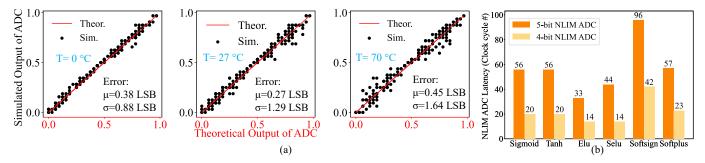

Fig. 8. (a) Robustness of our 5-bit NLIM ADC implementing sigmoid function under different temperatures (2-bit weight). (b) Total latency of NLIM ADC for different NL activations.

to generate a negative initial voltage. This enables the ADC to measure both positive and negative MAC values. Subsequently, 30 +RWL pulses are applied sequentially, producing a rising  $V_{Ramp}$  (orange line, "Programmed w/o calib" in Fig. 7(d)). However, the IM ADC in [12] is constrained by its binary input format (only one RWL in every column). To generate  $V_{init}$ , it must employ a separate array of 15 bitcells. Consequently, this method suffers from a large area overhead, with the  $V_{init}$  generation circuit consuming an area comparable to the ADC core itself (IM ADC area/initial ramp area $\approx$ 50% [12]), making the cost prohibitively high.

Calibration utilizes three rows of bitcells with input pulses of 1, 2, and 4 cycles, respectively. Weights in calibration rows are determined experimentally. With MAC and calibration pulses disabled, the ADC output is read at MAC=0. Any deviation from zero indicates a  $V_{Ramp}$  offset. For instance, an output of 3 in the first column signifies an upward shift. To realign  $V_{Ramp}$  through zero, the corresponding calibration weights are set to (0, -1, -1), shifting  $V_{init}$  downward by three resolution steps to  $V_{initcalib}$  in Fig. 7(d).

This calibration method, applied to determine all weights across the three rows, reduces the RMSE by a factor of 4.4 (from 3.1 LSB to 0.7 LSB in Fig. 7(d)). It is worth noting that for the 5-bit ADC, we require three additional rows for calibration, leaving 157 rows of bitcells available for MAC computation. However, for a 4-bit ADC, the 10 remaining bitcells can be used for calibration, after 20 are allocated to the ADC module itself as shown in Tab. IV. In this case, all 160 rows of bitcells can be used for MAC computation.

#### C. Robustness to temperature and Weight Calibration

Fig. 8(a) shows the distribution of the 5-bit NLIM ADC output implementing a sigmoid function compared to theoretical output values using data from GSCD with 2-bit weight quantization for LSTM weights for 0°C, 27°C and 70°C. It can be observed that the error remains consistently small in Fig. 8(a)) demonstrating the robustness of the NLIM ADC architecture against temperature fluctuations due to replica bias (the bitcells in NLIM ADC section used to generate the NLIM ADC references are identical to those in MAC section). When this maximum error distribution (N(0.45 LSB, 1.64 LSB) at 70°C) is added to the LSTM network, the simulated accuracy drops by only 1.1% (from 91.2% to 90.1%).

The  $\Delta VDD_{CORE}$  in Section II-C exhibits positive temperature dependence due to  $U_T$ . To maintain bit weighting ratio  $n_{BWR} = I_{MSB}/I_{LSB} \approx 2$  for our 3-bit LSTM network, we implement a temperature-proportional current  $(I_{PTAT})$ -based voltage generator [43], [44]. Using  $I_{PTAT}$  to create  $V_{MSB} = V_{LSB} + I_{PTAT}R$  (with fixed  $V_{LSB} = 0.42V$  and R). This design maintains a nearly constant  $n_{BWR} = e^{\kappa R} \frac{I_{PTAT}}{U_T}$  across temperature variations, since both the  $I_{PTAT}$  and  $U_T$  increase proportionally with temperature. SPICE simulation shows  $n_{BWR}$  remains within 1.99-2.02 across 0-70°C. The worst case  $n_{BWR}$  results in merely 0.15% inference accuracy degradation for 3-bit weight LSTM network.

In case a more precise ratio is necessary, we can do a simple calibration routine to make small adjustments to the  $\Delta VDD_{CORE}$ . Calibration can be performed by making the resistance, R, in the reference generator programmable (can be a combination of fixed and digitally tunable R). For calibration, the same set of inputs are applied to the array twice, while keeping the weights in the MSB and LSB array as  $(W_{MSB}, W_{LSB})$ =(0,  $W_{cal}$ ) and  $(W_{cal}, 0)$  respectively, where  $W_{cal}$  denotes a set of random weights used for calibration. The ADC is configured as a linear one and the measured outputs for the two cases can be used to extract an accurate estimate of the actual  $n_{BWR}$  on-chip. Next, binary search can be used to find the ideal resistor value to tune this ratio close to the desired one (=2 for 3, 4-bit weight, =4 for 5-bit weight).

#### D. Latency analysis

Our NLIM ADC can approximate different NL activations. The latency of 5-bit and 4-bit NLIM ADC with PWM mode for different NL activations is shown in Fig. 8(b), obtained according to the equation  $\sum_{k=1}^{30} Qnt.(\Delta V_k)$ .

#### IV. MEASUREMENT AND SIMULATION RESULTS

A  $0.92 \times 0.92$  mm<sup>2</sup> chip containing the macro was fabricated in a 65 nm CMOS process occupying a core area of 0.23 mm<sup>2</sup>.

#### A. Programmed In-memory Nonlinear ADC Results

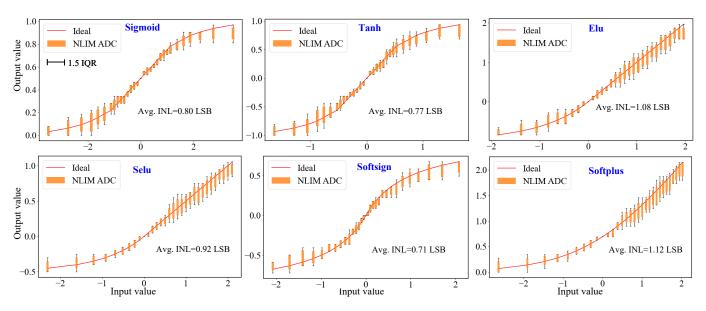

We experimentally programmed six common neural network NL activations (Sigmoid, Tanh, Elu, Selu, Softsign and Softplus) in our chip (100 columns) using 5-bit NLIM ADC with calibration, as shown in Fig. 9. The average integral nonlinearity (INL) for approximating these six NL activations are

Fig. 9. Experimental results of approximating six NL activations at 5-bit resolution. (Avg. INL =  $\sum_{col=1}^{100} [(\sum_{i=1}^{31} | Ideal_{col,i} - NLIMADC_{col,i} | )/31)]/100)$

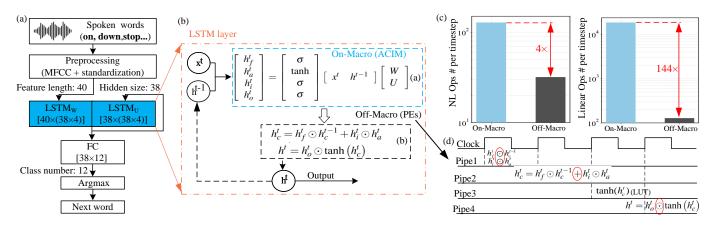

Fig. 10. (a) Architecture of LSTM network on-chip inference. (b) Mapping of the LSTM network onto the Macro of chip. (c) Operations breakdown in the LSTM layer of one timestep. 80% nonlinear operations and 99% linear operations can be done on-macro. (d) Pipe-lined timing diagram for PEs (off-macro).

0.80 LSB, 0.77 LSB, 1.08 LSB, 0.92 LSB, 0.71 LSB and 1.12 LSB, respectively.

## B. LSTM for KWS Task

The GSCD dataset [45] is used to train and test for the 12-class KWS task. The KWS training network includes Mel-frequency cepstral coefficient (MFCC) for feature extraction, standardization, LSTM layer and fully connected (FC) layer. Quantization and hardware nonidealities aware training (HWAT) [46], [47], [48] is employed to enhance the resilience of weights against quantization error and hardware nonidealities so that the network can be tested on-chip with less loss of accuracy. Our LSTM network can achieve better performance, even when employing low-bit quantization (2 or 3 bits) for weights using the quantization method as introduced in [46]. After 2-bit and 3-bit quantization, 60% and 67% of the weights in the macro are zero, respectively. These zero-valued weights, as illustrated in Fig. 2(d) (middle), create no

discharge paths within the bitcell, thereby reducing the energy consumed by RBL discharge.

On-chip inference depicted in Fig. 10(a) is performed after training. After feature extraction and standardization (both procedures are implemented off-chip), These extracted features, along with the previous 38-dimensional output vector  $h^{t-1}$ from the LSTM, are then sent to the Macro in the chip. Fig. 10(b) illustrates the division of operations within the LSTM layer, specifying which components are executed within the Macro of our chip and which are processed externally. The parameters (W and U) and NL activations (sigmoid ( $\sigma$ ) and tanh) in Equation (a) in Fig. 10(b) are programmed in the 6T-SRAM array of ACIM while  $h^{t-1}$  and  $x^t$  are converted into PWM pulses in Macro as the input of ACIM. While the Macro does not support the full set of LSTM operations for this model, it efficiently handles 80% of NL operations and 99% of linear (MAC) operations in the LSTM layer as shown in Fig. 10(c). For the computations in Equation (b) in Fig. 10(b), we implement a pipelined digital circuit composed of processing

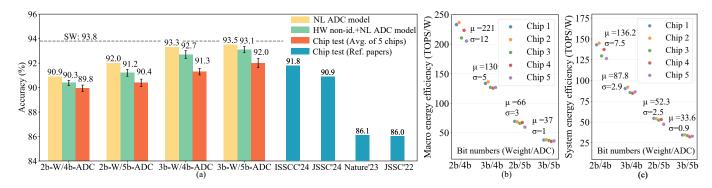

Fig. 11. (a) Comparison of the our inference accuracy results with the state-of-the-art results of 12 classes (ISSCC'24 [40], JSSC'23 [49], Nature'23 [19], ISSCC'22 [50]). (b) Macro energy efficiency (including nonlinear operations) of five chips under different resolutions @ 100 MHz 0.45V, 0.8V, 1V for 2-bit weight  $(VDD_{core} = 0.45V, \Delta VDD_{core} = 0.03 V, V_{RWL} = 0.8V, VDD = 1V$  for 3-bit weight). (c) System energy efficiency (including LSTM and FC layers).

elements (PEs), achieving a latency of 4 clock cycles per data set as shown in Fig. 10(d). The system employs 19 parallel PEs, with each PE processing 2 out of the total 38 dimensions of the hidden state, resulting in an overall latency of 5 cycles. Using TSMC 65 nm standard digital cells for synthesis, we estimate a total power consumption of this part as 32  $\mu W$  at 100 MHz, 1 V.

Inference accuracy results in software for 12-class KWS is shown in Fig. 11(a). After adding the NLIM ADC model to replace the NL functions in the LSTM layer, inference accuracies for the four configurations—employing 2-bit and 3-bit weights with 4-bit and 5-bit NLIM ADC—are 90.9%, 92.0%, 93.3% and 93.5%, respectively, which compare favorably with a floating-point baseline of 93.8%. To improve the robustness of the neural network against hardware nonideality when mapping weights to the chip, we incorporated a simple hardware nonideality model N(0,0.05) (obtained from actual chip measurements similar to Fig. 8(a)) to the output of NLIM ADC during the training process. Consequently, the software-based inference accuracies change to 90.3%, 91.2%, 92.7% and 93.1%, respectively. The robustness of the classification was verified through 10 independent experimental runs, resulting in a small standard deviation (Fig. 11(a)). Next, we experimentally evaluated the on-chip inference accuracy variations of five chips across four different configurations, observing mean accuracy drop within ≈1% margin of the hardware nonidealities calibrated NLIM ADC software model and low variability across five chips. As shown in Fig. 11(a), the averaged on-chip inference accuracy values (with error bars of five chips) under these four configurations are 89.8%, 90.4%, 91.3% and 92.0%, respectively. Our averaged on-chip inference accuracy is 92.0% for 5-bit ADC and 3-bit weight, demonstrating competitive performance with the state-of-theart result of 91.8% [40].

The maximum accuracy drop in Fig. 11(a) between the model (accounting for hardware nonidealities and ADC model) and the actual hardware is 1.4%, decreasing from 92.7% (green bar) to 91.3% (orange bar) at 3-bit weight and 4-bit ADC. The primary reason for this accuracy drop is the simple non-ideality model we have used during training which added noise from a fixed error distribution obtained after

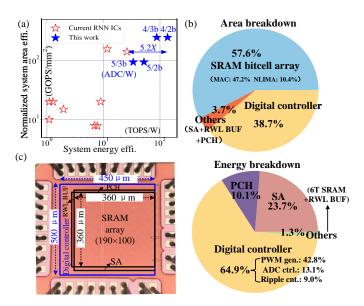

Fig. 12. (a) Comparison of our work with other RNN ICs. (b) Chip area and measured energy breakdowns (c) Die photograph of total active area  $0.23 \text{ mm}^2$

testing a fixed set of input data. In reality, the approximation error of the NL activation varies with different input data (note different variability in the different points of Fig. 9). In future, we will explore adding more detailed non-ideality model of the ADC as well as mismatch induced variations of  $n_{BWR}$  to have a better model of hardware nonidealities aware training.

# C. Hardware Performance

Fig. 11(b) presents the measured macro-level EE (including NL operations) of our design for the aforementioned four configurations, ranging from 37 TOPS/W to 221 TOPS/W. The measured fluctuation of macro EE remains within 10%. Following the evaluation methodology (pipe-lined architecture) described in Section IV-B, we estimate the latency, power consumption, and area of the FC layer. The resulting system-level EE and area efficiency for inference are [33.6, 52.3, 87.8, 136.2] TOPS/W as shown in Fig. 11(c) and [93.7, 93.7, 245, 245] GOPS/mm² under above four configurations, respectively. As shown in Fig. 12(a), when comparing our

| Metric                                       | VLSI'19 [28] | JSSC'20 <sup>[27]</sup> | VLSI'21 [26] | JSSC'21 [25] | Nat. Elec.'23 [24]    | Nature'23 [19]        | JSSC'23 [23] | This work             |

|----------------------------------------------|--------------|-------------------------|--------------|--------------|-----------------------|-----------------------|--------------|-----------------------|

| CMOS technology                              | 65 nm        | 65 nm                   | 65 nm        | 65 nm        | 14 nm                 | 14 nm                 | 16 nm        | 65 nm                 |

| Supply voltage(V)                            | 0.9          | 0.68                    | 0.75         | 0.7, 1       | 0.85-0.95             | 0.8-1.8               | 0.8          | 0.42/0.45, 0.8, 1     |

| Memory technology                            | SRAM         | SRAM                    | SRAM         | SRAM         | PCM                   | PCM                   | SRAM         | SRAM                  |

| Bitcell                                      | 6T           | _                       | 6T           | 6T           | 8T4R                  | 6T4R                  | -            | Dual 9T               |

| Frequency (MHz)                              | 75           | 80                      | 160          | 500          | 1000                  | 1000                  | 573          | 100                   |

| In./w./out. precision                        | 1/1/3        | 13/6/13                 | -/2/2        | 8/8/8        | 8/Analog/8            | 8/Analog/8            | 8/8/8        | 4-5/2-3/4-5           |

| CIM inclluding NL                            | N            | N                       | N            | N            | N                     | N                     | N            | Y                     |

| Algorithm                                    | RNN          | LSTM                    | LSTM         | RNN          | LSTM                  | LSTM                  | RNN          | LSTM                  |

| Dataset                                      | GSCD         | TIMIT                   | GSCD         | GSCD         | PTB                   | GSCD                  | LibriSpeech  | GSCD                  |

| Acc.(%)/class num.                           | 90.2/10      | -/-                     | -/-          | 90.38/7      | _/_                   | 86.1/12               | _/_          | 89.8 (4/2/4b)/12      |

| Acc. (10)/class hum.                         | 70.2/10      | _/_                     |              | 70.36/7      | 7-                    | 00.1/12               | -/-          | 92.0 (5/3/5b)/12      |

| Power (mW)                                   | 52.51        | 1.85                    | 46.90        | _            | 3450                  | 3317                  | 214          | 0.41 (4/2/4b)         |

| ` '                                          | 32.31        | 1.05                    | 10.50        |              | 3130                  | 3317                  | 211          | 0.63 (5/3/5b)         |

| Sys. energy                                  | 11.7         | 8.93 <sup>(b)</sup>     | 26.03        | 0.91         | 1.96                  | 6.94                  | 7.8          | 136.2 (4/2/4b)        |

| effi. (TOPS/W)                               |              |                         |              | ***          |                       | ***                   |              | 33.6 (5/3/5b)         |

| Norm. sys. energy                            | 11.7         | 696.5 <sup>(b)</sup>    | 104.12       | 58.24        | 125.44 <sup>(d)</sup> | 444.16 <sup>(d)</sup> | 499.2        | 1089.6 <sup>(e)</sup> |

| effi. (TOPS/W) <sup>(c)</sup>                |              |                         |              |              |                       |                       |              |                       |

| Sys. area effi.                              | 156          | 20                      | 228          | _            | 320                   | 170                   | 130          | 245 (4/2/4b)          |

| (GOPS/mm <sup>2</sup> )                      | 150          | 20                      | 220          |              | 320                   | 170                   | 150          | 93.7 (5/3/5b)         |

| Norm. sys. area                              | 156          | 20                      | 228          | _            | 14.9                  | 7.9                   | 7.8          | 245 (4/2/4b)          |

| effi. (GOPS/mm <sup>2</sup> ) <sup>(a)</sup> | 150          | 20                      | 220          | _            | 17.7                  | 1.2                   | 7.0          | 93.7 (5/3/5b)         |

TABLE VI

PERFORMANCE COMPARISON OF RNN ACCELERATORS WITH STATE-OF-THE-ARTS

(a) Normalized system area efficiency= system area efficiency × (process/65 nm)<sup>2</sup>; (b) FC layer is not included; (c) All energy efficiencies are normalized to 1-bit input and 1-bit weight, according to this formula [18]: Normalized EE=EE × input precision × weight precision; (d) The analog weights are normalized using 8 bits. (e) The data is normalized from 4/2/4b resolutions.

LSTM accelerator with current RNN accelerators [19]–[28], our design achieves 5.2× higher system-level EE and 1.6× better normalized (65 nm) area efficiency than SOTA solutions [26], [28] when operating at 2/4 bits (bit numbers: weight/NLIM ADC).

Fig. 12(b) displays the detailed area and energy breakdowns at supply voltages of  $VDD_{core} = 0.45V$ ,  $\Delta VDD_{core} =$ 0.03 V,  $V_{RWL}$  =0.8V, VDD =1V and 100 MHz clock frequency at 3/5 bits. The NLIM ADC (bitcell+SA) module occupies only 11% of the total area. The measured energy breakdown reveals that the digital controller dominates power consumption (64.9%), while the NLIM ADC module accounts for approximately 36.8% of total energy. Fig. 12(c) presents the die micrograph with total active area 0.23 mm<sup>2</sup>. Tab. VI provides a comprehensive performance comparison between our LSTM accelerator and SOTA RNN accelerators, highlighting improvements in configuration flexibility (4-5/2-3/4-5b, input/weight/output), accuracy of KWS, energy/area efficiency, and CIM including NL. For a fair comparison, all energy efficiency values are normalized to the configuration of 1-bit weight and 1-bit input, following the formula in [18]. Our normalized system energy efficiency (1089.6 TOPS/W, including the FC layer) is 2.2× higher than the SOTA result (499.2) TOPS/W reported in [23]). While we used a relatively older process of 65 nm CMOS, we expect even better performance in terms of leakage power, mismatch and bitcell area when moving to advanced nodes such as 22 nm FDSOI due to the intrinsically better characteristics of the transistor [51].

#### V. CONCLUSION

In this work, we propose the ACIM macro supporting reconfigurable NLIM ADC to approximate NL activations directly in the analog domain. Experimental results show the 5-bit NLIM ADC for approximating NL activations in LSTM cells, achieving < 1 LSB average error with a  $3.3 \times / 3.7 \times$  normalized area reduction over previous SAR ADC and linear IM ADC including NL units. Simulations further demonstrate its temperature robustness enabled by replica bias. Our LSTM accelerator achieves 92.0% on-chip inference accuracy for 12-class KWS task while demonstrating  $2.2 \times$  higher system-level normalized EE and  $1.6 \times$  better normalized area efficiency compared to SOTA designs. A dual 9T bitcell is proposed to support signed inputs and ternary weights, combined with our RUDC technique that increases DR of  $V_{RBL}$  by  $2.8 \times$  versus prior implementation. Dual-supply 6T-SRAM array is employed for multi-bit weight implementation, reducing both bitcell count  $(7.8 \times)$  and latency  $(4 \times)$  for 5-bit weight operations.

# VI. APPENDIX

#### A. Model training

The neural network training consists of three parts: data preprocessing and LSTM layer and fully connected (FC) layer.

During the data preprocessing phase, the GSCD [45] dataset serves as the foundation for model development. This comprehensive dataset comprises 65,000 one-second audio clips, collected from numerous individuals through public contributions. The original audios are consolidated into 12 primary classifications. Each one-second audio segment contains 16,000 discrete sampling points. Mel-Frequency Cepstral Coefficients (MFCC) processing is employed to extract essential vocal characteristics, with 49 analysis windows segmenting each audio recording to derive 40 distinctive features per window.

The LSTM training phase incorporates a customized LSTM layer (78×152=11856 weight parameters) as its central computational element. The network configuration processes input

#### **Algorithm 1** Hardware nonidealities aware training (HWAT)

```

Input: x^t, h^{t-1}, W_t and Nonidealities Output: W_{t+1} loop

Feed forward propagation: Y_{\mathbf{t}} \leftarrow Q([x^t, h^{t-1}] \cdot W_t)

Z_{\mathbf{t}} \leftarrow f(Y_t) + Nonidealities

Back-propagation: g_{\mathbf{t}} \leftarrow \text{calculate gradient based on } W_t \text{ and } f(Y_{\mathbf{t}})

W_{\mathbf{t}+1} \leftarrow W_{\mathbf{t}} + \eta \times g_{\mathbf{t}}

end loop

```

vectors of length 40 while maintaining a hidden state dimension of 38. With a sequence length of 49 and batch size of 1024, each training iteration involves 49 sequential computations within the LSTM architecture. Our LSTM network can achieve better performance, even when employing low-bit quantization (2 or 3 bits) for weights because of quantization-aware training (QAT) [46]. The following Equation (4) is an example for 2-bit weight quantization.

$$W_k = \begin{cases} +1, & \text{if } W_k > 0.7m \\ 0, & \text{if } -0.7m \le |W_k| \le 0.7m \\ -1, & \text{if } W_k < -0.7m. \end{cases}$$

(4)

where the threshold m is the average of the absolute values of all the weights.

Algorithm 1 formalizes the hardware nonidealities aware training (HWAT) [47], [48] process, which employs hardware-based nonidealities sampled from a normal distribution. HWAT is utilized to enhance the resilience of weights against hardware nonidealities so that the network can be tested on-chip with less loss of accuracy.

A FC layer subsequently processes the 38-dimensional feature vectors generated by the LSTM to perform the final 12-class classification. The model is optimized using the Adam optimizer and a cross-entropy loss function.

#### REFERENCES

- K. Lee, J. Kim, and J. Park, "A 28-nm 50.1-TOPS/W P-8T SRAM compute-in-memory macro design with BL charge-sharing-based in-SRAM DAC/ADC operations," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 6, pp. 1926–1937, 2023.

- [2] H. Diao, Y. He, X. Li, C. Tang, W. Jia, J. Yue, H. Luo, J. Song, X. Li, H. Yang et al., "A multiply-less approximate SRAM compute-inmemory macro for neural-network inference," *IEEE Journal of Solid-State Circuits*, 2024.

- [3] P.-C. Wu, W.-S. Khwa, J.-J. Wu, J.-W. Su, C.-J. Jhang, H.-Y. Chen, Z.-E. Ke, T.-C. Chiu, J.-M. Hsu, C.-Y. Cheng et al., "An Integer-Floating-Point Dual-Mode Gain-Cell Computing-in-Memory Macro for Advanced AI Edge Chips," *IEEE Journal of Solid-State Circuits*, 2024.

- [4] Y. Ju, Y. Wei, and J. Gu, "A 65 nm General-Purpose Compute-in-Memory Processor Supporting Both General Programming and Deep Learning Tasks," *IEEE Journal of Solid-State Circuits*, 2024.

- [5] Q. Liu, B. Gao, P. Yao, D. Wu, J. Chen, Y. Pang, W. Zhang, Y. Liao, C.-X. Xue, W.-H. Chen et al., "A fully integrated analog ReRAM based 78.4 TOPS/W compute-in-memory chip with fully parallel MAC computing," in 2020 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2020, pp. 500–502.

- [6] P.-C. Wu, J.-W. Su, Y.-L. Chung, L.-Y. Hong, J.-S. Ren, F.-C. Chang, Y. Wu, H.-Y. Chen, C.-H. Lin, H.-M. Hsiao et al., "An 8b-precision 6T SRAM computing-in-memory macro using time-domain incremental accumulation for AI edge chips," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 7, pp. 2297–2309, 2023.

- [7] Z. Chen, X. Chen, and J. Gu, "a 65nm 3T dynamic analog RAM-based computing-in-memory macro and CNN accelerator with retention enhancement, adaptive analog sparsity and 44TOPS/W system energy efficiency," in 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64. IEEE, 2021, pp. 240–242.

- [8] Y. Chi et al., "An 89 TOPS/W and 16.3 TOPS/mm2 all-digital SRAM-based full-precision compute-in memory macro in 22nm for machine-learning edge applications," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), vol. 64, 2021, pp. 252–254.

- [9] C. Yu, T. Yoo, K. T. C. Chai, T. T.-H. Kim, and B. Kim, "A 65-nm 8T SRAM compute-in-memory macro with column ADCs for processing neural networks," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 11, pp. 3466–3476, 2022.

- [10] X. Si, J.-J. Chen, Y.-N. Tu, W.-H. Huang, J.-H. Wang, Y.-C. Chiu, W.-C. Wei, S.-Y. Wu, X. Sun, R. Liu et al., "A twin-8T SRAM computation-in-memory unit-macro for multibit CNN-based AI edge processors," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 1, pp. 189–202, 2019.

- [11] H. Wang, R. Liu, R. Dorrance, D. Dasalukunte, D. Lake, and B. Carlton, "A charge domain SRAM compute-in-memory macro with C-2C ladder-based 8-bit MAC unit in 22-nm FinFET process for edge inference," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 4, pp. 1037–1050, 2023.

- [12] J. Yue, Z. Yuan, X. Feng, Y. He, Z. Zhang, X. Si, R. Liu, M.-F. Chang, X. Li, H. Yang et al., "14.3 A 65nm computing-in-memory-based CNN processor with 2.9-to-35.8 TOPS/W system energy efficiency using dynamic-sparsity performance-scaling architecture and energy-efficient inter/intra-macro data reuse," in 2020 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2020, pp. 234–236.

- [13] S. Dong, J. Yang, X. Peng, H. Shang, Y. Ke, X. Yang, H. Liu, and A. Basu, "Topkima-Former: Low-Energy, Low-Latency Inference for Transformers Using Top-k In-Memory ADC," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 72, no. 6, pp. 2509–2519, 2025.

- [14] A. Biswas and A. P. Chandrakasan, "Conv-RAM: An energy-efficient SRAM with embedded convolution computation for low-power CNNbased machine learning applications," in 2018 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2018, pp. 488–490.

- [15] C. Yu, H. Jiang, J. Mu, K. T. C. Chai, T. T.-H. Kim, and B. Kim, "A Dual 7T SRAM-Based Zero-Skipping Compute-In-Memory Macro With 1-6b Binary Searching ADCs for Processing Quantized Neural Networks," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2024.

- [16] S. Kim, S. Kim, S. Um, S. Kim, K. Kim, and H.-J. Yoo, "Neuro-CIM: ADC-less neuromorphic computing-in-memory processor with operation gating/stopping and digital-analog networks," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 10, pp. 2931–2945, 2023.

- [17] C. Yu, T. Yoo, T. T.-H. Kim, K. C. T. Chuan, and B. Kim, "A 16K current-based 8T SRAM compute-in-memory macro with decoupled read/write and 1-5bit column ADC," in 2020 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 2020, pp. 1–4.

- [18] J. Song, X. Tang, H. Luo, H. Zhang, X. Qiao, Z. Sun, X. Yang, Z. Wu, Y. Wang, R. Wang et al., "A 4-bit calibration-free computing-in-memory macro with 3T1C current-programed dynamic-cascode multi-level-cell eDRAM," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 3, pp. 842–854, 2023.

- [19] S. Ambrogio, P. Narayanan, A. Okazaki, A. Fasoli, C. Mackin, K. Hosokawa, A. Nomura, T. Yasuda, A. Chen, A. Friz *et al.*, "An analog-AI chip for energy-efficient speech recognition and transcription," *Nature*, vol. 620, no. 7975, pp. 768–775, 2023.

- [20] F. Conti, L. Cavigelli, G. Paulin, I. Susmelj, and L. Benini, "Chipmunk: A systolically scalable 0.9 mm 2, 3.08 Gop/s/mW@ 1.2 mW accelerator for near-sensor recurrent neural network inference," in 2018 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 2018, pp. 1–4.

- [21] S. Yin, P. Ouyang, S. Tang, F. Tu, X. Li, L. Liu, and S. Wei, "A 1.06-to-5.09 TOPS/W reconfigurable hybrid-neural-network processor for deep learning applications," in 2017 Symposium on VLSI Circuits. IEEE, 2017, pp. C26–C27.

- [22] D. Shin, J. Lee, J. Lee, and H.-J. Yoo, "DNPU: An 8.1 TOPS/W reconfigurable CNN-RNN processor for general-purpose deep neural networks," in 2017 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2017, pp. 240–241.

- [23] T. Tambe, E.-Y. Yang, G. G. Ko, Y. Chai, C. Hooper, M. Donato, P. N. Whatmough, A. M. Rush, D. Brooks, and G.-Y. Wei, "A 16-nm SoC

- for Noise-Robust Speech and NLP Edge AI Inference With Bayesian Sound Source Separation and Attention-Based DNNs," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 2, pp. 569–581, 2023.

- [24] M. Le Gallo, R. Khaddam-Aljameh, M. Stanisavljevic, A. Vasilopoulos, B. Kersting, M. Dazzi, G. Karunaratne, M. Brändli, A. Singh, S. M. Mueller et al., "A 64-core mixed-signal in-memory compute chip based on phase-change memory for deep neural network inference," *Nature Electronics*, vol. 6, no. 9, pp. 680–693, 2023.

- [25] H. Dbouk, S. K. Gonugondla, C. Sakr, and N. R. Shanbhag, "A 0.44-µJ/dec, 39.9-µs/dec, recurrent attention in-memory processor for keyword spotting," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 7, pp. 2234–2244, 2021.

- [26] R. Guo, H. Li, R. Liu, Z. Zhang, L. Tang, H. Sun, L. Liu, M.-F. Chang, S. Wei, and S. Yin, "A 6.54-to-26.03 TOPS/W computing-in-memory RNN processor using input similarity optimization and attention-based context-breaking with output speculation," in 2021 Symposium on VLSI Technology. IEEE, 2021, pp. 1–2.

- [27] D. Kadetotad, S. Yin, V. Berisha, C. Chakrabarti, and J.-s. Seo, "An 8.93 TOPS/W LSTM recurrent neural network accelerator featuring hierarchical coarse-grain sparsity for on-device speech recognition," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 7, pp. 1877–1887, 2020.

- [28] R. Guo, Y. Liu, S. Zheng, S.-Y. Wu, P. Ouyang, W.-S. Khwa, X. Chen, J.-J. Chen, X. Li, L. Liu et al., "A 5.1 pJ/neuron 127.3 us/inference RNNbased speech recognition processor using 16 computing-in-memory SRAM macros in 65nm CMOS," in 2019 Symposium on VLSI Circuits. IEEE, 2019, pp. C120–C121.

- [29] S. Yan, J. Yue, C. He, Z. Wang, Z. Cong, Y. He, M. Zhou, W. Sun, X. Li, C. Dou et al., "A 28-nm floating-point computing-in-memory processor using intensive-CIM sparse-digital architecture," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 8, pp. 2630–2643, 2024.

- [30] Y. S. Chong, W. L. Goh, Y. S. Ong, V. P. Nambiar, and A. T. Do, "Efficient implementation of activation functions for LSTM accelerators," in 2021 IFIP/IEEE 29th International Conference on Very Large Scale Integration (VLSI-SoC). IEEE, 2021, pp. 1–5.

- [31] X. Feng, Y. Li, Y. Qian, J. Gao, W. Cao, and L. Wang, "A high-precision flexible symmetry-aware architecture for element-wise activation functions," in 2021 International Conference on Field-Programmable Technology (ICFPT). IEEE, 2021, pp. 1–4.

- [32] G. Raut, S. Rai, S. K. Vishvakarma, and A. Kumar, "A CORDIC based configurable activation function for ANN applications," in 2020 IEEE computer society annual symposium on VLSI (ISVLSI). IEEE, 2020, pp. 78–83.

- [33] Y. Xie, A. N. J. Raj, Z. Hu, S. Huang, Z. Fan, and M. Joler, "A twofold lookup table architecture for efficient approximation of activation functions," *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol. 28, no. 12, pp. 2540–2550, 2020.

- [34] Y. Li, W. Cao, X. Zhou, and L. Wang, "A low-cost reconfigurable nonlinear core for embedded dnn applications," in 2020 International Conference on Field-Programmable Technology (ICFPT). IEEE, 2020, pp. 35–38.

- [35] J. Yang, R. Mao, M. Jiang, Y. Cheng, P.-S. V. Sun, S. Dong, G. Pedretti, X. Sheng, J. Ignowski, H. Li et al., "Efficient nonlinear function approximation in analog resistive crossbars for recurrent neural networks," Nature Communications, vol. 16, no. 1, p. 1136, 2025.

- [36] C. Xie, Z. Shao, M. Zhang, Y. Du, and L. Du, "RAC-NAF: A Reconfigurable Analog Circuitry for Nonlinear Activation Function Computation in Computing-in-Memory," *IEEE Journal of Solid-State Circuits*, 2025(Early Access).

- [37] S. Yin, Z. Jiang, J.-S. Seo, and M. Seok, "XNOR-SRAM: In-memory computing SRAM macro for binary/ternary deep neural networks," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 6, pp. 1733–1743, 2020.

- [38] A. Kneip, M. Lefebvre, J. Verecken, and D. Bol, "IMPACT: A 1-to-4b 813-TOPS/W 22-nm FD-SOI compute-in-memory CNN accelerator featuring a 4.2-POPS/W 146-TOPS/mm 2 CIM-SRAM with multi-bit analog batch-normalization," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 7, pp. 1871–1884, 2023.

- [39] B. Zhang, J. Saikia, J. Meng, D. Wang, S. Kwon, S. Myung, H. Kim, S. J. Kim, J.-S. Seo, and M. Seok, "MACC-SRAM: A multistep accumulation capacitor-coupling in-memory computing SRAM macro for deep convolutional neural networks," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 6, pp. 1938–1949, 2023.

- [40] F. Tan, W.-H. Yu, J. Lin, K.-F. Un, R. P. Martins, and P.-I. Mak, "A 1.8% FAR, 2ms Decision Latency, 1.73 nJ/Decision Keywords Spotting (KWS) Chip Incorporating Transfer-Computing Speaker Verification, Hybrid-Domain Computing and Scalable 5T-SRAM," in 2024 IEEE

- International Solid-State Circuits Conference (ISSCC), vol. 67. IEEE, 2024, pp. 330–332.

- [41] M. E. Sinangil, B. Erbagci, R. Naous, K. Akarvardar, D. Sun, W.-S. Khwa, H.-J. Liao, Y. Wang, and J. Chang, "A 7-nm compute-in-memory SRAM macro supporting multi-bit input, weight and output and achieving 351 TOPS/W and 372.4 GOPS," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 1, pp. 188–198, 2020.

- [42] F. Lyu, Y. Xia, Z. Mao, Y. Wang, Y. Wang, and Y. Luo, "ML-PLAC: Multiplierless piecewise linear approximation for nonlinear function evaluation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 69, no. 4, pp. 1546–1559, 2021.

- [43] S. Mandal, S. Arfin, and R. Sarpeshkar, "Fast startup cmos current references," in 2006 IEEE International Symposium on Circuits and Systems. IEEE, 2006, pp. 4–pp.

- [44] T. Delbrück and A. V. Schaik, "Bias current generators with wide dynamic range," *Analog Integrated Circuits and Signal Processing*, vol. 43, pp. 247–268, 2005.

- [45] P. Warden, "Speech commands: A dataset for limited-vocabulary speech recognition," arXiv preprint arXiv:1804.03209, 2018.

- [46] L. Hou, J. Zhu, J. Kwok, F. Gao, T. Qin, and T.-y. Liu, "Normalization helps training of quantized lstm," Advances in Neural Information Processing Systems, vol. 32, 2019.

- [47] R. Mao, B. Wen, M. Jiang, J. Chen, and C. Li, "Experimentally-validated crossbar model for defect-aware training of neural networks," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 69, no. 5, pp. 2468–2472, 2022.

- [48] V. Joshi, M. Le Gallo, S. Haefeli, I. Boybat, S. R. Nandakumar, C. Piveteau, M. Dazzi, B. Rajendran, A. Sebastian, and E. Eleftheriou, "Accurate deep neural network inference using computational phase-change memory," *Nature communications*, vol. 11, no. 1, p. 2473, 2020.

- [49] F. Tan, W.-H. Yu, K.-F. Un, R. P. Martins, and P.-I. Mak, "A 0.05-mm 2 2.91-nJ/decision keyword-spotting (KWS) chip featuring an always-retention 5T-SRAM in 28-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 59, no. 2, pp. 626–635, 2023.

- [50] K. Kim, C. Gao, R. Graça, I. Kiselev, H.-J. Yoo, T. Delbruck, and S.-C. Liu, "A 23 uW solar-powered keyword-spotting ASIC with ring-oscillator-based time-domain feature extraction," in 2022 IEEE International Solid-State Circuits Conference (ISSCC), vol. 65. IEEE, 2022, pp. 1–3.

- [51] K. Cheng and A. Khakifirooz, "Fully depleted SOI (FDSOI) technology," Science China Information Sciences, 2016.