# Compass: Mapping Space Exploration for Multi-Chiplet Accelerators Targeting LLM Inference Serving Workloads

Boyu Li<sup>ab</sup>, Zongwei Zhu\*<sup>b</sup>, Yi Xiong<sup>ab</sup>, Qianyue Cao<sup>ab</sup>, Jiawei Geng<sup>ab</sup>, Xiaonan Zhang<sup>b</sup>, Xi Li<sup>b</sup>

<sup>a</sup>School of Computer Science and Technology, University of Science and Technology of China, Hefei 230026, China

<sup>b</sup>Suzhou Institute for Advanced Research, University of Science and Technology of China, Suzhou 215123, China

{llbbyy,xiongyi,cqy\_1999,gjw1998}@mail.ustc.edu.cn, {zzw1988,llxx}@ustc.edu.cn, zhangxiaonan\_93@163.com

#### **Abstract**

Large Language Models (LLMs) impose massive computational demands, driving the need for scalable multi-chiplet accelerators. However, existing mapping space exploration efforts for such accelerators primarily focus on traditional CNN/Transformer workloads and fail to adequately support the dynamic behaviors of mixed request types and variable sequence lengths in real-world LLM inference serving. To bridge this gap, we first propose a computation execution graph-based mapping encoding scheme that decouples micro-batches and layers, enabling fine-grained execution control on heterogeneous chiplets and flexibly representing various parallelism strategies. Second, building upon this scheme, we develop the Compass framework, which integrates an evaluation engine and a genetic algorithm-based mapping generation engine to achieve efficient mapping search. Compared to state-of-the-art works, our solution achieves an average EDP reduction of 63.12%.

# Keywords

LLM inference, chiplet, mapping space exploration.

#### 1 Introduction

In recent years, large language models (LLMs) have become a central focus in the deep learning field, demonstrating extraordinary capabilities across a wide range of natural language processing tasks. Corresponding to this remarkable performance are substantial computational and memory demands, making multi-chiplet accelerators a compelling solution [13, 18].

Currently, numerous studies [8, 9, 21] have explored mapping strategies for traditional deep learning models (primarily CNNs) on multi-chiplet accelerators. These works treat LLMs as a special case of conventional DNNs and consistently explore LLM mapping schemes targeting individual request types (either prefill or decode) with specified sequence lengths. However, in real-world inference serving scenarios, LLMs face highly dynamic workloads. This dynamism manifests primarily in two aspects: mixed request types and variable sequence lengths.

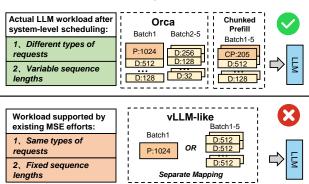

Mixed Request Types: Figure 1 illustrates the workload orchestration in two state-of-the-art inference serving scenarios: Orca [33] and Chunked Prefill [3]. Orca co-executes prefill requests together with decode requests upon their arrival, while Chunked Prefill partitions prefill requests into multiple chunks and executes them jointly with decode requests. However, existing works cannot support such scenarios where requests with different computational behaviors are executed together within the same batch.

Figure 1: Comparison between workload characteristics in real-world inference serving scenarios and those supported by existing MSE works. P:<num> denotes a prefill request with a sequence length of <num>. D denotes decode request, and CP denotes chunked prefill request.

Variable Sequence Lengths: LLM serving faces extreme sequence length variability (e.g., 1-161,281 in ShareGPT [2]). This not only causes different computational behaviors among instances within a batch, but also leads to significant workload variations across batches. Therefore, it is necessary to identify optimal mapping schemes based on the sequence length distribution of the serving scenario. However, existing works typically assume one specific sequence length or a fixed set of sequence lengths.

Existing multi-chiplet accelerator mapping space exploration (MSE) works can be categorized into two classes: mapping a single model [8, 29] and mapping multiple models simultaneously [9, 21]. However, both classes face challenges in handling LLM inference.

Single-model mapping works assume identical computation and memory access patterns across different instances within a batch, and extrapolate to the entire inference cycle by computing latency and energy for a steady state. For instance, SET[7] and Gemini [8] treat a single micro-batch as the steady state, while Stream [29] captures the steady state during runtime. The theoretical foundations of these approaches can only model LLMs with uniform types and sequence lengths, making it difficult to support more dynamic scenarios through minor framework adjustments.

Multi-model mapping works could seemingly model dynamism by treating different instances within a batch as separate models. However, mixed request types and variable sequences within batches necessitate a merge-split-merge pattern in LLM execution (see Section 3.1). Treating instances as separate models is incompatible with this pattern, and such a limited mapping space leads to suboptimal solutions. Moreover, variable sequence across batches

$<sup>^*</sup>$ Corresponding author.

require identifying optimal mappings based on the overall sequence length distribution, which has not been considered in prior works.

To address the above challenges, we contribute the following:

- (1) We propose a computation execution graph-based mapping encoding scheme. This scheme supports fine-grained scheduling of the minimal dynamic units in LLMs by decoupling micro-batches and layers. It can flexibly represent various mapping strategies (such as model, data, and pipeline parallelism on chiplets). To our knowledge, this is the first work to systematically define the mapping space for dynamic LLM inference workloads.

- (2) Building upon the encoding scheme, we develop Compass, an accelerator MSE framework supporting heterogeneous chiplet designs and dynamic LLM workloads. The evaluation engine is the core of Compass, which evaluates latency and energy consumption under given sequence distributions based on a fine-grained data access analysis algorithm. Additionally, Compass implements a genetic algorithm-based mapping search engine to enable efficient mapping exploration. Compass is open-sourced at: https://anonymous.4open.science/r/Compass-CB4A.

- (3) Compared with state-of-the-art MSE works, Compass effectively reduces energy-delay product across various scenarios. Furthermore, we also conducte experiments by combining cutting-edge service scheduling strategies such as Chunked Prefill. We hope that Compass can advance co-optimization efforts between multi-chiplet accelerators and dynamic LLM workloads.

#### 2 Related Work

LLM Inference Service Optimization. Numerous system-level efforts have emerged to accelerate LLM inference services since the advent of LLMs. Among them, Orca [33] is the first to propose iteration-level scheduling during batching: batching is applied during non-multi-head attention (MHA) stages, while requests are handled individually during the MHA stage. This eliminated the need for static batching [1], enabling mixed requests with different types and sequence lengths in a single batch. vLLM [15] also uses iteration-level scheduling but pauses ongoing decode processing upon the arrival of a prefill request, prioritizing prefill execution. From a chip-level perspective, this results in a type-separated workload pattern. Chunked Prefill [3, 4] introduces a strategy that splits prefill requests into multiple chunks and interleaves them with decode requests. These works have dramatically changed the nature of workloads faced by accelerators compared to traditional neural networks, leading to new challenges around mixed request types and variable sequence lengths.

Mapping for Chiplet Accelerators. As described in Section 1, related works can be categorized into two groups: mapping a single model and mapping multiple models simultaneously. Works such as Simba [26], Tangram [10], NN-baton [31], SET [7], Gemini [8], and Stream[29] focus on mapping a single model and cannot support mixed request types and variable sequence lengths. Works such as MAGMA [14], Veltair [19], MOHaM [9], and SCAR [21] focus on multi-model scenarios and can treat each LLM instance in a batch as a different model to handle dynamism. However, they result in incomplete mapping spaces due to mixed request types and variable sequence lengths, leading to suboptimal solutions.

# 3 Background

#### 3.1 LLM Inference Process

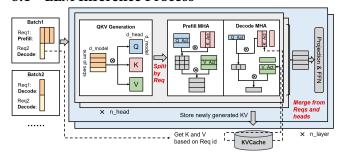

Figure 2: LLM Processing in Inference Serving.

Figure 2 illustrates the LLM workload execution process in inference serving when combined with dynamic batching paradigms. First, the workload in a batch is composed of multiple requests, each potentially differing in type and sequence length. Workloads across different batches may also vary. During inference, the workload of a batch is first **merged** into a large matrix containing all sequence lengths within the batch for QKV generation, in order to increase computational intensity. Subsequently, due to differences in request types and sequence lengths, these activations are **split** according to the input requests and processed individually. After multi-head attention (MHA) computation completes, the computational results from different requests are **merged** into a single matrix for subsequent FFN layer computation. This process of merging, splitting, and re-merging data within a batch distinguishes LLM workload execution from traditional neural networks.

# 3.2 Chiplet Hardware Template

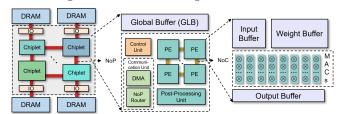

Figure 3: Multi-chiplet accelerator hardware template.

Figure 3 presents the hardware template used in this work, which is derived by extracting common features from existing chiplet accelerators [12, 16, 23, 34]. Multiple compute chiplets (which can have different dataflow architectures) are interconnected through a Network-on-Package (NoP) for inter-chiplet communication. Compute chiplets at the edge are connected to IO dies to enable communication with off-chip DRAM. Each chiplet contains a global buffer (GLB), post-processing unit, control unit, communication unit, and PE array. The PE array consists of a group of compute cores interconnected through an on-chip network, each containing input, weight, and output buffers as well as MAC arrays. Various chiplet accelerators can be realized by adjusting configuration parameters.

# 4 Mapping Encoding Scheme

As mentioned in Section 3.1, each instance in an LLM workload batch handles different tasks. Therefore, we treat the LLM workload

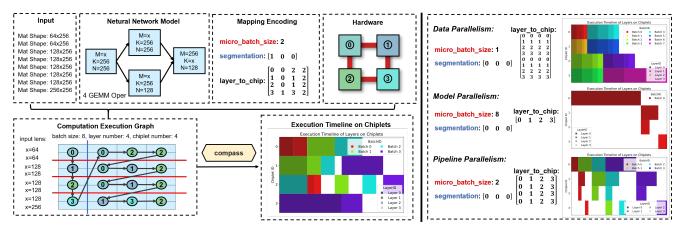

as a two-dimensional computation execution graph [27] with microbatch and layer as dimensions, rather than the one-dimensional layer sequence assumed in prior work [7, 10, 21, 32]. Consider a workload with batch size N and M layers to be mapped onto an accelerator with C chiplets. The encoding scheme consists of three components:  $micro\_batch\_size$ , segmentation, and  $layer\_to\_chip$ .

$micro\_batch\_size$  is an integer that describes how the computation graph is divided along the micro-batch dimension. It must satisfy  $micro\_batch\_size \mid N$ .

segmentation is a binary vector of length M-1 that indicates how the graph is segmented along the layer dimension. Formally, segmentation[i] = 1 means a segment boundary is placed after layer i; 0 means no segmentation. Since a natural segmentation occurs after the final layer, the length is M-1, not M.

After applying segmentation to both dimensions, the original computation graph is divided into  $\frac{N\times M}{micro\_batch\_size}$  subgraphs.  $layer\_to\_chip$  is a matrix of size  $\frac{N\times M}{micro\_batch\_size}$ , where each element is an integer between 0 and C-1, indicating which chiplet a subgraph is assigned to for execution.

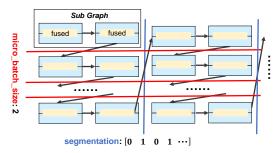

Figure 4: State and scheduling order of the computation execution graph after being partitioned into subgraphs.

Figure 4 shows the state of the computation execution graph after segmentation and the scheduling order. As described in Section 3.1, LLM inference typically merges all layers within a batch into a single matrix for processing, except during MHA computation. Therefore, workloads for the same layer within a subgraph are fused. After fusion, tasks within a subgraph are scheduled to their corresponding chiplets in layer order. Then, the subgraphs are scheduled first in micro-batch order, and then in layer order. It is important to note that "scheduling" here refers to the order of assigning workloads to chiplets, not the actual execution order. A workload can be executed only after its predecessor dependencies are resolved and the assigned chiplet becomes available. By leveraging the scheduling order and configuring segmentation, the workload can be flexibly scheduled. For example, setting the segmentation to all zeros enables row-wise (layer-first) scheduling; setting it to all ones enables column-wise (micro-batch-first) scheduling; other values of segmentation effectively segment the model itself. This scheduling order allows us to implement various common scheduling strategies by adjusting the values of *micro\_batch\_size* and *segmentation*.

Figure 5 shows a specific example of encoding and scheduling. In this example, the neural network model has four layers, each performing a matrix multiplication of  $M \times K$  and  $K \times N$ . The model processes a batch containing inputs of different matrix sizes. The

workload is to be mapped to hardware with four chiplets. The mapping scheme shown in Figure 5 is one found by Compass. The corresponding computation execution graph and the spatio-temporal execution diagram are also illustrated in the figure.

The right half of Figure 5 illustrates the mapping encoding and spatiotemporal execution diagrams for the three common parallelism strategies based on the case shown in the left half. In data parallelism, the model is split along the micro-batch dimension, with each chiplet independently executing all layers of a microbatch. There is no inter-chiplet communication, and inter-layer activations can be kept on-chiplet for reuse. In model parallelism, all layers with the same layer ID within a batch are fused together, and the entire model is split by layers and mapped to different chiplets. Inter-layer activations can be transferred via NoP to avoid DRAM accesses. In pipeline parallelism, each chiplet is fixed to process one specific layer and executes micro-batches in sequence, reducing both the DRAM accesses for inter-layer activations and the idle time of chiplets caused by layer dependencies. The mapping scheme here is similar to prior works mapping multiple models [14, 21], focusing on scenarios where individual layers are mapped to individual chiplets. For tensor parallelism, it can be achieved by configuring layer partitioning in the model architecture, thereby enabling exploration of hybrid parallelism schemes.

## 5 Compass Framework

# 5.1 Overview

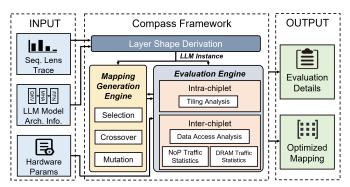

As shown in Figure 6, Compass takes sequence length traces, LLM architecture information, and hardware parameters as inputs, and outputs optimized mapping schemes along with evaluation details. Sequence length traces represent a novel input introduced by Compass compared to prior MSE works. This enables mapping generation based on sequence length distributions, thereby supporting optimization for specific application scenarios (e.g., summarization with long inputs and short outputs, or conversational scenarios with short inputs and long outputs). Considering the prohibitive overhead of searching for mapping schemes for every batch of requests, Compass is designed for the compilation phase to generate static mapping schemes. The problem can be formalized as follows: Given a request distribution  $\mathcal{D}$ , the engine samples a request set:  $\lambda \sim \mathcal{D}$ . For a mapping strategy set  $\mathcal{M}$  and an accelerator performance cost function C, Compass aims to select the optimal static mapping strategy  $M^*$  under request distribution  $\mathcal{D}$  that minimizes the expected performance loss over distribution  $\mathcal{D}$ :

$$M^* = \arg\min_{M \in \mathcal{M}} \ \mathbb{E}_{\lambda \sim \mathcal{D}} \left[ C(\lambda, M) \right] \tag{1}$$

Compass comprises two primary components: the mapping generation engine and the evaluation engine. First, Compass determines the layer shapes for each LLM instance in the batch based on sequence length traces and LLM architecture information. Subsequently, the instantiated LLM batches are dispatched to both engines. The mapping generation engine employs a genetic algorithm to optimize mappings based on evaluation results. The evaluation engine assesses the latency and energy consumption of given mappings based on LLM instances and hardware parameters. Compass generates multiple batches according to the traces to capture average performance across the sequence length distribution.

Figure 5: An example of a mapping encoding. The workload in this example is a neural network with 4 GEMMs, where the batch size is 8 with variable sequence lengths. This workload is to be mapped onto an accelerator with 4 chiplets. The mapping encoding provides a feasible mapping scheme. The lower-left portion shows the computation execution graph corresponding to the mapping encoding and the spatio-temporal diagram of the actual execution process. The right portion presents the mapping encoding representations and spatio-temporal execution diagrams of three common parallelism paradigms.

Figure 6: Overview of Compass.

#### 5.2 Mapping Generation Engine

The mapping encoding scheme proposed in Section 4 defines the mapping scheduling space of Compass, and the mapping generation engine is responsible for efficient exploration and sampling within this space. The engine first enumerates  $micro\_batch\_size$  values, and for each value, employs the genetic algorithm (GA) to explore the segmentation and  $layer\_to\_chip$  configurations.

**Selection and Crossover**: Tournament selection is employed to select offspring individuals, which avoids premature convergence toward optimal individuals. For *segmentation*, bit-level crossover is applied, where each bit is randomly inherited from one of the two parent individuals. After *segmentation* crossover, subgraph partitioning is performed. For *layer\_to\_chip*, subgraph-level crossover is applied, where each subgraph is randomly inherited from a parent. This crossover operation balances randomness while preserving the local stability of the computation execution graph.

**Mutation Operation**: For *segmentation*, two operators are defined: bit-flip and bit-swap. Bit-flip randomly selects a bit and toggles its value between 0 and 1. Bit-swap randomly selects a position and swaps its value with either the previous or the next bit. For *layer\_to\_chip*, we define seven mutation operators (see Table 1), ensuring complete coverage of the mapping space. Operators 1-3

Table 1: Mutation operators designed for layer\_to\_chip. : minimal impact, layer-level; : moderate impact, subgraph-level; : maximal impact, graph-level.

| ID | Description                                                                                                                  |  |

|----|------------------------------------------------------------------------------------------------------------------------------|--|

| 1  | Replace one position in <code>layer_to_chip</code> with a random chiplet                                                     |  |

| 2  | Swap the chiplet ID of one position in <code>layer_to_chip</code> with its adjacent position along the layer dimension       |  |

| 3  | Swap the chiplet ID of one position in <code>layer_to_chip</code> with its adjacent position along the micro-batch dimension |  |

| 4  | Randomly permute the <code>layer_to_chip</code> entries corresponding to a specific subgraph                                 |  |

| 5  | Replace every position in the $layer\_to\_chip$ of a specific subgraph with new random chiplets                              |  |

| 6  | Swap the <i>layer_to_chip</i> entries of one column of subgraphs with another                                                |  |

| 7  | Swap the <i>layer_to_chip</i> entries of one micro-batch with another                                                        |  |

target individual layers, operators 4-5 target subgraphs, and operators 6-7 affect entire rows or columns of the computation execution graph. During runtime, mutation probability is dynamically adjusted based on the exploration phase: more impactful mutations are favored in early stages for broader exploration, while less impactful ones are prioritized later for fine-tuning convergence.

#### 5.3 Evaluation Engine

The evaluation engine models latency and energy for a given mapping and hardware configuration by combining intra-chiplet and inter-chiplet evaluations.

**Intra-Chiplet Evaluation**: We employ ZigZag [20] to obtain the energy and latency for individual layers, and perform operation counting for non-compute-intensive layers through the vector compute unit, thereby enabling evaluation of layers such as activation

## Algorithm 1: Data Access Flag Determination

Input: Neural network model: model; computation execution graph: execGraph and corresponding data dimensions: segDim, microBatchDim, subGraphSize; number of chiplets: chipNum;

Output: Sets of direct predecessor and successor layers for each layer: layersPrev, layersNext; data access flags for each layer: isWriteOut, isLoadWei;

Data: Chiplet status table: chipState;

- 1 Initialize isWriteOut with true;

- 2 Initialize isLoadWei with false;

- $(laversPrev, laversNext) \leftarrow parse(model)$

- 4 for  $i \leftarrow 0$  to segDim do

```

for j \leftarrow 0 to microBatchDim do

5

for k \leftarrow 0 to subGraphSize do

6

(currChip, currLayer) \leftarrow execGraph[i, j, k];

7

for c \leftarrow 0 to chipNum do

8

(prevMicroBatch, prevLayer) \leftarrow chipState[c];

if c = currChip \land prevLayer = currLayer \land j \neq

10

prevMicroBatch then

11

isLoadWei[j][currLayer] \leftarrow true;

if prevMicroBatch = j then

12

layersNext[prevMicroBatch][prevLayer]

13

.erase(currLayer);

if layersNext[prevMicroBatch][prevLayer]

14

.empty() then

isWriteOut[prevMicroBatch][prevLayer]

layersPrev[j][currLayer] .erase(prevLayer);

16

chipState[\mathit{currChip}] \leftarrow (\mathit{j}, \mathit{currLayer});

17

```

18 **return** isWriteOut, isLoadWei, layersPrev, layersNext;

and normalization. In addition, we extend this foundation with support for temporal and spatial tiling by computing data reuse factors under different tiling strategies. Spatial tiling is similar to tensor parallelism [28] or spatial mapping [8] in prior works, where a layer is divided into multiple sub-layers to be processed by different chiplets. Temporal tiling, on the other hand, addresses insufficient buffer capacity by partitioning the workload into sub-blocks based on the maximum available buffer size.

**Inter-Chiplet Latency**: The total processing latency for a single layer is determined by the maximum of its computation latency and data access latency from DRAM and NoP, based on the widely used double-buffering assumption:  $T_{\text{proc},l} = \max (T_{\text{comp},l}, T_{\text{DRAM},l}, T_{\text{NoP},l})$ . The evaluation engine simulates layer execution based on the scheduling order defined in the mapping encoding. The start time of each layer is determined by the later of two times: the completion time of the previously scheduled layer on the same core, and the latest completion time among all its direct predecessor layers:  $T_{\text{start},l} = \max \left( \max_{l' \in \text{Pre}(l)} T_{\text{end},l'}, \max_{l'' \in \text{SameCore}(l)} T_{\text{end},l''} \right)$ . The completion time for a layer is then:  $T_{\text{end},l} = T_{\text{start},l} + T_{\text{proc},l}$ . The model's total execution time is the maximum completion time across all layers:  $T_{\text{model}} = \max_{l \in \mathcal{L}} T_{\text{end},l}$ .

Inter-Chiplet Energy: The total processing energy of a single layer is the sum of compute energy and data access energy from DRAM and NoP:  $E_{\text{proc},l} = E_{\text{comp},l} + E_{\text{DRAM},l} + E_{\text{NoP},l}$ . The total energy

Table 2: Hardware configuration.

| Accelerator<br>Architecture | WS (6×6 weight-stationary [11] chiplets),<br>OS (6×6 output-stationary [30] chiplets),<br>HE (3×6 WS and 3×6 OS chiplets) |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Chiplet Conf.               | 1024 MACs and 2 MiB GLB size per chiplet                                                                                  |

| Technology                  | TSMC 12nm, organic substrate, 1 GHz                                                                                       |

| NoP                         | GRS, mesh topology with XY routing, 128 GB/s                                                                              |

| DRAM                        | 64 GB/s × 4 dies                                                                                                          |

Table 3: Experimental configurations.

| Sequence Length Distribution | ShareGPT [2] (avg. input/output lens: 78/483)<br>CNN/DM [25] (avg. input/output lens: 866/63) |

|------------------------------|-----------------------------------------------------------------------------------------------|

| Serving Strategy             | vLLM [15], Orca [33], Chunked Prefill [3]                                                     |

| Batch Size                   | Prefill: 1, Decode: 128                                                                       |

| Model                        | GPT-3 6.7B [22]                                                                               |

| micro_batch_size             | [1, 2, 4, 8, 16, 32, 64, 128]                                                                 |

| Tensor Parallelism           | [8, 16, 32, 64] (number of FFN layer partitions)                                              |

| GA Settings                  | Population size: 120, Iterations: 200                                                         |

| Objective                    | Energy × Latency (EDP)                                                                        |

for the entire model is the sum of energy consumed by all layers:  $E_{\text{model}} = \sum_{l \in \mathcal{L}} T_{\text{proc},l}$ .

Data Access Analysis: As seen above, determining DRAM and NoP data access patterns is key to modeling inter-chiplet latency and energy. We use a scanning algorithm (see Algorithm 1) for this purpose. The algorithm maintains a chiplet status table and sets of direct predecessor and successor layers for each layer. The status table tracks which layers are temporarily stored on each chiplet during traversal. The basic idea is: if a layer is evicted from a chiplet and all its successor layers have already appeared (and it's not the last layer), then its output does not need to be written back to off-chip memory. When a layer is executed and the previous layer executed on the same chiplet has the same layer index but a different micro-batch ID, it indicates that weights do not need to be reloaded. The source of activations from predecessor layers is determined using the layersPrev set maintained by the algorithm. If a predecessor layer is still in layersPrev, it implies the output must be fetched from off-chip memory; otherwise, it can be directly retrieved from another chiplet via NoP. Additionally, Compass supports setting mandatory result write-out flags on a per-layer basis and allows specifying the DRAM ID for each layer's off-chip input and output. This enables flexible memory management control to accommodate the KV Cache management requirements in LLMs.

## **Experiments and Evaluation**

## Setup

Table 2 presents the hardware configuration, where parameter selections and the per-access energy and latency used by the evaluator are determined through ZigZag [20] and Gemini [8]. Compass has been validated and calibrated against the existing simulator Gemini, with latency and energy errors both within 3%. Table 3 provides additional experimental configurations, with batch sizes

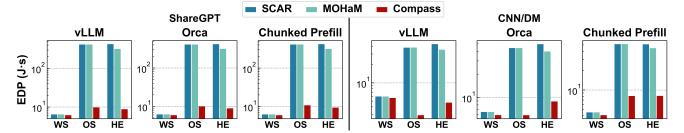

Figure 7: EDP comparison across mappings under different sequence length distributions, scheduling strategies, and hardware.

following common inference serving settings [1, 33] and MLPerf [24]. *micro\_batch\_size* and tensor parallelism degrees are explored through grid search to identify the optimal hybrid mapping scheme. Compass samples two sets of request traces from each sequence distribution, used for mapping search and validation respectively. The same request traces are scheduled under three different serving strategies. The experimental server is equipped with two Hygon 7285 processors with 128 logical cores. Leveraging multi-threaded parallelism, a single mapping search takes approximately five minutes on average, which is acceptable for practical mapping design.

SCAR [21] and MOHaM [9] are selected as comparison baselines, both representing state-of-the-art mapping methods for heterogeneous chiplets. SCAR develops a heuristic algorithm based on a hierarchical scheme, while MOHaM primarily employs genetic algorithms. We treat each LLM instance in the batch as a separate model to adapt their mapping schemes, convert their methods to Compass's mapping encoding for implementation, and evaluate them under identical configurations to ensure fair comparison.

#### 6.2 Comparison with Baseline

Figure 7 presents the experimental results. Overall, Compass achieves an average EDP reduction of 63.43% and 62.81% compared to SCAR and MOHaM, respectively. For homogeneous chiplet arrays (WS and OS), SCAR and MOHaM converge to similar optimal solutions. Compared to them, Compass achieves an average EDP reduction of 49.39%. This is primarily attributed to more comprehensive mapping space exploration enabled by its support for workload dynamism. For heterogeneous chiplet arrays, both GA-based approaches (MO-HaM and Compass) outperform SCAR. Compass further achieves an average EDP reduction of 89.61% compared to MOHaM through specialized genetic operator design. SCAR and MOHaM typically perform better on WS hardware (see Table 2), achieving performance comparable to Compass. Upon examining the generated mappings, we observe that they all produce pipeline parallelism-like mapping strategies, which align well with WS's weight-stationary hardware architecture.

## 6.3 Analysis of Solutions Generated by Compass

6.3.1 Impact of Sequence Distribution and Serving Strategy. As shown in Figure 7, ShareGPT exhibits similar performance across serving strategies due to its short inputs and long outputs, making the inference process dominated by pure decoding. CNN/DM exhibits more diverse performance under different serving strategies: OS architecture performs better under vLLM, while WS excels under Chunked Prefill. This demonstrates the need to jointly consider

application's sequence length distribution and serving strategy when determining hardware architecture.

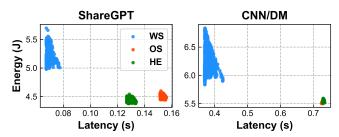

Figure 8: Mapping search process under Chunked Prefill for different sequence length distributions and hardware.

6.3.2 Design Point Analysis. Since Chunked Prefill is currently the most prevalent serving strategy and is based on mixed request types, we use it as a case study to analyze its mapping space. Figure 8 illustrates the mapping design points under this serving strategy for different sequence length distributions. Across both distributions, WS-based accelerators consistently achieve lower latency while OS-based accelerators deliver lower energy consumption. Overall, WS achieves lower EDP due to its more pronounced latency improvements. For CNN/DM, HE and OS designs exhibit similar performance. For ShareGPT, HE synergistically combines advantages of both architectures, establishing a new Pareto frontier. This demonstrates that hardware design performance is influenced by sequence length distribution, and that heterogeneous designs can enable novel trade-offs in certain scenarios.

## 6.4 Model Adaptability

Figure 9: Mapping EDP for different models under Chunked Prefill. Results are averaged across two sequence length distributions.

We further compare mapping results across different models under the Chunked Prefill strategy. In addition to GPT-3 6.7B, we

evaluate LLaMA-3 8B [5] (featuring GQA [6] and pre-layer normalization [17]) and GPT-3 13B. The average EDP performance across sequence length distributions is computed using geometric mean. As shown in Figure 9, Compass achieves lower EDP than other baselines across all models, demonstrating its adaptability to different model architectures and parameter scales.

#### 7 Conclusion

Compass proposes a mapping encoding scheme for mixed request types and variable sequence lengths, and implements an evaluation engine that supports heterogeneous multi-chiplet accelerators with fine-grained data access analysis. Furthermore, a customized genetic algorithm is applied to the mapping generation process to enable efficient exploration. Compared to state-of-the-art MSE methods, Compass achieves an average EDP reduction of 63.12%.

#### References

- [1] [n. d.]. GitHub NVIDIA/FasterTransformer: Transformer related optimization, including BERT, GPT. Website. https://github.com/NVIDIA/FasterTransformer.

- [2] [n.d.]. ShareGPT: Share your wildest ChatGPT conversations with one click. Website. https://sharegpt.com/.

- [3] Amey Agrawal, Nitin Kedia, Ashish Panwar, Jayashree Mohan, Nipun Kwatra, Bhargav S. Gulavani, Alexey Tumanov, and Ramachandran Ramjee. 2024. Taming Throughput-Latency Tradeoff in LLM Inference with Sarathi-Serve. In 18th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2024, Santa Clara, CA, USA, July 10-12, 2024. USENIX Association, 117-134.

- [4] Amey Agrawal, Ashish Panwar, Jayashree Mohan, Nipun Kwatra, Bhargav S. Gulavani, and Ramachandran Ramjee. 2023. SARATHI: Efficient LLM Inference by Piggybacking Decodes with Chunked Prefills. CoRR abs/2308.16369 (2023).

- 5] Meta AI. 2024. The Llama 3 Herd of Models. *CoRR* abs/2407.21783 (2024).

- [6] Joshua Ainslie, James Lee-Thorp, Michiel de Jong, Yury Zemlyanskiy, Federico Lebrón, and Sumit Sanghai. 2023. GQA: Training Generalized Multi-Query Transformer Models from Multi-Head Checkpoints. In Proceedings of the 2023 Conference on Empirical Methods in Natural Language Processing, EMNLP 2023, Singapore, December 6-10, 2023. Association for Computational Linguistics, 4895– 4901

- [7] Jingwei Cai, Yuchen Wei, Zuotong Wu, Sen Peng, and Kaisheng Ma. 2023. Interlayer Scheduling Space Definition and Exploration for Tiled Accelerators. In Proceedings of the 50th Annual International Symposium on Computer Architecture, ISCA 2023, Orlando, FL, USA, June 17-21, 2023. ACM, 13:1–13:17.

- [8] Jingwei Cai, Zuotong Wu, Sen Peng, Yuchen Wei, Zhanhong Tan, Guiming Shi, Mingyu Gao, and Kaisheng Ma. 2024. Gemini: Mapping and Architecture Coexploration for Large-scale DNN Chiplet Accelerators. In IEEE International Symposium on High-Performance Computer Architecture, HPCA 2024, Edinburgh, United Kingdom, March 2-6, 2024. IEEE, 156-171.

- [9] Abhijit Das, Enrico Russo, and Maurizio Palesi. 2024. Multi-Objective Hardware-Mapping Co-Optimisation for Multi-DNN Workloads on Chiplet-Based Accelerators. IEEE Trans. Computers 73, 8 (2024), 1883–1898.

- [10] Mingyu Gao, Xuan Yang, Jing Pu, Mark Horowitz, and Christos Kozyrakis. 2019. TANGRAM: Optimized Coarse-Grained Dataflow for Scalable NN Accelerators. In Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems, ASPLOS 2019, Providence, RI, USA, April 13-17, 2019. ACM, 807–820.

- [11] Google. 2017. In-Datacenter Performance Analysis of a Tensor Processing Unit. In Proceedings of the 44th Annual International Symposium on Computer Architecture, ISCA 2017, Toronto, ON, Canada, June 24-28, 2017. ACM, 1–12.

- [12] Xiaochen Hao, Zijian Ding, Jieming Yin, Yuan Wang, and Yun Liang. 2023. Monad: Towards Cost-Effective Specialization for Chiplet-Based Spatial Accelerators. In IEEE/ACM International Conference on Computer Aided Design, ICCAD 2023, San Francisco, CA, USA, October 28 - Nov. 2, 2023. IEEE, 1-9.

- [13] Siqi He, Haozhe Zhu, Jiapei Zheng, Lizhou Wu, Bo Jiao, Qi Liu, Xiaoyang Zeng, and Chixiao Chen. 2025. Hydra: Harnessing Expert Popularity for Efficient Mixture-of-Expert Inference on Chiplet System. In 62nd ACM/IEEE Design Automation Conference, DAC 2025, San Francisco, CA, USA, June 22-25, 2025. IEEE, 1-7.

- [14] Sheng-Chun Kao and Tushar Krishna. 2022. MAGMA: An Optimization Framework for Mapping Multiple DNNs on Multiple Accelerator Cores. In IEEE International Symposium on High-Performance Computer Architecture, HPCA 2022, Seoul, South Korea, April 2-6, 2022. IEEE, 814–830.

- [15] Woosuk Kwon, Zhuohan Li, Siyuan Zhuang, Ying Sheng, Lianmin Zheng, Cody Hao Yu, Joseph Gonzalez, Hao Zhang, and Ion Stoica. 2023. Efficient Memory Management for Large Language Model Serving with PagedAttention. In Proceedings of the 29th Symposium on Operating Systems Principles, SOSP 2023, Koblenz, Germany, October 23–26, 2023. ACM, 611–626.

- [16] Boyu Li, Zongwei Zhu, Weihong Liu, Qianyue Cao, Changlong Li, Cheng Ji, Xi Li, and Xuehai Zhou. 2025. Magnifier: A Chiplet Feature-Aware Test Case Generation Method for Deep Learning Accelerators. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 44, 7 (2025), 2803–2816.

- [17] Liyuan Liu, Xiaodong Liu, Jianfeng Gao, Weizhu Chen, and Jiawei Han. 2020. Understanding the Difficulty of Training Transformers. In Proceedings of the 2020 Conference on Empirical Methods in Natural Language Processing, EMNLP 2020, Online, November 16-20, 2020. Association for Computational Linguistics, 5747-5763.

- [18] Shiwei Liu, Zhirui Huang, Jiangnan Yu, Qi Liu, and Chixiao Chen. 2025. McPAL: Scaling Unstructured Sparse Inference with Multi-Chiplet HBM-PIM Architecture for LLMs. In 62nd ACM/IEEE Design Automation Conference, DAC 2025, San Francisco, CA, USA, June 22-25, 2025. IEEE, 1-7.

- [19] Zihan Liu, Jingwen Leng, Zhihui Zhang, Quan Chen, Chao Li, and Minyi Guo. 2022. VELTAIR: towards high-performance multi-tenant deep learning services via adaptive compilation and scheduling. In ASPLOS '22: 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Lausanne, Switzerland, 28 February 2022 - 4 March 2022. ACM, 388–401.

- [20] Linyan Mei, Pouya Houshmand, Vikram Jain, Juan Sebastian Piedrahita Giraldo, and Marian Verhelst. 2021. ZigZag: Enlarging Joint Architecture-Mapping Design Space Exploration for DNN Accelerators. *IEEE Trans. Computers* 70, 8 (2021), 1160–1174.

- [21] Mohanad Odema, Luke Chen, Hyoukjun Kwon, and Mohammad Abdullah Al Faruque. 2024. SCAR: Scheduling Multi-Model AI Workloads on Heterogeneous Multi-Chiplet Module Accelerators. CoRR abs/2405.00790 (2024).

- [22] OpenAI. 2020. Language Models are Few-Shot Learners. In Advances in Neural Information Processing Systems 33: Annual Conference on Neural Information Processing Systems 2020, NeurIPS 2020, December 6-12, 2020, virtual.

- [23] Chanho Park, Bogil Kim, Sungmin Ryu, and William J. Song. 2023. NeuroSpector: Systematic Optimization of Dataflow Scheduling in DNN Accelerators. *IEEE Trans. Parallel Distributed Syst.* 34, 8 (2023), 2279–2294.

- [24] Vijay Janapa Reddi, Christine Cheng, David Kanter, Peter Mattson, Guenther Schmuelling, Carole-Jean Wu, Brian Anderson, Maximilien Breughe, Mark Charlebois, William Chou, Ramesh Chukka, Cody Coleman, Sam Davis, Pan Deng, Greg Diamos, Jared Duke, Dave Fick, J. Scott Gardner, Itay Hubara, Sachin Idgunji, Thomas B. Jablin, Jeff Jiao, Tom St. John, Pankaj Kanwar, David Lee, Jeffery Liao, Anton Lokhmotov, Francisco Massa, Peng Meng, Paulius Micikevicius, Colin Osborne, Gennady Pekhimenko, Arun Tejusve Raghunath Rajan, Dilip Sequeira, Ashish Sirasao, Fei Sun, Hanlin Tang, Michael Thomson, Frank Wei, Ephrem Wu, Lingjie Xu, Koichi Yamada, Bing Yu, George Yuan, Aaron Zhong, Peizhao Zhang, and Yuchen Zhou. 2020. MLPerf Inference Benchmark. In 47th ACM/IEEE Annual International Symposium on Computer Architecture, ISCA 2020, Virtual Event / Valencia, Spain, May 30 June 3, 2020. IEEE, 446–459.

- [25] Abigail See, Peter J. Liu, and Christopher D. Manning. 2017. Get To The Point: Summarization with Pointer-Generator Networks. In Proceedings of the 55th Annual Meeting of the Association for Computational Linguistics, ACL 2017, Vancouver, Canada, July 30 - August 4, Volume 1: Long Papers. Association for Computational Linguistics, 1073–1083.

- [26] Yakun Sophia Shao, Jason Clemons, Rangharajan Venkatesan, Brian Zimmer, Matthew Fojtik, Nan Jiang, Ben Keller, Alicia Klinefelter, Nathaniel Ross Pinckney, Priyanka Raina, Stephen G. Tell, Yanqing Zhang, William J. Dally, Joel S. Emer, C. Thomas Gray, Brucek Khailany, and Stephen W. Keckler. 2019. Simba: Scaling Deep-Learning Inference with Multi-Chip-Module-Based Architecture. In Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture, MICRO 2019, Columbus, OH, USA, October 12-16, 2019. ACM, 14-27.

- [27] Ying Sheng, Lianmin Zheng, Binhang Yuan, Zhuohan Li, Max Ryabinin, Beidi Chen, Percy Liang, Christopher Ré, Ion Stoica, and Ce Zhang. 2023. FlexGen: High-Throughput Generative Inference of Large Language Models with a Single GPU. In International Conference on Machine Learning, ICML 2023, 23-29 July 2023, Honolulu, Hawaii, USA (Proceedings of Machine Learning Research, Vol. 202). PMLR. 31094–31116.

- [28] Mohammad Shoeybi, Mostofa Patwary, Raul Puri, Patrick LeGresley, Jared Casper, and Bryan Catanzaro. 2019. Megatron-LM: Training Multi-Billion Parameter Language Models Using Model Parallelism. CoRR abs/1909.08053 (2019).

- [29] Arne Symons, Linyan Mei, Steven Colleman, Pouya Houshmand, Sebastian Karl, and Marian Verhelst. 2025. Stream: Design Space Exploration of Layer-Fused DNNs on Heterogeneous Dataflow Accelerators. *IEEE Trans. Computers* 74, 1 (2025), 237–249.

- [30] Emil Talpes, Atchyuth Gorti, Gagandeep S. Sachdev, Debjit Das Sarma, Ganesh Venkataramanan, Peter Bannon, Bill McGee, Benjamin Floering, Ankit Jalote, Christopher Hsiong, and Sahil Arora. 2020. Compute Solution for Tesla's Full Self-Driving Computer. IEEE Micro 40, 2 (2020), 25–35.

- [31] Zhanhong Tan, Hongyu Cai, Runpei Dong, and Kaisheng Ma. 2021. NN-Baton: DNN Workload Orchestration and Chiplet Granularity Exploration for Multichip Accelerators. In 48th ACM/IEEE Annual International Symposium on Computer Architecture, ISCA 2021, Virtual Event / Valencia, Spain, June 14-18, 2021. IEEE, 1013-1026.

- [32] Yi Xiong, Weihong Liu, Rui Zhang, Yulong Zu, Zongwei Zhu, and Xuehai Zhou. 2024. EPipe: Pipeline Inference Framework with High-quality Offline Parallelism Planning for Heterogeneous Edge Devices. In Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design, ICCAD 2024, Newark Liberty International Airport Marriott, NJ, USA, October 27-31, 2024. ACM, 111:1-111:10.

- [33] Gyeong-In Yu, Joo Seong Jeong, Geon-Woo Kim, Soojeong Kim, and Byung-Gon Chun. 2022. Orca: A Distributed Serving System for Transformer-Based Generative Models. In 16th USENIX Symposium on Operating Systems Design and Implementation, OSDI 2022, Carlsbad, CA, USA, July 11-13, 2022. USENIX Association, 521–538.

- [34] Jinming Zhang, Xuyan Wang, Yaoyao Ye, Dongxu Lyu, Guojie Xiong, Ningyi Xu, Yong Lian, and Guanghui He. 2024. M2M: A Fine-Grained Mapping Framework to Accelerate Multiple DNNs on a Multi-Chiplet Architecture. IEEE Trans. Very Large Scale Integr. Syst. 32, 10 (2024), 1864–1877.