# On Circuit Imbalance and 0/1 Circuits for Coloring and Spanning Forest Problems

Steffen Borgwardt\* Nicholas Crawford<sup>†</sup> Sean Kafer<sup>‡</sup>

Jon Lee<sup>§</sup> Angela Morrison<sup>¶</sup>

#### Abstract

Circuits are fundamental objects in linear programming and oriented matroid theory, representing the elementary difference vectors of a polyhedron between points in its affine space. A recent concept introduced by Ekbatani, Natura, and Végh, the *circuit imbalance*, serves as a complexity measure relevant to iteration bounds for circuit-based augmentation and circuit diameters, as well as the general interpretability of circuits in terms of the underlying application. In this paper, we analyze linear programming formulations of relaxed combinatorial optimization problems to prove two contrasting types of results related to the circuit imbalance.

On one hand, we identify simple and common constraint structures, in particular arising in graph-theoretic problems, that inherently lead to an exponential circuit imbalance. These constructions show that, in quite general situations, working with the entire set of circuits poses significant challenges for an application of circuit augmentation or the study of circuit diameters.

On the other hand, through a case study of two classic graph-theoretic problems with exponential imbalance, the vertex graph coloring problem and the maximum weight forest problem, we exhibit the existence of sets and subsets of highly interpretable circuits of (best-case) imbalance 1. These sets correspond to the recoloring of vertices or to the addition or removal of edges, respectively, for example generalizing classic concepts of Kempe dynamics in coloring. Their interpretability in terms of the underlying application facilitates a study of circuit walks in the corresponding polytopes. We prove that a restriction of circuit walks to these sets suffices to not only guarantee reachability of the integral extreme-points of the skeleton, but leads to linear and constant circuit diameter bounds, respectively.

**Keywords:** polyhedron, linear programming, circuits, circuit imbalance, vertex coloring, maximum weight forest

MSC: 05C69, 52B05, 90C05, 90C27

## 1 Introduction

The circuits or elementary vectors of a polyhedron  $P = \{\mathbf{x} : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  are a classic topic introduced in the works of several authors in the 1960s and 70s [12, 23, 31, 34]. Formally, they are nonzero vectors  $\mathbf{g}$  in  $\ker(A)$  such that  $B\mathbf{g}$  is support-minimal. They are a generalization of the edge directions of P, and serve as an inclusion-minimal test set for optimality certificates for any linear program (LP) over P. In the past decade, research related to circuits has focused on circuit augmentation schemes for solving LPs [11, 17, 18], generalizations of the Simplex method for solving

$<sup>{\</sup>tt *steffen.borgwardt@ucdenver.edu;}\ \ {\tt University}\ \ {\tt of}\ \ {\tt Colorado}\ \ {\tt Denver},\ \ {\tt Department}\ \ {\tt of}\ \ {\tt Mathematical}\ \ {\tt and}\ \ {\tt Statistical}\ \ {\tt Sciences}$

<sup>†</sup>ncrawford@losmedanos.edu; Los Medanos College

<sup>&</sup>lt;sup>‡</sup>spkafer@ilstu.edu; Illinois State University, Department of Mathematics

<sup>§</sup>jonxlee@umich.edu; University of Michigan

<sup>¶</sup>angela.morrison1@ucalgary.ca; University of Calgary, Department of Mathematics and Statistics

LPs, wherein one can move in the direction of any circuit (taking a maximal-length step) instead of just along edges, and the *circuit diameter* of polyhedra [5, 6, 7, 25], which generalizes the combinatorial diameter in the same way and gives a lower bound on the number of iterations necessary to solve an LP via circuit augmentation algorithms, as well as a lower bound on the combinatorial diameter itself. Circuits have also been used indirectly as an analytical tool to bound the performance of interior point methods [15]. Research in the area takes several forms and has often focused on problems in combinatorial optimization. In fact, many algorithms from combinatorial optimization turn out to be efficient implementations of circuit augmentation tailored to the application.

It is well known that for many structured problems, there exist circuits that are readily interpreted in terms of the underlying application. This comes from a combination of two properties: first, circuits have an inclusion-minimal support; for standard-form problems, this typically means that they only have few nonzero entries. And second, it greatly matters how complicated the nonzero entries of a circuit are. This can be formally described by the so-called *circuit imbalance measure*, which is the maximum absolute ratio of nonzero components of any circuit (Definition 6). Whereas a small support is guaranteed by definition, a low circuit imbalance is not. In fact, it can be exponentially large in terms of the natural parameters of the underlying problem (for example, the number of vertices in the graph defining the problem). A high circuit imbalance is directly opposed to the ease of a formal analysis and study of diameters and circuit pivot rules. This leads to two promising directions of research: the study of problems where circuit imbalance is known to be low; or a restriction of the analysis to those circuits of low imbalance to gain valuable insights on more complicated problems.

Circuit augmentation and diameters are best understood for polyhedra with low circuit imbalance measure. A prime example lies in network-flows applications, which have totally-unimodular constraint matrices, in turn guaranteeing that circuits only have nonzero entries  $\pm 1$ . For example, the characterization of circuits in [8, 22, 19] are a key to showing that many graph-theoretic algorithms are, in fact, circuit augmentation schemes with respect to conceptually simple pivot rules. However, only a small number of concrete LPs from combinatorial optimization are known to have sub-exponential circuit imbalance measure. These include the fractional matching polytope, the fractional stable set polytope, and problems with totally-unimodular constraint matrices, such as the network-flows problems mentioned above [18, 25, 29].

In this work, we are interested in furthering the understanding of problems of high circuit imbalance. As we will see, the suggested approach of restricting the analysis to circuits of low imbalance is a powerful tool to obtain new insight.

A typical strategy for connecting classical algorithms to circuit augmentation schemes, or for bounding the circuit diameter, builds on a characterization of the set of circuits of the polyhedron at hand. To this end, one attempts to devise a complete or partial description of the circuits in terms of the underlying combinatorial problem [5, 8, 10, 19, 25]. For example, the circuit directions for the clustering problem described in [10] can be thought of as swapping items between clusters. As one of our contributions, we add to this area by establishing a relation between the circuits of coloring polytopes and classic Kempe dynamics.

A key challenge lies in the fact that for many polyhedra in combinatorial optimization, the set of circuits is not fully characterized, and it seems difficult to do so. This challenge is directly linked to the circuit imbalance and, relatedly, the fact that many (likely, most) of the circuits therefore admit no clear combinatorial interpretation. For example, a circuit  $\mathbf{g}$  defined over a set E of size n wherein one component of  $\mathbf{g}$  is  $2^n$  times larger than another is unlikely to admit a natural interpretation in terms of the underlying set. This is in contrast to, say, a circuit  $\mathbf{g} \in \{0, \pm 1\}^n$ , which we call a  $\theta/1$  circuit. Such circuits are readily interpreted as adding and removing elements from some subset M of E (e.g., adding and removing edges from a given matching). As one of our main contributions, in Section 2 we demonstrate that in a wide range of graph-theoretic problems, one already arrives at an exponential circuit imbalance just by using a small set of constraints with a simple structure: given a graph G = (V, E), we consider various potential constraint matrices A whose rows are in  $\{0,1\}^E$ . We consider a variety of natural choices of families  $\mathcal{H} \subseteq 2^E$  to determine the supports of the rows of

A (i.e., of the constraints). In all of the cases we consider, we are able to show that any polyhedron  $\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} \leq b, \mathbf{x} \geq \mathbf{0}\}$  has circuit imbalance at least exponential in |E|. This includes cases where A has a number of rows which is only polynomial in |E|. We find these observations to support the general hypothesis that it is rare for polyhedra arising from combinatorial optimization to have sub-exponential circuit-imbalance.

In Sections 3 and 4, we then study two classic families of polytopes, corresponding to fractional vertex coloring and graphic matroids (or the search for a maximum-weight forest). While we show that both of them have an exponential circuit imbalance, we are able to gain valuable insight from a study of their 0/1 circuits, leading to a generalization of classic concepts of combinatorial reconfiguration and constant circuit diameter bounds, respectively.

A restriction of the analysis to 0/1 circuits has already proven to be a successful approach in the literature for previous analytical results. Specifically, it was shown that the 0/1 circuits suffice to find extremely short paths (of just 1 or 2 steps) between the integral solutions of the well-known traveling salesman problem (TSP) [25], for which our results in Section 2 also imply exponential circuit imbalance. Further, many combinatorial algorithms which are, as mentioned above, in essence circuit augmentation algorithms utilize only 0/1 circuits, even when the associated polyhedron has other circuits. And finally, a restriction to 0/1 circuits gives a natural connection to the area of combinatorial reconfiguration: given two integral extreme-point solutions of an LP, one can ask if it is possible to transform one solution into another via a set of valid "moves", where each intermediary solution is required to also be integral. In a yes instance, one then asks how many steps it takes to transform any solution into any other solution. Here, our set of valid moves is precisely the circuits of the given LP. When we consider moving between integral solutions for problems whose integral solutions are all in  $\{0,1\}^n$ , this necessitates that only 0/1 circuits are used, even when others exist.

These questions can be seen as a variation of the study of circuit diameters [4, 9, 25], where we seek to move between any two extreme-point solutions (i.e., not only integral ones), and in each iteration we are allowed to take a maximal-length step in the direction of any circuit. For many LPs from combinatorial optimization, all extreme-point solutions are in  $\{0,1\}^n$ , and all solutions in  $\{0,1\}^n$  are extreme-point solutions. In this setting, the number of moves in the transformations we consider gives an upper bound on the circuit diameter.

In contrast, in view of circuit augmentation, a restriction of the analysis to 0/1 circuits or any subset of the set of circuits would have some natural limitations. First, generic methods for solving LPs via circuit augmentation may utilize circuits which are not 0/1, even if there was a monotone walk just using 0/1 circuits. In fact, many theoretical results bounding the running time of generic circuit augmentation algorithms on general LPs require that the full set of circuits be available as augmentation directions [16, 17, 18]. Relatedly, in combinatorial optimization we are typically interested in moving only between the integral solutions of an integer program. However, circuit augmentation — whether along general circuits or even along 0/1 circuits — may pass through non-integral solutions of the corresponding LP relaxation. There are several interesting open questions coming out of these challenges. We point out some of them in our final remarks in Section 5.

Next, in Section 1.1, we provide some necessary background and definitions on circuits and circuit imbalance measure. We then summarize our contributions and provide an outline of the paper in Section 1.2.

#### 1.1 Preliminaries

We now provide some formal terminology and then outline our contributions. Given a set X, a vector  $\mathbf{x} \in \mathbb{R}^X$ , and  $i \in X$ , we use  $\mathbf{x}(i)$  to denote the component of  $\mathbf{x}$  indexed by i.

**Definition 1.** The characteristic vector of a subset T of a set S is the vector  $\mathbf{X}_T := (x_s)_{s \in S}$  such that x(s) = 1 if  $s \in T$  and x(s) = 0 if  $s \notin T$ .

We follow [5, 11, 17, 19, 31] for some background on the theory of circuits and circuit augmentation. Recall that a set of *circuits* for a polyhedron can be defined as follows.

**Definition 2** (Circuits). Given matrices  $A \in \mathbb{R}^{m_A \times n}$  and  $B \in \mathbb{R}^{m_B \times n}$ , the set of circuits corresponding to A and B, denoted C(A, B), consists of those  $\mathbf{g} \in ker(A) \setminus \{\mathbf{0}\}$ , normalized to coprime integer components, for which  $B\mathbf{g}$  is support minimal over the set of  $\{B\mathbf{x} : \mathbf{x} \in ker(A) \setminus \{\mathbf{0}\}\}$ . When A is empty (in which case  $ker(A) = \mathbb{R}^n$ ), we denote the corresponding set of circuits by C(0, B).

Given a polyhedron P described by the system of equalities and inequalities  $P = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$ , we say that the circuits  $\mathcal{C}(A, B)$  are the circuits of this formulation of P. In the studies of circuit augmentation and diameters over a polyhedron P, it often is necessary to restrict to the feasible circuit directions at some point  $\mathbf{x}$  in P, i.e., those directions in which a nonzero step starting at  $\mathbf{x}$  remains in P.

**Definition 3.** Given a point  $\mathbf{x}$  in a polyhedron  $P = {\mathbf{x} : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}}$ , we say a circuit  $\mathbf{g} \in \mathcal{C}(A, B)$  is feasible at  $\mathbf{x}$  if there exists  $\epsilon > 0$  such that  $\mathbf{x} + \epsilon \mathbf{g} \in P$ .

This leads to the notion of a circuit walk where one moves between solutions in P using feasible circuits.

**Definition 4.** Let  $P = \{ \mathbf{x} \in \mathbb{R}^m : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d} \}$  be a polyhedron. Starting at an extreme-point  $\mathbf{v}$  of P, we call a sequence of  $\mathbf{v} = \mathbf{x}_0, ..., \mathbf{x}_k$  a **circuit walk** of length k if for i = 0, ..., k - 1:

- 1.  $\mathbf{x}_i \in P$

- 2.  $\mathbf{x}_{i+1} = \mathbf{x}_i + \epsilon_i \mathbf{g}_i$  for some  $\mathbf{g}_i \in \mathcal{C}(A, B)$  and  $\epsilon_i > 0$  and

- 3.  $\mathbf{x}_i + \epsilon_i \mathbf{g}_i$  is infeasible for all  $\epsilon > \epsilon_i$ .

This definition assumes that feasible circuits are used for steps of maximal length, and that the walk begins at an extreme-point  $\mathbf{v} = \mathbf{x}_0$ . We do not require that the walk terminate at an extreme-point  $\mathbf{x}_k$ .

In general, different formulations of the exact same polyhedron P can give rise to different sets of circuits. However, as shown in [24], all so-called *minimal* descriptions of a polyhedron give rise to the same set of circuits. Here, a minimal description is defined as follows.

**Definition 5** (See e.g. [13]). Given a polyhedron P (considered as a set), we say that  $\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} \leq \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  is a **minimal description of** P if it satisfies the following:

- 1.  $P = {\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}}$

- 2. No inequality of  $\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  can be made an equality without changing the set.

- 3. No inequality or equality of  $\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}\$  can be omitted without changing the set.

All valid formulations of P must contain the circuits of a minimal description of P. Thus, when  $\{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  is a minimal description of a polyhedron P, we can meaningfully say that  $\mathcal{C}(A,B)$  are the circuits of P. We can define the circuits of P equivalently as the set of all directions that can be obtained as edges of any polyhedron of the form  $P' = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}', B\mathbf{x} \leq \mathbf{d}'\}$  as the right-hand sides  $\mathbf{b}'$  and  $\mathbf{d}'$  vary [23]. As such, the circuits of a polyhedron include its edge directions. This latter fact holds even when one is given a non-minimal description. That is, for any description  $P = \{\mathbf{x} \in \mathbb{R}^n : A\mathbf{x} = \mathbf{b}, B\mathbf{x} \leq \mathbf{d}\}$  of a polyhedron P, (appropriate normalizations of) the edge directions of P are in  $\mathcal{C}(A,B)$ . We now formally define the circuit imbalance measure, a measure on how complex the set of circuits can be.

**Definition 6.** Given matrices A and B, the **circuit imbalance measure** of A and B is defined to be

$$\kappa(A, B) = \max \left\{ \left| \frac{\mathbf{g}(i)}{\mathbf{g}(j)} \right| : \mathbf{g} \in \mathcal{C}(A, B) \right\}.$$

We note that in some context, it may be more natural to define  $\kappa(A,B)$  to be the maximum possible value of  $\left|\frac{(B\mathbf{g})(i)}{(B\mathbf{g})(j)}\right|$  over all circuits  $\mathbf{g}$ . However, as we are in part concerned with the relationship between the circuit imbalance and the *interpretability* of circuits, here it is more natural to consider the components of the circuits themselves.

#### 1.2 Contributions

We now have the basic terminology needed to describe our contributions. As discussed previously, these are of two types: we begin with a study of the circuit imbalance measure for generic graph-theoretic constraint matrices in Section 2; then, in Sections 3 and 4, we study two specific, classic problems where we are able to devise new insight from their 0/1 circuits, despite those problems having an exponential imbalance.

First, consider a simple, loop-free graph G = (V, E) and  $\mathcal{H} \subseteq 2^E$ , and let  $B' = B'(G, \mathcal{H})$  be the matrix whose rows are given by  $\mathbf{X}(H)$  for all  $H \in \mathcal{H}$ , where  $\mathbf{X}(H)$  is the characteristic vector of H. Let

$$B = B(G, \mathcal{H}) = \begin{bmatrix} B' \\ I \end{bmatrix},$$

and let  $\kappa(\mathcal{H}) = \max_G \{\kappa(0, B)\}$ . Note that this a very general framing that captures many well-studied constraint matrices from combinatorial optimization (for appropriate choices of  $\mathcal{H}$ ). It is known, for example, that if

$$\mathcal{H} = \{ \delta(v) : v \in V \},\$$

then B is the inequality constraint matrix of the standard formulation of the fractional matching polytope, and the circuit imbalance measure of that matrix at most 2 (see, e.g., [18]).

In Section 2, we consider the following natural question:

#### **Question 1.1.** Can simple, small sets $\mathcal{H}$ lead to exponential $\kappa(\mathcal{H})$ ?

A sub-exponential circuit imbalance comes with several advantages. In particular, known bounds on circuit diameters become stronger [16] and, more generally, a partial (or complete) characterization of the set of circuits becomes more attainable. However, we will show that many families of constraints (both structurally-simple and small in size) already lead to exponential circuit imbalance. Consider for example the set

$$\mathcal{H} = \{\delta(v) : v \in V\} \cup \{E[S] : S \subseteq V, |S| \text{ odd}\},\$$

where, for  $S \subseteq V$  we let  $E[S] = \{uv \in E : u, v \in S\}$ . In this case,  $B(G, \mathcal{H})$  is the inequality constraint matrix of the standard formulation of the matching polytope, and we show that its circuit imbalance measure is at least exponential in the number of edges.

In particular, in Theorem 2.1 we show that the inclusion of just a polynomial-sized subset of  $\{E[S]: S\subseteq V, |S| \text{ odd}\}$  is already enough to guarantee at least exponential circuit imbalance. In the same theorem, we show the same holds if  $\mathcal{H}$  contains all paths of length 4 or if  $\mathcal{H}$  contains all sets of size 3. We strengthen these last two conclusions with a new construction in Theorem 2.2 and show that even if  $\mathcal{H}$  only contains all paths of length 3, then  $\kappa(\mathcal{H})$  is at least exponential. Finally, in Theorems 2.3 and 2.4, we get at least exponential circuit imbalance when  $\mathcal{H}$  contains all cycles of length 4 or all star subgraphs, respectively.

These results suggest that for many simple and seemingly natural candidates for  $\mathcal{H}$ , we get exponential circuit imbalance, in turn suggesting that collections  $\mathcal{H}$  that give low circuit imbalance for all graphs may be rare. We see this exponential circuit imbalance for the classic families of polytopes studied in Sections 3 and 4 (Lemma 3.8 and Corollary 4.1, respectively), which adds to our motivation for a study of their 0/1 circuits.

In Section 3, we study the relationship between the 0/1 circuits of the fractional coloring polytope and classic Kempe dynamics. We consider the following well-known representation of the fractional coloring problem.

**Definition 7.** Let G = (V, E) be a graph and  $\tau = \{t_1, \ldots, t_r\}$  a set of colors. The fractional coloring problem has the following formulation:

$$\begin{aligned} \mathbf{x} \in \mathbb{R}^{|V| \times r} : & \sum_{i \in K} \mathbf{x}(v, i) = 1 \quad \forall v \in V \\ \mathbf{x}(v, i) + \mathbf{x}(u, i) \le 1 \quad \forall i \in \tau, \ uv \in E \\ \mathbf{x}(v, i) \ge 0 \quad \forall v \in V, \forall i \in \tau \end{aligned}$$

Using this formulation, in Theorem 3.2 we are able to characterize the circumstances under which (the extreme-points corresponding to) two proper colorings differ by a circuit. A consequence of Theorem 3.2 is that the Kempe chains of the underlying reconfiguration graph correspond to some but not all of the 0/1 circuits of the fractional coloring polytope. This correspondence allows us to reinterpret Kempe feasibility in terms of circuit walks. Here, and in the literature, Kempe feasibility or Kempe equivalence refers to the ability to transform one proper coloring into another by a sequence of Kempe swaps, i.e., an exchange of two colors on a minimal number of vertices subject to the coloring remaining proper.

In the polyhedral setting, this is analogous to reachability between extreme-points of the integer coloring polytope via edge walks. However, it is well known that Kempe swaps do not suffice to move between any pair of colorings (i.e., reachability can fail); for instance, in the case of the 3-colorings of the triangular prism.

In fact, in Theorem 3.2, we fully characterize the 0/1 circuits of the fractional coloring polytope. In particular, we show that the set of 0/1 circuits of the fractional coloring polytope includes vectors corresponding to a generalization of Kempe swaps wherein they can involve more than just two colors. We then show in Theorem 3.5 that all extreme-points of the fractional coloring polytope which correspond to proper colorings are reachable from each other via circuit walks using this subset of the 0/1 circuits. That is to say, while Kempe swaps do not suffice to achieve reachability between all proper colorings, the generalized Kempe swaps corresponding to these 0/1 circuits do suffice to achieve reachability.

On the other hand, in contrast to some combinatorial polytopes (like TSP and Matching discussed earlier), we show that the 0/1 circuits of the fractional coloring polytope are not enough to guarantee the existence of constant-length circuit walks between extreme-points corresponding to proper colorings (if those walks are required to visit only integral extreme-points, i.e., proper colorings). In particular, we show in Theorem 3.6 that for a graph on n vertices, n steps can be necessary (and that n steps suffices is trivial). Finally, in Section 3.2, we provide an explicit construction showing that the circuit imbalance of the coloring polytope is at least exponential, further supporting the restriction of our attention to 0/1 circuits.

In Section 4 we study the maximum weight forest polytope, a polytope associated with a graphic matroid. A major difference between this polytope and the coloring polytope discussed in Section 3 is that it has an exponential number of constraints, which leads to some interesting differences in our approach and results.

**Definition 8.** Let G = (V, E) be a simple graph. The maximum weight forest problem has a feasible set that corresponds to the extreme-points of the polytope given by the following system of constraints:

$$\mathbf{x} \in \mathbb{R}^{|E|}: \qquad \sum_{e \in E(G[U])} \mathbf{x}(e) \leq |U| - 1 \qquad \forall \emptyset \neq U \subseteq V \\ \mathbf{x}(e) \geq 0 \qquad \forall e \in E,$$

(MWF)

where G[U] is the subgraph of G induced by  $U \subseteq V$ .

In the constraint matrix of (MWF), there are duplicated rows in that the matrix rows for the constraints  $\mathbf{x}(e) \geq 0$  appear also in the rank inequality constraints  $(\sum_{e \in E(G[U])} \mathbf{x}(e) \leq |U| - 1)$  for sets  $U = \{u, v\}$  with  $uv \in E$ . For the characterization of circuits or non-circuits, it suffices to consider the simpler system

$$\sum_{e \in E(G[U])} \mathbf{x}(e) \leq |U| - 1 \qquad \forall \emptyset \neq U \subseteq V.$$

(Rank)

First, we note that the circuit imbalance of (Rank) is exponential; this follows from one of the results presented in Section 2. In combination with the exponential number of constraints, a full and interpretable characterization of the whole set of circuits of (Rank) is unlikely, and we dedicate the section to studying the 0/1 circuits of (Rank) and walks along them within (MWF).

In Section 4.1, we begin by devising a number of properties that 0/1 circuits or non-circuits must satisfy. First, we show in Lemma 4.2 that unit vectors are circuits of (Rank) and that no other uniform-sign 0/1 vectors (i.e., 0/1 vectors where all nonzero entries have the same sign) are circuits. This allows us to frame the main discussion as that of mixed-sign vectors which have at least one positive and one negative entry. As a key tool to this end, we introduce the idea of balanced vertex sets, where the values of induced edges "cancel out", and imbalanced vertex sets, where they do not.

Recall that, to check whether a given 0/1 vector is a circuit, we have to check whether there exists a vector of smaller, i.e., strictly included support with respect to (Rank). If a single edge could be dropped to arrive at such a vector, then that edge is not in a balanced set, and vice versa (Lemma 4.3). This implies that all edges in the support of a circuit lie in *some* balanced set. As the number of vertex subsets is exponential in the size of V, the property of an edge *not* being in a balanced set is very restrictive. In Lemma 4.4, this allows us to prove that many mixed-sign 0/1 vectors with disconnected edge sets are circuits. We conclude this first subsection by proving that "alternating" (and connected) graph structures (reminiscent of alternating paths and cycles in the setting of matchings) correspond to 0/1 circuits of (Rank), as do certain generalizations of these structure; see Lemmas 4.5, 4.6, and 4.7). These structures are of interest due to their connection to classical combinatorial algorithms; see for example [8].

In Section 4.2, we prove a set of more general properties that characterize mixed-sign 0/1 vectors as non-circuits. Notably, we show that for 0/1 non-circuits, either it is possible to drop a single edge to obtain a smaller support (Lemma 4.9 and Corollary 4.10), or the the support of the non-circuit 1) has to be the disjoint union of edge sets which induce connected graphs of diameter at most 5, and 2) has to induce a connected graph itself. Thus, in this latter case, the support of a 0/1 non-circuit must be of low diameter itself (Theorems 4.11 and 4.12). This implies that, outside of special cases, 0/1 vectors with an edge set of diameter greater than 10 must be circuits.

While we do not have, and did not expect, a full characterization of 0/1 circuits for (Rank), the insight gained allows us to prove surprisingly strong circuit diameter bounds for (MWF) in Section 4.3. For general graphs, we show a constant upper bound of 9 (Theorem 4.13), which improves to 7 for complete graphs (Theorem 4.14). We conclude by proving a lower bound of 3 (and for most graphs, 4) in Theorem 4.15. These results, where diameters range between 3 and 9 (or in special cases, between 4 and 7), contrast with diameter upper bounds of 1 or 2 in the literature for problems such as TSP and matching [25].

Finally, in Section 5 we conclude with some remarks and discuss some natural directions of future work.

## 2 Exponential Circuit Imbalance from Graph Problems

In this section we explore a variety of seemingly-natural sets of constraints defined over the edges of a graph whose inclusion in a linear system guarantees it to have at least exponential circuit imbalance. Our first theorem (Theorem 2.1) shows that even a small collection (i.e., polynomially sized) of relatively "simple" constraints is enough to guarantee exponential circuit imbalance. Many LPs from combinatorial optimization have a number of constraints which are exponential in the number of variables. Since, in general, the number of circuits grows exponentially in the number of constraints, it is not surprising to find that such LPs often also have exponential circuit imbalance measure. This holds, for example, for the Matching LP. A particularly surprising consequence of Theorem 2.1 is that only a polynomially sized subset of the constraints of the Matching LP (i.e., those described by point 1. in the theorem) are necessary to already give exponential circuit imbalance. We go on to show analogous results for other structurally simple, polynomially sized sets of constraints. In our view, this

underscores a general difficulty of characterizing *all* circuits of LPs from combinatorial optimization, and motivates a focus on a restricted attention to just the 0/1 circuits (or, in general, a subset of circuits which is interpretable, characterizable, and sufficient to be useful).

Before we state and prove Theorem 2.1, we recall a useful notation and fact of which we will make use in the remainder of this section. We will use Landau notation to describe the circuit imbalance. Recall the following definition.

**Definition 9.** Let  $f, g : \mathbb{Z}^+ \to \mathbb{R}^+$ . We say that f(n) is  $\Omega(g(n))$  (or  $f(n) \in \Omega(g(n))$ ) if there exists a real constant c > 0 and an integer constant  $n_0 \ge 1$  such that  $f(n) \ge c \cdot g(n)$  for every integer  $n \ge n_0$ .

The following simple observation on a linear system with four variables will be used repeatedly in our proofs.

If

$$b + c = a, b + d = a$$

, and  $c + d = a$ , then  $b = c = d = \frac{1}{2}a$ . (1)

We now state Theorem 2.1 Recall that  $\mathcal{H}$  denotes the supports of the rows of an inequality constraint matrix, as defined in Section 1.2.

**Theorem 2.1.** Let G = (V, E) be a simple, loop-free graph and  $\mathcal{H} \subseteq 2^E$ . We have that  $\kappa(\mathcal{H}) \in \Omega(2^{|E|})$  whenever:

- 1.  $\mathcal{H} \supseteq \{E[U] : U \subseteq V, |U| = 5\},\$

- 2.  $\mathcal{H} \supseteq \{H : H \text{ is the edge set of a path}, |H| = 4\},$

- 3.  $\mathcal{H} \supseteq \{H : |H| = 3\},\$

*Proof.* We first prove conclusion 1. explicitly. As we will see later, points 2. and 3. follow from the fact that such collections of edge sets give rise to the same relationships between the same variables.

Consider the graph  $G_k$  with vertex set  $V = \{w_0\} \cup \{t_i, u_i, v_i, w_i : 1 \le i \le k\}$  and edge set  $E = \{t_i u_i, t_i v_i, v_i w_i, u_i w_i : 1 \le i \le k\} \cup \{w_i t_{i+1} : 0 \le i \le k-1\}.$

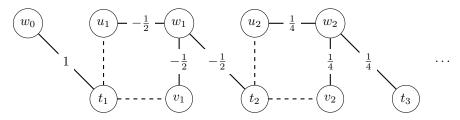

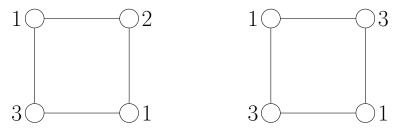

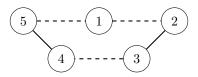

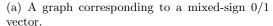

Let **g** be such that  $\mathbf{g}(w_i t_{i+1}) = (-2)^{-i}$  for all  $0 \le i \le k-1$ ,  $\mathbf{g}(t_i u_i) = \mathbf{g}(t_i v_i) = 0$  for all  $1 \le i \le k$ , and  $\mathbf{g}(u_i w_i) = \mathbf{g}(v_i w_i) = (-2)^{-i}$ . See Figure 1 for such a construction of **g**.

There exists a circuit **h** with supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ . We will show that in any such circuit **h**,  $|\mathbf{h}(w_it_{i+1})| = 2|\mathbf{h}(w_{i+1}t_{i+2})|$  for all  $0 \le i \le k-2$ . We have that for all  $1 \le i \le k-1$ ,

$$\mathbf{g}(E[\{w_{i-1}, t_i, u_i, v_i, w_i\}]) = 0, \tag{2}$$

$$\mathbf{g}(E[\{w_{i-1}, t_i, u_i, w_i, t_{i+1}\}]) = 0, \text{ and}$$

(3)

$$\mathbf{g}(E[\{w_{i-1}, t_i, v_i, w_i, t_{i+1}\}]) = 0. \tag{4}$$

Since supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ , we also have that for all  $1 \le i \le k-1$ ,

$$\mathbf{h}(E[\{w_{i-1}, t_i, u_i, v_i, w_i\}]) = 0,$$

$$\mathbf{h}(E[\{w_{i-1}, t_i, u_i, w_i, t_{i+1}\}]) = 0, \text{ and }$$

$$\mathbf{h}(E[\{w_{i-1}, t_i, v_i, w_i, t_{i+1}\}]) = 0.$$

If for all  $1 \le i \le k-1$  we let  $a = -\mathbf{h}(w_{i-1}t_i)$ , the above implies that

$$\mathbf{h}(u_i w_i) + \mathbf{h}(v_i w_i) = a,$$

$$\mathbf{h}(v_i w_i) + \mathbf{h}(w_i t_{i+1}) = a, \text{ and }$$

$$\mathbf{h}(u_i w_i) + \mathbf{h}(w_i t_{i+1}) = a.$$

By (1),  $\mathbf{h}(u_i w_i) = \mathbf{h}(v_i w_i) = \mathbf{h}(w_i t_{i+1}) = \frac{1}{2}a$ . It follows that  $|\mathbf{h}(w_{i-1} t_i)| = 2|\mathbf{h}(w_i t_{i+1})|$  for all  $1 \le i \le k-1$ . Thus,  $\kappa(\mathcal{H}) \in \Omega(2^{|E|})$ , as desired.

Finally, we observe that in the above construction, the exact same relations between  $\mathbf{h}(u_i w_i)$ ,  $\mathbf{h}(v_i w_i)$ , and  $\mathbf{h}(w_i t_{i+1})$  can be achieved if  $\mathcal{H} \supseteq \{H : H \text{ is the edge set of a path, } |H| = 4\}$  or if  $\mathcal{H} \supseteq \{H : |H| = 3\}$ , giving the desired results. In particular, consider the edge sets  $E[\{w_{i-1}, t_i, u_i, v_i, w_i\}]$ ,  $E[\{w_{i-1}, t_i, u_i, w_i, t_{i+1}\}]$ , and  $E[\{w_{i-1}, t_i, v_i, w_i, t_{i+1}\}]$  utilized in equations (2), (3), and (4), respectively. Denote by S the set

$$E[\{w_{i-1}, t_i, u_i, v_i, w_i\}] \cap \operatorname{supp}(\mathbf{g}) = \{w_{i-1}t_i, u_iw_i, w_iv_i\}.$$

If we let P denote the path  $\{w_{i-1}t_i, t_iu_i, u_iw_i, w_iv_i\}$ , then we have that  $P \cap \text{supp}(\mathbf{g}) = S$  and |P| = 4. Thus, the equation (2) holds in the case that  $\mathcal{H} \supseteq \{H : H \text{ is the edge set of a path}, |H| = 4\}$ . Analogous paths exist for equations (3) and (4). Thus, in this case we infer the same relationships between the same variables, as desired.

Likewise, the set S defined above is of size 3, and of course  $S \cap \text{supp}(\mathbf{g}) = S$ . Thus, the equation (2) holds in the case that  $\mathcal{H} \supseteq \{H : |H| = 3\}$ . Analogous inferences hold for (3) and (4). Thus, in this case we again infer the same relationships between the same variables, as desired.

Figure 1: The construction of the vector  $\mathbf{g}$  in the proof of Theorem 2.1. Each edge is labeled with its corresponding value in  $\mathbf{g}$ , where dashed lines indicate a value of 0.

In fact, we can show that we get at least exponential circuit imbalance if we consider only paths of size 3.

**Theorem 2.2.** If  $\mathcal{H} \supseteq \{H : H \text{ is the edge set of a path}, |H| = 3\}, \text{ then } \kappa(\mathcal{H}) \in \Omega(2^{|E|}).$

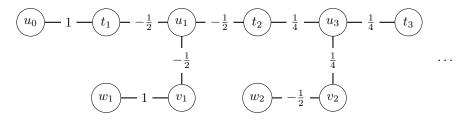

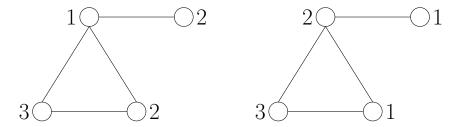

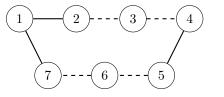

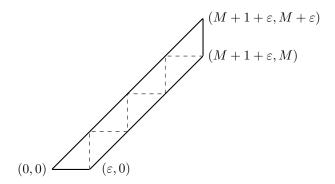

*Proof.* Consider the graph  $G_k$  with vertex set  $V = \{u_0\} \cup \{t_i, u_i, v_i, w_i : 1 \le i \le k\}$  and edge set  $E = \{u_{i-1}t_i, t_iu_i, u_iv_i, v_iw_i\}$ . Let  $\mathbf{g}$  be such that  $\mathbf{g}(u_it_{i+1}) = (-2)^{-i}$  for all  $0 \le i \le k-1$ ,  $\mathbf{g}(t_iu_i) = \mathbf{g}(u_iv_i) = (-2)^{-i}$  for all  $1 \le i \le k$ , and  $\mathbf{g}(v_iw_i) = (-2)^{-(i-1)}$  for all  $1 \le i \le k$ . See Figure 2 for such a construction of  $\mathbf{g}$ .

There exists a circuit  $\mathbf{h}$  with supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ . We will show that for any such circuit,  $|\mathbf{h}(u_{i-1}t_i)| = 2|\mathbf{h}(u_it_{i+1})|$  for all  $1 \le i \le k-1$ . We have that for all  $1 \le i \le k-1$

$$\mathbf{g}(\{u_{i-1}t_i, t_iu_i, u_iv_i\}) = 0,$$

$$\mathbf{g}(\{t_iu_i, u_iv_i, v_iw_i\}) = 0,$$

$$\mathbf{g}(\{w_iv_i, v_iu_i, u_it_{i+1}\}) = 0, \text{ and }$$

$$\mathbf{g}(\{u_{i-1}t_i, t_iu_i, u_it_{i+1}\}\}) = 0.$$

Since supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ , we also have that for all  $1 \le i \le k-1$

$$\mathbf{h}(\{u_{i-1}t_i, t_iu_i, u_iv_i\}) = 0, \tag{5}$$

$$\mathbf{h}(\lbrace t_i u_i, u_i v_i, v_i w_i \rbrace) = 0, \tag{6}$$

$$\mathbf{h}(\{w_i v_i, v_i u_i, u_i t_{i+1}\}) = 0, \text{ and}$$

(7)

$$\mathbf{h}(\{u_{i-1}t_i, t_iu_i, u_it_{i+1}\}) = 0. \tag{8}$$

It follows from equations (5) and (6) that for all  $1 \le i \le k$

$$\mathbf{h}(u_{i-1}t_i) = -(\mathbf{h}(t_iu_i) + \mathbf{h}(u_iv_i)) = \mathbf{h}(v_iw_i)$$

Then, if for all  $1 \le i \le k-1$  we let  $a = -\mathbf{h}(u_{i-1}t_i) = -\mathbf{h}(v_iw_i)$ , it follows from equations (6), (7), and (8) that

$$\mathbf{h}(t_i u_i) + \mathbf{h}(u_i v_i) = a,$$

$$\mathbf{h}(u_i v_i) + \mathbf{h}(u_i t_{i+1}) = a, \text{ and }$$

$$\mathbf{h}(t_i u_i) + \mathbf{h}(u_i t_{i+1}) = a.$$

By (1),  $\mathbf{h}(t_i u_i) = \mathbf{h}(u_i v_i) = \mathbf{h}(u_i t_{i+1}) = \frac{1}{2}a$ . It follows that  $|\mathbf{h}(u_{i-1}t_i)| = 2|\mathbf{h}(u_i t_{i+1})|$  for all  $1 \le i \le k-1$ . Thus,  $\kappa(\mathcal{H}) \ge \Omega(2^{|E|})$ , as desired.

Figure 2: The construction of the vector  $\mathbf{g}$  in the proof of Theorem 2.2. Each edge is labeled with its corresponding value in  $\mathbf{g}$ .

Given that the circuit imbalance measure is unbounded for edge sets of short paths, a natural question is whether this holds true for edge sets of short cycles. We see this is true by a very similar construction in the next result.

**Theorem 2.3.** If  $\mathcal{H} \supseteq \{H : H \text{ is the edge set of a cycle}, |H| \leq 4\}$ , then  $\kappa(\mathcal{H}) \in \Omega(2^{|E|})$ .

*Proof.* Consider the graph  $G_k$  with vertex set  $V = \{u_i, v_i : 0 \le i \le k\}$  and edge set

$$E = \{u_i v_i, u_i u_{i+1}, u_i v_{i+1}, v_i u_{i+1}, v_i v_{i+1} : 0 \le i \le k-1\} \cup \{u_k v_k\}.$$

Let **g** be such that  $\mathbf{g}(u_i v_i) = (-2)^{-i}$  for all  $0 \le i \le k$ ,

$$\mathbf{g}(u_{i-1}u_i) = \mathbf{g}(v_{i-1}u_i) = (-2)^{-i}$$

for all  $1 \le i \le k$ , and

$$\mathbf{g}(u_{i-1}v_i) = \mathbf{g}(v_{i-1}v_i) = 0$$

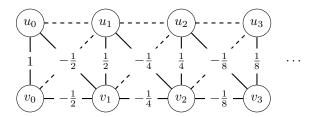

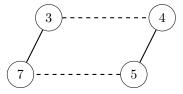

for all  $1 \le i \le k$ . See Figure 3 for such a construction of **g**.

There exists a circuit **h** with supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ . We will show that for any such circuit,  $|\mathbf{h}(u_iv_i)| = 2|\mathbf{h}(u_{i+1}v_{i+1})|$  for all  $0 \le i \le k-1$ . We have that for all  $0 \le i \le k-1$ ,

$$\mathbf{g}(\{u_iv_i, v_iu_{i+1}, u_iu_{i+1}\}) = 0,$$

$$\mathbf{g}(\{u_iv_i, v_iu_{i+1}, u_{i+1}v_{i+1}, u_iv_{i+1}\}) = 0, \text{ and }$$

$$\mathbf{g}(\{u_iv_i, v_iv_{i+1}, v_{i+1}u_{i+1}, u_iu_{i+1}\}) = 0.$$

Since supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ , we also have that for all  $0 \le i \le k-1$

$$\mathbf{h}(\{u_iv_i, v_iu_{i+1}, u_iu_{i+1}\}) = 0,$$

$$\mathbf{h}(\{u_iv_i, v_iu_{i+1}, u_{i+1}v_{i+1}, u_iv_{i+1}\}) = 0, \text{ and }$$

$$\mathbf{h}(\{u_iv_i, v_iv_{i+1}, v_{i+1}u_{i+1}, u_iu_{i+1}\}) = 0.$$

If for all  $0 \le i \le k-1$  we let  $a = -\mathbf{h}(u_i v_i)$ , the above implies that

$$\begin{aligned} \mathbf{h}(u_i u_{i+1}) + \mathbf{h}(v_i u_{i+1}) &= a, \\ \mathbf{h}(v_i u_{i+1}) + \mathbf{h}(u_{i+1} v_{i+1}) &= a, \text{ and} \\ \mathbf{h}(u_i u_{i+1}) &+ \mathbf{h}(u_{i+1} v_{i+1}) &= a. \end{aligned}$$

By (1),  $\mathbf{h}(u_i u_{i+1}) = \mathbf{h}(v_i u_{i+1}) = \mathbf{h}(u_{i+1} v_{i+1}) = \frac{1}{2}a$ . It follows that  $|\mathbf{h}(u_i v_i)| = 2|\mathbf{h}(u_{i+1} v_{i+1})|$  for all  $1 \le i \le k-1$ . Thus,  $\kappa(\mathcal{H}) \ge \Omega(2^{|E|})$ , as desired.

Figure 3: The construction of the vector  $\mathbf{g}$  in the proof of Theorem 2.3. Each edge is labeled with it's corresponding value in  $\mathbf{g}$ , where dashed lines indicate a value of 0.

Finally, we note that  $\mathcal{H} = \{\delta(v) : v \in V\}$ —the collection such that  $B(G, \mathcal{H})$  is the inequality constraint matrix of the fractional matching polytope—can be equivalently expressed as

$$\mathcal{H} = \{H : H \text{ is the edge set of a maximal star subgraph}\},$$

where H is the edge set of a maximal star subgraph if there does not exist  $e \in E$  such that  $H \cup \{e\}$  is also the edge set of a star subgraph of G. As noted in Section 1.2, this collection  $\mathcal{H}$  gives constant circuit imbalance [18]. Since the collection of all maximal star subgraphs gives constant circuit imbalance, it is natural to wonder whether the collection of all star subgraphs gives sub-exponential circuit imbalance. We now show that this is not the case.

**Theorem 2.4.** If  $\mathcal{H} \supseteq \{H : H \text{ is the edge set of a star subgraph}, |H| \geq 2\}$ , then  $\kappa(\mathcal{H}) \in \Omega(2^{|E|})$ .

*Proof.* Consider the graph  $G_k$  with vertex set  $V = \{u_i, v_i : 0 \le i \le k\}$  and edge set

$$E = \{u_i v_i, v_i u_{i+1} v_i v_{i+1} : 0 < i < k-1\} \cup \{u_k v_k\}$$

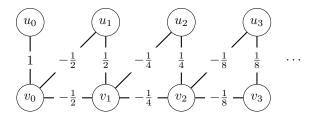

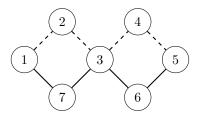

Let **g** be such that  $\mathbf{g}(u_i v_i) = 2^{-i}$  and  $\mathbf{g}(v_{i-1} u_i) = \mathbf{g}(v_{i-1} v_i) = -(2^{-i})$  for  $1 \le i \le k$ . See Figure 4 for such a construction of **g**.

There exists a circuit **h** with supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ . We will show that for any such circuit,  $\mathbf{h}(u_iv_i) = 2\mathbf{h}(u_{i+1}v_{i+1})$  for all  $0 \le i \le k-1$ . We have that for all  $0 \le i \le k-1$ ,

$$\mathbf{g}(\{u_i v_i, v_i u_{i+1}, v_i v_{i+1}\}) = 0,$$

$$\mathbf{g}(\{v_i u_{i+1}, u_{i+1} v_{i+1}\}) = 0, \text{ and}$$

$$\mathbf{g}(\{v_i v_{i+1}, u_{i+1} v_{i+1}\}) = 0.$$

Since supp $(B\mathbf{h}) \subseteq \text{supp}(B\mathbf{g})$ , we also have that for all  $0 \le i \le k-1$

$$\mathbf{h}(\{u_i v_i, v_i u_{i+1}, v_i v_{i+1}\}) = 0, \tag{9}$$

$$\mathbf{h}(\{v_i u_{i+1}, u_{i+1} v_{i+1}\}) = 0, \text{ and}$$

(10)

$$\mathbf{h}(\{v_i v_{i+1}, u_{i+1} v_{i+1}\}) = 0. \tag{11}$$

By equations (10) and (11) we have that for  $0 \le i \le k-1$ ,

$$-\mathbf{h}(v_i u_{i+1}) = \mathbf{h}(u_{i+1} v_{i+1}) = -\mathbf{h}(v_i v_{i+1}),$$

and so by equation (9) we have that for  $0 \le i \le k-1$

$$\mathbf{h}(u_i v_i) = -(\mathbf{h}(v_i u_{i+1}) + \mathbf{h}(v_i v_{i+1})) = 2\mathbf{h}(u_{i+1} v_{i+1}).$$

Thus,  $\kappa(\mathcal{H}) \in \Omega(2^{|E|})$ , as desired.

Figure 4: The construction of the vector  $\mathbf{g}$  in the proof of Theorem 2.4. Each edge is labeled with its corresponding value in  $\mathbf{g}$ .

## 3 The Coloring Problem

In this section, we focus on the problem of vertex-coloring a graph with n vertices. Specifically, we are interested in analyzing the circuits of the *fractional* coloring LP, i.e., the linear programming relaxation of the coloring problem (see Definition 14). As we will show in Section 3.2, this LP has at least exponential circuit imbalance measure. In keeping with the broad themes and objectives of this work, we therefore explore the degree to which the 0/1 circuits alone are sufficiently useful in settings where one might ordinarily utilize the full set of circuits. What we find is that the 0/1 circuits of the fractional coloring LP suffice to allow one to move between any pair of *proper* colorings (i.e., between the integer solutions of the LP).

As we show in Theorem 3.2 and Corollary 3.3, the 0/1 circuits that move from a proper coloring to a proper coloring can be interpreted as a very natural generalization of so-called Kempe swaps. Kempe swaps are a classical notion in the theory of graph coloring which give a natural and, in some sense, minimal way to reconfigure a coloring. However, it is known that in some circumstances, Kempe swaps do not suffice to allow one to reconfigure any coloring to any other coloring. In contrast, a consequence of our results is that these generalized Kempe swaps which come from 0/1 circuits do suffice for this purpose.

Moreover, we show that this is *not* because the 0/1 circuits constitute so large a portion of  $\{0, \pm 1\}^n$  as to make it trivial to move between two colorings. To explain this by way of contrast, it is known that the 0/1 circuits of the Matching and TSP LPs contain so many vectors from  $\{0, \pm 1\}^n$  that almost all pairs of matchings (resp. TSP tours) are one circuit step apart [25]. In Theorem 3.5 we show that reconfiguring two proper colorings via these generalized Kempe swaps may require up to n steps.

Before proceeding to the results, we will first define all the necessary concepts and terminology.

#### 3.1 Kempe Dynamics

We begin with the graph-theoretic definitions needed to study the polytopes in this section and Section 4. Let G = (V, E) be a graph with the vertex set V, the edge set E, and the minimum degree  $\delta(G)$ . Let  $S \subseteq V$  be any subset of vertices of G. The *induced subgraph*, G[S] is the graph whose vertex set is S and whose edge set consists of all the edges in E that have both endpoints in S. An *independent set* in a graph G, is a set  $I \subseteq V$  such that no two vertices of I are adjacent in G.

A coloring of the vertices of a graph is an assignment of colors to the vertices of a graph. We say that a coloring of the vertices of G is proper if any two adjacent vertices receive different colors. A graph G is t-colorable if it has a proper coloring using at most t colors. Given a set  $\tau = \{1, 2, ... t\}$ , we say that the graph is  $\tau$ -colored if we color the vertices using all the colors in the set  $\tau$ . We denote a  $\tau$ -colored graph as  $G(\tau)$ . Note that this notation does not, in itself, specify the coloring, and each color class forms an independent set. The chromatic number of a graph G, denoted  $\chi(G)$ , is the smallest integer t such that G is t-colorable. We formally define this as follows.

**Definition 10.** Let G = (V, E) be a graph and let t be a positive integer. A t-coloring of G is a function  $\phi : V \to \{1, 2, ..., t\}$  such that if  $v_i$  and  $v_j$  are adjacent then  $\phi(v_i) \neq \phi(v_j)$ . The numbers 1, 2, ..., t are called the colors of the coloring  $\phi$ .

Figure 5: Left: Proper coloring of the cycle on four vertices using colors {1,2,3}. Right: Proper coloring using the minimum number of colors of the cycle on four vertices using colors {1,3}.

We follow the standard notation found in [28] for the following definitions. The coloring problem is defined as determining whether it is possible to color the vertices of a graph with a limited number of colors, say t, such that the coloring is proper. The t-colorability problem for  $t \geq 3$  is an NP-complete problem [26], and as a result determining the chromatic number of a graph is NP-complete. Traditionally, the coloring problem is modeled as the integer program below.

**Definition 11.** Let G = (V, E) be a graph and  $\tau = \{t_1, \ldots, t_r\}$  a set of colors. The following system is the integer program formulation for the coloring problem.

$$\begin{split} \mathbf{x} \in \mathbb{R}^{|V| \times r} : \sum_{i \in K} \mathbf{x}(v, i) &= 1 \ \forall v \in V \\ \mathbf{x}(v, i) + \mathbf{x}(u, i) &\leq 1 \ \forall i \in \tau, \ uv \in E \\ \mathbf{x}(v, i) \in \{0, 1\} \ \forall v \in V, \forall i \in \tau \end{split}$$

The first set of constraints ensures that each vertex in our graph receives a color. The second set of constraints ensures that if two vertices u and v are connected via an edge they must receive a different color. We define the coloring characteristic vector to index which vertices have been assigned which color.

**Definition 12.** Let G = (V, E) be a graph and  $\tau = \{t_1, \ldots, t_r\}$  a set of colors. Let  $G(\tau)$  be a vertex  $\tau$ -colored graph. We define the **coloring characteristic vector** of  $G(\tau)$  to be  $\mathbf{X}(G(\tau)) \in \mathbb{R}^{|V| \times |\tau|}$  where  $\mathbf{X}(G(\tau))_{j,t} = 1$  if vertex j is colored with color t and 0 otherwise.

The entries of this vector are exactly the values of the variables  $\mathbf{x}(v,i)$ . Relaxing the integrality constraints in the above integer programming formulation allows us to investigate the circuits associated with the coloring problem. In this relaxation, extreme-point solutions of the feasible region are able to have fractional values. This corresponds to assigning a single vertex a "fractional mix" of the available colors (provided this assignment still adheres to the constraints). This gives rise to the following definition of the fractional chromatic number.

**Definition 13.** Let I(G) denote the set of all independent sets of vertices of a graph G, and let I(G, u) denote the independent sets of G that contain the vertex u. A **fractional coloring** of G is a non-negative real function f on I(G) such that for any vertex u of G,

$$\sum_{S \in I(G,u)} f(S) \ge 1.$$

The sum of the values of f is called the fractional coloring's weight, and the minimum possible weight of a fractional coloring is called the fractional chromatic number  $\chi_f(G)$ .

The following LP relaxation of the coloring IP is the formulation of the fractional coloring problem which we will consider. In contrast to Definition 13, which assigns weights to independent sets (which are understood to be sets of vertices who receive a common fraction of a common color), it directly assigns fractions of colors to vertices one at a time.

**Definition 14.** Let G = (V, E) be a graph and  $\tau = \{t_1, \dots, t_r\}$  a set of colors. The fractional coloring problem has the following formulation:

$$\mathbf{x} \in \mathbb{R}^{|V| \times r} : \sum_{i \in K} \mathbf{x}(v, i) = 1 \quad \forall v \in V$$

$$\mathbf{x}(v, i) + \mathbf{x}(u, i) \le 1 \quad \forall i \in \tau, uv \in E$$

$$\mathbf{x}(v, i) \ge 0 \quad \forall v \in V, \forall i \in \tau$$

The polytope associated with this continuous relaxation is the fractional coloring polytope. This is in contrast to the coloring polytope which is defined as the convex hull of the feasible solutions to the IP formulation found in Definition 11. We note that, although the fractional coloring polytope has fractional extreme-points, we will still be predominantly concerned with the use of circuits to move between integral extreme-points. That is, in this context, the circuits are being considered to the extent that they allow us to reconfigure proper t-colorings into other proper t-colorings.

In graph-theoretic terms, we say that two t-colorings,  $\phi_1$  and  $\phi_2$ , are Kempe equivalent (or simply equivalent) if there exists a sequence of so-called Kempe swaps (defined below) which transform the first coloring into the second coloring. By the definition of a Kempe swap, all intermediate colorings are proper. Equivalently, we can define the reconfiguration graph H whose vertex set is the set of t-colorings of G, and where two colorings are adjacent if they differ by a single Kempe swap. Two colorings  $\phi_1$  and  $\phi_2$  are hence equivalent if their corresponding vertices lie in the same connected component of H. Below, we formally define these terms.

**Definition 15.** Let G = (V, E) be a graph and  $\phi : V \to \tau$  be a proper coloring where  $|\tau| \geq 2$ , and for each  $x \in \tau$ , let  $V^x = \{v \in V : \phi(v) = x\}$ . Given distinct colors  $a, b \in \tau$ , an (a,b)-Kempe chain of  $(G,\phi)$  is a connected component of  $G[V^a \cup V^b]$ . We say a subgraph C of G is a Kempe chain of  $(G,\phi)$  if it is an (a,b)-Kempe chain for some colors a and b. When  $\phi$  is clear from context, we may just refer to (a,b)-Kempe chains and Kempe chains of G.

Given an (a, b)-Kempe chain, we can swap the colors a and b preforming a so-called Kempe swap.

**Definition 16.** Given G = (V, E), a proper coloring  $\phi : V \to S$  with  $|S| \ge 2$ , distinct colors  $a, b \in S$ , and an (a, b)-Kempe chain C of  $(G, \phi)$ , we say a coloring  $\phi' : V \to S$  is obtained from  $\phi$  via a **Kempe swap** on C if  $\phi'(v) = \phi(v)$  for all  $v \notin C$ ,  $\phi'(v) = a$  if  $v \in C$  and  $\phi(v) = b$ , and  $\phi'(v) = b$  if  $v \in C$  and  $\phi(v) = a$ .

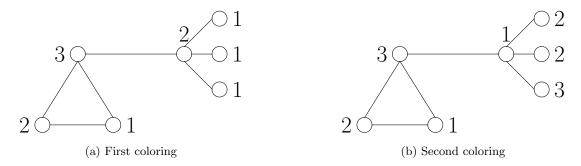

The following classical notion of Kempe equivalence will play a crucial role in defining the circuits of the fractional coloring polytope. We provide an example of two colorings that are Kempe equivalent in Figure 6.

Figure 6: Two Kempe equivalent colorings that differ by a Kempe swap.

**Definition 17.** Two colorings are **Kempe equivalent** if we can transform one into the other through a sequence of Kempe swaps. If all pairs of t-colorings are Kempe equivalent, then we say the graph is t-**Kempe mixing**.

An important note here is that Kempe chains almost always suffice to achieve reachability between any pair of colorings (i.e., graphs are usually t-Kempe mixing) as long as the graph in question has a low enough minimum degree in relation to the number of colors available. Combining several previous results of other authors, we get that two colorings are Kempe equivalent if there are enough colors related to the maximum degree of your graph.

**Theorem 3.1** (see [2], [27], [20]). Let  $3 \le \Delta \le k$ . If G is a connected graph with maximum degree  $\Delta$ , then all k-colorings of G are Kempe-equivalent, unless G is the triangular prism.

Due to this condition, current research on Kempe chains is concerned with the so-called t-Kempe diameter of any two t-colorings [3, 14].

**Definition 18.** The t-Kempe-diameter of a graph G is defined to be the maximum length of the shortest transformation between any two t-colorings of G. If a graph is not t-Kempe mixing, then we say the diameter is  $\infty$ .

An important observation here is that Kempe swaps correspond to edges of the coloring polytope (though there are edges that do not correspond to Kempe swaps). Since each vertex in the reconfiguration graph will also correspond to an extreme-point of the coloring polytope, and since each Kempe swap corresponds to movement along a circuit, the Kempe diameter gives an upper bound on the circuit diameter.

We now define a natural generalization of Kempe chains which allow for more than two colors in each chain. As we will show, swaps along these generalized Kempe chains will correspond to 0/1 circuits of the fractional coloring polytope which are feasible at extreme-points corresponding to proper colorings (Proposition 3.4).

**Definition 19.** Let G = (V, E) be a graph and  $\phi : V \to \tau$  be a proper coloring where  $|\tau| \geq k$ , and for each  $x \in \tau$ , let  $V^x = \{v \in V : \phi(v) = x\}$ . Given distinct colors  $a_1, \ldots, a_k \in S$ , an  $(a_1, \ldots, a_k)$ -Kempe chain of  $(G, \phi)$  is a connected component of  $G[V^{a_1} \cup \cdots \cup V^{a_k}]$ . We say a subgraph C of G is a generalized Kempe chain of  $(G, \phi)$  if it is an  $(a_1, \ldots, a_k)$ -Kempe chain of  $(G, \phi)$  for some colors  $a_1, \ldots, a_k$ . When  $\phi$  is clear from context, we may just refer to  $(a_1, \ldots, a_k)$ -Kempe chains as generalized Kempe chains of G.

We define a similar notion for a generalized Kempe swap.

**Definition 20.** Given G = (V, E), a proper coloring  $\phi : V \to \tau$  with  $|\tau| \ge k$ , distinct colors  $a_1, \ldots, a_k \in \tau$ , and an  $(a_1, \ldots, a_k)$ -Kempe chain C of  $(G, \phi)$ , we say a proper  $\tau$ -coloring  $\phi' : V \to \tau$  is obtained from  $\phi$  via a **generalized Kempe swap** on C if

1.

$$\phi'(v) = \phi(v)$$

for all  $v \notin C$ ,

- 2.  $\phi'(v) \neq \phi(v)$  if  $v \in C$ , and

- 3. for all edges uv in C, either  $\phi'(u) = \phi(v)$  or  $\phi'(v) = \phi(u)$ .

This final condition requires that if two adjacent vertices change colors, at least one of them receives the other's color. Note that in the above definition, if k = 2 we recover exactly the definition of an (a, b)- Kempe chain. We can now define a correspondence from the coloring characteristic vector to a Kempe chain.

**Definition 21.** Given  $\tau$ -colored graph  $G(\tau)_1$  and  $G(\tau)_2$  with colorings  $\phi_1$  and  $\phi_2$  such that  $\phi_2$  is obtained from  $\phi_1$  via a generalized Kempe swap, we say that this Kempe swap **corresponds** to the vector  $\mathbf{s} = \mathbf{X}(G(\tau)_2) - \mathbf{X}(G(\tau)_1)$ .

Next, we show the circumstances under which two characteristic vectors of proper colorings differ by a circuit.

**Theorem 3.2.** Let G = (V, E) be a graph and  $G(\tau)_1$  and  $G(\tau)_2$  be two different proper  $\tau$ -colorings of G. The vector  $\mathbf{s} := \mathbf{X}(G(\tau)_2) - \mathbf{X}(G(\tau)_1)$  is a circuit of the fractional coloring polytope if and only if the subgraph G(s) given by the vertices

$$V(\mathbf{s}) = \{v : \mathbf{s}(v, i) \neq 0 \text{ for some } i \in \tau\}$$

and by the edges

$$E(\mathbf{s}) = \{uv \in E : \mathbf{s}(u,i) + \mathbf{s}(v,i) = 0, \mathbf{s}(u,i) \neq 0 \text{ for some } i \in \tau\}$$

is connected.

*Proof.* We first handle the case where  $V(\mathbf{s}) = \{v\}$  for some vertex v. In this case,  $G(\tau)_1$  and  $G(\tau)_2$  only differ at v. Without loss of generality, say v has color 1 in  $G(\tau)_1$  and color 2 in  $G(\tau)_2$ . If  $\mathbf{s}$  is not a circuit, there exists a circuit  $\mathbf{s}'$  whose support is contained in the support of  $\mathbf{s}$ , i.e.,  $\mathbf{s}'(u,k) = 0$  for all  $(u,k) \notin \{(v,1),(v,2)\}$ . Moreover, since  $\mathbf{s}(v,1) + \mathbf{s}(v,2) = 0$ , we have that  $\mathbf{s}'(v,1) + \mathbf{s}'(v,2) = 0$ . Since  $\mathbf{s}' \neq 0$ , it follows that  $\mathbf{s}'$  is a scalar multiple of  $\mathbf{s}$ .

Now, suppose that  $G(\mathbf{s})$  is disconnected. Let  $G'(\mathbf{s})$  be a connected component of  $G(\mathbf{s})$ . Let  $\mathbf{s}'$  be the vector given by  $\mathbf{s}'(v,k) = \mathbf{s}(v,k)$  if v is a vertex of  $G'(\mathbf{s})$  and zero otherwise. It is easy to see that the support of  $\mathbf{s}'$  is strictly contained in the support of  $\mathbf{s}$  and  $\mathbf{s}'(u,k) + \mathbf{s}'(v,k) = 0$  whenever  $\mathbf{s}(u,k) + \mathbf{s}(v,k) = 0$ . Thus,  $\mathbf{s}$  is not a circuit.

Now, suppose that  $G(\mathbf{s})$  is connected. If  $\mathbf{s}$  is not a circuit, then there exists  $\mathbf{s}' \neq 0$  such that  $\mathbf{s}'(v,k) = 0$  whenever  $\mathbf{s}(v,k) = 0$  and  $\mathbf{s}'(v,k) + \mathbf{s}'(v,k) = 0$  whenever  $\mathbf{s}(v,k) + \mathbf{s}(v,k) = 0$ .

First, we show that if  $\mathbf{s}(v,k) \neq 0$ , then  $\mathbf{s}'(v,k) \neq 0$ . Suppose for the sake of a contradiction that there exist vertices v and colors k such that  $|\mathbf{s}(v,k)| > \mathbf{s}'(v,k) = 0$ , and let (v,k) be any such pair of vertex and color. Since  $G(\mathbf{s})$  is connected and contains more than one vertex, there exists a neighbor u of v such that  $\mathbf{s}(u,k)+\mathbf{s}(v,k)=0$ . Then  $\mathbf{s}'(u,k)+\mathbf{s}'(v,k)=0$ , and thus  $0=\mathbf{s}'(u,k)<|\mathbf{s}(u,k)|$ . By the connectedness of  $G(\mathbf{s})$ , it follows that  $\mathbf{s}'(v,k)=0$  for all  $v\in V(s)$  and all colors k, contradicting that  $\mathbf{s}'\neq 0$ .

Now, since the support of  $\mathbf{s}'$  is equal to the support of  $\mathbf{s}$  then there exist some u, v, and k such that  $\mathbf{s}(u,k)+\mathbf{s}(v,k)\neq 0$  and  $\mathbf{s}'(u,k)+\mathbf{s}'(v,k)=0$ . Since  $\mathbf{s}$  is the difference of two vectors in  $\{0,1\}^{V\times\tau}$ , it follows that  $\mathbf{s}(u,k)+\mathbf{s}(v,k)\in\{0,\pm 1,\pm 2\}$ . By assumption,  $\mathbf{s}(u,k)+\mathbf{s}(v,k)\neq 0$ , and if  $\mathbf{s}(u,k)+\mathbf{s}(v,k)=\pm 1$  then exactly one of  $\mathbf{s}(u,k)$  or  $\mathbf{s}(v,k)$  is zero, and thus exactly one of  $\mathbf{s}'(u,k)$  or  $\mathbf{s}'(v,k)$  is 0. Since  $\mathbf{s}'(u,k)+\mathbf{s}'(v,k)=0$ , we have that  $\mathbf{s}'(u,k)=\mathbf{s}'(v,k)=0$ , contradicting that the support of  $\mathbf{s}$  is equal to the support of  $\mathbf{s}'$ . Finally,  $\mathbf{s}(u,k)+\mathbf{s}(v,k)\neq \pm 2$  because this would imply that in one of the colorings  $G(\tau)_1$  or  $G(\tau)_2$ , u,v are adjacent vertices with the same color, a contradiction. Thus, no such  $\mathbf{s}'$  exists, and therefore  $\mathbf{s}$  is a circuit.

Corollary 3.3. If two proper  $\tau$ -colored graphs satisfy the hypotheses of Theorem 3.2, then the difference of their characteristic vectors corresponds to a generalized Kempe swap. For any colors  $a_1, \ldots, a_k$ , any  $(a_1, \ldots, a_k)$ -Kempe swap corresponds to a circuit of the fractional matching polytope.

Although we have shown that the difference of characteristic vectors of two proper colorings is a circuit if and only if those colorings differ by a generalized Kempe swap (which are themselves only defined on proper colorings), we observe that there are nevertheless 0/1 circuits of the coloring polytope which do not correspond to Kempe swaps. In particular, there exist improper colorings whose characteristic vectors differ by a circuit. Figure 7 exhibits two improper colorings of  $K_3$ , and it can be easily verified that the difference of their characteristic vectors is indeed a circuit of the coloring polytope.

Figure 7: Two improper colorings of  $K_3$  whose characteristic vectors differ by a circuit.

As mentioned in Section 1, 0/1 circuits are a useful tool in circuit augmentation, and so it is valuable to have a complete characterization of the set of 0/1 circuits. Recall also that we are primarily concerned with 0/1 circuits that allow us to move between *integral* extreme-point solutions of the fractional coloring polytope (i.e., those circuits which are differences of characteristic vectors of proper colorings) Although the example above shows that Theorem 3.2 does not describe all 0/1 circuits, it does succeed in describing all of the 0/1 circuits that we care about.

Next, we show that, at an extreme-point of the coloring polytope which corresponds to a proper coloring, all feasible 0/1 circuits correspond to generalized Kempe swaps. Note that this is not already implied by the previous results. In general, at an extreme-point solution in  $\{0,1\}^n$ , it is possible that moving along a feasible 0/1 circuit causes one to arrive at a non-integral (or even non-extreme-point) solution. We must first define the following, and then provide a formal statement and proof.

**Definition 22.** Given a graph G and a set of colors  $\tau$ , we say that a circuit  $\mathbf{s}$  of the fractional coloring polytope uses colors  $\tau' \subset \tau$  if for all vertices v of G and all colors  $j \in \tau \setminus \tau'$ ,  $\mathbf{s}(v, j) = 0$ .

**Proposition 3.4.** Let  $G(\tau)$  be a  $\tau$ -colored graph with corresponding coloring  $\phi$  where  $G(\tau)$  corresponds to an extreme-point solution  $\mathbf{X}(G(\tau))$  of the fractional coloring polytope. If  $\mathbf{s}$  is a 0/1 circuit which is feasible at  $\mathbf{X}(G(\tau))$  and which uses  $\tau' = \{a_1, \ldots, a_k\}$ , then  $\mathbf{s}$  corresponds to an  $(a_1, \ldots, a_k)$ -Kempe swap at  $\phi$ .

*Proof.* We will define a proper  $\tau$ -coloring  $\phi'$  such that the resulting  $\tau$ -colored graph  $G(\tau)'$  satisfies  $\mathbf{s} = \mathbf{X}(G(\tau)') - \mathbf{X}(G(\tau))$ . Let  $G(\mathbf{s}), V(\mathbf{s})$ , and  $E(\mathbf{s})$  be defined as in Theorem 3.2. Since  $\mathbf{s}$  is feasible at  $\mathbf{X}(G(\tau))$  and 0/1, we have that

- for all  $v \in V(\mathbf{s})$ ,  $\sum_{i \in \tau} \mathbf{s}(v, i) = 0$ ,

- $\mathbf{s}(v, \phi(v)) = -1$  for all  $v \in V(\mathbf{s})$ , and

- $\mathbf{s}(v,i) \geq 0$  for all  $v \in V(\mathbf{s})$  and  $i \neq \phi(v)$ .

We therefore have that for all  $v \in V(\mathbf{s})$ , there is exactly one color  $i^v$  such that  $\mathbf{s}(v, i^v) = 1$ , and for all colors  $j \in \tau \setminus \{\phi(v), i^v\}$ ,  $\mathbf{s}(v, j) = 0$ . We define  $\phi'(v) = i^v$  for all  $v \in V(\mathbf{s})$  and  $\phi'(v) = \phi(v)$  otherwise. We let  $G(\tau)'$  be the  $\tau$ -colored graph colored by  $\phi'$ . Then  $\mathbf{s} = \mathbf{X}(G(\tau)') - \mathbf{X}(G(\tau))$ . Since  $\mathbf{s}$  is a circuit, it follows from Theorem 3.2 that  $G(\mathbf{s})$  is connected, and thus by Corollary 3.3,  $\mathbf{s}$  corresponds to an  $(a_1, \ldots, a_k)$ -Kempe swap at  $\phi$ , as desired.

We note that we can indeed find 0/1 circuits that do not correspond to ordinary Kempe swaps (i.e., those using only two colors) Figure 8 depicts such an example. The depicted colorings differ by a generalized Kempe swap, and therefore the corresponding extreme-points of the fractional matching

polytope differ by a circuit. However, it can be readily seen that they do not differ by a single Kempe swap. By reinterpreting the 0/1 circuits as a generalization of Kempe swaps, Proposition 3.4 allows for improved reachability results in the coloring setting.

Figure 8: Two colorings whose corresponding extreme-points differ by a circuit, but are not a single (ordinary) Kempe swap apart.

**Theorem 3.5.** Let G be a k-colorable graph where  $k \geq \chi(G)$ . Every k-coloring of G is equivalent via generalized Kempe swaps.

As in the setting of ordinary Kempe swaps, we can use the results proved here to analyze the Kempe diameter when generalized Kempe swaps (especially in those cases where ordinary Kempe swaps do not achieve reachability). In [3], the authors explore subclasses of perfect graphs and give bounds on the Kempe diameter. For example, they show that bipartite graphs and cographs have Kempe diameter at most 3n/2 and  $2n\log(n)$  respectively. Although generalized Kempe swaps are far more permissive than ordinary Kempe swaps, we show that there is still a linear lower bound on the Kempe diameter even when using generalized Kempe swaps.

Definition 23. Given a graph G, a color set  $\tau$ , and two proper  $\tau$ -colorings  $G(\tau)_1$  and  $G(\tau)_2$ , we say a circuit walk from  $\mathbf{X}(G(\tau)_1)$  to  $\mathbf{X}(G(\tau)_2)$  in the fractional coloring polytope is a proper walk if each point visited in the walk is the characteristic vector of a proper  $\tau$ -coloring of G.

Note that, by definition, the circuits in a proper walk are necessarily 0/1 circuits, and thus correspond to generalized Kempe swaps.

**Theorem 3.6.** For all n, there exists a graph G on n vertices, a color set  $\tau$ , and proper  $\tau$ -colorings  $G(\tau)_1$  and  $G(\tau)_2$  such that a shortest proper walk from  $\mathbf{X}(G(\tau)_1)$  to  $\mathbf{X}(G(\tau)_2)$  has length n.

Proof. Let  $G = K_n$ , the complete graph on n vertices with vertex set  $\{v_1, \ldots, v_n\}$ . Let  $\tau \supseteq \{c_1, \ldots, c_n, d_1, \ldots, d_n\}$ , let  $G(\tau)_1$  be the coloring that colors the vertex  $v_i$  with the color  $c_i$ , and let  $G(\tau)_2$  be the coloring that colors the vertex  $v_i$  with the color  $d_i$ . Clearly,  $n \ 0/1$  circuit steps suffice to move from  $\mathbf{X}(G(\tau)_1)$  to  $\mathbf{X}(G(\tau)_2)$  since the color of each vertex can be changed one at a time.

Next, we will show as an intermediate step that for any  $\tau$ -colorings  $G(\tau)'$  and  $G(\tau)''$ , if  $\mathbf{X}(G(\tau)'')$  is a single circuit step away from  $\mathbf{X}(G(\tau)')$ , then there is at most one color that appears in  $G(\tau)''$  but not in  $G(\tau)'$ . By Theorem 3.2, if we let  $\mathbf{s} = \mathbf{X}(G(\tau)'') - \mathbf{X}(G(\tau)')$ , then  $(V(\mathbf{s}), E(\mathbf{s}))$  is connected. We now consider the digraph  $(V(\mathbf{s}), A(\mathbf{s}))$  where

$$A(\mathbf{s}) = \{(u, v) : \mathbf{s}(u, i) + \mathbf{s}(v, i) = 0, \mathbf{s}(u, i) < 0 \text{ for some } i \in \tau\}$$

That is, an arc is directed from u to v if v's color in  $G(\tau)''$  is the same as u's color in  $G(\tau)'$ .

Next we note that if a color appears in  $G(\tau)''$  but not in  $G(\tau)'$ , then this corresponds to a source in  $(V(\mathbf{s}), A(\mathbf{s}))$ , i.e., a vertex not incident to any in-arcs. Now, assume for the sake of a contradiction that  $(V(\mathbf{s}), A(\mathbf{s}))$  has at least two sources  $w_1$  and  $w_2$ . Consider any simple path P from  $w_1$  to  $w_2$

in  $(V(\mathbf{s}), E(\mathbf{s}))$ . The edge of P incident to  $w_i$  is an out-arc in  $(V(\mathbf{s}), A(\mathbf{s}))$  since  $w_i$  is a source. This means that there is at least one vertex u in P whose incident edges in P are both in-arcs in  $(V(\mathbf{s}), A(\mathbf{s}))$ . By definition, this means that both neighbors of u in P have the same color in  $G(\tau)'$ . However, since G is the complete graph, this contradicts that  $G(\tau)'$  is a proper  $\tau$ -coloring of G.

Thus, any circuit step between two proper  $\tau$ -colorings of G can introduce at most one new color. It follows that  $\mathbf{X}(G(\tau)_2)$  cannot be reached from  $\mathbf{X}(G(\tau)_1)$  in fewer than n circuit steps if we require those steps to move between the proper  $\tau$  colorings of G.

We note that the length of a shortest proper walk between two proper colorings depends heavily on the number of available colors. Theorem 3.6 relies on the fact that the number of colors available is twice the number of colors necessary to color the graph. As we show below, if we have only n available colors to color  $K_n$ , then for any two proper colorings, there is a proper walk between them of length at most 2.

**Proposition 3.7.** Let  $G = K_n$  and  $|\tau| = n$ . Then for any proper  $\tau$ -colorings  $G(\tau)_1$  and  $G(\tau)_2$ , there exists a proper walk between  $\mathbf{X}(G(\tau)_1)$  and  $\mathbf{X}(G(\tau)_2)$  of length at most two.

Proof. We may assume that  $\mathbf{s} = \mathbf{X}(G(\tau)_1) - \mathbf{X}(G(\tau)_2)$  is not a circuit. We reuse the notation  $A(\mathbf{s})$  introduced in the proof of Theorem 3.6. Since all n colors appear in both  $G(\tau)_1$  and  $G(\tau)_2$ , we have that  $(V(\mathbf{s}), A(\mathbf{s}))$  is the disjoint union of t directed cycles for some t. Since  $\mathbf{s}$  is not a circuit, we have  $t \geq 2$ . Assume without loss of generality that these cycles have vertex sets  $V_1, \ldots, V_t$  where  $V_1 = \{v_1, \ldots, v_{n_1}\}$  and for  $1 \leq i \leq t$ ,  $1 \leq i \leq$

Now, let  $G(\tau)'$  be obtained from  $G(\tau)_1$  in the following way. For  $k > n_t$ ,  $v_k$  receives the same color in  $G(\tau)'$  as in  $G(\tau)_1$ . For  $2 \le k \le n_t$ , in  $G(\tau)'$   $v_k$  receives the color of  $v_{k-1}$  in  $G(\tau_1)$ , and in  $G(\tau)'$   $v_1$  receives the color of  $v_{n_t}$  in  $G(\tau_1)$ . Then if  $\mathbf{g}_1 = \mathbf{X}(G(\tau)') - \mathbf{X}(G(\tau)_1)$ , it is not hard to see that  $(V(\mathbf{g}_1), E(\mathbf{g}_1))$  is a single cycle, and so  $\mathbf{g}_1$  is a circuit by Theorem 3.2. Likewise, it is not hard to see that if  $\mathbf{g}_2 = \mathbf{X}(G(\tau)_2) - \mathbf{X}(G(\tau)')$  then  $V(\mathbf{g}_2) = \{v_1, v_{n_1+1}, v_{n_2+1}, \dots, v_{n_{t-1}+1}\}$ , and  $(V(\mathbf{g}_2), E(\mathbf{g}_2))$  is a cycle. Then  $\mathbf{g}_2$  is also a circuit by Theorem 3.2. Therefore, there exists a proper walk between  $\mathbf{X}(G(\tau)_1)$  and  $\mathbf{X}(G(\tau)_2)$  of length at most two, as desired.

In the next section, we give an explicit example that the circuits of the fractional coloring polytope have unbounded circuit imbalance measure.

#### 3.2 Exponential Circuit Imbalance

We show that the fractional coloring polytope has circuit imbalance which grows at least exponentially in the size of the underlying graph. To do so, we give an explicit construction. In particular, we show this is true even when restricted to a constant number of colors.

**Lemma 3.8.** Given a graph G = (V, E), let A and B refer to the equality and inequality constraint matrices (respectively) of the fractional coloring polytope. Then  $\kappa(A, B) \in \Omega(2^{|V|})$ , even for a constant number of colors.

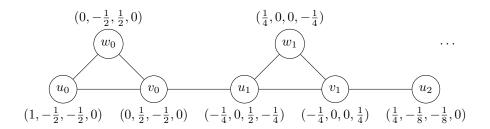

*Proof.* Let  $t \geq 3$  be odd and let G = (V, E) where  $V = \bigcup_{i=0}^t \{u_i, v_i, w_i\}$  and  $E = \{u_t v_t, v_t w_t, w_t u_t\} \cup \bigcup_{i=0}^{t-1} \{u_i v_i, v_i w_i, w_i u_i, v_i u_{i+1}\}$ . Let  $K = \{a, b, c, d\}$  be the set of colors. Let  $\mathbf{g}$  (see Figure 9) be such that for all even  $i \in \{0, \dots, t\}$ ,

$$\begin{split} \mathbf{g}(u_i,a) &= \frac{1}{2^i} & \mathbf{g}(u_i,b) = -\frac{1}{2^{i+1}} & \mathbf{g}(u_i,c) = -\frac{1}{2^{i+1}} & \mathbf{g}(u_i,d) = 0 \\ \mathbf{g}(v_i,a) &= 0 & \mathbf{g}(v_i,b) = \frac{1}{2^{i+1}} & \mathbf{g}(v_i,c) = -\frac{1}{2^{i+1}} & \mathbf{g}(v_i,d) = 0 \\ \mathbf{g}(w_i,a) &= 0 & \mathbf{g}(w_i,b) = -\frac{1}{2^{i+1}} & \mathbf{g}(w_i,c) = \frac{1}{2^{i+1}} & \mathbf{g}(w_i,d) = 0 \\ \mathbf{g}(u_{i+1},a) &= -\frac{1}{2^{i+2}} & \mathbf{g}(u_{i+1},b) = 0 & \mathbf{g}(u_{i+1},c) = \frac{1}{2^{i+1}} & \mathbf{g}(u_{i+1},d) = -\frac{1}{2^{i+2}} \\ \mathbf{g}(v_{i+1},a) &= -\frac{1}{2^{i+2}} & \mathbf{g}(v_{i+1},b) = 0 & \mathbf{g}(v_{i+1},c) = 0 & \mathbf{g}(v_{i+1},d) = -\frac{1}{2^{i+2}} \\ \mathbf{g}(w_{i+1},a) &= \frac{1}{2^{i+2}} & \mathbf{g}(w_{i+1},b) = 0 & \mathbf{g}(w_{i+1},c) = 0 & \mathbf{g}(w_{i+1},d) = -\frac{1}{2^{i+2}} \end{split}$$

Figure 9: The construction of the vector  $\mathbf{g}$  in the proof of Lemma 3.8. Each vertex  $z_i$  is labeled by  $(\mathbf{g}(z_i, a), \mathbf{g}(z_i, d), \mathbf{g}(z_i, c), \mathbf{g}(z_i, d))$ , the values of the vector  $\mathbf{g}$  corresponding to that vertex.

Clearly,  $\mathbf{g} \in \ker(A)$ . Note that  $\mathbf{g}(u_i, a) = 4\mathbf{g}(u_{i+2}, a)$  for all  $i \in \{0, \dots, t-3\}$ . If  $\mathbf{g}$  is a circuit, the result follows. If  $\mathbf{g}$  is not a circuit, there exists a circuit  $\mathbf{h}$  with  $\mathrm{supp}(B\mathbf{h}) \subseteq \mathrm{supp}(B\mathbf{g})$ . We will show that in any such circuit  $\mathbf{h}$ ,  $\mathbf{h}(u_i, a) = 4\mathbf{h}(u_{i+2}, a)$ .

The fact that  $\operatorname{supp}(B\mathbf{h}) \subseteq \operatorname{supp}(B\mathbf{g})$  implies that for any row i of B such that  $B_i\mathbf{g} = 0$ , we have that  $B_i\mathbf{h} = 0$ . Then, since the identity matrix is a submatrix of B, we have that for all vertices v and colors f with  $\mathbf{g}(v, f) = 0$ ,  $\mathbf{h}(v, f) = 0$ . Likewise, for all edges uv and colors f with  $\mathbf{g}(u, f) = -\mathbf{g}(v, f)$ ,  $\mathbf{h}(u, f) = -\mathbf{h}(v, f)$ . Finally, the fact that  $\mathbf{h} \in \ker(A)$  implies that for all vertices z,

$$\mathbf{h}(z,a) + \mathbf{h}(z,b) + \mathbf{h}(z,c) + \mathbf{h}(z,d) = 0.$$

By the above, we obtain the following equalities:

$$\mathbf{h}(u_{i}, a) = -\mathbf{h}(u_{i}, b) - \mathbf{h}(u_{i}, c)$$

$$= \mathbf{h}(v_{i}, b) + \mathbf{h}(w_{i}, c)$$

$$= -\mathbf{h}(v_{i}, c) - \mathbf{h}(v_{i}, c) = -2\mathbf{h}(v_{i}, c) = 2\mathbf{h}(u_{i+1}, c)$$

$$= 2(-\mathbf{h}(u_{i+1}, a) - \mathbf{h}(u_{i+1}, d))$$

$$= 2(\mathbf{h}(w_{i+1}, a) + \mathbf{h}(v_{i+1}, d))$$

$$= 2(-\mathbf{h}(v_{i+1}, a) + \mathbf{h}(v_{i+1}, d)) = 4(-\mathbf{h}(v_{i+1}, a)) = 4\mathbf{h}(u_{i+2}, a),$$

as desired.

We note that although the graph G in the construction of Lemma 3.8 does not itself require 4 colors to be properly colored, the circuit  $\mathbf{h}$  constructed in the proof would still be a circuit even if G were merely a subgraph of the graph to be colored. As such, this proof does not rely on the fact that it uses more colors than are necessary.

## 4 The Maximum Weight Forest Problem

In this section, we devise some insight into the 0/1 circuits for the constraint system of the maximum weight forest problem for a simple graph G (i.e., a graph with no self loops and no parallel edges). Recall that for a graph G = (V, E) with vertex set V and edge set E (or V(G) and E(G) when the graph G is not clear from the context), a corresponding system can be stated as follows.

**Definition 24.** Let G = (V, E) be a simple graph. The maximum weight forest problem has a feasible set that corresponds to the extreme-points of the polytope given by the following system of constraints:

$$\mathbf{x} \in \mathbb{R}^{|E|}: \qquad \sum_{e \in E(G[U])} \mathbf{x}(e) \leq |U| - 1 \qquad \forall \emptyset \neq U \subseteq V \\ \mathbf{x}(e) \geq 0 \qquad \forall e \in E,$$

(MWF)

where G[U] is the subgraph of G induced by  $U \subseteq V$ .

Here  $\mathbf{x}(e)$  denotes the entry in vector  $\mathbf{x} \in \mathbb{R}^{|E|}$  corresponding to edge  $e \in E$ . We will use the notation  $\mathbf{x}_e$  to denote the unit vector where only  $\mathbf{x}(e)$  is nonzero. The first set of constraints, known as rank inequality constraints, enforces that at an integral extreme-point, the support of  $\mathbf{x}$  contains no cycles. In matroid theory, these rank inequalities appear as constraints in the independent matroid polytope for graphic matroids; see [30] for further details. Here, they ensure that the solutions to (MWF) correspond to forests, i.e., independent sets of the graphic matroid associated with G.

We note that the matrix rows for the constraints  $\mathbf{x}(e) \geq 0$  appear also in the rank inequality constraints for sets  $U = \{u, v\}$  with  $uv \in E$ . Thus, for the purpose of characterizing circuits or non-circuits of (MWF) in this section, it suffices to consider only the constraints

$$\sum_{e \in E(G[U])} \mathbf{x}(e) \leq |U| - 1 \quad \text{for all } \emptyset \neq U \subseteq V.$$

(Rank)