# Boosting the Memory Window of Memristive Stacks via Engineered Interfaces with High Ionic Mobility

José Diogo Costa,<sup>1,a)</sup> Daniel Veira-Canle,<sup>2</sup> Noa Varela-Domínguez, <sup>1</sup> Nicholas Davey,<sup>3</sup> Victor Leborán,<sup>1</sup> Rafael Ramos,<sup>1</sup> Fèlix Casanova,<sup>3</sup> Luis E. Hueso,<sup>3</sup> Victor M. Brea,<sup>2</sup> P. López,<sup>2</sup> and Francisco Rivadulla<sup>1,a)</sup>

<sup>1</sup>Centro Singular de Investigación en Química Biolóxica e Materiais Moleculares (CIQUS), Universidade de Santiago de Compostela, 15782 Santiago de Compostela, Spain;

<sup>2</sup> Centro Singular de Investigación en Tecnoloxías Intelixentes (CiTIUS), Universidade de Santiago de Compostela, Santiago de Compostela, Spain;

<sup>3</sup>CIC nanoGUNE BRTA, Donostia–San Sebastian 20018, Spain; IKERBASQUE, Basque Foundation for Science, Bilbao 48009, Spain.

The great potential of memristive devices for real-world applications still relies on overcoming key technical challenges, including the need for a larger number of stable resistance states, faster switching speeds, lower SET/RESET voltages, improved endurance, and reduced variability. One material optimization strategy that has still been quite overlooked is interface engineering, specifically, tailoring the electrode/dielectric interface to modulate oxygen exchange. Here, we demonstrate that introducing materials with high ionic mobility can significantly expand the accessible oxygen concentration range within the dielectric layer, significantly broadening the memory window. Using SrTiO<sub>3</sub>-based memristive stacks, we integrated an ion-conducting SrCoO<sub>3</sub> interfacial layer to facilitate oxygen transfer, increasing the number of distinguishable resistance states from 8 to 22. This modification also reduced the SET/RESET voltage by 50% and markedly improved device endurance, albeit with a trade-off of reduced state retention. To assess the practical implications of this trade-off, we trained a two-layer fully connected neural network using the experimental SrTiO<sub>3</sub>/SrCoO<sub>3</sub> memristor characteristics on the MNIST handwritten digit dataset. Networks with hidden-layer sizes between 64 and 256 memristive elements achieved classification errors below 7%. The observed temporal drift means the functional state must be updated at intervals of less than 1 h to maintain reliable operation. Finally, we confirmed the transferability of this interface-engineering approach by applying it to  $HfO_x$ -based devices, achieving a similarly enhanced memory window.

# I. INTRODUCTION

The rapid growth of data-driven technologies and artificial intelligence has placed unprecedented demands on modern computing systems. These systems are increasingly constrained by the separation of memory and logic units, leading to bottlenecks in speed and energy efficiency. As a result, there is a pressing need for novel hardware paradigms that can support high-density, low-power, and scalable data processing. Among emerging technologies, resistive switching (RS) devices have gained substantial attention for their ability to serve as both memory elements and computational units within a single, compact structure. 1–4

RS devices operate by toggling between distinct resistance states under applied electrical stimuli, enabling them to store and process information in a tendentially non-volatile manner. While binary switching has been the conventional focus, <sup>5,6</sup> recent interest has shifted toward multi-level resistive switching, wherein a single device can access multiple discrete conductance states. <sup>7-9</sup> This capability is especially valuable for multilevel memory storage, analog computing, and neuromorphic systems, since fine control over conductance enables increased bit density. More precisely, while a binary (2-state) system can encode only a single bit (0 or 1), a 4-state system can encode 2 bits (00, 01, 10, 11), with the general pattern following a 2<sup>N</sup> relationship. Achieving stable and tunable multistate behavior, however, remains a significant materials challenge, often limited by interfacial instabilities, stochastic switching dynamics, or poor device endurance.

These limitations are closely tied to the underlying physical mechanisms of RS. Among these different mechanisms, valence change-based switching in transition metal oxides plays a prominent role. The transition between the high-resistance state (HRS) and the low-resistance state (LRS) is driven by oxygen migration that leads to the formation of conducting filaments. Despite the growing understanding of RS phenomena, several key technical challenges still require innovative strategies from a material growth standpoint. These include achieving a greater number of stable resistance states, faster switching speeds, lower SET/RESET voltages, reduced breakdown cycles, and minimized variability (both device-to-device and cycle-to-cycle). In many cases, trade-offs arise between these performance metrics.

The most common material-driven optimization strategy involves exploring different dielectric systems, with a wide range of oxides having been investigated, including TiO<sub>x</sub>, HfO<sub>x</sub>, TaO<sub>x</sub>, and SrTiO<sub>3</sub>. <sup>11</sup> In addition,

alloying strategies have been pursued to tailor defect chemistry and improve switching uniformity. A notable example is  $HfAlO_x$ , which has demonstrated enhanced memory window, reduced variability, and improved endurance. Beyond single- or alloyed-oxide systems, nanocomposite architectures, typically comprising a host matrix with embedded nanoscale columns or secondary phases, have also been explored. These hybrid structures can offer advantages such as reduced device-to-device variability and electroforming-free operation. However, fabricating controlled nanocomposite films is challenging, necessitating precise and often hard-to-reproduce growth conditions and advanced deposition equipment.

A more fabrication-friendly strategy involves engineering the interface between the dielectric and the electrode to modulate oxygen exchange across the interface. Introducing an oxygen-migration-blocking layer, such as SrO or  $Al_2O_3$ , has been shown to effectively confine ionic transport, thereby improving retention stability. However, this benefit comes with trade-offs: the additional barrier increases SET/RESET voltages and power consumption, while the extra series resistance can induce local Joule heating and accelerate dielectric breakdown, ultimately degrading endurance. Moreover, the restricted ionic mobility typically slows the switching dynamics by an order of magnitude.

On the other hand, materials with high oxygen-ion mobility can significantly improve both switching kinetics and interfacial charge transport. In fact, fast ionic conductors such as strontium ferrite (SFO) and strontium cobaltite (SCO) have been successfully employed as functional layers in memristive stacks.  $^{18,19}$  This approach exploits the topotactic phase transition between the insulating brownmillerite (BM) phase (SrCo(Fe)O<sub>2.5</sub>) and the metallic perovskite phase (SrCo(Fe)O<sub>3</sub>) to realize binary switching, which inherently limits its suitability for multi-level operation.

In contrast, our strategy employs a bilayer architecture consisting of a high-performance RS dielectric combined with an oxygen-conductive interfacial layer inserted between the oxide and the electrode. This design is intended to broaden the accessible oxygen-stoichiometry range, thereby enabling a larger and more controllable multi-state memory window. In addition, promoting oxygen exchange at the interface mitigates interfacial degradation, which enhances endurance. Finally, improved ionic transport at the interface lowers the SET/RESET voltage, resulting in reduced power consumption and faster switching dynamics. To this end, SCO

was the selected material due to its exceptional oxygen mobility and redox activity.<sup>20–22</sup> This material works as an efficient oxygen exchange layer or catalytic interface, promoting filament formation without introducing adverse effects such as excessive series resistance or increased susceptibility to dielectric breakdown.

In this work, we employ strontium titanate (SrTiO<sub>3</sub>, STO)<sup>23,24</sup> as a platform to investigate the role of high oxygen-ion-mobility materials at the active electrode interface. To this end, we fabricated pulsed-laser-deposited (PLD) STO and STO/SCO heterostructures and integrated Pt/Au top electrodes for electrical characterization. We have shown that introducing the SCO interfacial layer results in a remarkable enhancement of the memory window, expanding the number of distinguishable resistance levels from 8 states (3-bit equivalent) in the STO reference device to 22 states in the STO/SCO heterostructure, surpassing the threshold for 4-bit encoding. Equivalently, this also translates on enhanced synaptic behaviors.

In addition to multilevel capability, the engineered interface leads to a 50% reduction of the SET/RESET voltages, increased switching endurance, and reduced device-to-device (D2D) and cycle-to-cycle (C2C) variability. This performance improvement comes with a trade-off of increased ionic drift, which limits long-term retention and imposes periodic refresh requirements. To assess the suitability of these devices for neuromorphic applications, we trained a two-layer fully connected neural network using the MNIST handwritten digit dataset using experimentally extracted device parameters with lab-scale hidden layer dimensions ranging from 32 to 256 memristors. Initial error rates below 7% are achievable, requiring refresh operation within 1 h of operation.

Finally, we demonstrate the generality and technological relevance of this strategy by extending it to a CMOS-compatible  $HfO_x$  platform. The incorporation of an SCO interfacial layer likewise produces a substantial enhancement of the memory window. Notably, this improvement is achieved even under lower-temperature deposition conditions for SCO, highlighting the robustness and transferability of the approach and its suitability for scalable processes aimed at larger multibit memory windows or enhanced synaptic functionality.

#### II. EXPERIMENTAL DETAILS

Two sets of thin-film samples were fabricated using pulsed laser deposition (PLD) on (001)-oriented Nb-doped (0.5 wt%) SrTiO<sub>3</sub> (Nb:STO) substrates. The samples were designed to investigate the impact of the high ionic mobility SCO layer on resistive switching behavior:

- 1. Nb:STO substrate / STO (25.5 nm)

- 2. Nb:STO substrate / STO (25.5 nm) / SCO (5 nm)

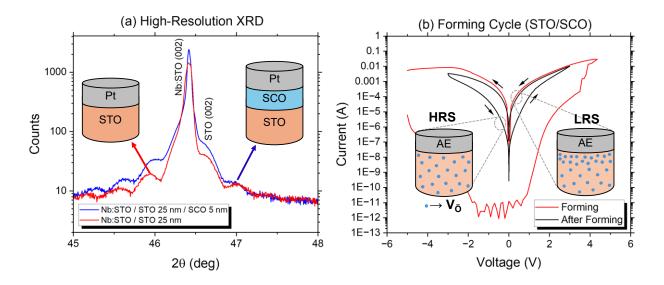

The STO layers were deposited at 765 °C under an oxygen partial pressure of 100 mTorr, while the SCO layer was deposited at 750 °C under the same oxygen pressure. The cooling down to room temperature occurred at 5 °C/min, under the same atmosphere. After deposition, top electrodes (Pt 5 nm / Au 60 nm) were patterned using standard photolithography and lift-off. This leads to 2 different interfaces between dielectric material and active electrode: STO/Pt and STO/SCO [see inset of Fig. 1(a)]. The structural properties of the STO and STO/SCO films were characterized using x-ray diffraction (XRD, Malvern Panalytical Empyrean) and scanning transmission electron microscopy (STEM).

A second series of devices was fabricated to evaluate the transferability of this strategy, consisting of (1) Nb:STO / HfO<sub>x</sub> (25.5 nm) and (2) Nb:STO / HfO<sub>x</sub> (25.5 nm) / SCO (5 nm) heterostructures. These films were deposited at 100 mTorr and 400 °C for both the HfO<sub>x</sub> and SCO layers. While the primary characterization and analysis were carried out on the STO-based memristive stacks, the HfO<sub>x</sub> devices were included to assess the broader applicability of the interface-engineering approach.

Electrical characterization was carried out at room temperature under ambient atmospheric conditions using a Keithley 2450 source meter in a two-terminal configuration, with the Nb:STO substrate acting as the bottom electrode. Fast pulsed measurements down to 5  $\mu$ s were performed using a TGA 1240 waveform generator and the electric setup detailed in the Supplementary Material (Fig. S5). No measurable dependence on top-contact area was observed for the STO-based devices. For consistency and ease of comparison, all data shown correspond to devices with 55  $\mu$ m  $\times$  55  $\mu$ m pads unless otherwise specified.

#### III. RESULTS AND DISCUSSION

#### A. Material Framework

The XRD  $\theta$ –2 $\theta$  scans of both STO and STO/SCO samples [Fig. 1(a)] display a sharp (002) Nb:STO substrate reflection and a distinct STO film shoulder with well-defined thickness fringes. This confirms smooth surfaces and chemically abrupt interfaces, with a fitted STO thickness of 25.5 nm. No additional reflections corresponding to the SCO layer are observed, including the (002) and (006) peaks characteristic of the in-plane ordering of oxygen vacancies in the BM phase (region not shown), which would be distinguishable even for a 5 nm film. While vertically oriented oxygen-vacancy channels in the BM phase can suppress these reflections, the as-grown films such as those measured in Fig. 1(a), typically exhibit horizontally oriented channels.<sup>25</sup> Therefore, the SCO layer is unlikely to be in the BM phase.

The perovskite phase should exhibit a (002) reflection near  $47^{\circ}$  in the  $\theta$ - $2\theta$  scan, which is either absent or below the detection limit in our measurements. Moreover, formation of the perovskite  $SrCoO_3$  phase is quite challenging and requires thermal treatments at high oxygen pressure.<sup>26</sup> Therefore, the SCO layer is most likely amorphous. This interpretation is further supported by the analogous  $HfO_x/SCO$  bilayer samples deposited at lower temperatures (400 °C), which display similar memory-window broadening, as discussed in the final section.

# B. DC I-V characterization

The initialization of the RS dynamics required a forming cycle to generate the initial conductive filaments. There was a significantly lower forming voltage in the case of STO/SCO (~3.6 V), compared to the STO sample (~5.0 V), suggesting an easier filament formation due to the enhanced ionic mobility at the STO/SCO interface [Fig. 1(b), red line for the STO/SCO case]. Following this generative cycle, eightwise switching<sup>27</sup> was observed, as shown by the black line in Fig. 1(b) (note the logarithmic scale of the modulus). The hysteresis loops followed a dual current path, from largest negative value to positive and back to negative voltages [see black arrows in Fig. 1(b)].

This eightwise switching RS behavior has been attributed to changes in the oxygen vacancy density within the STO film, particularly at the interface with the active electrode. <sup>28</sup> More specifically, when a positive voltage is applied to the active electrode, oxygen ions migrate toward it, leading to the accumulation of oxygen vacancies near the STO/Pt or STO/SCO interface. This process leaves behind two electrons, resulting in the LRS [inset of Fig. 1(b)];

$$O_0^x \to V_{\ddot{0}} + 2e + \frac{1}{2}O_2$$

Similarly, applying a negative bias to the active electrode triggers the opposite reaction at the interface, extracting available electrons and leading to the HRS. This absorption of oxygen by the active electrode is one of the root causes of sample breakdown. Therefore, the quality and composition of the interface will be crucial for enhancing the endurance of the RS behavior, as will be discussed in the following sections.

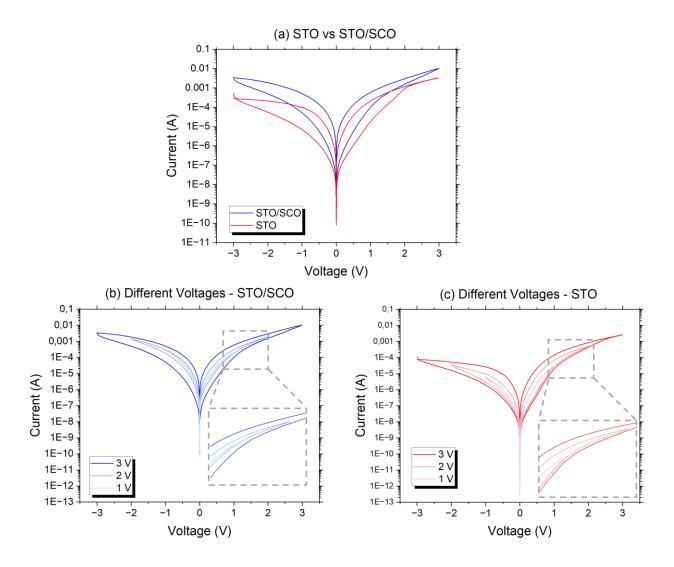

A direct comparison of the measured I–V curves for both STO and STO/SCO samples is shown in Fig. 2(a), where a larger current is evident for the STO/SCO case. If we examine the I–V curves in more detail, another clear and reproducible difference between the samples emerges. Figures 2(b) and 2(c) show the I–V curves for similar dual loops but with varying maximum voltage modules (1, 2 and 3 V), for STO/SCO and STO samples, respectively. In the case of the STO sample, the device returns to the full HRS after completing the first full loop, indicating a complete RESET [inset of Fig. 2(c)]. In contrast, for the STO/SCO interface, the HRS in subsequent cycles exhibits an intermediate resistance value [inset of Fig. 2(b)]. This behavior suggests that SCO acts as a more effective oxygen sponge, with a more gradual filament break/formation, while in the STO/Pt interface all the oxygen returns to the STO layer after RESET.

Regarding the nature and geometry of the RS mechanism, filamentary switching tends to be abrupt and often step-like, whereas interfacial switching typically shows a gradual increase in resistance. The I–V curves observed for both samples, which exhibit a gradual current increase, suggest a dominant interfacial effect. This type of switching has also been reported to exhibit some area dependence. <sup>29</sup> Although the STO sample shows lower current for the smallest contact size, consistent with the expected area scaling for interfacial RS, this correlation is not clearly established and is absent in the STO/SCO sample (see Supplementary Material, Fig. S1). More importantly, the uniformity and repeatability of the STO/SCO sample are significantly better than those of STO/Pt,

including D2D and C2C variability (Figs. S2 and S3). Significant and irreversible damage was observed in the STO sample after just 7 cycles at a voltage magnitude of 3 V (Fig. S3). This effect was substantially mitigated by limiting the maximum voltage to 2 V; therefore, this value was adopted as the voltage limit throughout the remainder of this work. This easier dielectric breakdown suggests that the oxygen exchange at the STO/Pt interface is more susceptible to critical damage, potentially compromising device reliability. Since no clear area dependence was observed, it is more likely that this improved performance results from the smoother STO/SCO interface, which facilitates more consistent redox reactions, rather than from a fundamentally different filament formation mechanism.

# C. RF performance analysis

The quasi-DC analysis presented in the previous section has already shed light on the impact of the SCO interface on the performance of the memristor stack. Nevertheless, radiofrequency (RF) electrical pulses are commonly used to characterize memristors, as they better replicate the real operating conditions encountered in practical applications. By applying RF pulses, different resistance states can be induced in the device, allowing for a more accurate assessment of its switching behavior, retention capabilities, and endurance.

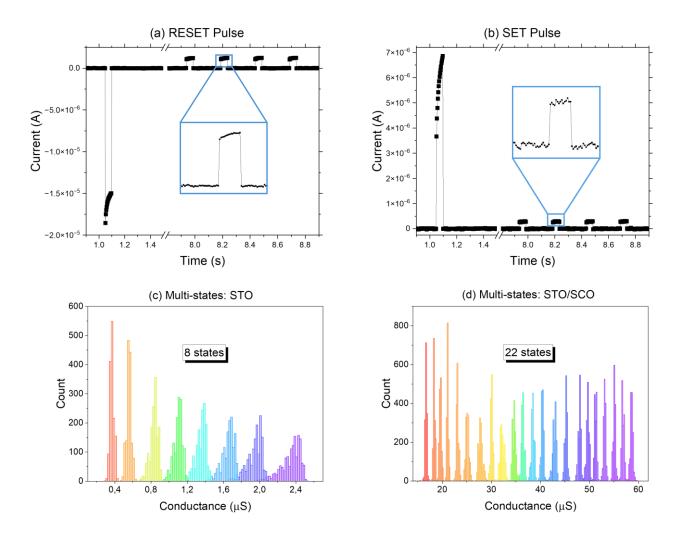

The full SET and RESET states were achieved by applying long pulses (800 ms,  $\pm 2$  V) until the current stabilized. Subsequently, shorter pulses (50 ms,  $\pm 2$  V) were used to move through the entire resistance range from the HRS to the LRS, and vice versa. A lower read voltage (50 ms, 0.5 V) was then used to measure the resistance state without altering it. To ensure the reliability of this readout method, a train of 100 read pulses was applied. This readout scheme is illustrated in Fig. 3(a) and (b), following a RESET and SET pulse, respectively, for the STO sample.

Figures 3(c) and 3(d) present the resistance states measured for the STO and STO/SCO devices, respectively. A pronounced enhancement in both the memory window and the number of discernible resistance levels is observed in the STO/SCO sample, increasing from 8 to 22 stable states. This remarkable improvement is consistent with the broader range of the I–V characteristics for the STO/SCO device, as shown in Fig. 2(a) (note the logarithmic scale).

In the STO reference device, a noticeable drift in the read-pulse response is observed within the LRS [see inset of Fig. 3(a)], which broadens the distribution of low-resistance values and thereby limits the number of distinguishable states [Fig. 3(c)]. This drift is absent in both the HRS and in the STO/SCO device. Consequently, the substantial increase in the number of resolvable states in the STO/SCO structure arises from the combined effect of a wider memory window and reduced readout variability. These results highlight the capability to encode an additional bit of information, expanding from 8 states (3 bits) to over 16 states (4 bits), simply through the introduction of an SCO interfacial layer.

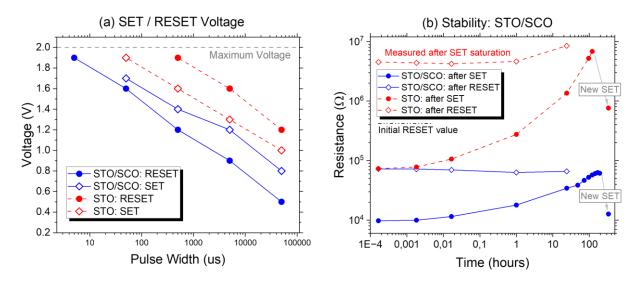

To gain further insight into the SET/RESET kinetics, both samples were characterized using pulse widths spanning five orders of magnitude (from 5 µs to 50 ms) and maximum absolute voltages up to 2 V. Given the history-dependent nature of RS dynamics, a full SET/RESET cycle was performed by applying long pulses (800 ms, ±2 V), followed by a read/SET or RESET/read sequence. By comparing the current values measured before and after the SET/RESET pulses, the corresponding switching voltages for each pulse width were extracted (see Supplementary Material, Fig. S6).

Figure 4(a) clearly shows a significant reduction, close to 50%, in both the SET and RESET voltages for the STO/SCO sample (blue lines). This shows that the higher ionic mobility associated with the SCO interface facilitates reduced operating voltages and enables shorter pulse operation. Additionally, the STO sample exhibits a lower SET voltage compared to the RESET voltage, suggesting a distinct filament formation mechanism. In contrast, the STO/SCO sample shows a smoother transition away from the LRS, pointing to easier oxygen diffusion from the SCO layer into the dielectric, relative to the STO-only case.

Another technologically relevant factor for memristive devices is the retention time of electrically programmed resistance states. Although long retention is usually preferred for conventional data storage, short retention is often advantageous for spiking neural networks. 30,31 In valence change-based memristors, ionic drift and diffusion gradually alter the oxygen-vacancy distribution and can dissolve or reshape conductive filaments, producing resistance relaxation on timescales ranging from minutes to days. 32 The extent of this ionic drift is also influenced by the interfacial electrostatics, in particular the depletion width and Schottky-barrier characteristics at the dielectric–electrode interface, which control the local electric field and therefore vacancy migration rates. 33

To assess how the SCO interface influences device retention, we performed repeated SET/RESET cycling until the current levels stabilized. We then monitored the resistance evolution over several days under zero bias. Figure 4(b) presents the temporal evolution of the resistance in the STO/SCO sample following a full SET (blue circles) and a full RESET (blue diamonds), spanning from seconds to multiple days. A pronounced drift toward the HRS is observed over time, consistent with a gradual relaxation toward a more uniform oxygen distribution [inset of Fig. 1(b)]. This interpretation is further supported by the stable resistance observed for the HRS (blue diamonds). Nevertheless, applying a subsequent full SET pulse restores the device to a state close to its initial condition, as indicated by the final data point labeled "New SET" (gray box).

Following the forming cycle, the STO/Pt sample also exhibits a similar time-dependent evolution from the LRS toward a higher resistance [Fig. 4(b), red circles]. However, while the initial LRS after forming is around 70 k $\Omega$ , comparable to the HRS of the STO/SCO sample, the resistance gradually increases over time, reaching approximately 7 M $\Omega$ . Unlike the STO/SCO case, performing another full SET at this point does not return the system to its original state. Instead, the new LRS stabilizes at approximately 0.8 M $\Omega$  (see measurement after "New SET"). As a result, the initial resistance range (from the original red circles to the black dashed line) is never recovered. Furthermore, when the HRS is measured after saturation, it is found to be significantly higher (red diamonds). It was confirmed that this evolution begins after the forming cycle for each device, and unfolds in the several hours timeframe.

While the permanent shift in the resistance operation window of the STO/Pt sample is likely caused by the ex-situ deposition of the Pt/Au contacts, it nevertheless underscores the benefits of the smoother and more consistent oxygen ion exchange occurring at the STO/SCO interface. This leads to improved repeatability, stable operation, and overall enhanced device performance, along with a significantly greater number of accessible intermediate states. In fact, we conducted endurance tests up to  $\sim 10^5$  cycles using large voltage pulses (1 s duration) to ensure full SET/RESET transitions. These tests revealed significantly more controlled degradation in the STO/SCO sample, whereas the STO sample exhibited pronounced degradation (see Fig. S4).

#### D. Scanning Transmission Electron Microscopy

To be checked

#### E. Performance of STO/SCO memristor crossbar array for MNIST classification tasks

The observed time evolution of the resistance states can be leveraged for spiking neural network applications.<sup>30,31</sup> However, for data storage and in-memory computing, longer retention times are typically preferred. In this work, we focus on the latter case, aiming to understand the trade-offs between achieving a large number of resistance states and maintaining their temporal stability.

To evaluate the performance of the fabricated STO/SCO memristors, we extracted the time evolution of their conductance states and the corresponding standard deviations across a statistical set of approximately ten devices, as reported elsewhere [Ref ISCAS]. We then trained a two-layer fully connected neural network using the MNIST handwritten digit dataset. The hidden layer size was varied from 32 to 256 memristive elements to explore the trade-off between model capacity and array size within a small system feasible in a laboratory environment [see schematic representation of Fig. 5(a)]. The training dataset (60,000 images) was augmented using random affine transformations, including rotations up to  $\pm 15^{\circ}$ , translations and scaling up to 10%, and shear up to  $\pm 10^{\circ}$ , with occasional perspective distortions to enhance generalization. The 10,000 test images were used as a fixed validation set.

Training was performed digitally in PyTorch using quantized weights limited to five discrete integer levels [-2,-1,0,1,2]. The quantization step was adapted to the standard deviation of each layer's weights to ensure an even occupation of all levels. To improve robustness to device variability, we performed hardware-aware training on the weights by injecting Gaussian noise with 10% standard deviation and 50% probability per step. Each synaptic weight was represented by a differential conductance pair  $(G^+,G^-)$ , corresponding to two memristors. This scheme reduces the impact of device asymmetries, nonlinear conductance–voltage behavior, and readout offsets. We used five conductance levels between 12 and 60  $\mu$ S, mapped linearly to the digital weights [-1, 1]. The selection of this number of states resulted from a trade-off between the initial number of states and their drift.

After training, the networks were mapped to analog form using IBM's AIHWKit, $^{36}$  which simulates inference on resistive crossbar arrays. The experimentally measured drift and variability of our STO/SCO-based memristors were incorporated through a custom ReRAM noise model. $^{37}$  For each network, the synaptic weights were programmed once at t = 0 s, and their conductance drift was then simulated over time without reprogramming. Performance evaluation was carried out at t = 0.1 s, 1 s, 10 s, 1 min, 15 min, 1 h, 5 h, 10 h, 1 day, and 2 days.

Figure 5(b) shows the classification error as a function of time for different hidden-layer sizes. Hidden layers with more than 64 memristive elements exhibit a clear reduction in the initial classification error, decreasing from approximately 13% for 32 elements to below 7% for larger arrays. These values compare well with state-of-the-art ferroelectric tunnel-junction (FTJ) devices, for which we also calculated an error of around 11% for 32 memristive elements using the reported device parameters.<sup>38</sup> Although the initial error remains similar for hidden-layer sizes ≥64, the network with 256 elements maintains a noticeably lower baseline error at early times (below 1 h) compared with smaller arrays. As expected, ionic drift induces progressive conductance variation and a corresponding increase in classification error, which exceeds 80% after two days for all hidden-layer dimensions, effectively rendering the system unusable beyond this timescale.

Therefore, the enhanced memory window of the STO/SCO memristors can be effectively exploited in neuromorphic identification tasks, provided that the operational state is redefined for time intervals below 1 h. The trend of decreasing baseline error with increasing hidden-layer size is evident even in lab-scale demonstrator arrays.

### F. Transferability to other material frameworks

The proposed approach is quite promising as a material heterostructure for increasing the number of resistance states in STO-based memristors. Nevertheless, in an ideal scenario, introducing an interface with high ionic mobility—and the associated benefits discussed above—should be a generally transferable strategy to enhance the memory window across different memristive systems. As previously noted, the primary driver of this improvement is the increased ionic mobility at the interface rather than any specific crystalline growth.

To test this hypothesis, we selected  $HfO_x$ , which is the most widely used memristive material, as an alternative valence-change-based system. Following the same methodology as in the previous sections, two samples were fabricated: (i)  $HfO_x$  (25 nm) and (ii)  $HfO_x$  (25 nm) / SCO (5 nm), allowing us to evaluate the effect of the SCO insertion layer. Both layers were deposited under the same conditions as STO, except for a lower deposition temperature of 400 °C (see Experimental Section). This reduced temperature was applied to both  $HfO_x$  and SCO, further confirming that the role of the SCO layer is to broaden the accessible oxygen concentration range rather than to rely on any particular crystalline ordering.

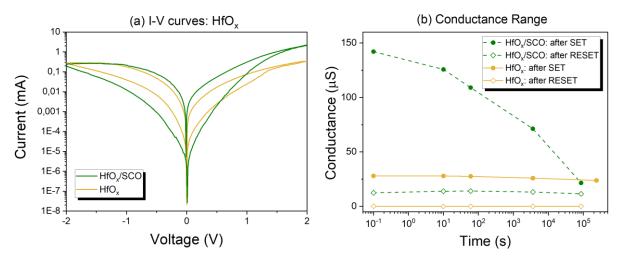

Figure 6(a) shows the comparison between both I-V curves, depicting a similar current enhanced as the one discussed in Fig. 2(a), providing already an indication of a similar enhancement. It should be noted that there was a more significant dependence on the pad size in the  $HfO_x$  sample, and the results presented here concern 220  $\mu$ m pad size. This is an indication of a different mechanism for filament formation that, nevertheless, does not affect the effect of the SCO layer.

As shown in Fig. 6(b), we then performed the saturation of the system toward the HRS (open diamonds) and LRS (closed circles) for the  $HfO_x$  (orange) and  $HfO_x$ /SCO (green) samples, and monitored the conductance evolution over time. This is similar to the analysis performed in Fig. 4(b) but, in this case, the conductance was plotted instead of resistance, as it provides a clearer representation of the memory window broadening [shown in Fig. 3(b) for the STO-based memristors].

Both the  $HfO_x$  and  $HfO_x/SCO$  samples exhibited minimal degradation over time and could be reliably switched back to their respective HRS and LRS states. A pronounced drift toward the HRS was again observed for the SCO-based sample, accompanied by an almost fivefold increase in the memory window. The  $HfO_x$  device, on the other hand, showed a more stable state definition but proved significantly more fragile, often failing after routine characterization cycles. This behavior further supports the notion that the improved interface in the  $HfO_x/SCO$  heterostructure enhances memristor endurance.

Comparing the  $HfO_x$ - and STO-based samples, we observe that, despite the overall higher conductance of the  $HfO_x$  devices, the total conductance range is approximately 55  $\mu$ S in both cases. Moreover, the conductance decay for comparable initial conductance states is also similar, being the one of  $HfO_x$  8% larger. A detailed analysis of the  $HfO_x$ -based devices, similar to that performed for the STO system, lies beyond the scope of this study as these

results clearly demonstrate the transferability of the proposed interface-engineering strategy to other memristive material systems.

#### IV. CONCLUSIONS

In conclusion, we have demonstrated that introducing a high-ionic-mobility layer at the electrode/dielectric interface significantly enhances memristive device performance. Specifically, incorporating an SCO interfacial layer in STO-based memristors expanded the memory window from 8 to 22 states, reduced SET/RESET voltages by 50%, and improved endurance, albeit with reduced state retention. A two-layer fully connected neural network, trained using the experimental device characteristics, achieved classification errors below 7% on the MNIST dataset. Reliable operation requires state updates within one hour due to temporal drift. Finally, we show that this interface-engineering strategy is broadly transferable, achieving comparable performance improvements in HfO<sub>x</sub>-based memristive devices.

# **ACKNOWLEDGEMENTS**

This work has received financial support from "Cátedra Televés en Diseño Microelectrónico" (TSI-069100-2023-0010) by the PERTE Chip, Secretaría de Estado de Telecomunicaciones e Infraestructuras Digitales, Ministerio de Asuntos Económicos y Transformación Digital and has been co-funded by the European Union-NextGenerationEU. Funding for open access charge: Universidade de Santiago de Compostela/CISUG.

#### REFERENCES

- 1. Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. *Nature Nanotechnology* vol. 15 529–544 Preprint at https://doi.org/10.1038/s41565-020-0655-z (2020).

- 2. Liu, Y. *et al.* Cellular automata imbedded memristor-based recirculated logic in-memory computing. *Nat Commun* **14**, (2023).

- 3. Mehonic, A. *et al.* Memristors—From In-Memory Computing, Deep Learning Acceleration, and Spiking Neural Networks to the Future of Neuromorphic and Bio-Inspired Computing. *Advanced Intelligent Systems* **2**, (2020).

- 4. Im, I. H., Kim, S. J. & Jang, H. W. Memristive Devices for New Computing Paradigms. *Advanced Intelligent Systems* **2**, (2020).

- 5. Huang, P. *et al.* Binary Resistive-Switching-Device-Based Electronic Synapse with Spike-Rate-Dependent Plasticity for Online Learning. *ACS Appl Electron Mater* **1**, 845–853 (2019).

- 6. Fang, Z. *et al.* HfOx/TiOx/HfOx/TiOx multilayer-based forming-free RRAM devices with excellent uniformity. *IEEE Electron Device Letters* **32**, 566–568 (2011).

- 7. Milo, V. *et al.* Multilevel HfO2-based RRAM devices for low-power neuromorphic networks. *APL Mater* **7**, (2019).

- 8. Antad, V. *et al.* Resistive switching in HfO2-x/La0.67Sr0.33MnO3Heterostructures: An intriguing case of low H-Field susceptibility of an E-Field controlled active interface. *ACS Appl Mater Interfaces* **13**, 54133–54142 (2021).

- 9. Brivio, S., Spiga, S. & Ielmini, D. HfO2-based resistive switching memory devices for neuromorphic computing. *Neuromorphic Computing and Engineering* vol. 2 Preprint at https://doi.org/10.1088/2634-4386/ac9012 (2022).

- 10. Waser, R. & Aono, M. Nanoionics-based resistive switching memories. *Nat Mater* **6**, 833–840 (2007).

- 11. Wang, Z. *et al.* Resistive switching materials for information processing. *Nature Reviews Materials* vol. 5 173–195 Preprint at https://doi.org/10.1038/s41578-019-0159-3 (2020).

- 12. Hellenbrand, M. *et al.* Thin film design of amorphous hafnium oxide nanocomposites enabling strong interfacial resistive switching uniformity. *Sci Adv* **9**, (2023).

- 13. Cho, S. *et al.* Self-assembled oxide films with tailored nanoscale ionic and electronic channels for controlled resistive switching. *Nat Commun* **7**, (2016).

- 14. Dou, H. *et al.* Electroforming-Free HfO2:CeO2 Vertically Aligned Nanocomposite Memristors with Anisotropic Dielectric Response. *ACS Appl Electron Mater* **3**, 5278–5286 (2021).

- 15. Siegel, S. *et al.* Trade-Off Between Data Retention and Switching Speed in Resistive Switching ReRAM Devices. *Adv Electron Mater* **7**, (2021).

- 16. Hensling, F. V. E., Heisig, T., Raab, N., Baeumer, C. & Dittmann, R. Tailoring the switching performance of resistive switching SrTiO3 devices by SrO interface engineering. *Solid State Ion* **325**, 247–250 (2018).

- 17. Baeumer, C. *et al.* Spectromicroscopic insights for rational design of redox-based memristive devices. *Nat Commun* **6**, (2015).

- 18. Acharya, S. K. *et al.* Brownmillerite thin films as fast ion conductors for ultimate-performance resistance switching memory. *Nanoscale* **9**, 10502–10510 (2017).

- 19. Tambunan, O. T. *et al.* Resistance switching in epitaxial SrCoOx thin films. *Appl Phys Lett* **105**, (2014).

- 20. Jeen, H. *et al.* Reversible redox reactions in an epitaxially stabilized SrCoOx oxygen sponge. *Nat Mater* **12**, 1057–1063 (2013).

- 21. Jeen, H. *et al.* Orienting oxygen vacancies for fast catalytic reaction. *Advanced Materials* **25**, 6459–6463 (2013).

- 22. Jeen, H. *et al.* Topotactic phase transformation of the brownmillerite SrCoO2.5 to the perovskite SrCoO3-δ. *Advanced Materials* **25**, 3651–3656 (2013).

- 23. Szot, K., Speier, W., Bihlmayer, G. & Waser, R. Switching the electrical resistance of individual dislocations in single-crystalline SrTiO3. *Nat Mater* **5**, 312–320 (2006).

- 24. Álvarez-Martínez, V. *et al.* Interfacial Thermal Resistive Switching in (Pt,Cr)/SrTiO3 Devices. *ACS Appl Mater Interfaces* **16**, 15043–15049 (2024).

- 25. Han, H. *et al.* Control of Oxygen Vacancy Ordering in Brownmillerite Thin Films via Ionic Liquid Gating. *ACS Nano* **16**, 6206–6214 (2022).

- 26. Jeen, H. *et al.* Topotactic phase transformation of the brownmillerite SrCoO2.5 to the perovskite SrCoO3-δ. *Advanced Materials* **25**, 3651–3656 (2013).

- 27. Sarantopoulos, A., Waser, R. & Dittmann, R. Eightwise Switching Mechanism in Memristive SrTiO3 Devices and Its Implications on the Device Performance. *Physica Status Solidi (A) Applications and Materials Science* vol. 221 Preprint at https://doi.org/10.1002/pssa.202300483 (2024).

- 28. Cooper, D. *et al.* Anomalous Resistance Hysteresis in Oxide ReRAM: Oxygen Evolution and Reincorporation Revealed by In Situ TEM. *Advanced Materials* **29**, (2017).

- 29. Sassine, G. et al. Interfacial versus filamentary resistive switching in TiO2 and HfO2 devices.

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials,

Processing, Measurement, and Phenomena 34, (2016).

- 30. Duan, Q. *et al.* Spiking neurons with spatiotemporal dynamics and gain modulation for monolithically integrated memristive neural networks. *Nat Commun* **11**, (2020).

- 31. Park, S. O., Jeong, H., Park, J., Bae, J. & Choi, S. Experimental demonstration of highly reliable dynamic memristor for artificial neuron and neuromorphic computing. *Nat Commun* **13**, (2022).

- 32. Baeumer, C. *et al.* Spectromicroscopic insights for rational design of redox-based memristive devices. *Nat Commun* **6**, (2015).

- 33. Hellwig, J. *et al.* Resolving the Relaxation of Volatile Valence Change Memory. *Adv Electron Mater* https://doi.org/10.1002/aelm.202400062 (2024) doi:10.1002/aelm.202400062.

- 34. LeCun, Y. & Cortes, C. MNIST: The Database of Handwritten Digits. accessed (2025).

- 35. Xiao, T. P. *et al.* On the Accuracy of Analog Neural Network Inference Accelerators [Feature]. *IEEE Circuits and Systems Magazine* **22**, 26–48 (2022).

- 36. Rasch, M. J. *et al.* A Flexible and Fast PyTorch Toolkit for Simulating Training and Inference on Analog Crossbar Arrays. in *2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems, AICAS 2021* (Institute of Electrical and Electronics Engineers Inc., 2021). doi:10.1109/AICAS51828.2021.9458494.

- 37. Falcone, D. F. *et al.* All-in-One Analog Al Hardware: On-Chip Training and Inference with Conductive-Metal-Oxide/HfOx ReRAM Devices. *Adv Funct Mater* https://doi.org/10.1002/adfm.202504688 (2025) doi:10.1002/adfm.202504688.

- 38. Hosseinzadeh, S., Lancaster, S., Parvaresh, A., Silva, C. & Fey, D. Parameter Space Exploration of Neural Network Inference Using Ferroelectric Tunnel Junctions for Processing-In-Memory. in *Proceedings 2024 27th Euromicro Conference on Digital System Design, DSD 2024* 1–10 (Institute of Electrical and Electronics Engineers Inc., 2024). doi:10.1109/DSD64264.2024.00010.

Figure 1. (a) High-resolution XRD structural characterization of the STO (red line) and STO/SCO films (blue line) grown on Nb:STO substrates. The inset shows the deposited stack, including the Pt electrical contact. (b) I–V electrical measurements of the STO/SCO sample. The red line corresponds to the initial forming cycle (up to 5 V), and the black line to the subsequent cycle (up to 3 V). The inset shows schematic representations of the oxygen vacancy distribution in the low-resistance state (LRS) and the high-resistance state (HRS).

**Figure 2.** Electrical characterization (I–V curves) of the fabricated samples, showing dual hysteresis loops from negative to positive and back to negative voltages. **(a)** Comparison between the STO (red line) and STO/SCO (blue line) loops. I-V curves for different voltage ranges: ±3 V (black line), ±2 V (red line), and ±1 V (blue line) for the **(b)** STO/SCO and **(c)** STO samples.

**Figure 3.** Distinguishable resistance states. Example of current as a function of time for **(a)** RESET and **(b)** SET pulses, followed by a train of read pulses (50 ms, 0.5 V) for the STO sample. Current histograms showing distinguishable resistance states after a sequence of 50 ms-wide SET/RESET pulses, from highest to lowest achievable resistance states, for the **(c)** STO and **(d)** STO/SCO samples.

Figure 4. (a) SET (open diamonds) and RESET (filled circles) voltages as a function of pulse width for STO/SCO (solid blue line) and STO (dashed red line). (b) Measured resistance at the read voltage in the LRS (open diamonds) and HRS (filled circles) as a function of time for STO/SCO (solid blue line) and STO (dashed red line). (c) Number of cycles until breakdown for STO/SCO (blue bars) and STO (red bars).

#### (a) Two-Layer Neural Network Architecture (b) Classification error on the MNIST dataset 100 N memristive elements N = 32 N = 64 1 8 4 5 3 80 N = 128 N = 2564 6 7 9 4 60 Error (%) 3 3 9 8 \ 4 5 21293 6 20 7 0 8 0s 0,1s 10s 1min 15min 1h 5h 10h 1-2days Time N memristive elements

Figure 5. (a) Schematic representation of the used two-layer neural network, where  $N \in \{32, 64, 128, 256\}$  is the hidden layer size. (b) Classification error on the MNIST dataset as a function of time after programming for hidden-layer sizes The same baseline network was programmed once and then allowed to drift to each time point without reprogramming.

Figure 4. (a) Electrical characterization (I–V curves) of the  $HfO_x$  (orange line; 220  $\mu$ m pad) and  $HfO_x$ /SCO samples (green line; 55  $\mu$ m pad). (b) Measured conductance at the read voltage in the LRS (open diamonds) and HRS (filled circles) as a function of time for  $HfO_x$ /SCO (solid green line) and  $HfO_x$  (dashed orange line).