# Hardware-aware Neural Architecture Search of Early Exiting Networks on Edge Accelerators

Alaa Zniber, Member, IEEE, Arne Symons, Member, IEEE, Ouassim Karrakchou, Senior Member, IEEE Marian Verhelst, Fellow, IEEE, Mounir Ghogho, Fellow, IEEE

Abstract—Advancements in high-performance computing and cloud technologies have enabled the development of increasingly sophisticated Deep Learning (DL) models. However, the growing demand for embedded intelligence at the edge imposes stringent computational and energy constraints, challenging the deployment of these large-scale models. Early Exiting Neural Networks (EENN) have emerged as a promising solution, allowing dynamic termination of inference based on input complexity to enhance efficiency. Despite their potential, EENN performance is highly influenced by the heterogeneity of edge accelerators and the constraints imposed by quantization, affecting accuracy, energy efficiency, and latency. Yet, research on the automatic optimization of EENN design for edge hardware remains limited. To bridge this gap, we propose a hardware-aware Neural Architecture Search (NAS) framework that systematically integrates the effects of quantization and hardware resource allocation to optimize the placement of early exit points within a network backbone. Experimental results on the CIFAR-10 dataset demonstrate that our NAS framework can discover architectures that achieve over a 50% reduction in computational costs compared to conventional static networks, making them more suitable for deployment in resource-constrained edge environments.

Index Terms—Dynamic Neural Networks, Neural Architecture Search, Early Exiting Networks, Hardware Deployment, Heterogeneous Edge Accelerators

# I. INTRODUCTION

THE rapid advancement of high-performance processing devices and cloud technologies has driven a notable increase in the architectural complexity of Deep Learning (DL) models, leading to significant performance gains in various domains, such as large language models [1]. However, deploying DL models at the edge is often necessary to comply with data privacy regulations (e.g., in healthcare applications) or to meet real-time processing requirements (e.g., in autonomous driving). Additionally, the substantial energy consumption of large-scale DL models in the cloud raises serious environmental concerns. Consequently, there is an urgent need to reduce the computational complexity of DL models, making them more suitable for resource-constrained edge hardware while enhancing their energy efficiency.

Various techniques have been developed to reduce the energy consumption and computational burden of DL models.

This research has received funding from the European Union's Horizon research and innovation program under grant agreement No 101070374.

Zniber A. and Karrakchou O., are with the TICLab, International University of Rabat, Morocco (e-mail: alaa.zniber@uir.ac.ma; ouas-sim.karrakchou@uir.ac.ma)

Symons A. and Verhelst M. are with MICAS, KU Leuven, Belgium (e-mail: arne.symons@kuleuven.be, marian.verhelst@kuleuven.be)

Ghogho M. is with College of Computing, University Mohammed VI Polytechnic, Morocco (e-mail: mounir.ghogho@um6p.ma)

Some approaches, such as pruning and quantization, optimize weights and activations, while others, like knowledge distillation, focus on reducing model size during training [2]. However, these methods impose a static inference process that does not account for variations in input complexity. In practice, some inputs are inherently easier to process than others, suggesting that model complexity could be dynamically adjusted to enhance efficiency without compromising performance.

1

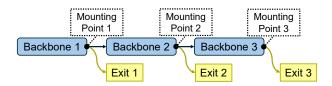

In this context, Dynamic Neural Networks (DyNN) represent a promising research direction due to their ability to adapt their structure and/or behavior based on variations in input complexity [3]. DyNN models can be broadly classified into two categories: those designed to enhance performance [4]-[6] and those aimed at reducing computational cost and runtime [7], [8] compared to their static counterparts. A prominent approach in the latter category is Early Exiting Neural Networks (EENN), which terminate computation once a confidence threshold on the output is reached [9]. In the case of classification, an EENN consists of a backbone network augmented with intermediate classifiers (ICs) positioned at predetermined exit points (cf. Figure 1). During inference, an input sample is processed sequentially through the network. At each exit point, an IC evaluates the sample before further processing in the backbone. The classification output (i.e., the highest class probability) is then compared against a userdefined confidence threshold. If the probability exceeds the threshold, the EENN confidently returns the classification result and halts further computation. Otherwise, feature extraction continues in the backbone until the next exit point is reached.

Although EENN can effectively reduce computational complexity, the resulting energy savings are highly dependent on the hardware on which they are deployed. However, little attention has been given in the literature to the automatic design and deployment of EENN on edge hardware. Most existing Neural Architecture Search (NAS) approaches focus on optimizing metrics such as Multiply-Accumulate (MAC) operations and inference time [10], [11]. Yet, in most cases, memory operations and data transfers are more costly than the computations themselves, limiting the practicality of such NAS frameworks for real-world applications. Furthermore, some methods, such as the approach proposed in [12], employ a hardware-in-the-loop strategy to estimate the energy consumption and latency of candidate EENN architectures using real hardware measurements. While this method provides accurate assessments of hardware costs (e.g., energy, latency), it lacks scalability, as NAS cannot be fully executed in the cloud. Additionally, reliance on physical hardware for evaluation reduces control over the target hardware and its resource allocation. Therefore, EENN's input-adaptiveness mandates prudent deployment on modern edge accelerators.

Additionally, edge hardware is becoming increasingly heterogeneous due to the presence of specialized kernels designed to accelerate specific operations (e.g., convolutions [13], softmax [14]). Consequently, optimizing model-to-hardware mapping is critical to prevent inefficient allocation of EENN components across cores, which can lead to suboptimal resource usage, increased latency, and higher energy consumption. Moreover, most edge devices require network weight quantization for inference. However, this process can degrade performance at intermediate exit points, necessitating architectural and training adjustments. In this context, achieving optimal energy efficiency with EENN requires careful consideration of hardware-specific factors such as quantization effects, accelerator capabilities, memory hierarchy, and multicore processing. To the best of our knowledge, the interplay between these demanding hardware characteristics and EENN behavior has not been investigated before.

To address this issue, we propose a hardware-aware NAS framework that integrates the effects of quantization and hardware allocation into the design and training process of EENN, ensuring adherence to modern edge accelerators' deployment constraints. Our main contributions span multiple levels. Given the prevalence of quantization in edge hardware, our training process is conducted in a quantization-aware manner, ensuring minimal performance degradation. Moreover, energy and latency metrics are derived from a hardware simulator, Stream [15], which enables fine-grained estimation of targeted hardware metrics and offers great flexibility in defining the target edge hardware using hard-coded components such as accelerators, memory hierarchy, and core count. Furthermore, we refine our NAS formulation by introducing early exitdependent constraints on EENN structure and performance. We enforce small overheads from the appended early exits and encourage effective exploitation of the early exiting mechanism (i.e., frequent exits in early layers). By considering the interplay between quantization, EENN architecture, and hardware mapping, our framework ensures that the final architecture achieves an efficient trade-off between accuracy, energy efficiency, and latency across various edge devices.

The paper is organized as follows: Section II reviews the literature. In Section III, we analyze the impact of quantization and EENN mounting points on hardware performance in terms of accuracy, energy consumption, and latency, further motivating the need for our proposed hardware-aware NAS for EENN, which is introduced in Section IV. Section V evaluates our NAS and discusses the experimental results. Finally, Section VI presents our conclusions.

## II. RELATED WORK

Several studies in the literature have explored the impact of hardware on the performance of DL models and proposed solutions to either design optimized hardware for a specific class of models or search for the best DL architecture for

Fig. 1. An example early exiting network with 3 backbone blocks and 3 exits

a given hardware. These techniques can be classified as design space exploration techniques or hardware-aware neural architecture search.

## A. Design Space Exploration

Hardware accelerators are specialized systems designed to perform DL operations more efficiently than general-purpose processors. They play a crucial role in enhancing the performance, energy efficiency, and scalability of DL models, particularly in edge computing applications where resources are limited. To maximize the potential of hardware accelerators, design space exploration (DSE) frameworks have been developed. These frameworks assist in hardware design by searching for the optimal hardware configuration (e.g. number of accelerators, memory hierarchy) for a specific class of DL models. Hence, DSE frameworks serve as proxies for hardware cost estimation in novel architectures, enabling informed design decisions without the need for physical prototyping.

Timeloop [16] is a DSE tool designed to optimize the mapping of DL operations to hardware accelerators. It enables the exploration of various dataflows and memory hierarchies to enhance both performance and energy efficiency. ZigZag [17] extends the architectural and mapping design space further by accommodating uneven mapping schemes and diverse memory hierarchies. It employs an analytical model to estimate performance and energy efficiency, providing a comprehensive evaluation framework. However, these frameworks support only single-core accelerators, whereas homogeneous multicore architectures are gaining popularity for improved scaling [18]-[21], and heterogeneous multi-core architectures for workload specialization [22], [23]. One such framework is Stream [15], a DSE framework that evaluates and optimizes DL workload processing on multi-core accelerator architectures. It incorporates considerations for off-chip and core-tocore traffic congestion within its analytical model, offering a detailed analysis of performance and energy efficiency.

Specifically for EENN, the Atheena framework [24] was developed to address the unique challenges posed by these dynamic architectures. Atheena automates the design of hardware architectures for EENN on FPGAs, leveraging the varying difficulty of individual data samples to scale resource allocation across different network sections, thereby optimizing throughput and resource usage. It integrates DSE to transform high-level representations of EENN into optimized hardware descriptions suitable for FPGA implementation, significantly improving efficiency.

In contrast to existing DSE approaches that adapt hardware to the EENN workload, our work designs efficient EENN architectures for a specific backbone, enabling deployment

on existing edge accelerators without extensive hardware reconfiguration. Nevertheless, we leverage Stream's DSE for our EENN hardware-aware NAS and exploit estimated costs per potential hardware mapping to navigate the EENN search space.

#### B. Hardware-aware Neural Architecture Search

With the growing demand for edge applications, NAS has shifted toward designing hardware-friendly neural networks. Hardware-aware NAS aims to find an efficient neural architecture that maximizes accuracy while adhering to specific hardware constraints (e.g., energy, latency, memory, area). Once a search space is defined (e.g., different operators, possible hyperparameter values), a search algorithm (e.g., reinforcement learning, evolutionary algorithms) is executed to identify the best-performing architecture under all userdefined constraints. In addition to the task-dependent metric that NAS optimizes, hardware constraints are integrated at different levels, introducing varying degrees of complexity [25]. Under hard constraints (e.g., a memory consumption upper bound), NAS can be conducted within a constrained search space, where newly generated architectures are automatically discarded if they violate hardware limitations [26]. Conversely, when hardware constraints are soft (e.g., minimizing energy consumption), researchers have either opted for joint optimization—balancing accuracy and hardware metrics [27]—or free multi-objective optimization (MOO), where architectures are identified along the Pareto front of the given objectives [28]. However, in both cases, additional challenges arise from estimating hardware metrics, as obtaining real cost values for each new architecture can be difficult. To address this, several methods have been proposed, including analytical [29] and neural network-based [30] estimations of hardware costs.

The application of NAS to DyNN, and particularly to EENN, is still an emerging research area. Conventionally, an EENN is manually designed based on a predefined number of exits. A mounting point is selected after n% of the total network's cost (e.g., number of operations, latency), where n is a natural number from a user-defined set of options [31]. However, a few recent studies propose automating EENN design. In [32], early exiting in EENN is optimized automatically using a policy gradient-based reinforcement learning algorithm, where the global cost function is the product of accuracy and the number of MACs. Building on [32], the authors of [33] sought to reduce NAS search costs by employing a genetic algorithm (GA) along with pre-trained accuracy and cost metric predictors, avoiding the need to train every newly generated architecture from scratch. More recently, [10], [11] developed a GA-driven EENN automatic search with several enhancements in the EENN training strategy, such as handling hard hardware cost constraints by incorporating them as regularizers in the training loss. Additionally, the authors of [12] introduced a hardware-aware dynamic NAS framework, coined HADAS, for EENN that jointly optimizes the model architecture along with dynamic voltage and frequency scaling (DVFS) settings, accounting for runtime variations and the specific efficiency features of the underlying hardware.

In contrast, our work presents a NAS strategy where model performance on hardware is estimated using a DSE framework with an analytical model that accurately accounts for the impact of individual hardware components (e.g., accelerators, memory). This approach is more precise than MAC-based methods and is less costly and more flexible than hardware-in-the-loop-based methods.

## III. HARDWARE IMPACTS ON EENN DESIGN

In this section, we investigate the impact of hardware on EENN design across two dimensions. First, we explore the effect of quantization on the performance of a fixed EENN, considering accuracy, energy consumption, and latency. Second, we examine how different EENN architectures derived from the same backbone behave on specific hardware. Our goal is to show to what extent variations in EENN models—such as quantization level and exit point placement—interact with hardware architecture, leading to differences in performance.

## A. Methodology of EENN Performance Evaluation

We conduct our study on an image classification task using CIFAR-10 [34], a well-known dataset from the MLPerf Tiny benchmark [35], which is dedicated to edge devices and applications. The evaluated metrics include model accuracy and hardware costs (i.e., energy and latency). Formally, we define the exit ratio of the  $i^{th}$  early exit,  $ER_i$ , as the proportion of input data that exit at i, satisfying a predefined confidence threshold. Thus, the average accuracy and energy-latency product of the full EENN can be expressed as follows:

$$ACC\_avg = \sum_{i=1}^{m} ER_i \times ACC_i$$

(1)

$$ET_{avg} = \sum_{i=1}^{m} ER_i \times ET_i$$

(2)

where  $ACC_i$  is the accuracy of the samples that exited at point i and  $ET_i$  is the product of energy (E, in joule) and latency/delay (T, in cycles) of the i<sup>th</sup> subnetwork (i.e. from the input up to the considered exit).

We evaluate our hardware cost using an enhanced version of the Stream DSE framework [15], which provides detailed energy and latency estimates while accounting for dynamicity and quantization. Stream considers factors such as off-chip memory usage and Network-on-Chip (NoC) core-to-core communication overhead for both activations and weights—critical for understanding system-level performance and energy efficiency. This evaluation includes the computational cost of each backbone layer and the overhead introduced by early exit blocks, offering insights into the trade-offs between energy consumption and latency. Moreover, Stream supports optimized workload mapping onto the multi-core architecture through an intra-core temporal mapping optimization engine called LOMA [36] and an inter-core workload allocation GAbased engine [37]. Once the best workload allocation for a given multi-core accelerator is determined, we use Stream's

TABLE I

#### ACCURACY AND EXIT RATIO FOR DIFFERENT QUANTIZATION CONFIGURATIONS

FP/INT X+Y means X-bit precision for the backbone and Y-bit precision for the exit point classifiers Cum. Params denotes cumulative number of parameters, Cum. MACs denotes cumulative multiply-accumulate operations

|             | Exit       | 1 (D)      | Exit       | 2 (F)      | Exit        | 3 (I)      | Exit        | 4 (K)      |         |        |

|-------------|------------|------------|------------|------------|-------------|------------|-------------|------------|---------|--------|

| Cum. Params | 30.922     |            | 71.946     |            | 354.634     |            | 1.439.498   |            |         |        |

| Cum. MACs   | 24.515.584 |            | 48.752.640 |            | 118.307.840 |            | 195.377.152 |            |         |        |

|             | Accuracy   | Exit Ratio | Accuracy   | Exit Ratio | Accuracy    | Exit Ratio | Accuracy    | Exit Ratio | ACC_avg | ET_avg |

| FP32+32     | 98.48      | 34.21      | 94.73      | 14.22      | 93.80       | 28.22      | 63.68       | 23.35      | 88.50   | 4921   |

| INT8+8      | 99.10      | 25.49      | 96.86      | 15.31      | 95.70       | 31.14      | 66.36       | 28.06      | 88.51   | 467    |

| INT8+4      | 98.97      | 24.18      | 97.69      | 15.12      | 95.60       | 29.31      | 69.48       | 31.39      | 88.53   | 489    |

| INT4+8      | 98.99      | 22.71      | 97.56      | 12.31      | 96.90       | 28.41      | 70.39       | 36.57      | 87.76   | 215    |

| INT4+4      | 97.40      | 31.49      | 94.97      | 12.33      | 93.80       | 23.72      | 65.87       | 32.46      | 86.01   | 186    |

hardware cost breakdown to extract relevant hardware metrics—namely, the energy  $E_k$  and latency  $T_k$  for a layer k. The energy for a given layer k is defined as follows:

$$E_k = \text{Computation}_k + \text{NoC Traffic}_k$$

where the computational cost is combined with the traffic across the NoC to estimate the overall utilization of the resources of the considered layer, while latency  $T_k$  is defined as the duration of executing the layer k. Therefore, for a subnetwork i (e.g. all layers up to exit i), we can define  $\mathrm{ET}_i$  as follows:

$$ET_i = \left(\sum_{k=1}^i E_k\right) \times \left(\sum_{k=1}^i T_k\right) \tag{3}$$

It is worth mentioning that  $ET_i$  includes the overhead of all previous intermediate exits, as all of them are executed during inference before a sample exits at exit i.

## B. Impact of Quantization

To study the impact of quantization, we use a modified MobileNetV2 backbone with a quad-core Edge TPU target (see Appendix A for more details). We enhance the backbone with three intermediate exit points placed at approximately 12%, 25%, and 60% of the total MAC operations. We finetune the confidence threshold  $\tau$  between 80% and 95% for all exit points. We reduce the precision from 32-bit floating point for weights and activations to 8-bit and 4-bit integer precision, as these are the most widely used quantization levels in edge accelerators. Furthermore, to assess the accuracy improvements contributed by each component (i.e., backbone or early exits), we apply a heterogeneous mixed-precision quantization scheme that disentangles the precision of the backbone and early exits. To train our model, we adopt a quantization-aware training scheme [2] for greater flexibility in representation learning and minimal sensitivity to quantization noise (see Appendix B).

Table I summarizes the results of our study. First, we observe consistent trends in the distribution of per-exit accuracy and exit ratios across all experiments. The networks exhibit high confidence in relatively easy samples, leading to high perexit accuracy at intermediate exit points and a 63% reduction in computation for nearly 40% of cases (corresponding to samples exiting at points 1 and 2). However, more feature extraction is required in deeper layers for harder samples.

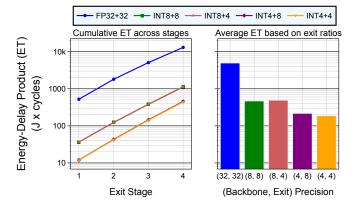

Fig. 2. The cumulative (left) and average (right) energy-delay product ET at different stages for differently quantized models. The ET\_avg is drastically reduced thanks to the early exiting at early stages.

Additionally, the accuracy at the last exit tends to be lower due to the increased difficulty of these samples. Hence, we verify the efficiency of EENN across all quantization levels. Second, across various quantization configurations, we observe notable differences in per-exit accuracy and exit-ratio distributions. Although the full-precision and 8-bit precision models exhibit only a small difference in average accuracy, the full-precision model benefits from increased expressivity, with the first exit achieving an exit ratio of 34.21%, compared to just under 30% for the quantized models. This results in more frequent late exits in the quantized models. When both the backbone and early exits are quantized to 4 bits, significant hardware cost reductions are achieved, but the average accuracy suffers due to lower precision. In contrast, mixed quantization schemes provide a balanced trade-off between soft (e.g., 8-bit) and hard (e.g., 4-bit) homogeneous quantization. This approach minimizes the impact on average accuracy while still achieving notable hardware cost savings. Specifically, quantizing the backbone to 4 bits reduces the computational burden of heavy operations (e.g., backbone convolutions) while allowing the exits to compensate for accuracy loss due to their larger capacity for information encoding.

Figure 2 details the breakdown of the energy-delay product (ET) in different exit stages (left) and shows  $ET_{\rm avg}$  for different precisions (right). Note the logarithmic scale of the Y-axis, which demonstrates that  $ET_{\rm avg}$  is significantly lower

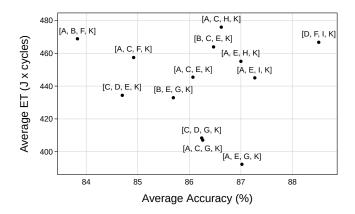

Fig. 3. Family of 4-exit models in INT8+8 configuration with identical backbone and exits topologies. Each model has different exit points, identified by the exit indices (c.f., Table III).

than the worst case due to the high exit ratios at earlier stages. Moreover, the reduction in  $ET_{\rm avg}$  for reduced precision is shown. Interestingly, we note that the model quantized with 8 bits for the backbone and 4 bits for the exits exhibits a slightly worse  $ET_{\rm avg}$  than the 8-bit + 8-bit quantized model, despite being more aggressively quantized. This is due to lower exit ratios at the early stages. Hence, quantization and early exit can interact in complex ways, potentially leading to significant performance differences, as observed in mixed-quantization models.

# C. Impact of Mounting Points

Next, we study the interplay between early exit mounting points and hardware performance. For this, we use 8-bit quantization for both the backbone and the exits. Figure 3 shows the average accuracy and ET for models with different mounting points of the four exits (denoted by four letters; cf. Table III). We observe that some architectures become severely unfit (e.g., model [A, B, F, K], which achieves low accuracy and high hardware cost), while others are more promising, offering a reasonable balance between accuracy and ET, yielding a subset of efficient networks to choose from (e.g., model [A, E, G, K]). However, no obvious patterns emerge for efficiently designing EENN. For instance, if we examine the four models [A, C, x, K], where x can be E, F, G, or H, we find significant differences in ET and accuracy between the models after minimal changes in the third exit point placement. Taking x to be E results in high accuracy and low ET, while moving it by a single block to F severely degrades performance.

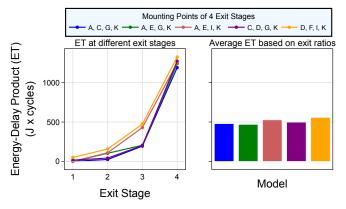

Figure 4 presents the execution time (ET) at different exit points for a subset of the best-performing models depicted in Figure 3. The results indicate that most of the degradation in ET comes from the difference in the placement of the third exit, while differences in the other exits are minor. This showcases the complex nature of the interactions between the placement of exit points and the hardware, which may have a significant impact on energy efficiency in some cases while being relatively harmless in others. Another example is the

Fig. 4. The cumulative (left) and average (right) energy-delay product ET at different stages for different mounting points with identical backbone and exit architecture. The ET varies due to exit ratio differences and tensor dimension mismatches with the accelerator dataflows.

behavior of [A, C, G, K] and [C, D, G, K], which achieve similar performance despite having different first and second exit points. These differences could be explained by complex interactions between the layers' shapes and the dataflows of the hardware cores, as different mounting points can have different activation and channel dimensions. For instance, if the dimensions are not a power of 2, this may lead to underutilization of the compute array.

Based on these findings, it becomes clear that automating the search for optimal mounting points, backbone architectures, and exit configurations is essential for designing an efficient EENN. In the next section, we introduce a NAS tool to address this complexity by systematically balancing these parameters, thereby reducing the need for exhaustive manual tuning and enhancing model efficiency across diverse deployment scenarios.

#### IV. HARDWARE-AWARE EENN NAS

In this section, we present our proposed solution for automatically designing quantized EENN for target hardware architectures. We start by formalizing our search optimization problem and describing the steps by which the framework delivers an optimally deployable EENN on an edge accelerator.

#### A. Problem Description

Given a fixed DL backbone, the objective is to enhance it automatically with early exits to enable efficient execution of the subsequent EENN on multi-core edge accelerators. The DL backbone can serve different use cases, such as image classification [31], audio denoising [38], or transformer-based sentiment analysis [39]. Thus, our objective is to develop a generic, hardware-aware NAS framework that identifies an efficient EENN architecture while considering the constraints of the available hardware resources. Additionally, we ensure that the computational overhead incurred by each additional exit point does not exceed a user-defined percentage of the remaining backbone layers up to the next exit. Furthermore, we constrain all architectures to efficiently implement early

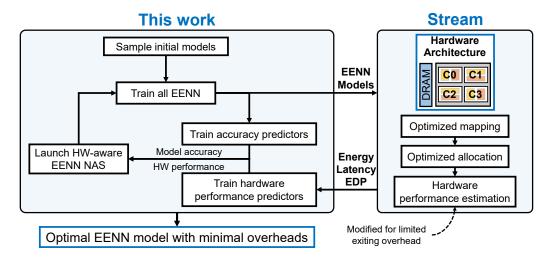

Fig. 5. Overview of the hardware-aware NAS process with enhanced Stream [15] framework for hardware performance estimation at different exit points.

exiting by bounding the last exit point ratio, enforcing sample exiting as early as possible. Formally, our NAS problem can be written as a constrained multi-objective optimization (MOO) problem as follows:

$$\max_{s \in \mathcal{S}} \text{ ACC\_avg}(s)$$

$$\min_{s \in \mathcal{S}} \text{ ET\_avg}(s)$$

$$\text{s.t. } \begin{cases} \text{OH}_i(s) \leq \theta, \ \forall i \in \{1, \dots, m\} \\ \text{ER}_m(s) \leq \mu \end{cases}$$

(4)

where s is an architecture from the NAS search space  $\mathcal{S}$ , m is the number of exits (including the final classifier),  $\mathrm{OH}_i(s)$  is the ratio between the additional ET cost incurred by exit point i and the ET of the backbone layers up to the next exit point (e.g., in Figure 1,  $\mathrm{OH}_1(s)$  corresponds to the ratio of the ET of Exit 1 to the ET of Backbone 2),  $\theta$  is the user-defined threshold on the overhead, and  $\mathrm{ER}_m$  is the exit ratio of the last exit, which is upper-bounded by a user-defined threshold  $\mu$ . Hence, our main goal is to optimize two conflicting objectives, namely EENN's average accuracy and energy-latency product, within the constrained search space of networks with bounded intermediate exit overhead and effective early exiting.

## B. NAS Search Space

The EENN search space is parameterized by the intrinsic properties of EENN models, namely the number of exits, their placement along the backbone, the architecture of intermediate exits (e.g., depth and width for a multilayer perceptron classifier), and the quantization level. Given a DL backbone, let us denote by H the maximum number of intermediate exits (excluding the final exit point) that could be appended to the backbone, by q the possible quantization levels, and by p the possible architectures of the exit points. For each candidate model with k intermediate exits, we have  $p^{k+1}$  and  $q^{k+1}$  possible EENN architectures and quantization levels (including the different configurations of the final exit point). Thus, the total number of architectures in our search space is  $\sum_{k=0}^{H} {H \choose k} (pq)^{k+1}$ , which simplifies through the binomial theorem to  $pq(1+pq)^H$ . We see that the search space grows

exponentially with the depth of the DL backbone and that an exhaustive search would be inefficient. Hence, using heuristics to guide the search is necessary. In our approach, we chose to use a genetic algorithm (GA) due to its flexibility and efficiency compared to non-evolutionary methods [25].

## C. NAS Framework

Our proposed NAS framework, illustrated in Figure 5, consists of the following four steps:

(Step 1) The process begins by sampling various EENN architectures to form an initial set of candidate models, denoted  $S^0$ , that comply with the overhead constraint  $\theta$ .

(Step 2) Each architecture in  $S^0$  is trained using quantization-aware training and evaluated on the Stream platform to obtain its corresponding accuracy and energy-delay product metrics. For each trained model, we apply the last exit ratio constraint  $\mu$  and remove those that do not satisfy it.

(Step 3) The metrics collected from each model constitute a labeled dataset:  $\mathcal{P}^0 = \{(s, \text{ACC\_avg}(s), \text{ET\_avg}(s)) \mid s \in \mathcal{S}^0\}$ , where each architecture is mapped to its respective accuracy and hardware cost. The dataset  $\mathcal{P}^0$  is then used to train accuracy and ET predictors.

(*Step 4*) Finally, the GA triggers an automatic search over multiple generations to generate better architectures. One generation proceeds as follows:

- Based on the previously trained predictors, the accuracy and ET are predicted for the parent architectures in the initial population.

- The population is ranked according to accuracy, and the top 2N parents are shortlisted. These are then ranked by ET value to retain the best N architectures for applying the GA operators. However, other ranking metrics, such as a weighted sum of accuracy and ET, can also be used.

- The GA applies mutation and crossover operators to the chromosomes of the parent architectures, which describe the EENN configuration (i.e., mounting points, depth of each early-exit network, quantization level, etc.).

- Each generation of GA offspring is filtered to remove models that do not satisfy the overhead constraint.

The new generation forms a new population, to which the same steps are applied.

At the end of the GA process, a new set  $S^1$  is created, consisting of the best N offspring and their ancestors from  $S^0$ . Steps 2 to 4 are then repeated on  $S^1$ , and the process continues for a finite number of iterations or until a desired balance between accuracy and ET cost is reached. However, previously trained architectures are not retrained during Step 2, and the training of predictors in Step 3 is done using the combined dataset:  $\mathcal{P}^k = \bigcup_{i=0}^k \mathcal{P}^i$ .

In conventional NAS, performance predictors are trained only once from a large set  $\mathcal{P}^0$  (e.g., four orders of magnitude in [33]), yielding strong predictors. This approach results in a sequential NAS pipeline where  $\mathcal{S}^1$  is not trained, and the best-performing architecture is retained, thereby ending the search. However, our NAS framework aims to combine optimality (i.e., finding the best architecture) and efficiency (i.e., a shorter search time compared to conventional NAS). Hence, we adopt a more efficient approach based on progressive weak predictors, originally proposed in [40]. The idea is to alternate between training predictors using increasingly large datasets (i.e.,  $\mathcal{P}^k$ ) and running the GA process. Therefore, our NAS search can be formulated as the generation of the two sets  $\mathcal{P}^k$  and  $\mathcal{S}^{k+1}$  at iteration k as follows:

$$\begin{cases} \mathcal{P}^k = \left\{ (s, \mathsf{ACC\_avg}(s), \mathsf{ET\_avg}(s)) \mid s \in S^k \right\} \\ S^{k+1} = \mathsf{Top\_GA}_N(\mathcal{S}^k) \cup \mathcal{S}^k \end{cases} \tag{5}$$

where  $\operatorname{Top\_GA}_N$  a function that returns the best N GA offspring architectures from an input set of parent architectures  $\mathcal{S}^k$  ordered based on the estimated accuracy and ET cost predictors.

# V. EXPERIMENTAL EVALUATION

In this section, we experimentally evaluate our NAS framework for an image classification task dedicated to edge applications.

## A. Experimental setup

Similarly to Section III, we use an image classification task on CIFAR-10 to evaluate our NAS framework on a quad-core edge TPU (cf. Appendix A). Our search space is built on a fixed 12-block-deep MobileNetV2 backbone. Early exits can be mounted in the positions denoted by letters in Table III. The search parameters are the depth, position, and number of early exits, which are encoded using a one-hot representation. The exit-point classifier consists of max-pooling operators that reduce the input tensors' height and width to 4×4 tensors with the same number of channels, as done in [31], followed by one or two linear layers with ReLU6 activation functions. We constrain newly generated EENN architectures according to  $\theta = 50\%$  and  $\mu = 50\%$ .

# B. NAS Framework Results

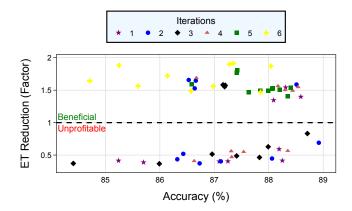

Figure 6 presents the reduction in the ET\_avg relative to the static backbone (where all samples exit at the final stage without considering intermediate exit overhead) on the y-axis,

Fig. 6. The development of the search with respect to accuracy and EENN ET reduction (i.e. ratio of ET\_avg and the respective static architecture ET, without early exits). More exploration tends to yield architectures with high accuracy and high ET reduction.

and the x-axis shows ACC\_avg. The figure reveals that our NAS explores the search space covering inefficient models with low accuracy and high ET\_avg and tends to exploit local regions where both objectives are well-balanced as iterations increase. With more iterations, the inherent random nature of the search is reduced, and the NAS begins to avoid low-outcome regions of the search space and exploit others more promising for better trade-offs (e.g., iteration 5). However, due to the stochasticity of the GA operators, a few inefficient architectures can still be encountered (e.g., iteration 6). Nevertheless, efficient architectures can be found with as little as 5 NAS iterations, which can be explained by the presence of the constraints on the overhead and exit ratios that were added to our search space.

Furthermore, we can also separate the models based on their profitability, i.e. when early exiting brings a gain compared to the static backbone (see dotted line in Figure 6). Across the entire dataset, the NAS process identifies architectures that are notably more efficient than their static counterparts. These NAS-optimized architectures can achieve improvements exceeding 50%. This highlights the potential benefits of enhancing conventional networks with early exiting mechanisms, particularly when tailored to specific use-case objectives.

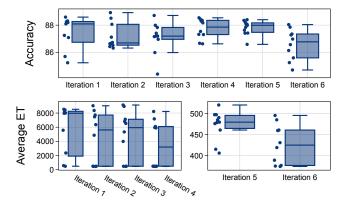

For better insights on the NAS models evolution, we visualize the distribution of accuracy and ET\_avg across NAS iterations in Figure 7. We observe in the first iterations a large exploration of the search space with different architectures of variable performance (e.g., models with an ET\_avg exceeding 8000 J x cycles). As the number of iterations grows, the NAS capitalizes on previously selected best-performing architectures thus increasing the overall mean accuracy and decreasing the overall mean ET\_avg of the found models. Moreover, the balancing effect of the NAS problem conflictual objectives can be observed from iterations 5 and 6 where the mean accuracy was slightly reduced to gain in terms of ET. This is mainly due to an implicit higher weight given to ET\_avg from the ranking of generated architectures after fairly stabilizing accuracy.

Fig. 7. Distribution over EENN models in terms of Accuracy (in %) and Average ET (in J x cycles) across NAS iterations.

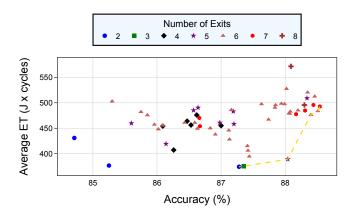

#### C. Analysis of Efficient Architectures

In this section, we analyze a subset of efficient architectures explored during the NAS process with  $ET_{avg} < 1000$ . As seen in Figure 8, there is a notable concentration of architectures with a high number of exits. This observation can be explained by the fact that a greater number of exits generally improves performance, as it provides more opportunities for input samples to terminate earlier in the network, thereby reducing computational costs. Specifically, additional exits allow for the early termination of input samples that can be processed more quickly, leading to lower overall resource usage. However, the benefits of increasing exits are not without trade-offs. A greater number of exits may negatively impact model accuracy due to the amplification of the cascading effect in gradient propagation during backpropagation. As the number of exits increases, the gradients may become more dispersed, potentially reducing the effectiveness of weight updates. Additionally, a higher exit count can impose greater demands on the hardware, particularly by increasing reliance on max-pooling operations and inter-core data transfers, which can reduce computational efficiency. Furthermore, we observe from the landscape that accuracy improves with a higher number of exits, albeit at the expense of a higher ET<sub>avg</sub>. Indeed, the Pareto-optimal architectures (gold line in Figure 8) follow the same trend and prove that our NAS strives to balance the trade-off between accuracy and computational efficiency.

Even though our NAS framework brings new constraints to the training (i.e., quantization, last exit ratio) and optimizes more complex hardware-related metrics (i.e., energy and latency via DSE), we intend to compare our efficient models with similar studies. We compare against EDANAS [10] and NACHOS [11] with which we have close initial conditions where EENN backbones are built on MobileNets and trained on CIFAR-10. It is worth noting three major differences: (1) their hardware cost is modeled with the number of MAC operations, (2) their training procedure is based on [41] whereas our models are trained using linear scalarization under quantization, and (3) their backbone parameters (e.g., kernel size, depth) are extra dimensions of the search space, contrarily to our case where the backbone is fixed. In Table II, we report

Fig. 8. Subset of efficient architectures (where  $ET_avg < 1000$ ) from the NAS showing the Pareto front (gold line) with varying number of exits.

the accuracy and MAC reduction of the best models from EDANAS and NACHOS along with a Pareto optimal model from our NAS (c.f., star marker in the Pareto front gold line in Figure 8). We show that our framework is competitive yielding highly accurate and MAC-efficient architectures. The added constraints in our NAS helped the search be more effective in finding architectures that are both hardware friendly (i.e., overhead) and that benefit well from early exiting (i.e., last exit ratio). Overall, thanks to the constraints we impose on our NAS framework, we are able to find well-adapted EENN models with reduced design time for fast deployment. Furthermore, with a rich Pareto front, the NAS facilitates the identification of the most suitable model aligned with real-world performance and resource requirements.

TABLE II

COMPARISON OF EFFICIENT MODELS IN TERMS OF ACCURACY AND MAC

OPERATIONS FROM PREVIOUS EENN-SPECIFIC NAS STUDIES.

| Method      | Precision | Accuracy (%) | MAC Reduction (%) |

|-------------|-----------|--------------|-------------------|

| EDANAS [10] | FP32      | 81.10        | 36.79             |

| NACHOS [11] | FP32      | 72.86        | 58.99             |

| Ours        | INT8      | 88.04        | 56.46             |

## VI. CONCLUSION

In this paper, we addressed the challenges associated with deploying EENN on resource-constrained edge devices. We studied the impacts of quantization and EENN design on the model-hardware interaction and concluded that small differences in quantization levels and EENN mounting point positions can lead to significant differences in performance and energy efficiency. To this end, we introduced a hardware-aware NAS framework that incorporates the effects of quantization and optimizes the hardware allocation of EENN models on multi-core edge accelerators using Stream, with the aim of finding efficient architectures in terms of accuracy, energy efficiency, and latency. Our NAS framework was tested on an image classification task using a quad-core edge TPU and demonstrated promising Pareto-optimal architectures with high accuracy and low energy-delay product. Future investigations will focus on further enhancing the computational

efficiency of EENN models. This will include exploring the potential benefits of layer fusion, where exit decisions are based on small chunks of processed network layers. Additionally, we intend to investigate alternative metrics for early exit decision-making, such as per-layer neuronal activity or hardware-specific metrics, which could provide a more nuanced evaluation of feature expressivity. Finally, we aim to develop hardware-aware techniques for training EENN models to meet the specific constraints of deployment platforms and application-related requirements.

#### **APPENDIX**

In this appendix, we present further details about the backbone architecture, the models' training configuration, the accelerator architecture used in our experiments, and the adopted quantization-aware training strategy.

## A. Implementation Details

Backbone Architecture: Due to a resolution mismatch, we adopt a modified version of the original MobileNetV2 architecture [42] described in Table III. We set all depthwise convolution kernel sizes, padding, and MobileNet blocks' expansion rates to 3, 1, and 6, respectively. Each bottleneck is composed of Repetition times blocks where each block is a sequence of 3 convolutions. The second convolution is when the number of channels is multiplied by the expansion factor. We allow early exits to be mounted between blocks of the bottlenecks A through J, thus having 10 possible positions. The last exit is always mounted at the end of the network, at position K.

TABLE III

MOBILENETV2 WITH EARLY EXITS MOUNTING POINTS

| Operator   | Repetition | Exit Index | Channels | Strides |

|------------|------------|------------|----------|---------|

| conv2d     | 1          | -          | 32       | 1       |

| bottleneck | 1          | -          | 16       | 1       |

| bottleneck | 2          | A, B       | 24       | 1       |

| bottleneck | 2          | C, D       | 32       | 1       |

| bottleneck | 2          | E, F       | 64       | 2       |

| bottleneck | 2          | G, H       | 96       | 1       |

| bottleneck | 2          | I, J       | 160      | 2       |

| bottleneck | 1          | K          | 320      | 1       |

**Training:** We train all EENN networks for 100 epochs using mini-batch gradient descent with a learning rate of  $10^{-3}$ , a momentum of 0.9, a weight decay of 5e-4, and a batch size of 128. Particularly for image classification, for a dataset  $\mathcal{D}$  of size  $|\mathcal{D}|$ , the exit ratio of an early exit i is defined as follows:

$$ER_i = \frac{1}{|\mathcal{D}|} \sum_{d \in \mathcal{D}} \mathbb{1}\{ \max \hat{\mathbf{y}}_i \ge \tau \land \forall j < i, \max \hat{\mathbf{y}}_j < \tau \} \quad (6)$$

where  $\mathbb{1}(.)$  is the function returning 1 when the boolean expression within is true and 0 otherwise,  $\tau$  is a user-defined threshold describing the minimum confidence to acquire for a sample to exit at exit i, and  $\hat{\mathbf{y}}_i$  is the softmax vector of probabilities over all classes of an input sample d at exit i. All experiments were conducted on a 16GB RTX 4080 GPU.

Accelerator Architecture: Our modeled edge accelerator is a quad-core accelerator whose computing cores are modelled using Google's Edge TPU architecture [43] with extra cores for pooling operations and SIMD to handle element-wise additions and multiplications. Each compute core is capable of executing 512 MACs/cycle and includes a local 2 MiB SRAM scratchpad memory for activations. An off-chip memory is linked to the compute cores with a bandwidth of 64 bits/cycle. The relative energy costs for the memories are scaled from [44]. For the quantization-aware training we take into account flexible precision both at the MAC compute level and the levels of the memory hierarchy. Finally, based on our definition of the quad-core edge TPU (i.e. operational arrays and memory hierarchy), we launch Stream to obtain relevant hardware cost metrics for an input workload.

## B. Quantization-aware Training of EENN

Training EENN is a MOO in which m objective functions (corresponding to the loss of every exit point) are simultaneously optimized. We can convert this MOO into a single-objective problem via linearly weighted scalarization (LS) as follows:

$$\mathcal{L}_{LS} = \sum_{i=1}^{m} \lambda_i \mathcal{L}_i \tag{7}$$

where  $\mathcal{L}_{LS}$  is the linearly scalarized loss, and  $\lambda_i$  is the  $i^{th}$  loss preference value. We set all preference values to 1, as in [31], [32]. Furthermore, be they static or dynamic, DL networks must be quantized before deployment on modern edge accelerators. We linearly quantize weights and activations where each real value r is mapped into  $Q(r) \in [-c, c]$  and linearly quantized into b bits thus yielding:

$$Q(r) = \left[ \max\left(-c, \frac{\min(r, c)}{s}\right) \right] \times s \tag{8}$$

where s is the scaling factor defined as:

$$s = \frac{c}{2^{b-1} - 1} \tag{9}$$

The values of c are set for each layer such that the KL-divergence between the real and quantized values  $\mathcal{D}_{KL}(r||Q(r))$  is minimal, as in [45].

#### REFERENCES

- B. R. Bartoldson, B. Kailkhura, and D. Blalock, "Compute-efficient deep learning: algorithmic trends and opportunities," *Journal of Machine Learning Research*, vol. 24, no. 1, pp. 5465-5541, Jan. 2024.

- [2] G. Menghani, "Efficient Deep Learning: A Survey on Making Deep Learning Models Smaller, Faster, and Better," ACM Computing Surveys, vol. 55, issue 12, no. 259, pp. 1-37, Dec. 2023.

- [3] Y. Han, G. Huang, S. Song, L. Yang, H. Wang, and Y. Wang, "Dynamic Neural Networks: A Survey," *IEEE Transactions on Pattern Analysis and Machine Intelligence*, vol. 44, no. 11, pp. 7436-7456, Nov. 2021.

- [4] J. Hu, L. Shen, and G. Sun, "Squeeze-and-excitation networks," Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition, June 2018.

- [5] H. Gao, X. Zhu, S. Lin, and J. Dai, "Deformable Kernels: Adapting Effective Receptive Fields for Object Deformation," *International Conference on Learning Representations*, May 2019.

- [6] Y. Chen, X. Dai, M. Liu, D. Chen, L. Yuan, and Z. Liu, "Dynamic Relu," Proceedings of the Sixteenth European Conference on Computer Vision, pp. 351–367, August 2020.

- [7] D. Shan, Y. Luo, X. Zhang, and C. Zhang, "DRRNets: Dynamic Recurrent Routing via Low-Rank Regularization in Recurrent Neural Networks," *IEEE Transactions on Neural Networks and Learning Systems*, vol. 34, no. 4, pp. 2057-2067, 2023.

- [8] Z. Jie, P. Sun, X. Li, J. Feng, and W. Liu, "Anytime Recognition with Routing Convolutional Networks," *IEEE Transactions on Pattern Analysis* and Machine Intelligence, vol. 43, no. 6, pp. 1875-1886, June 2021.

- [9] S. Laskaridis, A. Kouris, and N. D. Lane, "Adaptive Inference through Early-Exit Networks: Design, Challenges and Directions," *Proceedings* of the Fifth International Workshop on Embedded and Mobile Deep Learning, pp. 1-6, June 2021.

- [10] M. Gambella and M. Roveri, "EDANAS: Adaptive Neural Architecture Search for Early Exit Neural Networks," 2023 International Joint Conference on Neural Networks, pp. 1-8, 2023.

- [11] M. Gambella, J. Pomponi, S. Scardapane, and M. Roveri, "NACHOS: Neural Architecture Search for Hardware Constrained Early Exit Neural Networks," arXiv preprint, arXiv:2401.13330, Jan. 2024.

- [12] H. Bouzidi, M. Odema, H. Ouarnoughi, M. A. Al Faruque, and S. Niar, "HADAS: Hardware-Aware Dynamic Neural Architecture Search for Edge Performance Scaling," *Design, Automation & Test in Europe Conference & Exhibition*, pp. 1-6, 2023.

- [13] A. Ansari and T. Ogunfunmi, "Hardware Acceleration of a Generalized Fast 2-D Convolution Method for Deep Neural Networks," *IEEE Access*, vol. 10, pp. 16843-16858, 2022.

- [14] J. Kim, S. Kim, K. Choi and I. -C. Park, "Hardware-Efficient SoftMax Architecture With Bit-Wise Exponentiation and Reciprocal Calculation," *IEEE Transactions on Circuits and Systems*, vol. 71, no. 10, pp. 4574-4585, Oct. 2024.

- [15] A. Symons, L. Mei, S. Colleman, P. Houshmand, S. Karl and M. Verhelst, "Stream: Design Space Exploration of Layer-fused DNNs on Heterogeneous Dataflow Accelerators," IEEE Transactions on Computers, 2024.

- [16] A. Parashar, P. Raina, Y. S. Shao, Y.-H. Chen, V. A. Ying, A. Mukkara, R. Venkatesan, B. Khailany, S. W. Keckler, and J. Emer, "Timeloop: A Systematic Approach to DNN Accelerator Evaluation," in *IEEE Interna*tional Symposium on Performance Analysis of Systems and Software, pp. 304–315, March 2019.

- [17] L. Mei, P. Houshmand, V. Jain, S. Giraldo, and M. Verhelst, "ZigZag: Enlarging Joint Architecture-Mapping Design Space Exploration for DNN Accelerators," *IEEE Transactions on Computers*, vol. 70, no. 8, pp. 1160–1174, 2021.

- [18] Ghodrati, Soroush, et al. "Planaria: Dynamic architecture fission for spatial multi-tenant acceleration of deep neural networks," 53rd Annual IEEE/ACM International Symposium on Microarchitecture, IEEE, 2020.

- [19] Shao, Yakun Sophia, et al. "Simba: Scaling deep-learning inference with multi-chip-module-based architecture," Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture, 2019.

- [20] Radway, Robert M., et al. "Illusion of large on-chip memory by networked computing chips for neural network inference," *Nature Electronics*, 4.1 (2021): 71-80.

- [21] Jia, Hongyang, et al. "Scalable and programmable neural network inference accelerator based on in-memory computing," *IEEE Journal of Solid-State Circuits*, 57.1 (2021): 198-211.

- [22] Kwon, Hyoukjun, et al. "Heterogeneous dataflow accelerators for multi-DNN workloads," 2021 IEEE International Symposium on High-Performance Computer Architecture, IEEE, 2021.

- [23] P. Houshmand, G.M. Sarda, V. Jain, K. Ueyoshi, I.A. Papistas, and M. Shi, "DIANA: An End-to-End Hybrid DIgital and ANAlog Neural Network SoC for the Edge," *IEEE Journal of Solid-State Circuits*, vol. 58, no. 1, pp. 203-215, Jan. 2023.

- [24] B. Biggs, C. Bouganis, and G. Constantinides, "ATHEENA: A Toolflow for Hardware Early-Exit Network Automation," Proceedings of the IEEE thirty-first Annual International Symposium on Field-Programmable Custom Computing Machines, pp. 121-132, May 2023.

- [25] H. Benmeziane, K. El Maghraoui, H. Ouarnoughi, S. Niar, M. Wistuba, and N. Wang, "Hardware-Aware Neural Architecture Search: Survey and Taxonomy", *Proceedings of the Thirtieth International Joint Conference on Artificial Intelligence*, pp. 4322-4329, Aug. 2021.

- [26] H. Cai, C. Gan, T. Wang, Z. Zhang, and S. Han, "Once for All: Train One Network and Specialize it for Efficient Deployment", The Eighth International Conference on Learning Representations, 2020.

- [27] K. T. Chitty-Venkata, Y. Bian, M. Emani, V. Vishwanath and A. K. Somani, "Differentiable Neural Architecture, Mixed Precision and Accelerator Co-Search," *IEEE Access*, vol. 11, pp. 106670-106687, 2023.

- [28] Z. Lu, I. Whalen, V. Boddeti, Y. Dhebar, K. Deb, E. Goodman, and W. Banzhaf, "Nsga-net: Neural architecture search using multiobjective

- genetic algorithm," *Proceedings of the Genetic and Evolutionary Computation Conference*, pp. 419-427, July 2019.

- [29] A. Marchisio, A. Massa, V. Mrazek, B. Bussolino, M. Martina, and M. Shafique, "Nascaps: A framework for neural architecture search to optimize the accuracy and hardware efficiency of convolutional capsule networks," *Proceedings of the 39th International Conference on Computer-Aided Design*, no. 114, pp. 1-9, Nov. 2020.

- [30] H. Cai, L. Zhu, and S. Han, "ProxylessNAS: Direct Neural Architecture Search on Target Task and Hardware", The Seventh International Conference on Learning Representations, 2019.

- [31] Y. Kaya, S. Hong, and T. Dumitras, "Shallow-Deep Networks: Understanding and Mitigating Network Overthinking," *Proceedings of the 36th International Conference on Machine Learning*, vol. 97, pp. 3301-3310, June 2019.

- [32] Z. Yuan, B. Wu, G. Sun, Z. Liang, S. Zhao, W. Bi, "S2DNAS: Transforming Static CNN Model for Dynamic Inference via Neural Architecture Search," *Proceedings of the Sixteenth European Conference on Computer Vision*, vol. 12347, pp. 175-192, Aug. 2020.

- [33] Z. Yuan, X. Liu, B. Wu, and G. Sun, ENAS4D: Efficient Multistage CNN Architecture Search for Dynamic Inference, arXiv preprint, arXiv:2009.09182, Sep. 2020.

- [34] A. Krizhevsky, "Learning Multiple Layers of Features from Tiny Images," Tech. Report, 2009.

- [35] B. Colby, et al.; "MLPerf Tiny Benchmark," Proceedings of the Neural Information Processing Systems Track on Datasets and Benchmarks, vol. 1, 2021.

- [36] A. Symons, L. Mei and M. Verhelst, "LOMA: Fast Auto-Scheduling on DNN Accelerators through Loop-Order-based Memory Allocation," *IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems*, pp. 1-4, Jun. 2021.

- [37] S. Karl, A. Symons, N. Fasfous and M. Verhelst, "Genetic Algorithm-based Framework for Layer-Fused Scheduling of Multiple DNNs on Multi-core Systems," *Design, Automation & Test in Europe Conference & Exhibition*, pp. 1-6, Apr. 2023.

- [38] R. Miccini, A. Zniber, C. Laroche, T. Piechowiak, M. Schoeberl, L. Pezzarossa, O. Karrakchou, J. Sparsø, and M. Ghogho, "Dynamic nsNET2: Efficient Deep Noise Suppression with Early Exiting," 2023 IEEE 33rd International Workshop on Machine Learning for Signal Processing, pp. 1-6, Sept. 2023.

- [39] Z. Zhang, W. Zhu, J. Zhang, P. Wang, R. Jin, and T.-S. Chung, "PCEE-BERT: Accelerating BERT Inference via Patient and Confident Early Exiting", Findings of the Association for Computational Linguistics: NAACL, pages 327–338, 2022.

- [40] J. Wu, X. Dai, D. Chen, Y. Chen, M. Liu, Y. Yu, Z. Wang, Z. Liu, M. Chen, and L. Yuan, "Stronger NAS with weaker predictors," *Proceedings of the 35th International Conference on Neural Information Processing Systems*, pp. 28904-28918, June 2024.

- [41] J. Pomponi, S. Scardapane, and A. Uncini, "A probabilistic reinterpretation of confidence scores in multi-exit models," *Entropy*, vol. 24, no. 1, 2022.

- [42] M. Sandler, A. Howard, M. Zhu, A. Zhmoginov, and L. -C. Chen, "MobileNetV2: Inverted Residuals and Linear Bottlenecks", *Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition*, pp. 4510-4520, June 2018.

- [43] "Accelerator Module datasheet," https://coral.ai/docs/module/datasheet/, (accessed Oct. 30, 2024).

- [44] S. Han, X. Liu, H. Mao, J. Pu, A. Pedram, M.A. Horowitz, and W.J. Dally, "EIE: efficient inference engine on compressed deep neural network," ACM SIGARCH Computer Architecture News, pp. 243–254, vol. 44, Issue 3, Jun. 2016.

- [45] T. Wang, K. Wang, H. Cai, J. Lin, Z. Liu, H. Wang, Y. Lin, and S. Han, "APQ: Joint Search for Network Architecture, Pruning and Quantization Policy," *Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition*, pp. 2075-2084, 2020.