# Investigation of the Physical Mechanism behind Retention Loss in FeFETs with MIFIFIS Gate Structure

Tao Hu, Zeqi Chen, Runhao Han, Xinpei Jia, Jia Yang, Mingkai Bai, Ruoyao Ji, Yajing Ding, Mengwei Zhao, Yuhan Li, Kaiyi Li, Wenbo Fan, Xianzhou Shao, Xiaoqing Sun, Kai Han, Jing Zhang, Yanrong Wang, Junshuai Chai, Hao Xu, Xiaolei Wang, Wenwu Wang and Tianchun Ye

Abstract—A **Metal-Gate Blocking** Layer (GBL)-Ferroelectric-Tunnel Dielectric Layer (TDL)-Ferroelectric -Channel Insulator (Ch.IL)-Si (MIFIFIS) structure is proposed to achieve a larger MW for applications in Fe-NAND. However, the large retention loss (RL) in the MIFIFIS structure restricts its application. In this work, we vary the physical thickness of the GBL and TDL, and conduct an in-depth analysis of the energy bands of the gate structure to investigate the physical mechanism behind the RL in FeFETs with the MIFIFIS structure. The physical origin of the RL is that the electric field direction across the TDL reduces the potential barrier provided by the ferroelectric near the silicon substrate. Based on the above physical mechanism, the RL can be reduced to 12% and 0.2% by redesigning the gate structure or reducing the pulse amplitude, respectively. Our work contributes to a deeper understanding of the physical mechanism behind the RL in FeFETs with the MIFIFIS gate structure. It provides guidance for enhancing the reliability of FeFETs.

Index Terms—Ferroelectric, retention loss,  $Hf_{0.5}Zr_{0.5}O_2$ , MIFIFIS, FeFETs.

# I. INTRODUCTION

SINCE the discovery of ferroelectricity in doped  $HfO_2$  in 2011 [1], hafnia-based silicon channel ferroelectric field-effect transistors ( $HfO_2$  Si-FeFETs) have attracted widespread research interest as a strong candidate for

This work was supported in part by the National Natural Science Foundation of China under Grant Nos. 92264104 and 52350195, in part by National Key Research and Development Program of China under Grant No. 2022YFB4400300, and Supported by the Postdoctoral Fellowship Program of CPSF under Grant No. GZC20232925. (Tao Hu and Zeqi Chen contributed equally to this work.) (Corresponding authors: Hao Xu, Junshuai Chai.)

Tao Hu, Zeqi Chen, Runhao Han, Xinpei Jia, Jia Yang, Mingkai Bai, Ruoyao Ji, Yajing Ding, Mengwei Zhao, Yuhan Li, Kaiyi Li, Wenbo Fan, Xianzhou Shao, Xiaoqing Sun, Junshuai Chai, Hao Xu, Xiaolei Wang, Wenwu Wang and Tianchun Ye are with the Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China, and also with the School of Integrated Circuits, University of Chinese Academy of Sciences, Beijing 100049, China (e-mail: xuhao@ime.ac.cn; chaijunshuai@ime.ac.cn).

Kai Han is with the School of Physics and Electronic Information, Weifang University, Weifang 261061, Chian.

Yanrong Wang and Jing Zhang are with the School of Information Science and Technology, North China University of Technology, Beijing 100144, China.

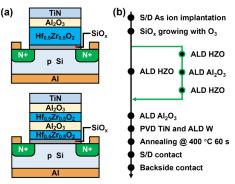

Fig. 1. (a) Schematic and (b) fabrication process flow of FeFETs.

nonvolatile memory with low write voltage, high switching speed, CMOS compatibility, and excellent scalability [2-17]. For FeFETs with the MFIS gate structure, the large amount of charge injected from the silicon channel shields the spontaneous polarization of the ferroelectric [18-21]. This results in a narrow memory window (MW), and the MW is generally limited to less than 2 V [22-25], which severely restricts its application in multi-bit memory.

Recently, a Metal-Gate Blocking Layer (GBL)-Ferroelectric -Tunnel Dielectric Layer (TDL)-Ferroelectric-Channel Insulator (Ch.IL)-Si (MIFIFIS) structure has been proposed to achieve a larger MW [26-28]. Unfortunately, the retention characteristics of the MIFIFIS gate structure exhibit a significant degradation. The retention loss (RL) exceeds 25%, which limits its application in Fe-NAND [29, 30]. Therefore, we conducted a detailed study on the physical mechanism behind the RL in the MIFIFIS gate structure. This mechanism is attributed to the direction of the electric field across TDL pointing towards the silicon substrate, which reduces the potential barrier provided by the ferroelectric near the silicon substrate

In addition, to reverse the electric field direction across the TDL (specifically, directing it toward the silicon substrate), we propose the following strategies: (i) inserting a charge-trapping layer (CTL) on both sides of the TDL to increase the charge density at the TDL ends, or (ii) reducing the operating voltage amplitude to decrease the charge density at the GBL/FE interface. Using these methods, the RL can be reduced to 12% and 0.2%, respectively. This study provides guidance for improving FeFET reliability through gate stack engineering

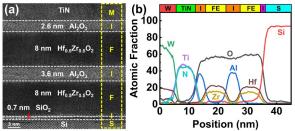

Fig. 2. (a) HRTEM images and (b) EDS of the 8483 MIFIFIS structure.

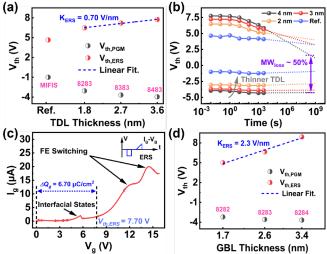

Fig. 3. The measurement results of (a)  $V_{th}$  and (b) retention characteristics corresponding to the maximum MW. (c) The  $I_g$ - $V_g$  curve of the reading process after the erase pulse. (d) The dependence of  $V_{th}$  corresponding to the maximum MW on the physical thickness of the GBL.

and optimizing pulse conditions.

# II. DEVICE FABRICATION AND CHARACTERIZATION

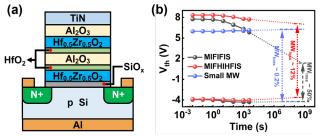

We fabricated FeFETs with different gate structures, as shown in Fig. 1(a). One is a TiN/Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/SiO<sub>x</sub>/Si (MIFIS) structure with 18 nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> and 3 nm Al<sub>2</sub>O<sub>3</sub> as the control sample, and the other is a TiN/Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/ Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/SiO<sub>x</sub>/Si (MIFIFIS) structure with 8 nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>. For the MIFIFIS structure, when the TDL thickness is 2 nm, the GBL thickness is 2-, 3-, or 4 nm, and when the GBL thickness is 3 nm, the TDL thickness is 2-, 3-, or 4 nm. For simplicity, we denote the gate stacks by their ferroelectric/TDL/ferroelectric/GBL nominal thicknesses. For example, 8/2/8/2 (8282), 8/2/8/3 (8283), and 8/2/8/4 (8284). Fig. 1(b) shows the fabrication process flow. This detailed process flow is described in our previous works [31, 32]. All of the fabrication processes of the MIFIS structure are the same as the MIFIFIS structure, except that the gate structure and thickness of the dielectric layer are different.

Fig. 2 shows the High-Resolution Transmission Electron Microscopy (HRTEM) images and the Energy Dispersion Spectrometer (EDS) of the 8483 MIFIFIS structure.

In this work, the gate length/width (L/W) of the FeFETs is 5/150 µm. The electrical measurements were performed by Keysight B1500A. The threshold voltage ( $V_{th}$ ) is extracted by the constant current method.

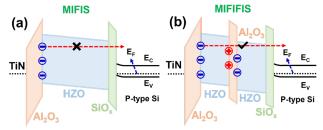

Fig. 4. The energy band diagram of (a) the MIFIS structure and (b) the 8283 MIFIFIS structure after the erase operation.

### III. RESULTS AND DISCUSSION

We first study the maximum MW of the FeFETs with different gate structures. Here, we find the maximum MW by adopting different program/erase (P/E) voltage amplitudes under the pulse width of 50 µs for each sample. Fig. 3(a) shows the dependence of  $V_{th}$ , which corresponds to the maximum MW, on the TDL thickness. For the MIFIS structure and the 8283 MIFIFIS structure, at the same physical thickness of the gate stack, the 8283 MIFIFIS structure shows a maximum MW of 9.5 V, while the MIFIS gate structure shows a maximum MW of 5.7 V. Therefore, inserting an Al<sub>2</sub>O<sub>3</sub> interlayer in the middle of the ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> can increase the MW of FeFETs, which is consistent with the phenomenon reported in [33, 34]. This is attributed to the presence of the trapped charges at both ends of the TDL [7, 33]. Furthermore, we find that  $V_{th,ERS}$ increases linearly with the increase of the TDL thickness. According to (1), this slope K<sub>ERS</sub> in Fig. 3(a) represents the magnitude of the electric field across the TDL at V<sub>g</sub>=V<sub>th,ERS</sub>.

$$V_{th} = \varphi_{MS} + 2\varphi_{B} + \frac{1}{C_{TDL}} \bullet (Q_{TDL} + Q_{t_{-}Ch} + Q_{Si_{-}th}) + \frac{1}{C_{GBL}} \bullet (Q_{t_{-}GBL} + Q_{t_{-}Ch} + Q_{Si_{-}th}) + \frac{2}{C_{FE}} \bullet$$

$$(P_{FE_{-}th} + Q_{t_{-}Ch} + Q_{Si_{-}th}) + \frac{1}{C_{BIL}} \bullet Q_{Si_{-}th}$$

$$(1)$$

Here,  $Q_{t\_Ch}$ ,  $Q_{t\_TDL}$ ,  $Q_{t\_GBL}$ , and  $Q_{Si\_th}$  respectively represent the charge densities at the GBL/FE, TDL/FE, FE/Ch.IL interfaces, and on the silicon substrate when  $V_g = V_{th}$ .

We investigate the retention characteristics under the maximum MW. Fig. 3(b) shows the measurement results of retention characteristics. We find that the retention characteristics of the MIFIFIS structure have significantly degraded compared to the MIFIS structure, and the RL increases with the increase of the TDL thickness. In addition, we find that the RL is mainly caused by the rapid degradation of the  $V_{th,ERS}$ . Therefore, we need to investigate the physical origin of the  $V_{th,ERS}$  degradation when  $V_g{=}0$  V after the erase operation. The latest research results indicate that the de-trapping of the trapped charges at the GBL/FE onto the silicon substrate leads to the RL of the  $V_{th,ERS}$  in the MIFIS gate structure [35, 36]. Thus, we investigate the effect of the TDL insertion and increased TDL thickness on the de-trapping potential barrier of the trapped charges.

We discuss in detail the effect of the TDL insertion on the de-trapping potential barrier through an in-depth analysis of the energy bands. We measure the same  $I_g$ - $V_g$  curve as the reading process after the erase operation. Fig. 3(c) shows the

Fig. 5. (a) Schematic of the MIFHIHFIS-FeFETs. (b) Comparison between the retention characteristics.

measurement results. We find that there is almost no switching of the ferroelectric polarization during the 0-V<sub>th,ERS</sub>. Therefore,  $I_g$  is a current formed by the background capacitance response of the gate stack. We can integrate  $I_g$  to obtain  $\Delta Q_g$ , and the change in the electric field of each layer in the gate stack can be calculated by (2)

$$\Delta E = \frac{\Delta Q_g}{\varepsilon_0 \varepsilon_r} \tag{2}$$

Therefore, we can calculate the electric field across the TDL at  $V_g=0$  V from the electric field across the TDL at  $V_g=V_{th,ERS}$ . We find that the electric field across the TDL at  $V_g=0$  V is -1.41 MV/cm (specifically, directing it toward the metal gate), which is opposite to the direction of the electric field formed by the trapped charges on both sides of the TDL, and the same direction as the electric field formed by the trapped charges at the GBL/FE interface, as shown in Fig. 4. This is because  $Q_{t\_GBL}$  is significantly larger than  $Q_{t\_TDL}$ , which is consistent with the slope in Fig. 3(d) being greater than the slope in Fig. 3(a). The electric field across the TDL at  $V_g=0$  V reduces the potential barrier provided by the ferroelectric near the silicon substrate, as shown in Fig. 4, resulting in a significant RL in the MIFIFIS structure compared to the MIFIS structure.

To reverse the electric field direction across the TDL (specifically, directing it toward the silicon substrate), we propose the following strategies: (i) increasing the charge density at the TDL ends. Therefore, we insert a 1.5 nm HfO<sub>2</sub> CTL on both sides of the TDL to increase the charge density at the TDL ends. Fig. 5(a) shows the optimized device structure, namely the MIFHIHFIS structure. (ii) Reducing the charge density at the GBL/FE interface. Therefore, we reduce the erase pulse amplitude to decrease the charge density at the GBL/FE interface. Using these methods, the RL can be reduced to 12% and 0.2%, respectively, as shown in Fig. 5(b).

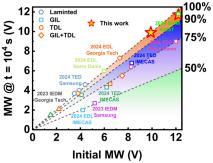

Fig. 6 shows the benchmark of our work. Our device demonstrates the ability to achieve both high MW and good retention characteristics simultaneously.

# IV. CONCLUSION

This work investigates the physical mechanism behind the retention loss of the MIFIFIS-FeFET. This is attributed to the direction of the electric field pointing towards the metal gate across the TDL at Vg=0 V, which reduces the potential barrier contributed by the ferroelectric near the silicon substrate, resulting in a significant RL. By adopting the following strategies: (i) inserting a CTL on both sides of the TDL and (ii) reducing the erase pulse amplitude, RL can be reduced to 12% and 0.2%, respectively. Our work contributes to a deeper

Fig. 6. The benchmark for the retention characteristics of FeFET.

understanding of the physical mechanism behind the RL in FeFETs with the MIFIFIS gate structure.

## **REFERENCES**

- [1] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, "Ferroelectricity in hafnium oxide thin films," *Appl. Phys. Lett.*, vol. 99, no. 10, Sept. 2011, doi: 10.1063/1.3634052.

- [2] M. Trentzsch, S. Flachowsky, R. Richter, J. Paul, B. Reimer, D. Utess et al., "A 28nm HKMG super low power embedded NVM technology based on ferroelectric FETs," in *IEDM Tech. Dig.*, Dec. 2016, pp. 11.5.1-11.5.4, doi: 10.1109/IEDM.2016.7838397.

- [3] Z. Cai, K. Toprasertpong, M. Takenaka, and S. Takagi, "HZO Scaling and Fatigue Recovery in FeFET with Low Voltage Operation: Evidence of Transition from Interface Degradation to Ferroelectric Fatigue," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185295.

- [4] K. T. Chen, H. Y. Chen, C. Y. Liao, G. Y. Siang, C. Lo, M. H. Liao et al., "Non-Volatile Ferroelectric FETs Using 5-nm Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> With High Data Retention and Read Endurance for 1T Memory Applications," *IEEE Electron Device Lett.*, vol. 40, no. 3, pp. 399-402, Jan. 2019, doi: 10.1109/LED.2019.2896231.

- [5] M. Si, X. Lyu, and P. D. Ye, "Ferroelectric Polarization Switching of Hafnium Zirconium Oxide in a Ferroelectric/Dielectric Stack," ACS Appl. Electron. Mater., vol. 1, no. 5, pp. 745-751, May. 2019, doi: 10.1021/acsaelm.9b00092.

- [6] J. Müller, T. S. Böscke, S. Müller, E. Yurchuk, P. Polakowski, J. Paul et al., "Ferroelectric hafnium oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories," in *IEDM Tech. Dig.*, Dec. 2013, pp. 10.8.1-10.8.4, doi: 10.1109/IEDM.2013.6724605.

- [7] D. Das, H. Park, Z. Wang, C. Zhang, P. V. Ravindran, C. Park et al., "Experimental demonstration and modeling of a ferroelectric gate stack with a tunnel dielectric insert for NAND applications," in *IEDM Tech. Dig.*, Dec. 2023, pp. 1-4, doi: 10.1109/IEDM45741.2023.10413697.

- [8] S. Lim, T. Kim, I. Myeong, S. Park, S. Noh, S. M. Lee et al., "Comprehensive Design Guidelines of Gate Stack for QLC and Highly Reliable Ferroelectric VNAND," in *IEDM Tech. Dig.*, Dec. 2023, pp. 1-4, doi: 10.1109/IEDM45741.2023.10413820.

- [9] S. Yoon, S. I. Hong, D. Kim, G. Choi, Y. M. Kim, K. Min et al., "QLC Programmable 3D Ferroelectric NAND Flash Memory by Memory Window Expansion using Cell Stack Engineering," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185294.

- [10] K. Ni, P. Sharma, J. Zhang, M. Jerry, J. A. Smith, K. Tapily et al., "Critical Role of Interlayer in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Ferroelectric FET Nonvolatile Memory Performance," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2461-2469, Jun. 2018, doi: 10.1109/TED.2018.2829122.

- [11] J. G. Lee, J. Kim, D. I. Suh, I. Kim, G. D. Han, S. W. Ryu et al., "Memory Window Expansion for Ferroelectric FET based Multilevel NVM: Hybrid Solution with Combination of Polarization and Injected Charges," in *Proc. IEEE Int. Memory Workshop (IMW)*, May. 2022, pp. 1-4, doi: 10.1109/IMW52921.2022.9779292.

- [12] C. Y. Liao, Z. F. Lou, C. Y. Lin, A. Senapati, R. Karmakar, K. Y. Hsiang et al., "Superlattice HfO<sub>2</sub>-ZrO<sub>2</sub> based Ferro-Stack HfZrO<sub>2</sub> FeFETs: Homogeneous-Domain Merits Ultra-Low Error, Low Programming Voltage 4 V and Robust Endurance 10<sup>9</sup> cycles for Multibit NVM," in *IEDM Tech. Dig.*, Dec. 2022, pp. 36.6.1-36.6.4, doi: 10.1109/IEDM45625.2022.10019369.

- [13] P. Xu, P. Jiang, Y. Yang, T. Gong, W. Wei, Y. Wang et al., "Demonstration of Large MW and Prominent Endurance in a Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> FeFET With IGZO Channel Utilizing Postdeposition Annealing," *IEEE Electron Device Lett.*, vol. 45, no. 11, pp. 2110-2113, Nov. 2024, doi: 10.1109/LED.2024.3464589.

- [14] M. Hoffmann, A. J. Tan, N. Shanker, Y. H. Liao, L. C. Wang, J. H. Bae et al., "Write Disturb-Free Ferroelectric FETs With Non-Accumulative Switching Dynamics," *IEEE Electron Device Lett.*, vol. 43, no. 12, pp. 2097-2100, Dec. 2022, doi: 10.1109/LED.2022.3212330.

- [15] X. Wang, L. Jiao, Z. Zhou, Z. Zheng, Y. Chen, R. Shao et al., "Investigating the Correlation Between Material Ferroelectricity and Silicon-Channel FeFET Performance: Insights for Material Engineering in Device Optimization," *IEEE Trans. Electron Devices*, vol. 72, no. 7, pp. 3535-3542, May. 2025, doi: 10.1109/TED.2025.3566349.

- [16] F. Zhang, Z. Zhang, J. Yao, X. Zhu, Y. Peng, J. Huo et al., "The Investigation of Reduced Variation Effect in FinFETs With Ultrathin 3-nm Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>," *IEEE Trans. Electron Devices*, vol. 71, no. 5, pp. 2876-2880, May. 2024, doi: 10.1109/TED.2024.3379160.

- [17] Y. Feng, X. Wang, Y. He, Y. Kang, D. Zhang, W. Shi et al., "Record-High Pr (2Pr>40 μC/cm²) in 3 nm (Physical) Ferroelectric HZO Annealed at 450 °C: High-T (85 °C) Electrical Cycling and Oxygen Vacancy Engineering," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2025, pp. 1-3, doi: 10.23919/VLSITechnologyandCir65189.2025.11074816.

- [18] N. Gong, and T. P. Ma, "A Study of Endurance Issues in HfO<sub>2</sub>-Based Ferroelectric Field Effect Transistors: Charge Trapping and Trap Generation," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 15-18, Jan. 2018, doi: 10.1109/LED.2017.2776263.

- [19] E. Yurchuk, J. Müller, S. Müller, J. Paul, M. Pešić, R. v. Bentum et al., "Charge-Trapping Phenomena in HfO<sub>2</sub>-Based FeFET-Type Nonvolatile Memories," *IEEE Trans. Electron Devices*, vol. 63, no. 9, pp. 3501-3507, Sept. 2016, doi: 10.1109/TED.2016.2588439.

- [20] K. Toprasertpong, Z. Y. Lin, T. E. Lee, M. Takenaka, and S. Takagi, "Asymmetric Polarization Response of Electrons and Holes in Si FeFETs: Demonstration of Absolute Polarization Hysteresis Loop and Inversion Hole Density over 2×10<sup>13</sup> cm<sup>-2</sup>," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1-2, doi: 10.1109/VLSITechnology18217.2020.9265015.

- [21] B. Zeng, M. Liao, J. Liao, W. Xiao, Q. Peng, S. Zheng et al., "Program/Erase Cycling Degradation Mechanism of HfO<sub>2</sub>-Based FeFET Memory Devices," *IEEE Electron Device Lett.*, vol. 40, no. 5, pp. 710-713, May. 2019, doi: 10.1109/LED.2019.2908084.

- [22] R. Ichihara, K. Suzuki, H. Kusai, K. Ariyoshi, K. Akari, K. Takano et al., "Re-Examination of Vth Window and Reliability in HfO<sub>2</sub> FeFET Based on the Direct Extraction of Spontaneous Polarization and Trap Charge during Memory Operation," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1-2, doi: 10.1109/VLSITechnology18217.2020.9265055.

- [23] H. Mulaosmanovic, E. T. Breyer, T. Mikolajick, and S. Slesazeck, "Recovery of Cycling Endurance Failure in Ferroelectric FETs by Self-Heating," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 216-219, Feb. 2019, doi: 10.1109/LED.2018.2889412.

- [24] X. Jia, J. Chai, J. Duan, X. Sun, X. Shao, J. Xiang et al., "Investigation of Charge Trapping Induced Trap Generation in Si FeFET With Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>," *IEEE Trans. Electron Devices*, vol. 71, no. 3, pp. 1845-1851, Jan. 2024, doi: 10.1109/TED.2024.3351599.

- [25] D. H. Min, S. Y. Kang, S. E. Moon, and S. M. Yoon, "Impact of Thickness Control of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Films for the Metal–Ferroelectric–Insulator–Semiconductor Capacitors," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1032-1035, Jul. 2019, doi: 10.1109/LED.2019.2917032.

- [26] D. Das, L. Fernandes, P. V. Ravindran, T. Song, C. Park, N. Afroze et al., "Design Framework for Ferroelectric Gate Stack Engineering of Vertical NAND Structures for Efficient TLC and QLC Operation," in *Proc. IEEE Int. Memory Workshop (IMW)*, 12-15 May 2024. 2024, pp. 1-4, doi: 10.1109/IMW59701.2024.10536982.

- [27] L. Fernandes, P. V. Ravindran, J. Chen, M. Tian, D. Das, H. Chen et al., "Optimizing Memory Window for Ferroelectric Nand Applications: An Experimental Study on Dielectric Material Selection and Layer Positioning," *IEEE Trans. Electron Devices*, vol. 72, no. 1, pp. 234-239, Jan. 2025, doi: 10.1109/TED.2024.3504475.

- [28] P. Venkatesan, and A. Khan, "Ferroelectrics for Vertical NAND Flash Applications," in *Proc. IEEE Int. Memory Workshop (IMW)*, May. 2025, pp. 1-4, doi: 10.1109/IMW61990.2025.11026978.

- [29] P. Venkatesan, L. Fernandes, S. Kang, P. Ravikumar, T. Song, C. Park et al., "Pushing the limits of NAND technology scaling with ferroelectrics," MRS Bull., vol. 50, no. 9, pp. 1094-1107, Oct. 2025, doi: 10.1557/s43577-025-00991-y.

- [30] P. Venkatesan, L. Fernandes, P. Ravikumar, C. Park, H. Tran, Z. Wang et al., "Demonstration of Robust Retention in Band Engineered FEFETs for NAND Storage Applications Using Tunnel Dielectric Layer," *IEEE Electron Device Lett.*, vol. 46, no. 3, pp. 397-400, Dec. 2025, doi: 10.1109/LED.2024.3523235.

- [31] T. Hu, X. Sun, M. Bai, X. Jia, S. Dai, T. Li et al., "Enlargement of Memory Window of Si Channel FeFET by Inserting Al<sub>2</sub>O<sub>3</sub> Interlayer on Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>," *IEEE Electron Device Lett.*, vol. 45, no. 5 pp. 825-828, May. 2024, doi: 10.1109/LED.2024.3381966.

- [32] T. Hu, X. Shao, M. Bai, X. Jia, S. Dai, X. Sun et al., "Impact of Top SiO<sub>2</sub> Interlayer Thickness on Memory Window of Si Channel FeFET With TiN/SiO<sub>2</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/SiO<sub>x</sub>/Si (MIFIS) Gate Structure," *IEEE Trans. Electron Devices*, vol. 71, no. 11, pp. 6698-6705, Nov. 2024, doi: 10.1109/TED.2024.3459873.

- [33] P. Venkatesan, C. Park, T. Song, L. Fernandes, D. Das, N. Afroze et al., "Disturb and its Mitigation in Ferroelectric Field-Effect Transistors With Large Memory Window for NAND Flash Applications," *IEEE Electron Device Lett.*, vol. 45, no. 12, pp. 2367-2370, Sept. 2024, doi: 10.1109/LED.2024.3467210.

- [34] P. Venkatesan, A. Padovani, L. Fernandes, P. Ravikumar, C. Park, H. Tran et al., "Enhanced Memory Performance in Ferroelectric NAND Applications: The Role of Tunnel Dielectric Position for Robust 10-Year Retention," May. 2025, pp. 1-7, doi: 10.1109/IRPS48204.2025.10982749.

- [35] H. Choi, G. Kim, H. Shin, Y. Nam, S. Jeon, K. Kim et al., "The Opportunity of Anti-ferroelectrics in FeFET for Emerging Non-Volatile Memory Applications," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, May. 2025, pp. 1-6, doi: 10.1109/IRPS48204.2025.10982822.

- [36] T. Hu, X. Jia, R. Han, J. Yang, M. Bai, S. Dai et al., "Effect of Top Al<sub>2</sub>O<sub>3</sub> Interlayer Thickness on Memory Window and Reliability of FeFETs With TiN/Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>/SiO<sub>x</sub>/Si (MIFIS) Gate Structure," *IEEE Trans. Electron Devices*, vol. 72, no. 11, pp. 5958-5965, Nov. 2025, doi: 10.1109/TED.2025.3607888.