# FLEX: Leveraging FPGA-CPU Synergy for Mixed-Cell-Height Legalization Acceleration

# Xingyu Liu

xliugu@connect.ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

# Yipu Zhang

yzhangqg@connect.ust.hk The Hong Kong University of Science and Technology Kowloon, Hong Kong

# Jiawei Liang

jliangbr@connect.ust.hk The Hong Kong University of Science and Technology Kowloon, Hong Kong

# Chaofang Ma

cmaaw@connect.ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

# Linfeng Du

linfeng.du@connect.ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

# Hanwei Fan

hfanah@connect.ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

# Jiang Xu

jiang.xu@hkust-gz.edu.cn The Hong Kong University of Science and Technology (Guangzhou) Guangzhou, China

# **Abstract**

Legalization is a critical yet time-consuming step in very large-scale integration (VLSI) design, tasked with iteratively relocating standard cells to eliminate overlaps while resolving design rule violations. This process is applied after global placement and repeatedly invoked during VLSI physical design. However, increasing spatial constraints and complex design rules impose significant challenges on existing CPU- and GPU-based legalizers, including suboptimal task assignment, inefficient algorithm, and long hardware idle time caused by processing tasks with irregular computational patterns in parallel.

In this work, we present FLEX, an FPGA-CPU accelerator for mixed-cell-height legalization tasks. We address the above challenges from the following perspectives. First, we optimize the task assignment strategy and perform an efficient task partition between FPGA and CPU to exploit their complementary strengths. Second, a multi-granularity pipelining technique is employed to accelerate the most time-consuming step, finding optimal placement position (FOP), in legalization. At last, we particularly target the computationally intensive cell shifting process in FOP, optimizing the design to align it seamlessly with the multi-granularity pipelining framework for further speedup. Experimental results show that FLEX achieves up to 18.3× and 5.4× speedups compared to state-of-the-art CPU-GPU and multi-threaded CPU legalizers with better scalability, while improving legalization quality by 4% and 1%.

# **CCS Concepts**

• Hardware  $\rightarrow$  Physical design (EDA); Hardware accelerators.

# Keywords

Legalization, Electronic Design Automation, Hardware Acceleration, FPGAs

Wei Zhang wei.zhang@ust.hk The Hong Kong University of Science and Technology Kowloon, Hong Kong

#### **ACM Reference Format:**

Xingyu Liu, Jiawei Liang, Linfeng Du, Yipu Zhang, Chaofang Ma, Hanwei Fan, Jiang Xu, and Wei Zhang. 2025. FLEX: Leveraging FPGA-CPU Synergy for Mixed-Cell-Height Legalization Acceleration. In 54th International Conference on Parallel Processing (ICPP '25), September 08–11, 2025, San Diego, CA, USA. ACM, New York, NY, USA, 10 pages. https://doi.org/10.1145/3754598.

#### 1 INTRODUCTION

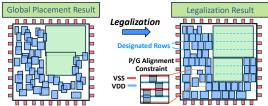

As electronic design automation (EDA) algorithms confront escalating demands from sub-10nm technology nodes [17] and billion-component designs, legalization [3, 9, 29] emerges as a critical yet computationally intensive step in VLSI physical design. This stage, as shown in Fig. 1, transforms globally placed circuits [33] into legally aligned layouts by resolving overlaps while maintaining placement quality—a prerequisite for successful routing. The proliferation of mixed-cell-height designs [10, 28, 34], where single-row and multi-row cells coexist to optimize performance and design flexibility, further complicates the problem: cell interactions propagate displacement across rows [4], while stringent design rules severely constrain solution spaces [5, 17, 18, 20]. To address these challenges, existing legalization strategies [4, 6–8, 11, 15, 17, 18, 20, 28, 31, 32, 34] primarily follow two paradigms: purely analytical and heuristic-analytical-mixed approaches.

**Figure 1: Example of layouts before and after legalization.** Purely analytical methods [4, 6, 7, 20] formulate legalization as common optimization problems such as quadratic programming,

1

Figure 2: Overview of the challenges and contributions.

which can be solved by existing solvers. While theoretically capable of achieving optimal solutions, these methods suffer from high runtime and poor scalability, limiting their practicality. To improve efficiency, these problems are simplified into smaller, faster-to-solve tasks, while compromising solution quality.

In contrast, heuristic-analytical-mixed methods achieve a balance between runtime and solution quality by employing heuristic algorithms for the broader problem and applying analytical methods to smaller sub-problems for refinement. Heuristic components, typically based on greedy strategies augmented by manually designed constraints, enable faster convergence to locally optimal solutions. Among these, the Multi-row Global Legalization (MGL) algorithm [18] resolves overlaps and meets technology constraints efficiently, leveraging analytical methods for fine optimization. While outperforming many purely analytical methods [18], its runtime remains a bottleneck for large-scale designs [30], as the computational intensity of finding optimal placement position for cells. Moreover, iterative nature of VLSI physical design may require thousands of legalization steps, significantly impacting overall efficiency.

Despite efforts to enhance legalization quality, accelerating this time-consuming step presents underexplored challenges. Existing parallelization methods exhibit poor scalability and diminishing returns: CPU-based multi-threading (processing several unlegalized cells concurrently [18]) saturates at 8 threads (Fig. 2(a)), while GPU implementations [30] suffer from two inherent problems. First, coarse-grained parallelism leads to high synchronization overhead (Fig. 2(b)), causing GPU methods to underperform even CPU baselines. Second, the number of parallelizable regions falls short of available CUDA cores (Fig. 2(c)), which means using a GPU with more cores is inefficient. These observations reveal a critical gap in current acceleration methods: neither conventional CPU multi-threading nor brute-force GPU parallelization effectively harness modern hardware for scalable legalization.

To further enhance acceleration and scalability, several persistent challenges must be addressed:

Challenge-1: Unbalanced task assignment on heterogeneous platforms limits speedup and degrades quality. For example, in [30], tough cells are assigned to CPU, leading to CPU's long runtime with minimal task completion on it (Fig. 2(d)). This also disrupts the processing order of regions, significantly affecting legalization quality. Additionally, assigning many non-overlapping regions to GPU for parallel processing results in a suboptimal processing order (Fig. 2(e)), further compromising the overall legalization quality.

Challenge-2: Finding optimal placement position (FOP), the bottleneck of MGL algorithm, exhibits irregular computational patterns [26], which conventional architectures struggle to handle efficiently. While multi-threaded CPU or GPU acceleration improves throughput, it leads to resource underutilization due to idle hardware during sequential operation execution (Fig. 2(f)). Similarly, normal FPGA pipelines incur inefficiencies, as operators must wait for predecessors to finish, causing idle time and delays from memory access when intermediate results are stored and retrieved.

**Challenge-3**: High-complexity cell shifting dominates over 60% of FOP runtime (Fig. 2(g)) due to two factors: 1) unpredictable number of full-region cell data traversals, and 2) hardware-agnostic algorithm design with unoptimized memory access patterns. Existing implementations [18, 30] lack architecture-aware optimizations, leaving parallelism potential unexploited.

To overcome these challenges, we propose FLEX, a heterogeneous accelerator for mixed-cell-height legalization based on a CPU-FPGA platform. Our contributions are summarized as follows:

To the best of our knowledge, FLEX is the first CPU-FPGAbased accelerator designed for mixed-cell-height legalization, featuring co-optimization of algorithm and architecture.

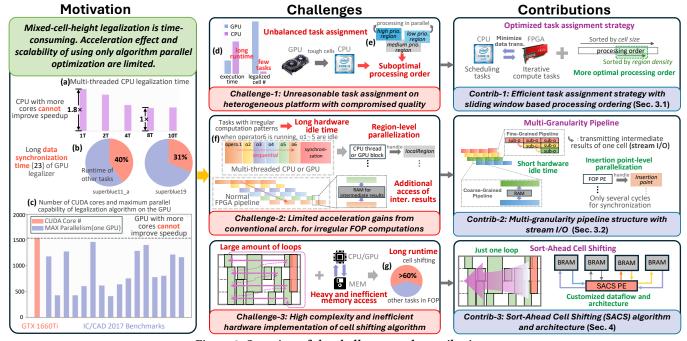

Figure 3: (a) Example of window and localCell. (b) Example of localRegion, localSegment, and subcell. (c) Example of displacement curves. (d) Example of the sum of displacement curves. (e) The legalization flow of using MGL algorithm [18].

- FLEX applies an efficient task assignment strategy to minimize bandwidth usage between CPU and FPGA, significantly reducing runtime. Moreover, a cell processing ordering method is developed to enhance legalization quality.

- The most time-intensive FOP stage is accelerated through a multi-granularity pipeline design, achieving higher hardware efficiency and faster performance.

- For the loop-intensive cell shifting inside FOP, we propose a Sort-Ahead Cell Shifting algorithm to lower computational complexity and implement a high-performance architecture.

FLEX achieves up to 18.3× and 5.4× speedups over SOTA CPU-GPU [30] and multi-threaded CPU [18] legalizers with better scalability, while improving solution quality by 4% and 1%.

#### 2 BACKGROUND

In this section, we provide an overview of mixed-cell-height legalization problem, introduce key terms of the MGL algorithm [17], and summarize the legalization flow.

# 2.1 Mixed-Cell-Height Legalization Problem

After global placement [33], the positions of n standard cells are determined, each with an initial bottom-left coordinate  $(x'_i, y'_i)$ , width  $w_i$ , and height  $h_i$ . The cell height is measured in units of standard row heights. Global placement ensures an optimal distribution of cells, so legalization must preserve this placement quality by minimizing the overall cell displacement [8].

The problem is formally defined as follows: given a set of m mixed-cell-height cells  $C = \{c_1, c_2, ..., c_m\}$ , each cell  $c_i$  must be moved from its initial global placement position  $(x_i', y_i')$  to a legalized position  $(x_i, y_i)$  such that the displacement is minimized. The displacement is defined by Manhattan distance as:

$$\delta_i = |x_i - x_i'| + |y_i - y_i'|, \tag{1}$$

and the placement quality is typically measured by the average displacement,  $S_{am}$  [10]:

$$S_{am} = \frac{1}{H} \sum_{h=1}^{H} \frac{1}{|C_h|} \sum_{c_i \in C_h} \delta_i,$$

(2)

where *H* is the largest cell height, and  $C_h \subseteq C$  represents the set of all cells with height *h*.

Legalization also requires cells to align with placement sites and avoid overlaps. Each cell is further constrained by the chip's power rail configuration, with boundaries defined as either Power or Ground (P/G). This imposes a P/G alignment constraint, as illustrated in Fig. 1. Vertical movement is costly due to alignment constraints [8], so the MGL algorithm restricts movement to the horizontal direction, simplifying the problem while maintaining placement quality.

# 2.2 Terminology of the MGL Algorithm

To facilitate analysis and improvement of MGL algorithm in subsequent sections, we briefly introduce its key terms and concepts.

#### 2.2.1 LocalSegment, LocalCell, and LocalRegion.

The legalization problem is localized within a rectangular window W, as shown in Fig. 3(a). For each row within W, the longest continuous sequence of unblocked placement sites is defined as a localSegment [8]. A cell is classified as a localCell if it is entirely contained within the localSegments of W. Together, all localSegments and localCells in W form the localRegion. The legalization of an unplaced target cell is simplified as a task to insert it into its localRegion and legalize all localCells. Additionally, a subcell represents a one-row-height unit of a multi-row-height localCell within a localSegment. The number of subcells in a localCell equals to its height in row units. For example, in Fig. 3(b), cell c spans three rows and thus contains three subcells.

#### 2.2.2 Insertion Interval and Insertion Point.

An insertion interval is the gap between two adjacent cells in a localSegment and an insertion point is a combination of insertion intervals across multiple rows. For example, the three intervals marked in Fig. 6(a) can be combined to get an insertion point for a three-row-height target cell.

#### 2.2.3 Displacement Curve and Breakpoint.

Even within a valid insertion point, the exact placement position of target cell can vary, resulting in different total displacements. *Displacement curves* and *breakpoints* are used to evaluate all possible placement positions within an insertion point. As shown in Fig. 3(c), a localCell's displacement curve is a piecewise linear function of target cell's placement position [8]. The turning points of these curves are referred to as breakpoints [17]. To identify the optimal placement position, all displacement curves are summed, as illustrated in Fig. 3(d). The x-coordinate with the minimum total displacement value is selected as the best.

#### 2.3 Legalization Algorithm Flow

Like existing legalization accelerators [17, 18, 30], FLEX is also based on the MGL algorithm. The legalization flow is outlined in Fig. 3(e) and consists of five steps.

Figure 4: Architecture overview of FLEX.

- a) input & pre-move: Load the global placement results and temporarily position cells in the nearest designated rows while tolerating initial overlaps.

- b) process ordering: Identify unlegalized target cells and determine the processing order.

- c) define localRegion: Identify localSegments and localCells in currently processing target cell's window, and compute the localRegion density.

- d) FOP: Employ triple-loop traversal to evaluate all candidate positions for minimal displacement.

- e) insert & update: Insert the target cell into the localRegion and update affected cells.

Steps b) to e) are repeated until achieving complete legalization with zero overlaps and design rule violations.

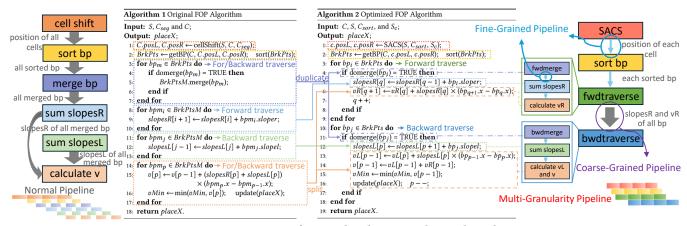

FOP process, the most computationally intensive step of MGL, involves three nested loops traversing all insertion points in a localRegion. Each localRegion may contain hundreds of insertion points, making operations inside the inner loop of FOP the primary bottleneck of MGL. As illustrated in Fig. 3(e), operations inside the loop of FOP aim to identify the position with the minimum total displacement by evaluating all candidate positions. Key components of FOP include:

- **cell shift**: Resolve overlaps caused by target cell insertion through left-move (for cells on the left of target cell) and right-move (for cells on the right of target cell) phases.

- sort bp: Gather and sort all breakpoints (bp) by their xcoordinates.

- merge bp: Traverse the sorted breakpoints, merging those with identical x-coordinates by accumulating their displacement curves' left-slopes and right-slopes.

- sum slopesR: Forward traverse the merged breakpoints to compute cumulative right-slopes for all breakpoints to the left of bp<sub>i</sub>, storing the results in slopesR[i].

- **sum slopesL**: Backward traverse the merged breakpoints to calculate cumulative left-slopes for breakpoints to the right of *bp<sub>j</sub>*, storing values in *slopesL*[*j*].

- calculate value: Traverse the merged breakpoints to compute *slopes* between each adjacent merged breakpoints by accumulating all displacement curves obtained by summing corresponding items in *slopesR* and *slopesL*. Then compute displacement value of each merged breakpoint based on *slopes*, ultimately determining the position with the minimum displacement. This step and previous four steps are actually used to compute the sum of all displacement curves, as shown in Fig. 3(c) and (d).

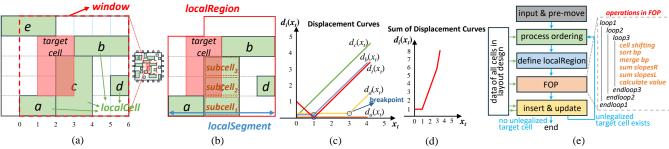

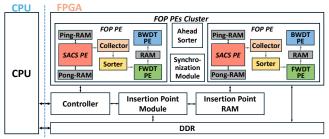

# 3 HARDWARE-DRIVEN LEGALIZATION FLOW

The architecture overview of FLEX is presented in Fig. 4. FLEX is specifically designed to accelerate the legalization flow depicted in Fig. 3(e), leveraging an FPGA-CPU platform. An controller manages the execution and data transfer across FPGA modules. The Insertion Point Module and RAM are utilized for computing and storing information pertaining to each insertion point. The FOP processing elements (PEs) cluster includes two FOP PEs, an Ahead Sorter, and a Synchronization Module. This section focuses on task assignment strategy and pipeline implementation within the FOP PE.

# 3.1 Task Assignment Strategy and Processing Ordering

#### 3.1.1 Task Assignment Between CPU and FPGA.

To address **Challenge-1**, we propose an efficient task assignment strategy that leverages the strengths of CPUs and FPGAs while minimizing bandwidth usage.

The first three steps in Fig. 3(e) are handled by the CPU with its flexibility and scheduling capabilities. Specifically: step a) is inherently serial [19] and benefits from CPU's high clock speed; step b) involves dynamically scheduling, making it well-suited for CPU's flexibility. Although step c) could theoretically be processed in parallel [30], we keep it on CPU for two reasons: (1) it accounts for only 3% of total runtime on CPU, making FPGA acceleration unnecessary and power-inefficient; (2) the localRegion density computed in step c) is a critical metric for processing ordering in step b). Keeping both on CPU minimizes data transmission overhead.

Step d), the FOP process, including iterative and irregular computations, is divided into sub-operations (for one cell, not all cells in a region) and offloaded to FPGA with customized design. On the one hand, a fine-grained pipeline is designed to ensure high hardware utilization, leveraging FPGA's pipelining and parallelism nature. On the other hand, FPGA's on chip RAM is flexibly configured to meet the need for fast and large-scale memory access.

Finally, step e), which involves a cell-shifting operation similar to step d), is kept on CPU despite its potential for FPGA acceleration. This is because step e) involves updating the positions of all moved cells, and assigning it to the FPGA would require transmitting all updated positions back to the CPU, introducing additional latency and interfering with steps b) and c). By keeping step e) on CPU, we eliminate unnecessary data transfer overhead, allowing the CPU to run at full capacity alongside the FPGA, reducing idle time for both. Effect of the assignment strategy is evaluated in Sec. 5.3.

# 3.1.2 Sliding Window Based Target Cell Processing Ordering.

The processing order of target cells significantly influences the quality of heuristic legalization methods [8, 17]. A widely adopted strategy prioritizes larger cells [30], as smaller cells are easier to place and less likely to disturb neighboring cells. However, existing methods overlook the impact of localRegion density: in high-density regions, placing a cell can cause greater displacement to nearby cells. Additionally, parallel processing of multiple non-overlapping regions [18, 30] may prematurely handle low-priority regions, deviating from the optimal processing order (Fig. 2(e)).

To address these limitations, we propose a method that considers both cell size and region density. Target cells are first sorted by

Figure 5: Comparison of original and optimized FOP algorithms.

size in descending order to generate an initial processing order sequence S. A sliding window  $W_s$  is then applied, moving sequentially through S. The first cell in  $W_s$ , denoted as  $C_{cur}$ , is always processed first. While  $C_{cur}$  is being processed, the next cell,  $C_{next}$ , is fixed, and other cells in  $W_s$  are dynamically reordered based on their localRegions' density in descending order, ensuring a density-first priority for the remaining cells in  $W_s$ . Once  $C_{cur}$  is processed,  $W_s$  slides forward, making  $C_{next}$  the new  $C_{cur}$ . To reduce runtime, if the localRegion of  $C_{next}$  does not overlap with that of  $C_{cur}$ , its data will be preloaded into the free Ping-Pong RAM.

# 3.2 Multi-granularity Pipeline for FOP

#### 3.2.1 Motivation and Insights.

Traditional FPGA pipelines used to accelerate FOP, shown as the Normal Pipeline in Fig. 2 (Challenge-2), suffer from inefficiencies. Each operation must wait for its predecessor to finish before starting, causing substantial idle time due to FOP's irregular computational patterns. Furthermore, intermediate results are stored in memory after each operation, incurring extra memory access delays when subsequent operators retrieve these results.

An ideal fine-grained pipeline would allow operators to output intermediate results as soon as sub-operations are done, enabling subsequent ones to begin execution without waiting for the completion of the entire predecessor operation. This requires a streaming input/output (stream I/O) model, where operators incrementally process input data and output results. However, the original FOP algorithms lack this capability. To address **Challenge-2**, we optimize FOP process for multi-granularity pipelining with two key improvements. First, we propose the Sort-Ahead Cell Shifting algorithm and architecture to handle the most complex cell-shifting operation, detailed in Sec. 4. Second, we restructure the last four operations in FOP to enhance pipelining efficiency.

#### 3.2.2 Operation Reorganization for Bidirectional Traversals.

Fig. 5 compares the original and optimized FOP workflows. In the original approach [19], each operation must wait for its predecessor to finish, requiring additional RAM for intermediate data storage. In contrast, the optimized workflow (Fig. 5 Algorithm 2) introduces stream I/O across most operations, except for the bidirectional traversals. Thin blue arrows indicate the immediate transfer of

intermediate results for individual cells or breakpoints between operations.

Enabling stream I/O requires not only optimized cell-shifting but also restructuring of the last four operations in the original FOP, which involve traversing breakpoints. Since *sum slopesR* and *sum slopesL* require bidirectional traversal of breakpoints, fine-grained pipelining between them is impractical because the output of one cannot be immediately utilized by the other.

To achieve speedup, we implement coarse-grained pipelining between the two bidirectional traversals and fine-grained pipelining within operations traversing in the same direction by splitting and reorganizing them. Specifically, the merging step is duplicated into forward-merge (fwdmerge) and backward-merge (bwdmerge), while calculate v is split into calculate vR, vL, and v. As shown in Fig. 5, the original four operations are reorganized into two streamlined operations: fwdtraverse and bwdtraverse, based on the traversal order. Within fwdtraverse, operations fwdmerge, sum slopesR, and calculate vR are executed sequentially in forward traverse order. Similarly, within bwdtraverse, operations bwdmerge, sum slopesL, calculate vL, and v are executed in backward traverse order. Stream I/O is enabled between internal operations within fwdtraverse and bwdtraverse, allowing for streaming input to fwdtraverse and streaming output from bwdtraverse without introducing additional loops. This combination of fine-grained and coarse-grained pipelining forms the multi-granularity pipeline structure.

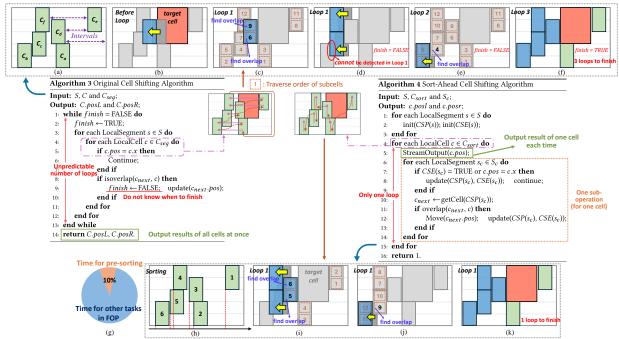

#### 4 SORT-AHEAD CELL SHIFTING

#### 4.1 Motivation

As illustrated in Fig. 2 **Challenge-3**, cell shifting is the most complex and time-consuming task within FOP, presenting significant problems for acceleration. Existing methods [19, 30] suffer from unpredictable multi-pass loops, making stream I/O and fine-grained pipelining infeasible. To address these issues, we propose the Sort-Ahead Cell Shifting (SACS) algorithm and its customized hardware architecture. SACS is integrated seamlessly into the multi-granularity pipelining framework for FOP, eliminating overlap resolution inefficiencies and enabling streaming outputs.

# 4.2 Sort-Ahead Cell Shifting Algorithm

Original cell shifting algorithm [18] (Fig. 6 Algorithm 3) employs a *finish* flag to indicate whether all overlaps are resolved in the

Figure 6: Comparison of the original cell shifting algorithm and the sort-ahead cell shifting algorithm.

current iteration. If overlaps persist, the loop continues iteratively until no cells are moved in the final pass. For example, in the leftmove phase shown in Fig. 6(a)-(f), overlaps are resolved iteratively by traversing subcells. The traversal order—bottom to top inter-row and right to left intra-row—can result in new overlaps remaining undetected in the same iteration (Fig. 6(d)). Consequently, multiple iterations (three in this example) are required to resolve all overlaps, with each loop traversing all subcells sequentially (1 to 12).

In contrast, our proposed SACS algorithm (Fig. 6 Algorithm 4) resolves overlaps in a single loop. Before shifting, all localCells are sorted by their x-coordinates (Fig. 6(h)). Cells are then processed sequentially: right to left for the left-move phase, and left to right for the right-move phase. Within each cell, subcells are processed from bottom to top. For instance, overlaps caused by subcell<sub>5</sub> and subcell<sub>6</sub> are resolved immediately by moving adjacent cells (Fig. 6(i)). Unlike the original algorithm, which leaves subsequent overlaps unresolved in the same pass, SACS detects and resolves all remaining overlaps during the current iteration (Fig. 6(i)-(j)). This allows the left-move process to complete in a single loop, compared to three loops required by the original algorithm.

In Fig. 6 Algorithm 4, S denotes the set of localSegments in a localRegion, and  $S_c$  represents the subset of localSegments containing a specific localCell c, used for identifying adjacent cells for overlap detection. The SACS algorithm pre-sorts localCells into  $C_{sort}$  by x-coordinates, ensuring predictable and sequential processing. This eliminates the need for multi-pass loops and ensures consistent overlap detection. Adjacent cells are identified using CurSegPtr (CSP) and CurSegEnd (CSE) structures: CSP tracks index of the next cell to process in each localSegment (row); CSE determines whether all cells in a localSegment have been processed.

Depending on left-move or right-move phase, CSP is initialized to the rightmost or leftmost cell in each localSegment. From line 4 to 15 in Algorithm 4, the outer loop iterates through all sorted cells in  $C_{sort}$ , while the inner loop processes their corresponding segments. Taking left-move as an example, since all cells to the right of the currently traversed cell c have already been processed, no other cells will affect its position. Thus, its pos can be directly output, as shown in line 5. Then it checks if all cells in each segment of  $S_c$  have been processed or if c has not yet moved. If no left-adjacent cell exists or no overlap occurs, CSP and CSE for segments of  $S_c$  are updated. If a left-adjacent cell exists in segment s and s has moved, resulting in an overlap in s, the next cell in s is processed to resolve it, followed by updating CSP and CSE. Unlike the original algorithm, SACS outputs each cell's final position during the loop, enabling fine-grained pipelining between cell shifting and sort bp.

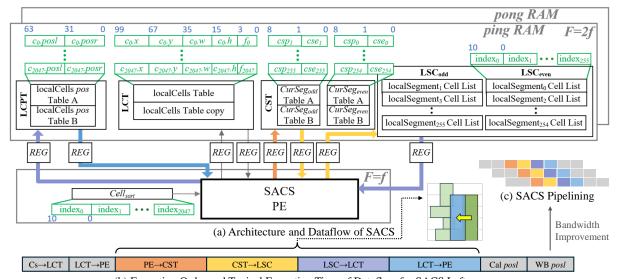

#### 4.3 Architecture for SACS Algorithm

# 4.3.1 Dataflow and Architecture.

The SACS algorithm requires extensive data to represent the spatial relationships, such as cell positions, heights, widths, and associations with localSegments. While software implementations use complex data structures, FPGA-based accelerators require optimized memory designs. To this end, we introduce two tables: localCells Table (LCT) stores fixed features and is updated only when processing a new localRegion; localCells pos Table (LCPT) stores the recently updated positions, modified during runtime. Additionally, Cellsort (Cs) and localSegment Cell Lists (LSC) store only cell indices to reduce memory usage, while the CurSeg Table (CST) manages CSP and CSE. All memory structures shown in Fig. 7(a) are implemented using FPGA BRAM for efficient execution.

Figure 7(b) illustrates the dataflow and execution order for the SACS left-move phase. The dataflow of each stage is as follows:

a. Cs→LCT: The next cell to be processed (*Rcell*), is fetched from Cs, and its index is used to read features from LCT.

(b) Execution Order and Typical Execution Time of Dataflow for SACS Left-move Figure 7: SACS architecture and pipeline for left-move phase.

- b. LCT→PE: Features of Rcell are loaded into the PE, which identifies the corresponding localSegments.

- c. PE→CST: PE queries CST to retrieve adjacent cells and check segment completion. Since Rcell may belong to multiple localSegments, due to multi-row-heights, multiple addresses are queried in CST. Thicker arrows in Fig. 7(a) represent data transfers for multiple cells. BRAM bandwidth limitations may increase latency during these queries ( Fig. 7(b)).

- d. CST→LSC: CSP retrieves the left-adjacent cell (*Lcell*) from LSC for each localSegment.

- e. LSC→LCT: Features of Lcells are fetched from LCT.

- f. LCT→PE: Features of all Lcells are loaded into PE.

- g. Cal posl: PE calculates new posl for Lcells to resolve overlaps.

- h. WB posl: Updated positions are written back to LCPT.

To reduce latency and hardware consumption, pre-sorting of localCells combines insertion [1] and merge sorters [2]. As shown in Fig. 6(g), sorting accounts for only 10% of the total FOP runtime, introducing acceptable overhead. Evaluation presented in Sec. 5.4 demonstrates that the sorter requires minimal hardware resources.

4.3.2 Bandwidth Improvement for Multi-row-height Cell Access.

BRAM bandwidth can become a bottleneck for designs with many multi-row-height cells. To mitigate this, we employ:

- Odd-Even RAM: Divides LSC and CST into odd and even rows to double bandwidth. For instance, assuming each BRAM has two read and two write ports, accessing four adjacent cells spanning odd and even rows now takes a single cycle instead of two.

- Ping-Pong Buffers: LCPT and CST are initialized in parallel using two alternating buffers (Tables A and B in Fig. 7(a)).

This hides initialization latency during region processing.

- Multiple Clock Domains: LCT, LCPT, CST, and LSC, which

require simultaneous access to multiple cells, are placed in a

clock domain running at twice the frequency of the SACS PE.

Additional split registers synchronize read addresses from

the low-frequency domain to high-frequency domain and merge registers store data read from the latter.

Additionally, LCT bandwidth is doubled by duplicating its memory, as its data is not row-dependent. Combined, these optimizations significantly reduce the latency of accessing multi-row-height cells, with minimal BRAM usage overhead. This enables highly efficient pipelining of the SACS algorithm, as illustrated in Fig. 7(c), fully leveraging the parallelism inherent inside cell shifting operations.

Although the SACS algorithm can also be implemented on CPUs, the actual performance gains are limited. The memory access pattern remains irregular, and additional indexing structures like CSP and CSE incur software overhead. In contrast, our FPGA implementation customizes the on-chip RAM and memory dataflow to match the algorithm, enabling highly efficient pipelining and parallelism. Furthermore, FPGA-based sorting [1, 2] is significantly faster and more scalable than CPU-based sorting, especially for sorting large amounts of data. Thus, SACS achieves far higher efficiency when deployed on FPGA.

#### **5 EXPERIMENTAL RESULTS**

#### 5.1 Configuration and Dataset

FLEX is implemented on a system with an Intel Core i5 CPU, 32 GB RAM, and an AMD Alveo U50 FPGA running at 285 MHz. Comparisons are made against the CPU-GPU legalizer [30] (Intel Core i5 CPU, NVIDIA GeForce GTX 1660 Ti GPU), the multi-threaded CPU legalizer [18] (Intel Xeon CPU, 8 cores, 64 GB RAM), and the purely analytical GPU-accelerated legalizer [25] (NVIDIA A800 GPU). All experiments use the IC/CAD 2017 contest benchmarks [10], with baseline results taken directly from the respective papers.

#### 5.2 Overall Performance

The performance of FLEX is evaluated against two MGL-based heuristic legalizers and one pure analytical legalizer: the CPU-GPU-based legalizer [30], the multi-threaded CPU legalizer [18] and GPU-accelerated LEGALM [25]. Table 1 provides a detailed comparison of results and the meaning of each column is:

| Benchmarks      | Cell # | Den. (%) | TCAD'22-MGL |         | DATE'22 |         | ISPD'25 |         | Ours   |         |        |        |        |

|-----------------|--------|----------|-------------|---------|---------|---------|---------|---------|--------|---------|--------|--------|--------|

|                 |        |          | AveDis      | Time(s) | AveDis  | Time(s) | AveDis  | Time(s) | AveDis | Time(s) | Acc(T) | Acc(D) | Acc(I) |

| des_perf_1      | 112644 | 90.6     | 0.967       | 4.74    | 1.05    | 3.47    | 0.66    | 7.51    | 0.665  | 1.322   | 3.6×   | 2.6×   | 5.7×   |

| des_perf_a_md1  | 108288 | 55.1     | 0.919       | 1.81    | 0.92    | 2.00    | 1.20    | 8.38    | 0.904  | 0.727   | 2.5×   | 2.8×   | 11.5×  |

| des_perf_a_md2  | 108288 | 55.9     | 1.148       | 1.67    | 1.32    | 2.00    | 1.12    | 16.64   | 1.144  | 0.663   | 2.5×   | 3.0×   | 25.1×  |

| des_perf_b_md1  | 112644 | 55.0     | 0.675       | 1.28    | 0.70    | 6.85    | 0.65    | 20.34   | 0.635  | 0.375   | 3.4×   | 18.3×  | 54.2×  |

| des_perf_b_md2  | 112644 | 64.7     | 0.618       | 1.31    | 0.72    | 1.75    | 0.70    | 1.11    | 0.653  | 0.501   | 2.6×   | 3.5×   | 2.2×   |

| edit_dist_1_md1 | 130661 | 67.4     | 0.664       | 0.98    | 0.67    | 1.67    | 0.63    | 2.68    | 0.646  | 0.347   | 2.8×   | 4.8×   | 7.7×   |

| edit_dist_a_md2 | 127413 | 59.4     | 0.614       | 1.30    | 0.73    | 1.80    | 0.67    | 2.22    | 0.650  | 0.547   | 2.4×   | 3.3×   | 4.1×   |

| edit_dist_a_md3 | 127413 | 57.2     | 0.783       | 1.78    | 0.91    | 3.92    | 0.79    | 19.21   | 0.771  | 0.897   | 2.0×   | 4.4×   | 21.4×  |

| fft_2_md2       | 32281  | 82.7     | 0.721       | 0.29    | 0.68    | 0.45    | 0.68    | 1.74    | 0.694  | 0.112   | 2.6×   | 4.0×   | 15.5×  |

| fft_a_md2       | 30625  | 32.3     | 0.563       | 0.22    | 0.65    | 0.32    | 0.75    | 0.51    | 0.604  | 0.041   | 5.4×   | 7.8×   | 12.4×  |

| fft_a_md3       | 30625  | 31.2     | 0.531       | 0.15    | 0.56    | 0.34    | 0.59    | 0.39    | 0.567  | 0.036   | 4.2×   | 9.4×   | 10.8×  |

| pci_b_a_md1     | 29517  | 49.5     | 0.652       | 0.33    | 0.63    | 0.58    | 0.92    | 0.70    | 0.699  | 0.106   | 3.1×   | 5.5×   | 6.6×   |

| pci_b_a_md2     | 29517  | 57.7     | 0.839       | 0.47    | 0.91    | 0.62    | 0.85    | 2.12    | 0.838  | 0.130   | 3.6×   | 4.8×   | 16.3×  |

| pci_b_b_md1     | 28914  | 26.6     | 0.781       | 0.31    | 0.48    | 0.62    | 1.14    | 0.88    | 0.821  | 0.085   | 3.6×   | 7.3×   | 10.4×  |

| pci_b_b_md2     | 28914  | 18.3     | 0.704       | 0.32    | 0.63    | 0.45    | 1.01    | 1.69    | 0.746  | 0.072   | 4.4×   | 6.3×   | 23.5×  |

| pci_b_b_md3     | 28914  | 22.2     | 0.925       | 0.34    | 0.87    | 0.45    | 1.09    | 1.92    | 0.945  | 0.082   | 4.1×   | 5.5×   | 23.4×  |

| Average         |        |          | 0.757       | 1.08    | 0.78    | 1.71    | 0.84    | 5.50    | 0.749  | 0.378   | 2.9×   | 4.5×   | 14.7×  |

| Ratio           |        | 1.01     | 2.86        | 1.04    | 4.52    | 1.12    | 14.67   | 1.00    | 1.00   | -       | -      | -      |        |

Table 1: Result comparison with state-of-the-art legalizer on IC/CAD 2017 contest benchmarks

- Benchmarks: IC/CAD 2017 contest test cases.

- Cell #: Number of cells to be legalized.

- Den.(%): Design density, calculated as total cell area divided by available free area.

- TCAD'22-MGL, DATE'22, ISPD'25: Results from [18] for MGL algorithm only, results from [30], and results from [25].

- AveDis: Average displacement of legalized cells, computed using Equation (2).

- Time(s): Runtime for the legalization task.

- Acc(T), Acc(D) and Acc(I): Speedup of this work compared to CPU legalizer [18], CPU-GPU legalizer [30] and GPU-based analytical legalizer [25].

From Table 1, FLEX achieves  $2.6\times-18.3\times$  speedup over the CPU-GPU legalizer and  $2\times-5.4\times$  over the multi-threaded CPU legalizer. Additionally, FLEX enhances solution quality, particularly in high-density cases like "des\_perf\_1," where FLEX achieves lower average displacement than the heuristic baselines. While the purely analytical legalizer from ISPD'25 is not our primary baseline, FLEX outperforms it in both runtime and legalization quality, demonstrating the superiority of the heuristic-analytical-mixed approach.

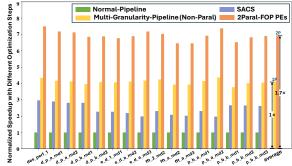

#### 5.3 Breakdown Analysis

To understand the contributions of each optimization, we perform a breakdown analysis of FLEX's acceleration mechanisms.

**FOP Optimization.** FLEX's FPGA-based FOP acceleration consists of three main components: cell shifting optimization (Sec. 4), multi-granularity pipelining (Sec. 3.2), and parallelization of FOP PE (shown in Fig. 4). Fig. 8 shows the normalized speedup by these optimizations: cell shifting optimization (SACS) achieves  $2\times-3\times$ , multi-granularity pipelining gains an additional speedup of  $1\times-2\times$ , and 2-parallelism FOP PE results in a further speedup of  $1.6\times-1.9\times$ .

**SACS Optimization.** SACS optimizations include architecture improvements, bandwidth optimization, and parallelization of left and right moves. Fig. 9 illustrates the normalized speedup achieved

Figure 8: Speedup with different optimization steps on FPGA.

through various optimizations. The gray line in Fig. 9 indicates the proportion of cells taller than three rows, which plays a critical role in determining the effectiveness of bandwidth optimization. Specifically, the speedup between "SACS-Ar" and "SACS-ImpBW" correlates with this ratio. A higher proportion of tall cells increases the likelihood of simultaneous access to multiple adjacent cells, thereby amplifying the benefits of bandwidth improvements. In benchmarks without cells taller than three rows (e.g., the 1st, 2nd, and 4th benchmarks), "SACS-ImpBW" demonstrates no additional speedup over "SACS-Ar." However, in the "pci\_b\_a\_md2" benchmark, the high proportion of such tall cells results in a significant acceleration due to the bandwidth optimization.

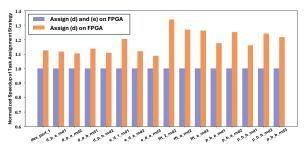

Task Assignment Optimization. To evaluate our task assignment strategy between CPU and FPGA, we compare different allocation schemes. As discussed in Sec. 3.1.1, steps a), b) and c) are performed on the CPU due to algorithmic constraints. Thus, the comparison focuses on step d) being executed solely on FPGA versus both d) and e) being offloaded to FPGA. Fig. 10 shows that our method, which keeps step e) on the CPU, achieves an average speedup of 1.2× compared to offloading both steps to FPGA.

A large part of the speedup brought by task assignment optimization comes from the reduction of communication overhead

Figure 9: Speedup with different optimization steps of SACS and percentage of cells taller than three-row height.

Table 2: Hardware resource consumption on FPGA

|                          | LUTs   | FFs     | BRAMs | DSPs |

|--------------------------|--------|---------|-------|------|

| No parallelism of FOP PE | 59837  | 67326   | 391   | 8    |

| 2 parallelism of FOP PE  | 86632  | 91603   | 738   | 12   |

| Available                | 871680 | 1743360 | 1344  | 5952 |

between CPU and FPGA, as mentioned in Sec. 3.1.1. In addition, our hardware design further reduces the impact of communication by enabling overlap between data transfer and computation. The employed Ping-Pong RAM structure (Fig. 4) and deeply pipelined architecture (Fig. 5) allow the FPGA to process one region while simultaneously loading data for the next. The processing ordering strategy also ensures that the required data for the next region  $(C_{next})$  is preloaded in advance. In fact, the visible communication cost approximately equals to the initial data transfer time of the first processed region, which is negligible in the overall runtime.

# 5.4 Resource Utilization and Scalability

Table 2 details FPGA resource utilization. Two parallel FOP PEs can process two insertion points within the same localRegion simultaneously. Additionally, the sorter for each localRegion is not duplicated, resulting in a less than two times increase in *LUT* and *FF* usage when enabling two parallelism of PEs. Speedup can be further improved by increasing the number of FOP PEs while BRAM may become a resource bound, but this can be addressed by using URAM with a slight FPGA clock frequency penalty.

Regarding scalability, multi-threaded CPU legalizers exhibit performance saturation at 8 threads due to the limitations of thread-level parallelism (Fig. 2(a)). Similarly, while the scalability of the CPU-GPU legalizer is not explicitly analyzed in [30], the experimental results in Fig. 2(b) and (c) indicate that its performance is constrained by significant data synchronization overhead. These methods rely on processing multiple localRegions in parallel, which necessitates extensive synchronization to update the positions of all moved cells, thereby limiting their scalability.

By contrast, FLEX takes a different approach to scalability by avoiding region-level parallelism, which inherently reduces synchronization costs. For example, in the 2-parallelism FOP PE configuration, FLEX computes the displacements of two insertion points for the same target cell concurrently. Afterward, a simple synchronization operation is performed to compare the displacement results and select the smaller one, taking several clock cycles. This low-level parallelism minimizes synchronization overhead, allowing FLEX to scale more effectively.

Figure 10: Speedup of proposed task assignment method.

Fig. 8 demonstrates that 2-parallelism FOP PEs on FPGA achieves an average 1.7× speedup compared to the non-parallel setup, approaching near-linear scalability. As on-chip memory and FPGA resource capacities grow, FLEX can achieve even higher levels of parallelism, further enhancing its performance for large-scale tasks. In contrast, the multi-threaded CPU legalizer shows diminishing returns as the number of threads increases. Specifically, 2-threaded CPU runtime is reduced by only 20% compared to a single-threaded implementation (Fig. 2(a)). With 8 threads, the speedup saturates, achieving only a 1.8× acceleration, falling short of ideal scalability.

#### 6 RELATED WORKS

**Legalization Algorithms:** Abacus [27] is one of the most widely used algorithms for traditional single-cell-height standard cell legalization and has been integrated into several SOTA placers [13, 21, 24]. It employs dynamic programming to achieve optimal solutions with minimal displacement for cells within a row. However, it is not well-suited for mixed-cell-height legalization tasks, as moving multi-row-height cells can introduce overlaps in adjacent rows. To address mixed-cell-height legalization, several works [6, 7, 20] formulate the problem as a quadratic programming (QP) task, which is subsequently reformulated into a linear complementarity problem (LCP). However, to ensure convergence and equivalence between the QP and LCP formulations, additional operations are required [20]. Furthermore, these methods often leave some cells in illegal states for specific benchmarks, which can degrade the overall solution quality. Chen et al.[4, 16] treats the legalization problem as a resource allocation task, employing a negotiation-based approach to achieve excellent displacement results. However, this method still suffers from pin shorts/access violations and edge spacing violations in several benchmarks[18]. Chow et al.[8] proposes a multi-row local legalization (MLL) algorithm for mixed-cell-height legalization. After cells are pre-aligned to their nearest row and power rail positions, MLL evaluates all possible insertion points and selects the best position for each target cell. Building on this, Li et al.[17, 18] introduces a multi-row global legalization (MGL) method to handle fence region and routability constraints. Unlike MLL, MGL accumulates the displacement between the global placement positions and final target positions, enabling identification of better insertion points for unlegalized cells.

Accelerators for VLSI Legalization: Most EDA algorithm accelerators [12, 14, 22, 23] leverage GPUs for parallelism. For legalization, a CPU-GPU-based legalization accelerator [30] utilizes GPU parallelization to optimize tasks by exploiting different levels of concurrency. It processes non-overlapping regions and handling different rows to refine search windows in parallel. However, due to

the lack of efficient queue data structure support on GPUs, a bruteforce approach is used. This method employs multiple threads to evaluate single-row intervals and their validity in parallel, while simultaneously computing legalization costs and determining optimal insertion points. Although this approach achieves high parallelism, it incurs significant data synchronization overhead. Furthermore, the scheduler of it assigns tough cells to CPU, leaving GPU to handle only simpler tasks, which results in CPU spending significant time on those challenging cases.

#### 7 CONCLUSION

We propose FLEX, an FPGA-CPU accelerator for mixed-cell-height legalization in VLSI physical design. Through efficient task assignment and architecture-algorithm co-optimization, FLEX achieves up to 18.3× and 5.4× speedups over SOTA GPU and CPU legalizers, while improving quality by 4% and 1% respectively. Our work demonstrates FPGAs' effectiveness for accelerating tasks with irregular computational patterns, suggesting potential for broader application across VLSI physical design as FPGA-based data centers become more prevalent.

# Acknowledgments

We would like to thank Dr. Haocheng Li and Prof. Evangeline F.Y. Young from the Chinese University of Hong Kong. This work was partially supported by the RGC GRF grant 16214123.

#### References

- AMD. 2023. Vitis Database Library User Guide Insert Sort. https://docs.amd.com/ r/2023.2-English/Vitis\_Libraries/database/guide/sort/insert\_sort.html

- [2] AMD. 2023. Vitis Database Library User Guide Merge Sort. https://docs.amd.com/ r/2023.2-English/Vitis\_Libraries/database/guide/sort/merge\_sort.html

- [3] U. Brenner and J. Vygen. 2004. Legalizing a placement with minimum total movement. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 23 (2004).

- [4] Jinwei Chen, Zhixiong Di, Jiangyi Shi, Quanyuan Feng, and Qiang Wu. 2022. NBLG: A Robust Legalizer for Mixed-Cell-Height Modern Design. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 41, 11 (2022).

- [5] Jianli Chen, Ziran Zhu, Longkun Guo, Yu-Wei Tseng, and Yao-Wen Chang. 2022. Mixed-Cell-Height Placement With Drain-to-Drain Abutment and Region Constraints. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 41, 4 (2022).

- [6] Jianli Chen, Ziran Zhu, Wenxing Zhu, and Yao-Wen Chang. 2017. Toward Optimal Legalization for Mixed-Cell-Height Circuit Designs. In 2017 54th ACM/EDAC/IEEE Design Automation Conference (DAC).

- [7] Jianli Chen, Ziran Zhu, Wenxing Zhu, and Chang Yao-Wen. 2020. A Robust Modulus-Based Matrix Splitting Iteration Method for Mixed-Cell-Height Circuit Legalization. ACM Trans. Des. Autom. Electron. Syst. 26, 2 (2020).

- [8] Wing-Kai Chow, Chak-Wa Pui, and Evangeline F. Y. Young. 2016. Legalization Algorithm for Multiple-Row Height Standard Cell Design. In 2016 53nd ACM/EDAC/IEEE Design Automation Conference (DAC).

- [9] Jason Cong and Min Xie. 2008. A Robust Mixed-Size Legalization and Detailed Placement Algorithm. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 27 (2008).

- [10] Nima Karimpour Darav, Ismail S. Bustany, Andrew Kennings, and Ravi Mamidi. 2017. ICCAD-2017 CAD Contest in Multi-Deck Standard Cell Legalization and Benchmarks. In 2017 IEEE/ACM International Conference on Computer-Aided Design (ICCAD).

- [11] SangGi Do, Mingyu Woo, and Seokhyeong Kang. 2019. Fence-Region-Aware Mixed-Height Standard Cell Legalization. In Proceedings of the 2019 Great Lakes Symposium on VLSI (GLSVLSI '19).

- [12] Guofeng Feng, Hongyu Wang, Zhuoqiang Guo, Mingzhen Li, Tong Zhao, Zhou Jin, Weile Jia, Guangming Tan, and Ninghui Sun. 2024. Accelerating Large-Scale Sparse LU Factorization for RF Circuit Simulation. In Euro-Par 2024: Parallel Processing.

- [13] Jiaqi Gu, Zixuan Jiang, Yibo Lin, and David Z. Pan. 2020. DREAMPlace 3.0: Multi-Electrostatics Based Robust VLSI Placement with Region Constraints. In 2020 IEEE/ACM International Conference On Computer Aided Design (ICCAD).

- [14] Zizheng Guo, Jing Mai, and Yibo Lin. 2021. Ultrafast CPU/GPU Kernels for Density Accumulation in Placement. In 2021 58th ACM/IEEE Design Automation Conference (DAC).

- [15] Chung-Yao Hung, Peng-Yi Chou, and Wai-Kei Mak. 2017. Mixed-Cell-Height Standard Cell Placement Legalization. In Proceedings of the Great Lakes Symposium on VLSI 2017 (GLSVLSI '17).

- [16] Chen Jinwei and Mai Jing. 2022. Open-NBLG. https://github.com/recurme/Mixed-Cell-Height legalizer

- [17] Haocheng Li, Wing-Kai Chow, Gengjie Chen, Evangeline F. Y. Young, and Bei Yu. 2018. Routability-Driven and Fence-Aware Legalization for Mixed-Cell-Height Circuits. In 2018 55th ACM/ESDA/IEEE Design Automation Conference (DAC).

- [18] Haocheng Li, Wing-Kai Chow, Gengjie Chen, Bei Yu, and Evangeline F.Y. Young. 2022. Pin-Accessible Legalization for Mixed-Cell-Height Circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 41, 1 (2022).

- [19] Haocheng Li, Lixin Liu, and Chak-Wa Pui. 2022. Ripple. https://github.com/cuhk-eda/ripple

- [20] Xingquan Li, Jianli Chen, Wenxing Zhu, and Yao-Wen Chang. 2019. Analytical Mixed-Cell-Height Legalization Considering Average and Maximum Movement Minimization. In Proceedings of the 2019 International Symposium on Physical Design (ISPD '19).

- [21] Peiyu Liao, Siting Liu, Zhitang Chen, Wenlong Lv, Yibo Lin, and Bei Yu. 2022. DREAMPlace 4.0: Timing-driven Global Placement with Momentum-based Net Weighting. In 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE).

- [22] Dian-Lun Lin, Umit Ogras, Joshua San Miguel, and Tsung-Wei Huang. 2024. TaroRTL: Accelerating RTL Simulation Using Coroutine-Based Heterogeneous Task Graph Scheduling. In Euro-Par 2024: Parallel Processing.

- [23] Dian-Lun Lin, Haoxing Ren, Yanqing Zhang, Brucek Khailany, and Tsung-Wei Huang. 2023. From RTL to CUDA: A GPU Acceleration Flow for RTL Simulation with Batch Stimulus. In Proceedings of the 51st International Conference on Parallel Processing (ICPP).

- [24] Yibo Lin, Zixuan Jiang, Jiaqi Gu, Wuxi Li, Shounak Dhar, Haoxing Ren, Brucek Khailany, and David Z. Pan. 2021. DREAMPlace: Deep Learning Toolkit-Enabled GPU Acceleration for Modern VLSI Placement. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 40, 4 (2021).

- [25] Jing Mai, Chunyuan Zhao, Zuodong Zhang, Zhixiong Di, Yibo Lin, and Runsheng Wang. 2025. LEGALM: Efficient Legalization for Mixed-Cell-Height Circuits with Linearized Augmented Lagrangian Method. In Proceedings of the 2025 International Symposium on Physical Design. (ISPD).

- [26] Quan M. Nguyen and Daniel Sanchez. 2023. Phloem: Automatic Acceleration of Irregular Applications with Fine-Grain Pipeline Parallelism. In 2023 IEEE International Symposium on High-Performance Computer Architecture (HPCA).

- [27] Peter Spindler, Ulf Schlichtmann, and Frank M. Johannes. 2008. Abacus: Fast Legalization of Standard Cell Circuits with Minimal Movement. In Proceedings of the 2008 International Symposium on Physical Design (ISPD '08).

- [28] Chao-Hung Wang, Yen-Yi Wu, Jianli Chen, Yao-Wen Chang, Sy-Yen Kuo, Wenxing Zhu, and Genghua Fan. 2017. An Effective Legalization Algorithm for Mixed-Cell-Height Standard Cells. In 2017 22nd Asia and South Pacific Design Automation Conference (ASP-DAC).

- [29] Zheng Xiao, Weijie Chen, Yunchuan Qin, Fan Wu, Anthony Theodore Chronopoulos, Alex Nicolau, and Kenli Li. 2024. NGLIC: A Nonaligned-Row Legalization Approach for 3-D Interdie Connection. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 43 (2024).

- [30] Haoyu Yang, Kit Fung, Yuxuan Zhao, Yibo Lin, and Bei Yu. 2022. Mixed-Cell-Height Legalization on CPU-GPU Heterogeneous Systems. In 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE).

- [31] Chen-Can Zhou, Yang Cao, Quan Shi, and Lu-Xin Wang. 2023. A Robust Newtontype Iteration Method for Mixed-Cell-Height Legalization. In 2023 International Symposium of Electronics Design Automation (ISEDA).

- [32] Chen-Can Zhou, Jie Qiu, Yang Cao, Geng-Chen Yang, Qin-Qin Shen, and Quan Shi. 2023. An Accelerated Modulus-Based Matrix Splitting Iteration Method for Mixed-Size Cell Circuits Legalization. *Integration* 88 (2023).

- [33] Wenxing Zhu, Jianli Chen, Zheng Peng, and Genghua Fan. 2015. Nonsmooth Optimization Method for VLSI Global Placement. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 34 (2015).

- [34] Ziran Zhu, Jianli Chen, Wenxing Zhu, and Yao-Wen Chang. 2020. Mixed-Cell-Height Legalization Considering Technology and Region Constraints. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 39, 12 (2020).