# tritonBLAS: Triton-based Analytical Approach for GEMM Kernel Parameter Selection

Ryan Swann, Muhammad Osama, Xiaohu Guo, Bryant Nelson, Lixun Zhang, Alex Brown, Yen Ong, Ali Yazdani, Sean Siddens, Ganesh Dasika, Alex Underwood Advanced Micro Devices, Inc.

Abstract—We present tritonBLAS, a fast and deterministic analytical model that uses architectural parameters like the cache hierarchy, and relative code and data placement to generate performant GPU GEMM kernels. tritonBLAS explicitly models the relationship between architectural topology, matrix shapes, and algorithmic blocking behavior to predict near-optimal configurations without runtime autotuning. Based on this model, we developed and implemented a lightweight GEMM framework entirely within Triton.

We evaluate the performance of *tritonBLAS* across a diverse set of GEMM problem sizes on modern GPUs. *tritonBLAS* achieves over 95% of the performance of autotuning solutions, while reducing autotuning time to *zero*. This makes *tritonBLAS* a practical drop-in replacement for empirical tuning in production HPC and ML workloads.

Index Terms—Analytical Tiling, General Matrix Multiplication, GPU, ROCm, Triton

### I. Introduction

General matrix multiplication (GEMM) drives performance in AI, ML, and HPC workloads [1], [2]. Large language models (LLMs) like GPT-4 depend on transformer networks that execute thousands to millions of GEMM operations per pass [3]. GPUs, equipped with specialized matrix cores, dominate GEMM acceleration. Despite the algorithm's apparent simplicity, developing efficient GEMM kernels and libraries for GPUs remains a difficult task. Writing a fast GEMM kernel requires carefully capturing the GPU's compute and memory hierarchies, orchestrating data movement across registers, shared memory, and caches, and ensuring that matrix cores are continuously supplied with data to avoid stalls.

Implementing a fast kernel is only one piece of the problem. Building a complete library requires not only a collection of optimized kernels but also the ability to select or Just-in-Time (JIT)<sup>1</sup> compile the right kernel configuration for the user's problem at runtime. Such configuration decisions include the choice of tile sizes, unroll depths, loop scheduling strategies, and data reordering to improve L2 cache hit rates. The effectiveness of the library therefore depends as much

on kernel selection and orchestration as it does on the raw efficiency of individual kernels.

Triton [4] has emerged as a productive programming model for writing high-performance GPU kernels. It simplifies much of the complexity of GPU programming such as thread synchronization, vectorization, and memory coalescing, while still exposing the necessary control for performance tuning. Triton therefore makes writing GEMM kernels significantly easier. However, Triton and similar frameworks still depend on autotuning to select kernel parameters. These search-based techniques require extensive compilation and benchmarking, consume large amounts of time and resources, and limit portability of tuned configurations across different hardware generations (see Section II-B).

We present *tritonBLAS*, a first-class GEMM library built on top of Triton that eliminates reliance on autotuning. Instead of empirical search, *tritonBLAS* uses an analytical performance model that captures the interaction between GPU architecture and algorithmic blocking choices. This model allows us to predict near-optimal configurations deterministically and to generate specialized kernels through JIT compilation without running a tuning phase. By combining Triton's programmability with a principled analytical model, we provide a practical alternative to autotuning for production HPC and ML workloads.

The contributions of this paper are as follows:

- A deterministic, zero-autotuning selector for Triton GEMM. Using this model, we implement *tritonBLAS*, a Triton-based GEMM library that replaces empirical autotuning architecture-parameterized configuration selection.

- Architecture portability with lightweight calibration.

The model is parameterized only by measurable hardware rates (bandwidths, instruction latencies, and matrix-core shapes), enabling retargeting to new GPU generations via microbenchmark-based calibration.

- Extensive evaluation demonstrating near-autotuned performance. Across 150,000 GEMM shapes and realworld LLM workloads, tritonBLAS achieves 94.7% of exhaustive autotuning performance while eliminating tuning overhead and matching or exceeding vendor libraries in memory-bound regimes.

<sup>&</sup>lt;sup>1</sup>Just-in-Time (JIT) compilation refers to the strategy of generating and compiling specialized machine code at runtime, based on problem parameters provided by the user. This allows the library to tailor kernel implementations to the specific matrix shapes and hardware characteristics without relying on precompiled variants.

# II. BACKGROUND AND RELATED WORK

# A. General Matrix Multiplication (GEMM)

General matrix multiplication (GEMM) is defined as C = $\alpha AB + \beta C$  where C is the output matrix of size  $M \times N$ , A and B are input matrices of size  $M \times K$  and  $K \times N$ respectively, and  $\alpha$  and  $\beta$  are scalar values. Efficient GEMM implementations on GPUs take advantage of a GPU's memory and compute hierarchy through hierarchical tiling structures in attempts to maximize the balance of maximum locality and utilization of available parallelism [5], [6]. GEMM tiles are scheduled using an "output stationary" dataflow with the reduction dimension, K, accumulated into an output buffer over time, and output tiles parallelized across processing elements (see Algorithm 1 and 2). GEMM's output tile dimensions influence both parallelism and data locality, and are impacted by the architectural characteristics such as memory hierarchy bandwidth and capacity, as well as the shape and throughput of the compute resources. This implies that any problem size and shape (M, N, K) of a GEMM may require a different tile size to reach peak performance on a specific architecture.

# **Algorithm 1** Compute matrix $C = A \times B$

```

Require: A \in \mathbb{R}^{m \times k}, B \in \mathbb{R}^{k \times n}

Ensure: C \in \mathbb{R}^{m \times n}

1: for i = 1, ..., m do

for j = 1, \ldots, n do

2:

C[i,j] \leftarrow 0

3:

for \ell = 1, \ldots, k do

4:

C[i,j] \leftarrow C[i,j] + A[i,\ell] \times B[\ell,j]

5:

end for

6:

end for

7:

8: end for

```

One such example of how the output tile size impacts parallelism is the case where the matrix sizes are M=256, N=256 and K=8192. A tile size of  $(M_T\times N_T\times K_T)=(16\times 16\times 256)$  results in 256 output tiles  $(\frac{M}{M_T}\times \frac{N}{N_T}=\frac{256}{16}\times \frac{256}{16})$ , which are parallelized over a GPU with 256 compute units (CUs), in a typical case each CU is responsible for producing one tile of the output matrix [6]. Consider if we had chosen a tile size of  $(M_T\times N_T\times K_T)=(256\times 256\times 128)$ , results in a single output tile  $(\frac{M}{M_T}\times \frac{N}{N_T}=\frac{256}{256}\times \frac{256}{256})$ . The entire problem would run on a single CU resulting in underutilization of compute resources.

Separately optimizing for locality results in entries of a tile being reused for  $(M_T \times N_T \times K_T)$  MAC operations. For example, a  $16 \times 16 \times 256$  tile size is reused a total 65,536 times whereas elements in a tile of  $256 \times 256 \times 128$  are reused 8,388,608 times. This is because tiling parameters change the amount of data loaded at a time into the lower levels of the memory hierarchy, i.e. one load to the lower level of caches can be reused for multiple matrix multiply operations. Tiling configurations are also recursive; most GPUs having some hardware predefined "Matrix Instructions" for a given data

# Algorithm 2 Tiled Matrix Multiply Schedule

```

Require: M, N, K dimensions of the problem;

M_T, N_T, K_T tile sizes in space and time

Ensure: Partial results accumulated in C

1: function SCHEDULETILE(i, j, \ell) \triangleright Compute one tile at

CU indices (i, j, \ell)

for m \leftarrow 1 to M_T do

for n \leftarrow 1 to N_T do \triangleright Across waves in a Block

3:

4:

for k \leftarrow 1 to K_T do \triangleright Across time in a wave

5:

C[i][j][m][n] +=

A[i][\ell][m][k] \times B[j][\ell][n][k]

[2]

end for

6:

end for

7:

8:

end for

9: end function

10: for i \leftarrow 1 to \lceil M/M_T \rceil do

\triangleright Over CUs (space) in M

for j \leftarrow 1 to \lceil N/N_T \rceil do \triangleright Over CUs (space) in N

11:

for \ell \leftarrow 1 to \lceil K/K_T \rceil do

▷ Over time tiles

12:

SCHEDULETILE(i, j, \ell)

13:

14:

end for

end for

15:

16: end for

```

type, which will ingest a fixed size input tile as the base case of the recursion.

Contemporary approaches build GEMM libraries with autotuning as a solution that addresses the delicate balance of parallelism and locality. GEMM problems are benchmarked to determine the peak performance configurations. While autotuning results in the solution with 100% efficiency in tuned cases, it takes  $O(P \times M \times N \times K)$  for P tiling configurations, with an additional complexity when adding different batch- or grouped GEMM-dimensions, and is not a scalable approach.

### B. Autotuning and Triton

Triton is a domain-specific language and compiler framework designed for writing high-performance GPU kernels, particularly those used in deep learning and tensor computation workloads [4]. Triton aims to simplify GPU programming with a high-level Python interface that delivers performance comparable to hand-optimized kernels. Triton kernels are written in Python and compiled Just-In-Time (JIT) to target specific GPU architectures. This allows developers to focus on the algorithmic structure of kernels while leaving many low-level optimization details to the compiler.

To achieve performance portability across different input sizes and hardware platforms, Triton includes an autotuning system, a mechanism commonly found in modern GPU programming frameworks such as TVM [7], TensorRT [8], TensorFlow [9], and TorchInductor [10]. Autotuning refers to the process of automatically exploring a space of implementation choices, such as tile sizes, memory tiling strategies, loop unrolling factors, and warp scheduling parameters to discover configurations that deliver optimal runtime performance for a specific target device and input shape.

In Triton, the autotuning mechanism is exposed through the @triton.autotune decorator. Users define a set of candidate configurations using triton.Config objects, where each configuration specifies compile-time parameters like tile sizes, number of warps/wavefronts, and pipeline stages. Additionally, users provide a set of input-dependent tuning keys (e.g., tensor size or shape) which determine when a new tuning search should be triggered. When a Triton kernel is first invoked for a particular key, the framework compiles all candidate configurations and benchmarks them on the target GPU using an event-based mechanism to measure execution latency. The configuration that yields the lowest execution time is selected as the optimal one and is cached internally for later reuse in subsequent invocations with the same tuning key.

However, the autotuning process introduces several forms of overhead. First, the initial tuning phase incurs compilation and measurement costs which can be significant when the configuration space is large. Second, the accuracy of the autotuner is bounded by the quality and completeness of the candidate configuration space that is manually provided by the user. Triton currently uses an exhaustive search over the user-defined configurations, which limits scalability and adaptability to applications that have a wide variety of kernel shapes and sizes. Finally, the need to benchmark each configuration at runtime makes this approach unsuitable and impractical for many applications, such as those with:

- Dynamic tensor shapes and sizes that vary from run-torun.

- Real-time constraints that demand low latency, such as online inference or control systems, and

- Applications with an already extremely high cost and power consumption such as LLM training runs.

The complex underlying relationship between GEMM kernel configurations, parallelism, locality, and performance has long been studied [11], [12], [13], [14]. Many of these studies analytically derive the ideal tiling configurations based on architectural shapes and bottlenecks. We extend this concept to the highly parallel and complex GPU architectures with GEMM as an example. In the next two sections, we provide an analytical model for capturing these intricacies on the AMD Instinct<sup>TM</sup> MI300X accelerator.

# C. Analytical Performance Models for GPU GEMM

Recent GPU optimization systems increasingly employ analytical or semi-analytical models to reduce the cost of empirical autotuning. CUTLASS [15] and cuBLAS [16], for instance, use hand-engineered heuristics to assess the viability of threadblock tiles based on memory traffic, register pressure, and tensor-core utilization. These rules work well for CUDA templates but are closed sources and tightly coupled to NVIDIA-specific execution models which do not transfer cleanly to Triton. Likewise, Ansor and AutoTVM [17], [18] combine analytical reuse estimates with learned correction terms to prune large search spaces; however, their reliance on data-driven fitting makes them less suitable for dynamic-shape

workloads or scenarios requiring deterministic, zero-sample prediction.

Several works also extend the roofline model to better capture locality in GPU kernels. DeLTA [19], for example, introduces a locality-aware roofline that predicts L1/L2 traffic via cache-blocking and reuse-distance analysis. Whereas DeLTA analyzes the performance of predefined kernel configurations, *tritonBLAS* uses only calibrated hardware bandwidths and instruction latencies to directly rank and select GEMM tile shapes. This enables microsecond overhead, deterministic configuration selection within Triton, supporting dynamic shapes and eliminating the need for runtime autotuning.

# III. DESIGN GOALS

The design goals of our analytical model and framework are:

Achieve Near-Optimal Performance. The model must efficiently select GEMM parameters such that the GEMM operations achieve near-optimal performance for a wide range of matrix shapes and sizes.

**No-Tuning Required.** The model must be designed as a general-purpose model that can be applied to any GEMM operation without the need for autotuning (exhaustive search) such as the one that exists within *Triton*.

*Lightweight and fast*. The model is meant to be used at *runtime* to guide the tiling decisions of the GEMM operation without impacting performance.

**Deterministic**. The model produces the same results for the same inputs, allowing for reproducibility and consistency in performance engineering.

**Architecture-Portable**. The model must be agnostic to the GPU micro-architecture, meaning it can be applied to any GPU architecture with minimal adjustments and without the need for hardware access to tune.

### A. Non-Goals

The model is not intended as a comprehensive performance model for GEMM latency prediction but rather to capture latency "trends," enabling accurate comparative evaluation of GEMM parameter choices.

**Non-GEMM Workloads**. This work is not intended for other GEMM-like algorithms such as various attention mechanisms, however we intend to explore that as part of our future works.

*Multi-GPU and Multi-Node*. This work focuses on GEMM kernel implementations within a single GPU and is not yet intended for distributed system environments.

# IV. TRITONBLAS: ANALYTICAL MODEL

We introduce *tritonBLAS*, a triton based GEMM library including an analytical model that captures the interplay between hardware architecture and algorithmic structure by decomposing the GEMM operation into hierarchical memory and compute stages. Our model enables accurate selection of a tiling hierarchy that maximizes both parallelism and locality on the target GPU architecture. *tritonBLAS* is built on the

| Memory Tiling Scope | Compute Scope | Physical Scope   | Logical     |

|---------------------|---------------|------------------|-------------|

| Instruction         | Matrix Core   | Matrix Core      | Instruction |

| Register            | SIMD          | SIMD             | Wave        |

| Shared Memory       | Compute Unit  | Compute Unit     | Workgroup   |

| L2                  | Group of CU   | XCD <sup>2</sup> | None        |

| LLC                 | All CUs       | Device           | None        |

TABLE I: The compute, memory, and logical scopes assigned to each level of tiles for an AMD Instinct<sup>TM</sup> MI300X GPU [20].

following key pillars described in detail in the subsections below:

- Hierarchical Tiling Structure

- Quantifying Parallelism (Spatial Loop Unroll)

- Quantifying Locality

- Tradeoffs between Parallelism and Locality

- GEMM schedule Latency

### A. Hierarchical Tiling Structure

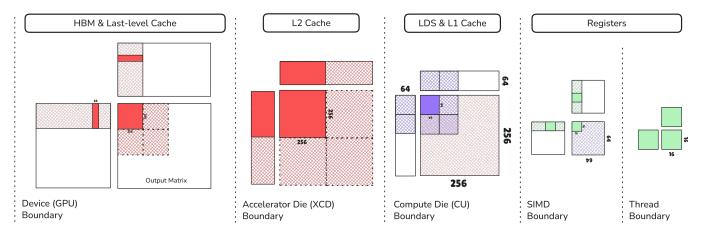

Our model captures the impact of tiling structures on parallelism and locality. Tiles are arranged in a hierarchy from the instruction-level "atom" of computation, to the overall systemlevel problem stored in main memory. The tiling hierarchy is defined as follows:

- 1) Instruction Level Tile: The tile size consumed by the matrix instruction (wmma, mfma, etc.) in each SIMD,

- 2) Warp/Wavefront (Register) Level Tile: A set of instruction tiles processed by a SIMD over time,

- 3) Workgroup/Thread block (Shared Memory) Level Tile: The Tile stored in software managed memory between SIMDs,

- 4) Cache Tile: Above software managed memory are one or more hardware managed memories, each with some set of shared memory tiles belonging to their scope. This can be modeled as a simple hierarchy of loads with increasing scope sizes (based on how many shared memory tiles are being processed in that scope.

- 5) Global Problem: The total overall problem unrolled over space (Compute Units) and time (when we run out of space).

From the bottom of the tiling hierarchy to the top encompasses the entire problem size and how it is mapped to progressively larger sub-tiles. Levels of hierarchical tiling exist to maximize data locality and reuse, which then enables a higher total bandwidth, thus allowing modern GPUs to keep the increasingly data hungry computational units fed. For the MI300X GPU, we map the tiling hierarchy to the logical and physical paradigms in the hardware/programming model as shown in Table I.

We implement a Triton-based kernel which leverages each of these scopes by parameterizing hierarchical tiling configurations. This enables us to permute the tiling hierarchy through simple changes of kernel configurations. tritonBLAS selects the kernel configurations by estimating the latency of the GEMM computation for each possible tiling hierarchy on a particular hardware architecture. To quantify the total system latency, we must consider the utilization of both the parallel compute and data movement resources.

# B. Quantifying Parallelism (Spatial Loop Unroll)

In modern compute accelerators, parallelism is one key principle that results in performance. We use many different compute resources to parallelize computation at different levels of the hierarchy. We will consider three levels of parallelism: matrix/tensor core-level parallelism [21], [22], parallelism within a compute unit, and parallelism across compute units. Our model captures and quantifies the performance impact of each of these types of parallelism with well-defined deterministic expressions that do not require heuristic tuning.

To formulate this expression, we use the latency of processing the *lowest* level tile which is determined by how many operations are parallelized across the matrix/tensor cores. In most cases a programmer has very little control over matrix/tensor core parallelism: it is defined by the architects of the GPU as the latency of the matrix instruction (e.g. wmma or mfma instructions [23], [24]). This means that we can assume the latency is a constant, resulting in a consistent throughput of matrix instructions with dimensions  $MI_M, MI_N, MI_K$ in some fixed amount of time  $L_{MI}$  which can be used to parameterize all other computations.

Algorithm 3 Calculate the Compute Latency of a Shared Memory Tile

**Require:**  $MI_M, MI_N, MI_K$ Dimensions of

Matrix/Tensor Instruction

**Require:**  $MT_M, MT_N, MT_K$ Dimensions of Shared

Memory Tile

**Require:**  $L_{MI}$ ▶ Latency of a matrix instruction **Ensure:**  $N_{MI}$  total Matrix Instructions per Shared Memory

**Ensure:**  $L_{MT}$  > compute latency per Shared Memory Tile

- 1:  $N_{MI,M} \leftarrow \left\lceil \frac{MT_M}{MI_M} \right\rceil$ 2:  $N_{MI,N} \leftarrow \left\lceil \frac{MT_M}{MI_N} \right\rceil$ 3:  $N_{MI,K} \leftarrow \left\lceil \frac{MT_K}{MI_K} \right\rceil$

- 4:  $N_{MI} \leftarrow N_{MI,M} \times N_{MI,N} \times N_{MI,K}$

- 5:  $L_{MT} \leftarrow L_{MI} \times N_{MI}$

Moving up the tiling hierarchy, we quantify the latency of the wavefront or register level tile which is parallelized over the set of SIMDs belonging to a compute unit. This parallelism means that the exposed latency for the shared memory or workgroup tile is exposed latency per register tile multiplied by the number of register tiles processed over time by a SIMD. Assuming the register tiles are processed in a way that results in a high utilization of the matrix multiplication acceleration

<sup>&</sup>lt;sup>2</sup>An XCD is a compute chiplet on the AMD Instinct<sup>TM</sup> MI300X GPU, which contains some number of compute units that share an L2 cache.

Fig. 1: Example of hierarchical tiling of output matrix for AMD's MI300X GPU (see Table I, illustrating device, XCD, CU, SIMD and Thread breakdown of the tile).

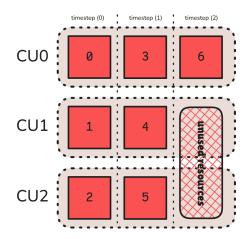

Fig. 2: Example of occupancy and CUs across time (timestep<sub>0</sub>, timestep<sub>1</sub> and timestep<sub>2</sub>) and available CUs ( $CU_0$ ,  $CU_1$ ,  $CU_2$ ).

unit, we can simplify the compute latency of a shared memory tile computation to be in terms of the dimensions and latency of the matrix instruction using Algorithm 3.

The last level of parallelism that tritonBLAS quantifies is the utilization of the compute units in the entire system, or occupancy [6]. To calculate occupancy, we first calculate using the dimension on which the problem is parallelized. Typical GPU GEMM implementations will map the M and N dimension across compute units in an output stationary dataflow. In this case, we parallelize workgroup tile dimension tensors in the M and N dimensions across space, and Kdimension processed sequentially processed over time. The occupancy is therefore determined by both the shape of the workgroup tile and the shape of the input problem in the M and N dimensions. Figure 2 shows, tiles parallelized across the CUs of a device with the occupancy of the total number of output tiles divided by the number of compute units. Figure 2 shows a key observation; the final timestep is the only "under occupied" timestep. This means that we can assume full occupancy (100% of CUs utilized) for all but the last timestep (also known as tail occupancy or the wave quantization problem [6]) to capture a complete view of occupancy of the entire problem. Algorithm 4 shows an algorithm for computing this tail latency.

# **Algorithm 4** Compute Active Compute Units in last timestep.

**Require:** M, N, K▶ Problem dimensions **Require:**  $MT_M, MT_N, MT_K$ Require:  $N_{CU}$ > Total number of CUs on hardware **Ensure:**  $active\_cu, \omega \triangleright \#$  CUs active for last wave, # Waves

- 1:  $n_{MT,M} \leftarrow \left[ \frac{M}{MT_{M}} \right]$  $2: \ n_{MT,N} \leftarrow \left\lceil \frac{\overline{N}}{MT_N} \right\rceil$

- 3:  $T_{\text{out}} \leftarrow n_{MT,M} \times n_{MT,N}$ 4:  $\omega \leftarrow \left\lceil \frac{T_{\text{out}}}{N_{CU}} \right\rceil$

- 5:  $active\_cu \leftarrow T_{out}\%N_{CU}$

- 6: return  $active\_cu$ ,  $\omega$

The degree of parallelism in GEMM across compute units influences not only the number of compute units utilized but also the availability of load and store units. This is particularly critical for small GEMM problems where a careful balance must be struck: issuing enough workgroups to sustain load/store throughput without fragmenting tiles to the point of compromising locality. An overly aggressive approach can undermine performance due to poor caching, despite increased parallelism. The following subsections detail how tritonBLAS captures this interplay between parallelism and locality.

### C. Quantifying Locality

In tritonBLAS we define two types of data locality: software managed and hardware managed. Modern GPU architectures support both paradigms using programmer-controlled memory (software managed) and caches (hardware managed). An example of software managed memory includes shared memory, where data movement is explicitly specified. In contrast, hardware managed locality relies on the hardware to transparently manage data placement and movement, as seen in caches. In the workgroup tile for example, the  $M \times K$  tile is reused N times and the  $N \times K$  is reused M times. This enables the programmer to precisely control data reuse within a SIMD and data sharing across SIMDs, thanks to the explicit management of shared memory.

The more implicit "cache tile" dimensions may be computed using the number of workgroup tiles that have access to a given cache. For example, if there are 16 compute units each processing their own workgroup tile, the area of the cache tile will be 16, and the options for arrangement of that cache tile are factorizations of 16. Within tritonBLAS we also predict the shape of the tile shared in a cache in a way that maximizes data reuse between the occupied compute units. Algorithm 6 shows an example of how to compute possible cache tile dimensions given a number of compute units belonging to a particular cache scope. Most often, the largest square formed out of compute units sharing the cache for a certain problem ensures the best data reuse, so in cases where we require a default, such as tile computation, we can often use  $floor(sqrt(N_{CU,Cache}))$ as a default factorization.

**Algorithm 5** Estimate Cache Hit Rate from tile dimensions.

```

Require: Cache-tile dimensions m_t, n_t;

Require: Workgroup tile dims. M_T, N_T, K_T

Ensure: Hit rate h

1: U \leftarrow (m_t M_T + n_t N_T) K_T

▶ Uncached reads

2: R \leftarrow (m_t n_t) (M_T + N_T) K_T

3: h \leftarrow 1 - \frac{U}{R}

▶ Total reads

⊳ Hit rate

Ensure: 0 \le h \le 1

4: return h

```

Algorithm 5 estimates the cache hit rate required for modeling memory latency in our analytical framework. The formulation assumes that higher-level caches interact with data in units defined by the tiles of the layer below, a key principle of hierarchical tiling. Thus, uncached reads (U) scale with the number of distinct tiles accessed per group of thread blocks, while total reads (R) reflect the full volume of memory traffic from all thread blocks.

```

Algorithm 6 Compute all tile-factorizations of N_{\text{CU\_Cache}}.

Require: Number of compute units in cache

Ensure: A list \mathcal{F} of all pairs (f_m, f_n) such that f_m \times f_n =

N_{\text{CU\_Cache}}

1: F ← []

▶ Initialize empty list of factor pairs

2: for i=1 to N_{\mathrm{CU\_Cache}} do

if N_{\text{CU\_Cache}} \mod i = 0 then j \leftarrow \frac{N_{\text{CU\_Cache}}}{i}

3:

4:

Append (i, j) to \mathcal{F}

5:

6:

end if

```

7: end for

8: return  $\mathcal{F}$

Our model incorporates cache capacity by comparing the tile-level working-set size at each K-step to the effective cache capacity and proportionally reducing the predicted hit rate whenever the footprint exceeds that limit. This captures the dominant capacity effects for GEMM, where reuse is governed mainly by tile-level temporal locality across K-steps. We do not model set associativity or replacement behavior, as these have limited influence on the large, regular access patterns in GEMM and would add significant complexity for only modest accuracy gains.

Using the hit rates for each level of the memory hierarchy, the memory latency for an example memory hierarchy with 2 caches before global memory can be computed using algorithm 7.

Algorithm 7 Calculate the Memory Latency of a Loop Iteration.

**Require:** Problem dims. M, N, K, tile dims.  $M_T, N_T, K_T$ **Require:** Hit rates  $H_1, H_2$  for Mem1 and Mem2

**Require:** Number of CU Loads  $Ld_{CU}$ , active CUs C, total

**Require:** Bandwidths  $R_{L1}, R_1, R_2, R_{\text{MEM}}$  in elements per compute cycle

**Require:** memory latency  $L_{\text{lat}}$

Ensure: Per-CU memory-bound latency  $L_{\mathrm{mem}}$

Ensure: Per-CU memory-bound latency

$$L_{\text{mem}}$$

1:  $L_{\text{CU\_lat}} \leftarrow \frac{Ld_{\text{CU}}}{R_{L_1}}$

2:  $T \leftarrow Ld_{\text{CU}} \times C$   $\Rightarrow$  Total loads across active CUs

3:  $L_1 \leftarrow \frac{T}{R_1}$   $\Rightarrow$  Latency of loads through Mem1

4:  $T_2 \leftarrow (1 - H_1)T$   $\Rightarrow$  Loads missing in Mem1

5:  $L_2 \leftarrow \frac{T_2}{R_2}$   $\Rightarrow$  Latency of loads through Mem2

6:  $T_{\text{M}} \leftarrow (1 - H_2)T_2$   $\Rightarrow$  Loads missing in Mem2

7:  $L_{\text{MEM}} \leftarrow \frac{T_{\text{M}}}{R_{\text{MEM}}} + L_{\text{lat}}$   $\Rightarrow$  Latency of memory loads

8:

9:  $L_{\text{mem}} \leftarrow \max(L_{\text{CU\_lat}}, L_1, L_2, L_{\text{MEM}})$

10: **return**  $L_{\mathrm{mem}}$

### D. Tradeoffs between Parallelism and Locality

The best tile for a problem is the one that achieves the lowest latency, however this does not necessarily correlate with the highest locality or parallelism. There are fine-grained trade-offs between parallelism and locality that determine the overall latency of a single loop iteration. Our analytical model quantifies the compute and memory latencies of one K-dimension iteration (over time). Due to software pipelining, the exposed computation latency is the maximum of the two latencies—data-movement/locality versus parallelism/occupancy—for a single iteration.

This means that, for each unique problem, there is a unique entry in the tradeoff space of parallelism and locality. The tradeoff can be conceptualized as a set of competing rooflines representing utilization of the different functional units (parallelism) and data busses (locality). Different tiling selections can be broken into categories based on which roofline their bottleneck belongs to for a particular problem. A coarsegrained set of bottlenecks that arise are:

- Load/Store Issue Rate Bound: There are not enough load/store units occupied to produce enough bandwidth. **Solution:** Increase load/store unit occupancy.

- Software Managed Memory Bandwidth Bound: Making the most reuse of the Shared Memory, but are bound by loads from it.

**Solution:** Increase register tile size to maximize reuse of data loaded from software managed memory.

• Cache Bandwidth Bound: The hardware managed caches are bounding the computation due to limited bandwidth.

Solution: Increase data reuse in software managed memory.

**Under-Occupied Compute Bound**: The utilization of the matrix instructions is high in the occupied compute units, but not enough compute units are occupied to achieve max throughput.

**Solution:** Unroll K-loop or change tile size to achieve higher occupancy.

• Max Parallelism Compute Bound: All compute units are occupied, and are achieving a high utilization of their matrix instruction due to a non memory bound software pipeline. In this state, we achieve the maximum possible performance.

Once certain factors are fully optimized, such as achieving compute-bound execution with full occupancy, further optimization may no longer be possible. However, many of these objectives are inherently conflicting: For instance increasing the load/store issue rate often requires greater parallelization across cores, which in turn necessitates smaller tile sizes. Smaller tiles, however, reduce data reuse in the cache hierarchy since reuse is closely tied to tile dimensions. The analytical model navigates these trade-offs by estimating total computational latency based on first-principles analysis of the underlying bottlenecks.

# E. Quantifying GEMM Latency

Lastly, all of these individual parameters are aggregated into a final "latency" as shown in Algorithm 9 which is used as a quantitative metric for the quality of a tiling solution for a problem. We must take into account that the pipeline is limited by the latency of the memory loads and compute instructions, whichever is larger, and that additional pipeline bubbles may exist. We call the pipeline bubble at the beginning (loads but no compute) the "prologue" and the pipeline bubble at the end (writes and no compute) the "epilogue". The prologue scales the same as the load stage of the software pipeline, but the store stage scales only in the output tile dimensions  $(MT_M, MT_N)$  instead of the input tile dimensions  $(MT_M, MT_N, MT_K)$ . Unlike the pipeline latency which will be incurred for each iteration in  $\frac{K}{MT_K}$ , the prologue and epilogue happen once per output tile.

However, as shown in Figure 2, a computation may be exposed to multiple timesteps if the number of output tiles **Algorithm 8** Compute the latency to complete an output tile

**Require:** hardware parameters H, problem dimensions M, N, K, tile sizes  $m_t, n_t, k_t$

**Require:**  $L_{mem}$  previously computed memory latency of tile loads

**Require:**  $L_{compute}$  previously computed compute latency of tile loads

**Require:**  $a \leftarrow \#$  of active CUs

**Require:** Bandwidths  $R_{L1}, R_1, R_2, R_{\text{MEM}}$  in elements per compute cycle

**Ensure:** tile latency  $L_{\rm tile}$

1:

$$L_{\text{prologue}} \leftarrow L_{\text{mem}}$$

2:  $L_{\text{epilogue}} \leftarrow \frac{a \cdot m_t \cdot n_t}{H \cdot R_{\text{mem}}}$

3:  $L_{\text{loopiter}} \leftarrow \max(L_{\text{compute}}, L_{\text{mem}})$ 4:  $I \leftarrow (\lceil K/k_t \rceil - 1)$

▶ # of loop iterations

5:  $L_{\text{tile}} \leftarrow L_{\text{prologue}} + L_{\text{epilogue}} + (L_{\text{loopiter}} \times I)$

6: **return**  $L_{\text{tile}}$

exceeds the number of compute units. This means the number of timesteps are directly related to the number of CUs in an architecture. Each timestep will have the latency of a single output tile, meaning we can use our previously mentioned output tile latency (assuming it produces  $N_{CU}$  output tiles) and the number of timesteps to compute the total GEMM operation latency using the computation shown in algorithm 9.

# **Algorithm 9** Compute Total GEMM Latency.

**Require:** hardware H

**Require:** problem dims M, N, K,

**Require:** tile dims  $m_t, n_t, k_t$

**Ensure:** total latency  $L_{\text{total}}$

1:  $n_m \leftarrow \lceil M/m_t \rceil$ ,  $n_n \leftarrow \lceil N/n_t \rceil$

2:  $N_{\text{waves}} \leftarrow \lceil (n_m \times n_n) / H. N_{\text{CU}} \rceil$

3:  $L_{\text{total}} \leftarrow N_{\text{waves}} \times L_{\text{tile}}$

4: return  $L_{\rm total}$

# V. Performance Evaluation

We present results on an AMD Instinct<sup>TM</sup> MI300X GPU using Triton version 3.4.0 using rocm/pytorch:rocm6.4.1 docker container. The results are presented as follows:

- Accuracy of tritonBLAS versus Triton's @triton.autotune exhaustive search,

- Analysis of the overhead of model prediction time for tritonBLAS and exhaustive search for Triton.

- General performance of *tritonBLAS* compared to vendor's peak GEMM implementation (using PyTorch.)

- Performance on key matrix sizes derived from Llama3

In our examples, we choose the float 16 (FP16) data type with both matrices being contiguous in K in memory.

# A. Accuracy of tritonBLAS vs. @triton.autotune

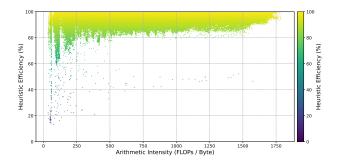

We compared *tritonBLAS*'s tile selection against the tiling selection achievable through an exhaustive search over all tiling combinations. In our experiment we used 150,000 random problem sizes whose dimensions are multiples of 128 less than 8193. We measure the performance of each set of tiling parameters exhaustively. We report the **selection efficiency**. The selection efficiency is defined as the percent of achieved performance by tritonBLAS relative to the maximum achieved performance in the exhaustive search of all options. In this experiment *tritonBLAS* achieves a 94.7% selection efficiency relative to the exhaustive search. Without the overhead of autotuning, *tritonBLAS* can achieve near-optimal performance of the exhaustive search based solution.

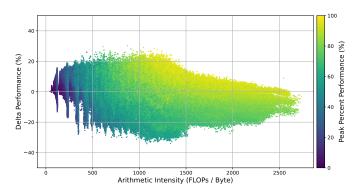

Figure 3 visualizes the achieved efficiency achieved per problem over the 150,000 problem shapes and sizes. The x-axis represents arithmetic intensity (flops/byte) of a problem, the y-axis represents efficiency achieved by the model, with 1.0 being best kernel predicted. Most data points are densely clustered near the top of the graph, indicating high heuristic efficiency across a wide range of arithmetic intensities, with more variation at lower intensities (latency-bound problems).

Fig. 3: Efficiency of *tritonBLAS* relative to Triton's autotune exhaustive search across 150,000 sizes.

# B. Overhead of using tritonBLAS

tritonBLAS is capable of significantly faster solution selection than the existing tuning-driven selection process. This is enabled by tritonBLAS's non-iterative math on the problem and tile dimensions, only looping over the number of parameters. Autotuning (exhaustive search) based approaches on the other hand will run the kernel for each parameter on each problem size, resulting in a much larger selection overhead. Solution selection in tritonBLAS adds a static cost of estimating latency for every candidate tile but removes the cost of exhaustively building and benchmarking each of the kernels resulting in a significant savings in the latency of new problem shapes. In other words, tritonBLAS has a purely linear overhead in P, while exhaustive search incurs an additional multiplicative factor of MNK. This problem becomes worse when we account for batched or grouped GEMM, where the cost/complexity for contemporary approach scales to  $\Theta(PMNKB)$ , where B is the number of batches.

Table II demonstrates a striking advantage of *tritonBLAS* over traditional Triton autotuning in terms of tile selection time. While autotuning incurs a cost proportional to the number of tile candidates (e.g., over 11 seconds for 75 tiles),

| Problem Size $(M \times N \times K)$                             | Triton Autotuning (s) $\mathcal{O}(TMNK)$ | tritonBLAS (s) $\mathcal{O}(T)$ |

|------------------------------------------------------------------|-------------------------------------------|---------------------------------|

| 512 × 512 × 512                                                  | 11.965                                    | 0.000070                        |

| $1024 \times 1024 \times 1024$<br>$2048 \times 2048 \times 2048$ | 11.928<br>12.303                          | 0.000057<br>0.000073            |

| $4096 \times 4096 \times 4096$<br>$8192 \times 8192 \times 8192$ | 13.537<br>48.087                          | 0.000055<br>0.000075            |

| $16384 \times 16384 \times 16384$                                | 1383.594                                  | 0.000073                        |

TABLE II: Comparison of selection time (in seconds) of Triton Autotuning vs *tritonBLAS* Heuristic and Tile Selection with 75 configurations searched. Shows that *tritonBLAS* does not scale with the problem sizes and is orders of magnitude faster selection than tuning-based approach.

the heuristic-based selection reduces this to the order of microseconds, representing an improvement of five to six orders of magnitude. In both instances, the results of parameter selection can be cached resulting in a subsequent selection for the same problem taking on the order of 1s of microseconds. tritonBLAS performs analytical tile selection in 50–80 us, independent of GEMM size, whereas Triton's autotuning requires compiling and benchmarking every candidate configuration, taking 10–50 seconds for the same 75 configurations (Table II). This means tritonBLAS typically selects a near-optimal kernel more than five orders of magnitude faster than autotuning. This makes tritonBLAS far more suitable for dynamic workloads, large search spaces, or environments where tuning cost dominates runtime.

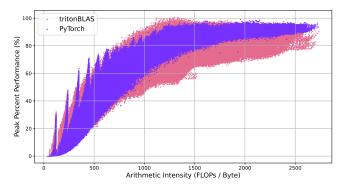

### C. General Performance of tritonBLAS in Triton

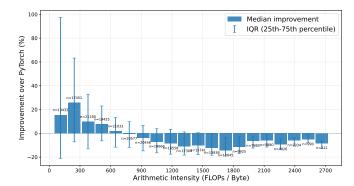

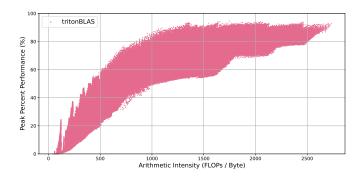

PyTorch matrix multiply also provides a python accessible method to perform matrix multiply on GPU using vendor libraries which, in the case of MI300X, are autotuned to achieve peak performance on the hardware. The results in Figure 4a show a comparison of the performance of our *tritonBLAS* implementation with PyTorch's matrix multiplication function. *tritonBLAS* uses techniques such as Stream-K [6], to manage wave quantization to get better GPU occupancy for all GEMM shapes and sizes. On average, *tritonBLAS* is 3% better than PyTorch's matrix multiplication.

Figure 4a also shows some performance gap from PyTorch, despite the efficiency of selection shown in Figure 3. While some of this gap can be attributed to the 5% average gap in selection efficiency we also find a significant portion comes from tile quantization; libraries such as the one used by PyTorch, tiling parameters are available in increments of matrix dimensions. Triton however, does not support tiles which do not have power of 2 tile dimensions, limiting options for managing tile quantization [4], [27].

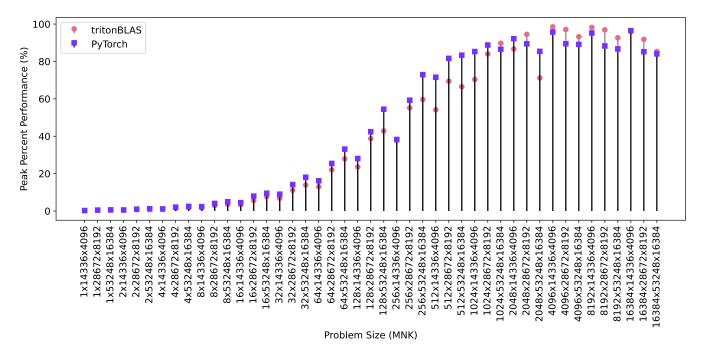

### D. tritonBLAS on Key Llama3 Matrices

Figure 6 illustrates the performance comparison between *tritonBLAS* and torch.matmul() across a range of problem sizes on the MI300X architecture. While Figure 4a highlights overall performance trends, this plot emphasizes that achieving high performance on key matrix sizes is equally important.

(a) Peak percent performance of *tritonBLAS* and torch.matmul() on AMD's Instinct<sup>TM</sup> MI300X. Peak percent throughput is normalized to maximum achievable performance as highlighted by Ben Sander [25], [26]. We show how closely the *tritonBLAS* implementation approaches the performance of the optimized torch's tuned and optimized implementation.

(b) Delta percent between torch.matmul() optimized GEMM implementation and *tritonBLAS*. Tritonblas performs within 20% of vendor libraries called by torch.matmul()

(c) Percent of Peak as a function of Arithmetic Intensity of *triton-BLAS* and torch.matmul() on AMD's Instinct<sup>TM</sup> MI300X.

(d) Binned peak percent performance of *tritonBLAS* and torch.matmul() on AMD's Instinct<sup>TM</sup> MI300X.

Fig. 4: Comparison between *tritonBLAS* and torch.matmul() on MI300X, showing peak percent performance (top-left), delta percent (top-right), performance vs. arithmetic intensity (bottom-left), and binned peak percent performance (bottom-right).

Fig. 5: *tritonBLAS* performance characteristics on AMD's Instinct<sup>TM</sup> MI350X. The *tritonBLAS* framework demonstrates strong performance on AMD Instinct<sup>TM</sup> MI350X, requiring only minor constant adjustments from the MI300X implementation.

The sizes shown here are derived from the Llama 3 model workload [28], making them representative of real inference demands. Our results show that *tritonBLAS* competes closely with the peak performance of torch.matmul(), with a maximum observed speedup of  $1.10\times$  and outperforming PyTorch in 10 cases. Although *tritonBLAS* is on average 13.9% slower, it still delivers performance that is highly competitive with the best kernels available for this hardware.

# E. Architecture Portability

Triton exposes a large configuration space with 50–150 valid tiles per GEMM depending on datatype. Architectural constraints create sharp performance cliffs and multiple disjoint optima, making the space unfriendly to random search methods. We display that our dataset is representative of many tradeoffs and arithmetic intensities without bias towards a particular intensity in figure 4d and show the average performance in bins of intensity in both 4d and 4c

Fig. 6: Delta percent between torch.matmul() and *tritonBLAS* on key Llama3 [28] matrix sizes. This plot shows how *tritonBLAS*'s selection is able to match the performance of optimized GEMM implementation.

The analytical model is architecture-portable as it depends only on a small set of calibrated hardware parameters: cache and memory bandwidths, access latencies, and MFMA/Tensor Core instruction shapes. Updating these values is sufficient to retarget the model to a new GPU. As shown in Fig. 5, applying the same model to AMD's MI350X (with only these parameters changed) yields performance trends consistent with MI300X, demonstrating straightforward crossarchitecture transfer. MI300X remains our primary evaluation platform due to resource constraints, but the MI350X results confirm that no additional tuning or model changes are required.

# VI. CONCLUSION AND FUTURE WORK

tritonBLAS introduces a deterministic, analytical framework for GEMM kernel parameter selection that eliminates the need for runtime autotuning. By modeling the interplay between GPU architecture, tiling hierarchies, parallelism, and data locality, tritonBLAS achieves near-optimal performance, 94.7% of exhaustive search efficiency, while drastically reducing configuration overhead. The model's architecture-agnostic design and reproducibility make it suitable for diverse workloads and hardware platforms. Performance evaluations demonstrate its scalability, low latency, and competitive throughput compared to vendor-optimized libraries. This work lays the foundation for future extensions to multi-GPU environments and broader algorithm classes, offering a practical and efficient alternative to empirical tuning in high-performance computing and machine learning applications.

### VII. ACKNOWLEDGMENTS

The authors would like to thank Minsu Kim, Babak Poursartip, Vinayak Gokhale, Mike Schulte, Ralph Wittig, Brad Nemanich and Khasid Ali Khan for the their continuous feedback and support in the development of Origami and tritonBLAS. AMD, the AMD Arrow logo, AMD CDNA<sup>TM</sup>, AMD Instinct<sup>TM</sup>, AMD ROCm<sup>TM</sup>, AMD Infinity Cache<sup>TM</sup>, AMD Infinity Fabric<sup>TM</sup>, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

### REFERENCES

- [1] K. Asanović, R. Bodík, B. Catanzaro, J. Gebis, P. Husbands, K. Keutzer, D. Patterson, W. Plishker, J. Shalf, S. Williams, and K. Yelick, "The landscape of parallel computing research: A view from berkeley," University of California, Berkeley, Tech. Rep. UCB/EECS-2006-183, 2006. [Online]. Available: http://www2.eecs.berkeley.edu/ Pubs/TechRpts/2006/EECS-2006-183.html

- [2] J. J. Dongarra, J. D. Croz, S. Hammarling, and I. Duff, "A set of level 3 BASIC linear algebra subprograms," ACM Transactions on Mathematical Software, vol. 16, no. 1, pp. 1–17, 1990.

- [3] OpenAI, "Gpt-4 technical report," https://cdn.openai.com/papers/gpt-4. pdf, 2023, accessed: 2025-08-31.

- [4] P. Tillet, H. T. Kung, and D. Cox, "Triton: An intermediate language and compiler for tiled neural network computations," in *Proceedings of* the 3rd ACM SIGPLAN International Workshop on Machine Learning and Programming Languages (MAPL '19), ser. MAPL 2019, Jun. 2019, pp. 1–10.

- [5] A. Kerr, D. Merrill, J. Demouth, and J. Tran, "CUTLASS: Fast linear algebra in CUDA C++," 2017. [Online]. Available: https://devblogs.nvidia.com/cutlass-linear-algebra-cuda/

- [6] M. Osama, D. Merrill, C. Cecka, M. Garland, and J. D. Owens, "Stream-K: Work-centric parallel decomposition for dense matrix-matrix multiplication on the GPU," *CoRR*, vol. abs/2301.03598, no. 2301.03598, Jan. 2023

- [7] T. Chen, T. Moreau, Z. Jiang, L. Zheng, E. Yan, H. Shen, L. Cowan, L. C. C. Wang, C. Guestrin, and A. Krishnamurthy, "Tvm: An automated end-to-end optimizing compiler for deep learning," in 13th USENIX Symposium on Operating Systems Design and Implementation (OSDI), 2018, pp. 578–594.

- [8] NVIDIA Corporation, NVIDIA TensorRT Developer Guide, 2024.[Online]. Available: https://docs.nvidia.com/deeplearning/tensorrt/

- [9] M. Abadi, P. Barham, J. Chen, Z. Chen, A. Davis, J. Dean, M. Devin, S. Ghemawat, G. Irving, M. Isard et al., "Tensorflow: A system for large-scale machine learning," in 12th USENIX Symposium on Operating Systems Design and Implementation (OSDI 16), 2016, pp. 265–283.

- [10] PyTorch Core Team, "Torchinductor: A compiler backend for pytorch," 2023, accessed 2025-06-06. [Online]. Available: https://github.com/pytorch/pytorch/tree/main/torch/\_inductor

- [11] F. G. Van Zee and R. A. van de Geijn, "BLIS: A framework for rapidly instantiating BLAS functionality," ACM Transactions on Mathematical Software, vol. 41, no. 3, pp. 14:1–14:33, June 2015. [Online]. Available: https://doi.acm.org/10.1145/2764454

- [12] F. G. Van Zee, T. Smith, F. D. Igual, M. Smelyanskiy, X. Zhang, M. Kistler, V. Austel, J. Gunnels, T. M. Low, B. Marker, L. Killough, and R. A. van de Geijn, "The BLIS framework: Experiments in portability," ACM Transactions on Mathematical Software, vol. 42, no. 2, pp. 12:1–12:19, June 2016. [Online]. Available: https://doi.acm.org/10.1145/2755561

- [13] T. M. Smith, R. A. van de Geijn, M. Smelyanskiy, J. R. Hammond, and F. G. Van Zee, "Anatomy of high-performance many-threaded matrix multiplication," in 28th IEEE International Parallel & Distributed Processing Symposium (IPDPS 2014), 2014. [Online]. Available: https://doi.org/10.1109/IPDPS.2014.110

- [14] T. M. Low, F. D. Igual, T. M. Smith, and E. S. Quintana-Ortí, "Analytical modeling is enough for high-performance BLIS," ACM Transactions on Mathematical Software, vol. 43, no. 2, pp. 12:1–12:18, August 2016. [Online]. Available: https://doi.acm.org/10.1145/2925987

- [15] NVIDIA, "Cutlass: Cuda templates for linear algebra subroutines and solvers," https://github.com/nvidia/cutlass, 2023.

- [16] —, "cublas library," https://docs.nvidia.com/cuda/cublas/index.html, 2023.

- [17] L. Zheng, Z. Jia, M. Guo, Y. Tan, T. Chen, M. Zhou, and J. Zhu, "Ansor: Generating high-performance tensor programs for deep learning," in OSDI, 2020.

- [18] T. Chen, T. Moreau, Z. Jiang, L. Shen, L. Ceze, C. Guestrin, and A. Krishnamurthy, "Autotvm: Automated tensor optimization," in OSDI, 2018.

- [19] D. Yan, D. Li, and Y. Xie, "Delta: Gpu performance model for deep learning applications," in HPCA, 2020.

- [20] AMD, "Introducing amd cdna<sup>TM</sup> 3 architecture," Advanced Micro Devices, Inc, White Paper, Dec. 2023, accessed July 8, 2025. [Online]. Available: https://www.amd.com/content/dam/amd/en/documents/ instinct-tech-docs/white-papers/amd-cdna-3-white-paper.pdf

- [21] Advanced Micro Devices, Inc, "Amd matrix cores," 2022, https://gpuopen.com/learn/amd-lab-notes/ amd-lab-notes-matrix-cores-readme/.

- [22] NVIDIA Corporation, "Tips for optimizing GPU performance using tensor cores," 2019, https://developer.nvidia.com/blog/ optimizing-gpu-performance-tensor-cores/.

- [23] Advanced Micro Devices, Inc, "amd instinct MI300" instruction set architecture reference guide," August 2025, accessed: 2025-08-07.

- [24] NVIDIA Corporation, "CUDA C++ Programming Guide," 2025, accessed: 2025-08-07. [Online]. Available: https://docs.nvidia.com/ cuda/cuda-c-programming-guide/

- [25] B. Sander, "Understanding peak, max-achievable & delivered flops, part 1," ROCm Blogs, Feb. 2025. [Online]. Available: https://rocm.blogs.amd.com/software-tools-optimization/Understanding\_Peak\_and\_Max-Achievable\_FLOPS/README.html

- [26] B. Sander, E. Masters, B. Poursartip, and H. Ho, "Measuring max-achievable flops part 2," ROCm Blogs, Feb. 2025. [Online]. Available: https://rocm.blogs.amd.com/software-tools-optimization/measuring-max-achievable-flops-part2/README.html

- [27] K. Zhou, M. Lezcano, A. Goucher, A. Rakhmati, J. Niu, J. Lebar, P. Szczerbuk, P. Bell, P. Tillet, T. Raoux, and Z. Moudallal, "Linear layouts: Robust code generation of efficient tensor computation using F<sub>2</sub>," 2025. [Online]. Available: https://arxiv.org/abs/2505.23819

- [28] Meta Platforms, Inc, "Introducing meta llama 3: The most capable openly available llm to date," https://ai.meta.com/blog/meta-llama-3/, 2024, accessed: 2025-08-14.