# A Chronological Analysis of the Evolution of SmartNICs

1<sup>st</sup> Olasupo Ajayi CAESAR Laboratory, Electrical & Computer Engineering Department, Queen's University, Kingston, ON, K7L3N6, Canada 0000-0001-6583-3749 2<sup>nd</sup>Ryan Grant

CAESAR Laboratory,

Electrical & Computer Engineering Department,

Queen's University, Kingston,

ON, K7L3N6, Canada

0000-0002-0163-3892

Abstract—Network Interface Cards (NICs) are one of the key enablers of the modern Internet. They serve as gateways for connecting computing devices to networks for the exchange of data with other devices. Recently, the pervasive nature of Internet-enabled devices coupled with the growing demands for faster network access have necessitated the enhancement of NICs to Smart NICs (SNICs), capable of processing enormous volumes of data at near real-time speed. However, despite their popularity, the exact use and applicability of SNICs remains an ongoing debate. These debates are exacerbated by the incorporation of accelerators into SNIC, allowing them to relieve their host's CPUs of various tasks. In this work, we carry out a chronological analysis of SNICs, using 370 articles published in the past 15 years, from 2010 to 2024, to gain some insight into SNICs; and shed some light on their evolution, manufacturers, use cases, and application domains.

Index Terms—Data Analysis, DPU, FPGA, HPC, Network Interface Cards, NIC, SmartNIC

## I. Introduction

Smart Network Interface Cards (SNICs) are a type of network interface card (NIC) that are equipped with a system-on-chip (SoC) capable of running full-fledged operating systems and can be programmed to handle various tasks, thus offloading such tasks from the host's Central Processing Unit (CPU) [1], [2].

Recently, several terminologies have emerged around the concept of SNICs, including Network Accelerators, Data Processing Unit (DPU), and FPGA-NIC (Field Programmable Gateway Array - NIC). There has also been a growing debate about the exact purpose and use cases of these devices. In many contexts, especially in High Performance Computing (HPC), SNICs are considered accelerators that are used to offload various tasks off the main CPU. The concepts of network and workload offloading are well discussed in literature hence, not repeated here. Rather, in this work, we carry out a chronological analysis of the concept of SNICs, exploring scholarly publications spanning a 15-year period from 2010 to 2024. The purpose and main contributions of this work are as follows:

To gain insights into how SNICs are being used in different scenarios, by exploring applications and use cases reported in literature.

- Identify the main research areas where SNICs have been and are being applied.

- Curate a dataset of published works on SNICs spanning a 15-year period.

- Identify the main manufacturers of SNICs and how their products have evolved over the past decade and a half.

## II. Background

Although the Transmission Control Protocol/Internet Protocol (TCP/IP) and Open Systems Interconnection (OSI) stacks have received a lot of attention, NICs are undoubtedly the unsung heroes of modern networks. A NIC (or network adapter) is a hardware component that connects a computing device to a network and allows the device to receive or send data to other devices on the network. NICs operate in both the first and second layers (physical and data link) of the OSI stack or layer 1 (link layer) of the TCP/IP protocol stack, implementing the IEEE 802.3 (wired Ethernet) and IEEE 802.11 (wireless) communication standards.

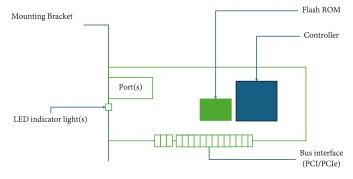

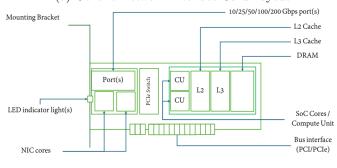

NICs are responsible for host addressing within a network (via Media Access Control or MAC address), data transmission (between its host device and the network), transmission control (including congestion avoidance and prevention of packet collisions), and error detection and correction (via checksums and redundancy checks). Fig. 1 shows a graphical comparison of the basic layouts of a classic NIC and a smart NIC (SNIC).

Computer networks have been growing at an exceptional rate in recent years. This is mainly due to the increase in global internet usage, which, as at the time of writing, stands at approximately 66% of the world's population [3], and the ubiquity of smart phones and connected devices. These factors have led to the evolution of NICs from mere network connection points to more advanced devices fitted with specialized circuitry capable of handling higher data transmission rates, faster processing, and more functionalities, called Smart NICs (SNICs).

From a functionality standpoint, SNICs can be classified into three categories - Application Specific Integrated Cir-

#### (a) Generic Network Interface Card Layout

(b) Generic SNIC

Fig. 1: Network Interface Cards

cuit (ASIC) based, Field Programmable Gateway Array (FPGA) based, and those that incorporate SoCs, called Data Processing Units (DPUs). ASIC-based SNICs, as the name suggests, are designed for a specific purpose, such as offloading network tasks off the CPU. These NICs are cheaper but not flexible, hence, cannot easily adapt to network needs. FPGA-based SNICs, on the other hand, are flexible and can be programmed for multiple network tasks. DPUs (SoC-based SNICs) have built-in processing units (ARM processors), memory, and host interface, in addition to ASIC or FPGA processing elements. They can be considered synonymous to edge or single-board computers and are highly programmable using C/C++ and/or Programming Protocol-independent Packet Processors (P4) programming languages. DPUs often have multiple accelerators and can be programmed to offload several tasks from their host's CPU [1], [2], [4].

## III. Related Works

A comprehensive review of SNICs was carried out in [7]. The work defined "SmartNICs" as programmable NICs, then compared various SNICs based on their design, hardware architecture, and type (ASIC, FPGA, SoC, Hybrid). A survey of the programmability of Smart-NICs, using P4, C/C++, and Nvidia's DOCA was also done by the authors. Finally, the work considered some common SmartNICs, specifically Nvidia's Bluefield and Netronome's NFP series, reviewed research publications

where they were used, and discussed some of the open challenges and limitations of SmartNICs in general.

In [9], a survey of SNICs was performed from both industrial and research perspectives. The authors reviewed several articles in an effort to propose a universal definition of the term "SmartNIC". This was then followed by an exploration of the various architectures, i.e., ASIC-based, FPGA-based, and SoC-based SNICs. Finally, the work compared two products, Intel's Programmable Acceleration Card (PAC) N3000 and Nvidia's Bluefield-2, and their performance in mitigating Distributed Denial of Service (DDoS) attacks.

In a similar work, [5] surveyed SNICs holistically. The authors began by comparing classic NICs with SmartNICs and then showed the evolution from the former to the latter. The work grouped SNICs into five categories, namely, ASIC-based, FPGA-based, ASIC+FPGA hybrid, ASIC+SoC and FPGA+SoC. Using a taxonomy as a guide, the authors compared various SNICs based on their programmability, CPU architecture, and traffic switching abilities. Task offloading using SNICs was also discussed and grouped into security, network, storage, and computing tasks. The paper was concluded with a discussion on the open challenges of SNICs.

An evolutionary trend analysis of SNICs was carried out in [8]. SNICs from major manufacturers were reviewed, as well as their applications as workload accelerators in various domains, including telecommunications, storage, artificial intelligence, and edge processing. Similarly, [6] also explored the potential of using SNICs as general-purpose accelerators in HPC. They explored the offloading mechanisms of Nvidia's Bluefield-2 DPU using Pennant and BigSort benchmarking applications.

This work, unlike other related works, does not focus on the architectures, taxonomy, or comparison of offloading capabilities of SNICs in HPC; instead, we carry out a systematic chronological analysis of SNICs, using published articles, to provide insights into their evolution and real-world applications over a 15-year period. To the best of our knowledge, this work is the first of its kind with respect to SNICs.

## IV. Methodology

Being a systematic review, this work followed the PRISMA guidelines [10], with the following steps taken to carry out the analysis.

- Step 1 Data collection: data on SNICs related publications were curated from IEEE Xplore repository.

"DPU", "SmartNIC", and "FPGA-NIC" were used as keywords, with the search limited to articles published in the 15 years between 2010 and 2024.

- Step 2 Filtration / screening: Step 1 resulted in about 490 articles, which were then passed through two filtration phases. In the first filtration phase, we read the abstract and index or key words of each article to filter out irrelevant articles. 26 articles were

excluded through this process. In the second phase, we read the entire content of each of the remaining articles. During this phase, we were able to exclude articles relating to smart switches and other solutions that were also termed data processing units (DPU) but referred to systems designed for other forms of end-to-end data processing. Finally, we were left with 370 articles.

- Step 3 Pre-processing: We pre-processed the metadata of each article (in bib and JSON formats) and created a Comma Separated Value (CSV) file using JabRef [11]. The initial CSV file had 30 columns (fields), from which we extracted six (6) relevant fields, namely "Author", "Title", "Year", "Abstract", "Publisher", and "NIC Type". NIC type refers to the type of SNIC used in the article, i.e., "DPU", "FPGANIC" or "SmartNIC".

- Step 4 Dataset preparation: We read each article to extract information on the type, model, and manufacturer of the SNIC(s) used by the researcher(s) / author(s). We also extracted information about the application domain (e.g., Medicine, AI, Databases, etc.), and specific focus of the research work (e.g., Energy conservation, Edge Processing, Performance evaluation and benchmarking, etc.). Finally, we included four (4) additional fields in our dataset, namely "Manufacturer", "Device", "Research Focus", and "Application Domain". In total, we had 10 fields and 370 rows in our dataset. The dataset curated from this work is available at [12].

- Step 5 Data analysis: In this step, we performed a chronological analysis of the data using a combination of Python, Microsoft Excel and PowerBI. For each analysis, the dataset (of articles) was grouped into 3 bins, each spanning a 5-year interval "2010–2014", "2015–2019" and "2020–2024".

## V. Research Findings

As stated above, the primary objective of this work was to perform a chronological analysis of the evolution of SNICs over a 15-year period, divided into 5-year bins. These bins would be used as guardrails for presenting the finds.

In the results presented in this section, the terms "DPU", "SmartNIC" and "FPGA-NIC" refer to the terms explicitly used by the authors of each publication. To avoid confusion between "SmartNIC" and "SNIC", in this work, "SNIC" refers to a general term used to categorize all forms of "smart" NICs, i.e., ASIC / FPGA / SoC based NICs, as described in section 2.

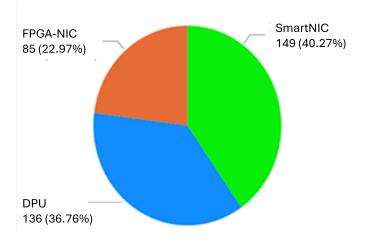

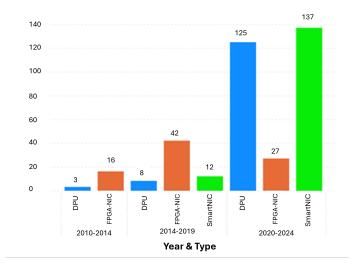

# A. Device Type

The distribution of devices by type is shown in Fig. 2. Although the figure shows that "SmartNICs" are the most common, this was not the case until 2020–2024. Fig.

Fig. 2: Device Types

3 reveals that "SmartNICs" did not exist between 2010-2014, while "DPUs" was only reported in 3 articles [13]–[15]. Also, before 2020, "FPGA-NICs" were the most common type of SNIC. The exponential rise of "DPUs" and "SmartNICs" post 2020 is likely driven by the acquisition of Mellanox by Nvidia in 2020 and the emergence of its Bluefield brand of NICs.

Fig. 3: Device Type distribution over the past 15 years

#### B. Device Manufacturers

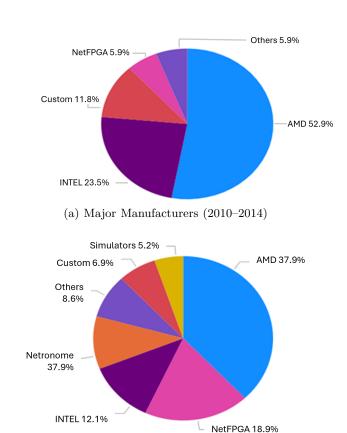

During the 15-year span, Fig. 4 shows that AMD was the dominant manufacturer. Even with the arrival of Nvidia in the 2020-2024 time frame, AMD still maintained almost 40% of the market share. Nvidia, Netronome, and Intel were, respectively, the second, third, and fourth largest SNICs manufacturers in the past 15 years.

## C. Device Models

Devices of different types and models were used in the 370 articles reviewed. In some cases, the authors provided

(c) Major Manufacturers (2020-2024)

**NVIDIA 27.7%**

Fig. 4: Device Manufacturers across the 15-year span

the exact device and model used, e.g., "Netronome Agilio NFP-4000 CX Dual-Port 10 Gigabit", while in other cases only the device family was mentioned, e.g., "Xilinx Virtex 7" or "NFP-4000". For this reason, our report has a mix of specific device model and family.

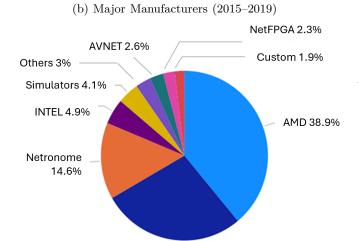

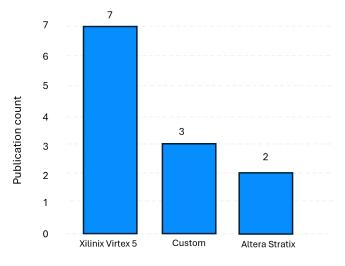

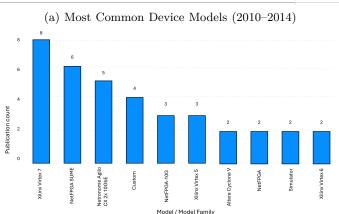

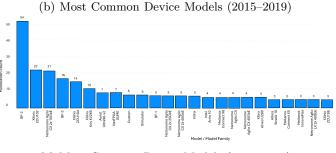

Please note that the graphs shown in Fig. 5 are truncated and only show the top-N devices for each time

Model / Model Family

(c) Most Common Device Models (2020–2024)

Fig. 5: Top-N SNIC Devices used between 2010-2024

frame. This was done for space-saving purposes. Table I provides information on the number of unique device models per time frame, using a truncation thresholds of at least 2,  $(N \ge 2)$ .

Between 2010 and 2014, Fig. 5a shows that three device models (AMD Xilinx Virtex-5, Intel Altera Stratix, and custom) were prominent. Custom refer to devices that were built by the authors, e.g., NanoBFP [35]. Other devices used in this time frame include Intel's Altera Cyclone

TABLE I: Summary of device count per time frame

| Time frame  | Unique Device Models | Top N (Truncation point) |

|-------------|----------------------|--------------------------|

| 2010 - 2014 | 11                   | N: $count \leq 2$        |

| 2015 - 2019 | 32                   | N: $count \leq 2$        |

| 2020 - 2024 | 94                   | N: $count \leq 3$        |

III, Xilinx Virtex-6, NetFPGA 10G, etc. Since each of these devices were reported in less than 2 publications, they were not shown in the graph.

Fig. 5b shows the top 10 devices used in the 2015-2019 time frame. AMD's Xilinx Virtex-7 (8) was the most common, followed by NetFPGA SUME, used in 6 research works, and Netronome's Agilio CX dual port 10GbE SmartNIC (5). Although "NetFPGA SUME" and "NetFPGA 10G" use Xilinx Virtex-7 and Virtex-5 chips, respectively, we do not consider them as part of the AMD Xilinx family. Finally, "Simulation" refers to research work in which software simulation tools, such as Vivado [36] and sPIN [37], were used instead of physical SNICs.

The 2020-2024 time frame was dominated by "DPU", which cumulatively represented more than 50% of all devices. These include Nvidia's Bluefield-2 (54) and Bluefield-3 (16), and AMD's ZCU 102 (23) and ZCU 104 (14) DPUs. The Netronome Agilio CX 2x10GbE SmartNIC was also common, as it was used in about 21 publications. The graph also shows that 4 articles used "Netronome Agilio CX", unfortunately, the authors did not specify the exact device model within the Agilio CX family of SmartNICs they used. Although only 24 devices are shown in Fig. 5c, a total of 94 unique devices were used in this period. The remaining 70 are not shown because they were used in less than 4 research work each ( $N \le 3$  in Table 1).

## D. Research Focus

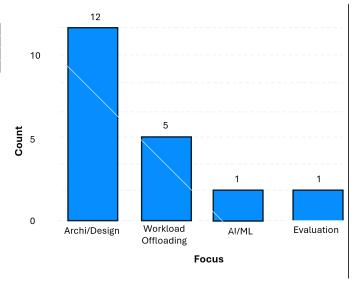

Fig. 6a shows that, between 2010 and 2014, researchers mostly focused on the architecture and design (Archi/Design) of FPGAs to improve network functionality, specifically reducing network latency. The few offloading tasks reported in this time frame were applied to Message Passing Interface (MPI) in HPC [16], memory (direct memory access), database processing and artificial intelligence in medical applications [13].

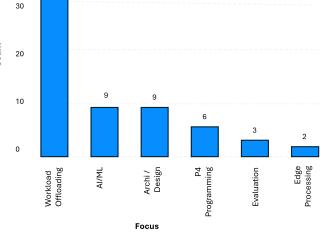

In addition to the four research areas in 2010-2014, programming of network devices using the P4 language [17], [18] and Edge processing [19], [20] were also investigated between 2015 and 2019, as shown in Fig. 6b. In the same period, the offloading of workloads onto SNICs became mainstream, with most offloading tasks geared towards security [21] and databases [22]. Similarly, the use of these devices to design and run Artificial Intelligence & Machine Learning tasks (AI/ML) [23], [24] also became common.

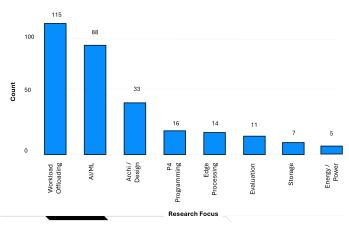

By 2020-2024, SNICs ("SmartNIC", "DPUs", and "FPGA-NIC") had become well established as tools for offloading various workloads and running AI/ML tasks.

(a) Major Research Focus (2010 – 2014)

(b) Major Research Focus (2015 - 2019)

(c) Major Research Focus (2020 - 2024)

Fig. 6: Distribution of Research Focus across the 15-year span

Fig. 6c shows that these two research areas represented 70% (40% and 30% respectively) of all research work related to SNICs in that time frame. In the same period, the application of SNICs in energy and power conservation [25], [26] as well as storage [27], [28] also become popular.

## E. Application Domains / Use Cases

Table II provides a concise distribution of the various use cases of SNICs ("DPUs", "FPGA-NIC", and "Smart-NIC") between 2010 and 2024.

In perusing the table, it immediately becomes clear that SNICs are pervasive and have been applied in numerous domains, beyond just networking. This is due to the offloading capabilities of SNICs, specifically the "DPU" and "SmartNIC". During the 15-year span, the highest number of non-network-specific use cases occurred in the most recent years (2020–2024).

"Security" had the highest number of applications (66 or 18% of all articles reviewed). This is unsurprising, as these use cases were aimed at securing networks. "Network Processes" had the second highest (46) use case. Again, this comes as no surprise, as SNICs are primarily network devices, and network processes include tasks such as network compression, filtration and firewalls. Interestingly, many researchers focused on "Performance Benchmarking / Improvement" (40), that is, analyzing and benchmarking the performance of SNICs. This implies that about 11% of all published work focused on the design / architecture of various forms of SNICs and benchmarking these variants against the state of the art.

Despite the popularity of AI and ML, only 7.5% of the publications reviewed discussed the application of SNICs to AI/ML specific tasks. To avoid confusion, in this context, "AI/ML Specific Tasks" refer to tasks that are solely associated with AI/ML. These include training [29], [30], quantization [31], [32], and pruning [33], [34] of AI/ML models on SNICs. The limited applications of SNICs in this domain is understandable, as SNICs are resource constrained with modest storage and processing capabilities, thus, are generally ill-suited for most AI/ML specific tasks, which usually require enormous computing resources.

#### VI. Insight & Discussions

Between 2010 and 2024, the following insights can be drawn about SNICs:  $\frac{1}{2}$

- FPGA-based and SoC-based SNICs were the most common type of SNICs due to their programmability and versatility.

- FPGAs are a major technological pedestal upon which modern day SNICs are built. This is because most "DPUs" and "SmartNICs", except Nvidia Bluefield 2 and 3, are hybridized forms of FPGA + SoC NICs.

- Regarding the terminology debate, the choice between "SmartNIC" versus "DPU" is mainly the manufacturer's preference. Considering the top 4 brands, Netronome uses the term "SmartNIC", while AMD uses both terms "SmartNIC" for its Alveo series and "DPU" for its Pensando series. Nvidia uses the term "SmartNIC" for its Connect-X series and "DPU" and/or "SuperNIC" for its Bluefield series. Intel uses the term "PAC" for its general or application-specific workload accelerators and Infrastructure Processing Unit (IPU) for its NICs developed for offloading infrastructure management tasks, such as networking, storage, and security.

- Many of the smaller SNIC manufacturers utilize AMD's FPGAs as their core. For example, NetF-PGA's SUME and NetFPGA-10G NICs use the Xilinx Virtex-7 and Virtex-5 FPGAs respectively. Similarly, Napatech NT200AS and NT40A01 NIC, respectively, use Xilinx XCVU5P and Xilinx KU11P FPGA, while Alpha-Delta ADM-PCIE-9H3 uses Xilinx XCVU33P. Netcope's NFB-200G2QL uses Xilinx XCVU7P, while Hitech Global's HTG-V5TXT is built on AMD's Xilinx Virtex-5 FPGA.

- The rise of "DPU" and "SmartNIC" has expanded the use of SNICs from pure networking tools to generalized devices (accelerators) capable of offloading different tasks from the host CPU. SNICs are now ubiquitous and are increasingly being applied in other seemingly unconventional application domains, such as autonomous vehicles, robotics, and medicine.

It is important to note that the manufacturers and devices mentioned in this work do not depict the entire landscape of SNICs, as this work is based on research articles published only in IEEE Xplore repository. There are numerous other manufacturers, such as Marvell - LiquidIO SmartNICs, Broadcom - Stingray, Cisco - Nexus, etc., that were not presented in this work. In addition, we have also identified about 1,500 related publications in ACM repository, which when analyzed might buttress or skew the results presented in this work.

## VII. Conclusion

In this paper, we performed a chronological analysis of the evolution of Smart Network Interface Cards (SNICs) over a 15-year period, from 2010 to 2024. 370 articles on SNICs published in IEEE Xplore repository were reviewed to gain insight into the evolution of SNICs and their applications in various domains. We identified the four main SNIC manufacturers, which are AMD, Nvidia, Intel, and Netronome, and their most prominent device models. We also discovered an exponential increase in the popularity of SNICs, specifically DPUs, between 2020–2024, and their general acceptance as accelerators to offload diverse workloads from the CPUs of their hosts.

Although this work unearthed several useful insights about SNICs, it only considered articles published in IEEE

TABLE II: Applications of SNICs across various Domains from 2010 to 2024

|                                        | Years     |          |           |          |           |     |          |          |       |

|----------------------------------------|-----------|----------|-----------|----------|-----------|-----|----------|----------|-------|

|                                        | 2010-2014 |          | 2015-2019 |          | 2020-2024 |     |          |          |       |

| Application domain / Use cases         | DPU       | FPGA-NIC | DPU       | FPGA-NIC | SmartNIC  | DPU | FPGA-NIC | SmartNIC | Total |

| 5G / 6G / Wireless Networks            |           |          |           | 2        |           | 3   |          | 10       | 15    |

| AI/ML Specific Tasks                   |           |          |           | 3        |           | 16  | 3        | 6        | 28    |

| Autonomous Vehicles & Automobile       |           |          | 1         | 2        |           | 10  |          | 2        | 15    |

| Blockchain                             |           |          |           | 2        |           |     |          | 2        | 4     |

| Cache / Memory                         |           | 5        | 2         | 5        |           | 7   | 6        | 8        | 33    |

| Cloud Computing                        |           |          |           |          |           | 1   | 1        | 8        | 10    |

| Data / Databases                       |           | 3        | 1         | 8        |           | 7   | 3        | 13       | 35    |

| Edge Processing                        |           |          |           |          |           | 10  |          | 1        | 11    |

| Energy / Power                         |           |          | 1         |          |           | 3   |          |          | 4     |

| Generic Tasks                          |           |          |           | 2        |           | 2   | 2        | 3        | 9     |

| Graph Processing                       |           |          |           |          |           | 2   |          |          | 2     |

| Human Activity Detection               |           |          |           |          |           | 2   |          |          | 2     |

| Medicine                               | 1         | 1        | 2         |          |           | 6   |          | 2        | 12    |

| Molecular Dynamics                     |           |          |           |          |           | 1   |          | 1        | 2     |

| MPI / HPC                              |           | 1        |           |          |           | 3   |          | 4        | 8     |

| Network Processes                      |           | 2        |           | 7        | 1         | 5   | 3        | 28       | 46    |

| Performance Benchmarking / Improvement | 1         | 1        |           | 2        | 2         | 24  | 2        | 8        | 40    |

| Resource Management                    |           |          |           |          |           | 2   | 1        | 1        | 4     |

| Robotics                               |           |          |           |          |           |     |          | 2        | 2     |

| SDN/NFV                                |           |          |           | 2        | 5         | 1   | 1        | 11       | 20    |

| Security                               | 1         | 3        | 1         | 7        | 4         | 18  | 5        | 27       | 66    |

| Task Scheduling                        |           |          |           |          |           | 2   |          |          | 2     |

| Total                                  | 3         | 16       | 8         | 42       | 12        | 125 | 27       | 137      | 370   |

Xplore. The exploration of other repositories, specifically ACM, could be a potential avenue to extend this work. Additionally, the use of SNICs in space and orbital satellites and in smart network switches was not considered in this work. These are opportunities for potential future work.

#### References

- Miano, S., Doriguzzi-Corin, R., Risso, F., Siracusa, D. and Sommese, R. (2019). Introducing SmartNICs in Server-Based Data Plane Processing: The DDoS Mitigation Use Case. IEEE Access, 7, pp. 107161-107170, 2019, doi:10.1109/ACCESS.2019. 2933491.

- Bhalgat, A. (2021, Sept. 14). Choosing the Best SmartNIC.

Technical Blog. https://developer.nvidia.com/blog/choosing-the-best-dpu-based-smartnic/

- [3] Kemp, S. (2024, Jan. 31). Internet Use in 2024. DATAREPORTAL https://datareportal.com/reports/digital-2024-deep-dive-the-state-of-internet-adoption

- [4] Chi, Y., Cui, W., Qiao, L., Long, X. and Wang, L. (2019). Hardware Architecture Design of the Deep-learning-based Machine Vision Chip. IEEE 3rd Information Technology, Networking, Electronic and Automation Control Conference (ITNEC), Chengdu, China, 2019, pp. 1110-1113, doi:10.1109/ITNEC. 2019.8729501.

- [5] Kfoury, E., Choueiri, S., Mazloum, A., AlSabeh, A., Gomez, J., and Crichigno, J. (2024). A Comprehensive Survey on SmartNICs: Architectures, Development Models, Applications, and Research Directions. IEEE Access, vol. 12, pp. 107297-107336, 2024, doi:10.1109/ACCESS.2024.3437203

- [6] Williams, B., Chen, Y., Poole, W. and Poole, S. (2023). Exploring Challenges Associated with Employing SmartNICs as General-Purpose HPC Accelerators. 2023 IEEE High Performance Extreme Computing Conference (HPEC), Boston, MA, USA, 2023, pp. 1-7, doi:10.1109/HPEC58863.2023.10363618.

- [7] Luizelli, M., Vogt, F., De Matos, G., Cordeiro, W., et al. Smart-NICs: The Next Leap in Networking. https://smartness2030.tech/wp-content/uploads/2024/05/Ch2.pdf

- [8] Boddupalli, R. and Sable, N. (2023). Smart NICs Evolution and Future Trends. Intel. https://www.intel.in/content/ dam/www/central-libraries/xa/en/documents/2023-12/ soc-track-smart-nics-1-.pdf

- [9] Döring, T., Stubbe, H., and Holzinger, K. (2021). SmartNICs: Current trends in research and industry. Network, 19. doi:10. 2313/Net-2021-05-1 05

- [10] Page, M., McKenzie, J., Bossuyt, P., Boutron, I., et al. (2021). The PRISMA 2020 statement: an updated guideline for reporting systematic reviews. bmj, 372. https://doi.org/10.1136/bmj.n71

- [11] Kopp, O., Snethlage, C. and Schwentker, C. (2023). JabRef: BibTeX-based literature management software. TUG-boat, 44(138), 441–447. https://doi.org/10.47397/tb/44-3/tb138kopp-jabref

- [12] Ajayi, O. (2025). 15 Year Evolution of Smart NICs. IEEE Dataport. https://dx.doi.org/10.21227/nwxe-ct19

- [13] Chen, Y., Wang, T. and Hu, Z. (2013, October). Implementation of an embedded dual-core processor for portable medical electronics applications. In 2013 IEEE 10th Int. Conf. on ASIC (pp. 1-4). IEEE.

- [14] Rao, X., Wang, T. and Wang, Y. (2013, October). A low-power and high-efficiency cache design for embedded bus-based symmetric multiprocessors. In 2013 IEEE 10th Int. Conf. on ASIC (pp. 1-4). IEEE.

- [15] Naghash, F. and Eshghi, M. (2014, May). Design an ASIP for Rabbit and HC-128 algorithms. In 2014 22nd Iranian Conf. on Electrical Engineering (ICEE) (pp. 1174-1179). IEEE.

- [16] Tanabe, N. and Nakajo, H. (2010, April). Acceleration for MPI derived datatypes using an enhancer of memory and network. In 2010 IEEE Int. Symp. on Parallel & Distributed Processing, Workshops and Phd Forum (IPDPSW) (pp. 1-6). IEEE.

- [17] Mohammadkhan, A., Panda, S., Kulkarni, S., Ramakrishnan, K. and Bhuyan, L. (2019, November). P4NFV: P4 enabled NFV systems with SmartNICs. In 2019 IEEE conf. on network function virtualization and software defined networks (NFV-SDN) (pp. 1-7). IEEE.

- [18] Eran, H., Zeno, L., István, Z. and Silberstein, M. (2019, April). Design patterns for code reuse in HLS packet processing pipelines. In 2019 IEEE 27th Annual Int. Symp. on Field-Programmable Custom Computing Machines (FCCM) (pp. 208-217). IEEE.

- [19] Mitsuzuka, K., Tokusashi, Y. and Matsutani, H. (2018, December). MultiMQC: A Multilevel Message Queuing Cache Combining In-NIC and In-Kernel Memories. In 2018 Int. Conf. on Field-Programmable Technology (FPT) (pp. 134-141). IEEE.

- [20] Tuan, D., Truyen, N., Vu, N., Volvenko, S. and Hung, N. (2019, December). Experimental UWB wireless sensor system for locomotive engine parameters monitoring. In 2019 6th NAFOSTED Conf. on Information and Comp. Sci. (NICS) (pp. 154-159). IEEE.

- [21] Sutter, G., Ruiz, M., Lopez-Buedo, S. and Alonso, G. (2018, December). Fpga-based tcp/ip checksum offloading engine for 100 gbps networks. In 2018 Int. Conf. on ReConFigurable Computing and FPGAs (ReConFig) (pp. 1-6). IEEE.

- [22] Tokusashi, Y. and Matsutani, H. (2017). Multilevel NoSQL Cache Combining In-NIC and In-Kernel Approaches. IEEE Micro 37(5), 44-51.

- [23] Phu, H., Tan, T., Van Men, P., Van Hieu, N. and Van Cuong, T. (2019, December). Design and implementation of configurable convolutional neural network on FPGA. In 2019 6th NAFOSTED Conf. on Information and Computer Science (NICS) (pp. 298-302). IEEE.

- [24] Chi, Y., Cui, W., Qiao, L., Long, X. and Wang, L. (2019, March). Hardware Architecture Design of the Deep-learningbased Machine Vision Chip. In 2019 IEEE 3rd Info. Tech., Networking, Electronic and Automation Control Conf. (ITNEC) (pp. 1110-1113). IEEE.

- [25] Huang, J., Lou, J., Sun, Y., Wang, T., et al. (2023, October). Making Sense of Using a SmartNIC to Reduce Datacenter Tax from SLO and TCO Perspectives. In 2023 IEEE Int. Symp. on Workload Characterization (IISWC) (pp. 28-42). IEEE.

- [26] Huang, J., Lou, J., Vanavasam, S., Kong, X., et al. (2024, June). Hal: Hardware-assisted load balancing for energy-efficient snichost cooperative computing. In 2024 ACM/IEEE 51st Annual Int. Symp. on Computer Architecture (ISCA) (pp. 613-627). IEEE.

- [27] Di Girolamo, S., De Sensi, D., Taranov, K., Malesevic, M., et al. (2022, November). Building blocks for network-accelerated distributed file systems. In SC22: Int. Conf. for High Performance Computing, Networking, Storage and Analysis (pp. 1-14). IEEE.

- [28] Basu, S. and Nadig, D. (2024, June). Offloading NVMe over fabrics (NVMe-oF) to SmartNICs on an at-scale distributed testbed. In IEEE 10th Int. Conf. on Network Softwarization (NetSoft) (pp. 316-318). IEEE.

- [29] Jain, A., Alnaasan, N., Shafi, A., Subramoni, H. and Panda, D. (2021, August). Accelerating CPU-based distributed DNN training on modern HPC clusters using bluefield-2 DPUs. In 2021 IEEE Symposium on High-Performance Interconnects (HOTI) (pp. 17-24). IEEE.

- [30] Jain, A., Alnaasan, N., Shafi, A., Subramoni, H. and Panda, D. (2021). Optimizing distributed DNN Training using CPUs and Bluefield-2 DPUs. IEEE Micro, 42(2), 53-60.

- [31] Upadhyay, G., Prasad, C., Akash, V., Singh, A., et al. (2024, August). Enhancing CNN Inference Time and Reducing Latency on Edge and Resource-Constrained Systems through Quantization. In 2024 Second Int. Conf. on Networks, Multimedia and Information Technology (NMITCON) (pp. 1-6). IEEE.

- [32] Gongye, C. and Fei, Y. (2024, May). One Flip Away from Chaos: Unraveling Single Points of Failure in Quantized DNNs. Int. Symp. on Hardware Oriented Security and Trust (HOST) (pp. 332-342). IEEE.

- [33] Jeong, T., Ghasemi, E., Tuyls, J., Delaye, E. and Sirasao, A. (2020, December). Neural network pruning and hardware acceleration. In IEEE/ACM 13th Int. Conf. on Utility and Cloud Computing (UCC) (pp. 440-445). IEEE.

- [34] Vicenzi, J., Korol, G., Jordan, M., Rutzig, M. and Beck, A. (2024, August). Exploiting Virtual Layers and Pruning for FPGA-Based Adaptive Traffic Classification. In 2024 27th Euromicro Conf. on Digital System Design (DSD) (pp. 194-201). IEEE.

- [35] Wang, J., Lv, G., Liu, Z. and Yang, X. (2022, September). QUIC encryption offloading based on NanoBPF. In 23rd Asia-Pacific Network Operations and Management Symposium (APNOMS) (pp. 1-4). IEEE.

- [36] AMD (n.d.) AMD Vivado Design Suite 2024.2 release now available including major enhancements for designing with AMD Versal TM adaptive SoCs. https://www.amd.com/en/products/software/adaptive-socs-and-fpgas/vivado.html

- [37] Hoefler, T., Di Girolamo, S., Taranov, K., Grant, R. and Brightwell, R. (2017, November). sPIN: High-performance streaming Processing in the Network. In Proceedings of the Int. Conf. for High Performance Computing, Networking, Storage and Analysis (pp. 1-16).