# On the Challenges of Energy-Efficiency Analysis in HPC Systems: Evaluating Synthetic Benchmarks and Gromacs

Rafael Ravedutti Lucio Machado

Erlangen National High Performance Computing Center Erlangen, Bavaria, Germany rafael.r.ravedutti@fau.de

# Georg Hager

Erlangen National High Performance Computing Center Erlangen, Bavaria, Germany georg.hager@fau.de

# **Abstract**

This paper discusses the challenges encountered when analyzing the energy efficiency of synthetic benchmarks and the Gromacs package on the Fritz and Alex HPC clusters. Experiments were conducted using MPI parallelism on full sockets of Intel Ice Lake and Sapphire Rapids CPUs, as well as Nvidia A40 and A100 GPUs. The metrics and measurements obtained with the Likwid and Nvidia profiling tools are presented, along with the results. The challenges and pitfalls encountered during experimentation and analysis are revealed and discussed. Best practices for future energy efficiency analysis studies are suggested.

### **Keywords**

HPC, energy efficiency, profiling, molecular dynamics, challenges, best practices

#### **ACM Reference Format:**

#### 1 Introduction

High-performance computing (HPC) systems are essential for advancing research and solving complex problems in many fields, such as molecular dynamics, biomedical simulations, and artificial intelligence. However, the growing scale and complexity of modern HPC infrastructures has led to a significant increase in energy consumption, creating challenges in terms of cost, sustainability, and system reliability. As energy becomes a limiting factor in system scalability and efficiency, it is increasingly important to conduct a comprehensive energy analysis.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

Conference acronym 'XX, Woodstock, NY

Jan Eitzinger

Erlangen National High Performance Computing Center Erlangen, Bavaria, Germany jan.eitzinger@fau.de

#### Gerhard Wellein

Erlangen National High Performance Computing Center Erlangen, Bavaria, Germany gerhard.wellein@fau.de

This paper evaluates various aspects of conducting research experiments on HPC energy efficiency analysis. It examines the power usage of synthetic benchmarks and real application codes to understand the practical differences between them and to demonstrate how simple benchmarks can be useful to understand the energy and performance characteristics of modern architectures. Gromacs [9], a molecular dynamics package with a primary focus on life-science simulations, is used as a real-world application. This software is renowned for its high performance on HPC systems comprising both CPUs and GPUs. The MD-Bench [10] prototyping harness for MD simulations is used as an additional benchmark. It contains short-range force calculation kernel implementations that use the Cluster Pair data structure introduced by Gromacs to exploit optimal SIMD usage on modern CPUs and GPUs.

The experiments were conducted on two clusters: the *Fritz* cluster, which consists of Intel Ice Lake (ICX) and Sapphire Rapids (SPR) nodes, and the *Alex* cluster, which consists of nodes with Nvidia A40 and A100 GPUs. The objectives are to (a) understand how different settings, such as power-capping limits and frequency, affect performance and energy efficiency in various simulation scenarios and hardware, and (b) share the insights gained from this systematic study and explain how performance metrics can be presented for a meaningful energy efficiency analysis.

Section 1.1 displays related work on the analysis of energy consumption and efficiency of HPC applications. Section 2 provides a theoretical background on Gromacs and the performance monitoring tools utilized in this work. Section 4 displays the challenges and results from our measurements, as well as a discussion on the pitfalls when doing research on performance and energy efficiency analysis on HPC systems. Finally, Section 5 provides the conclusions and outlines of this work.

#### 1.1 Related Work

As power constraints increasingly limit scalability in HPC systems, energy efficiency analysis at the application level has gained significant attention. Although some research focuses on system-level optimizations and power management techniques, such as DVFS [1, 5, 15] and power capping [4, 7, 13], with little focus on specific applications and hardware, many studies focus on understanding and improving the energy behavior of scientific applications themselves on specific machines. Analysis at the application level for a specific hardware is crucial because energy consumption is determined

by hardware characteristics, algorithmic choices, communication patterns, and computational intensity.

Several studies have examined the energy-to-solution and performance trade-offs of representative scientific workloads, including molecular dynamics [11], computational fluid dynamics [2], and numerical linear algebra [8, 12]. These studies often use measurement frameworks such as Likwid, Intel RAPL, or NVIDIA's NVML to collect power and performance metrics with high granularity. By correlating these measurements with computational phases (i.e. force calculations, solver steps, or communication regions), researchers can identify the code sections that are responsible for the majority of energy consumption and then evaluate whether these can be improved.

In addition to the correlation and characterization of the energy and power consumption of one or more applications, there are studies that focus on providing analytic models to predict the performance and energy consumption of modern multi-core processors as a function of relevant parameters, such as frequencies and the number of active cores [3, 6]. These studies must be validated through synthetic benchmarks and real-world applications. Therefore, using a consistent methodology can help identify and overcome obstacles.

# 2 Background and Theory

#### 2.1 Gromacs

Gromacs is an open-source molecular dynamics simulation package designed to simulate systems at the atomic level, particularly biomolecular systems. It implements advanced integrators and constraint solvers, as well as algorithms for treating long-range interactions, such as the Particle-Mesh Ewald method. It also provides data structures for efficiently computing short-range atomic forces. Its popularity comes from its combination of numerical accuracy, high efficiency, and portability across a range of hardware platforms.

Performance optimization has been a central objective throughout the development of Gromacs. The software exploits multiple levels of parallelism, including SIMD vectorization, OpenMP threading, MPI distribution, and GPU acceleration. Its hybrid parallelization strategy enables efficient use of heterogeneous architectures ranging from desktop workstations to top supercomputers. A distinctive feature of Gromacs parallelization is the separation of tasks between particle-particle (PP) computations, which dominate short-range force calculations, and PME computations for long-range electrostatics. Dedicated MPI ranks can be assigned exclusively to PME, while others focus on PP, reducing the cost and overhead from communication (MPI reductions from the PME algorithm only need to be done for dedicated PME ranks) and improving scalability on large systems. Combined with domain decomposition and dynamic load balancing, this strategy allows Gromacs to efficiently simulate systems with millions of atoms and to maintain high parallel efficiency on thousands of cores.

A key optimization in Gromacs for short-range non-bonded interactions is the Cluster Pair (CP) algorithm. Instead of evaluating forces between individual particle pairs, particles are grouped into small spatial clusters (typically containing 4–8 atoms), and all interactions between two such clusters are computed in a single operation. This design improves data locality, reduces branching, and

enables efficient use of SIMD vectorization on modern CPUs as well as massive parallelism on GPUs. In contrast, other MD packages rely primarily on Verlet neighbor-lists, where each atom maintains a list of neighbors within a cutoff distance (plus a buffer). While Verlet lists are conceptually simple and robust, they lead to irregular memory access patterns and often result in less efficient use of SIMD units, since they require the usage of gather instructions. The CP algorithm can be seen as an extension of the Verlet approach, since it also relies on neighbor searching, but it organizes the neighbor list at the cluster level rather than per atom. Besides, it also stores atom properties (such as positions, velocities and forces) in an array-of-struct-of-arrays (AoSoA) layout, where data from atoms in the same cluster is contiguous in memory and can be loaded into the vector registers without gather instructions. This reduces memory bandwidth requirements and also increases the arithmetic intensity by reusing loaded data for multiple pairwise computations. However, there is a significant increase in the number of redundant computations in contrast to the Verlet lists because interactions are evaluated for all pair of atoms in the two clusters during the force calculation kernel. When combined with domain decomposition and dynamic load balancing, the CP algorithm contributes significantly to the strong performance and scalability of Gromacs compared to other MD packages.

As high-performance computing (HPC) systems scale toward exascale, energy efficiency has become as important as raw throughput. MD simulations, particularly with codes like Gromacs, are computationally intensive and often run for extended time scales, leading to significant energy consumption. Studying the energy efficiency of Gromacs provides valuable insights into how different computational phases (e.g., PP vs. PME kernels) and hardware resources (CPU vs. GPU, network communication) contribute to the overall energy footprint. Such analyses help identify bottlenecks where energy use is disproportionate to performance gains, guiding both software optimization and hardware utilization strategies. From a practical perspective, energy-to-solution is increasingly relevant for users and HPC centers alike, as it directly impacts operational costs and the sustainability of large-scale scientific computing. Understanding and optimizing energy efficiency in Gromacs therefore supports not only scientific productivity but also the broader goals of green HPC and responsible resource usage.

#### 2.2 Synthetic Benchmarks

2.2.1 MD-Bench. MD-Bench is a performance-oriented prototyping harness implemented in C99 that comprises the most essential MD steps to calculate trajectories in an atomic-scale system. It contributes clean reference implementations of state-of-the-art MD optimization schemes from multiple community codes. Since MD-Bench contains kernels that compute short-range atomic forces using the same Cluster Pair algorithm strategy from Gromacs, it can be utilized to approach performance and energy efficiency studies with Gromacs. Kernel variants have been implemented for full (FN) and half (HN) neighbor lists. The former stores each pair of interacting atoms twice (in both the *i-j* and *j-i* directions) and reduces forces for only one atom. The latter case, which is also used by Gromacs, stores atom pair interactions only once (in the *i-j* direction) when the forces are symmetric. Using half-neighbor

lists reduces computation and data loads by roughly a factor of two but introduces gather and scatter operations to reduce forces in the j-atom; it also requires atomic operations when using shared-memory parallelism.

2.2.2 Stream. The **STREAM** benchmark family measures sustainable memory bandwidth and corresponding computation rates for simple vector kernels that are representative of many memory-bound scientific applications. In this work, we use the triad kernel, which computes  $A[i] = B[i] + \alpha \cdot C[i]$  for single-precision floating-point arrays A, B, C of size N.

2.2.3 GEMM. The GEMM (General Matrix Multiply) benchmark computes dense matrix multiplications of the form  $C = \alpha AB + \beta C$ . There are optimized implementations of the benchmark in libraries such as cuBLAS and Intel MKL, and these are well-known representative scenarios for assessing instruction throughput bound applications on both CPUs and GPUs. The benchmarks are usually referred to as **SGEMM** and **DGEMM**, where the former works on single 32-bit floating-point precision and the latter on double 64-bit floating-point precision. Although modern GPU implementations can use Tensor Cores to achieve higher performance throughput, it was decided not to use them, as they are tailored for matrix multiplication workloads, unlike Gromacs. Instead, we stressed the CUDA cores.

#### 3 Materials and Methods

Table 1 lists the CPU and GPU processors used in this work and displays their relevant settings. Experiments were conducted on two Intel CPUs available in the Fritz cluster: an Intel Sapphire Rapids system and an Intel Ice Lake system. For GPU experiments, two different GPU models available in our Alex cluster were used: an A40 and an A100, both featuring the Ampere architecture. For each node in the Alex cluster, 8 units of the respective GPUs are present together with 2 AMD EPYC 7713 ("Milan", "Zen3") CPUs, each with 2 x 64 cores at 2.0 GHz base clock frequency. Each node in the Alex cluster has 8 of the respective GPUs together with 2 AMD EPYC 7713 ("Milan", "Zen3") CPUs, each with 2 x 64 cores at a base clock frequency of 2.0 GHz. While some of the Gromacs phases run on the CPU in a hybrid setting, the heavy computational workloads, such as the PP and PME kernels, are offloaded to the GPU. Therefore, our analysis is performed exclusively on the GPUs in this work.

The LIKWID software [14] was utilized to pin tasks for specific cores and measure HPM counter metrics. The configuration of the CPU frequency settings is facilitated by the SLURM option –cpufreq in conjunction with the performance governor, a configuration that ensures the continuous operation of the CPU at its maximum frequency capacity. In the context of GPUs, the nvidia-smi tool is employed to modify the frequency and power capping settings. This is achieved by utilizing the set-applications-clock and power-limit options, respectively.

The Gromacs 2023.4 version was used and built from the repository to include the proper Likwid instrumentation markers in the code. For this, the ICX 2023.2.0.20230721 compiler was used with the Intel MPI 2021.7.0 and Intel MKL 2023.2.0 modules. In the

GPU systems, the module *gromacs/2023.3-gcc11.2.0-openmpi-mkl-cuda*, which indicates that Gromacs 2023.3 compiled with the GCC 11.2.0 compiler was used. Although many other Gromacs test cases were evaluated, this study covers the ones that showed the most interesting results and did enough work to avoid major impacts caused by the overhead. The benchmarks were selected from a list of representative cases<sup>1</sup>:

- **B4:** a protein in explicit water (170,320 atoms)

- B5: a protein membrane channel with explicit water (615,924 atoms)

Both benchmarks were executed for a duration of 200,000 time steps, with the majority of cases continuing for more than 10 minutes to ensure the accurate rendering of energy and power consumption behaviors.

In the context of MD-Bench, the standard Copper Lattice simulation is employed, encompassing 128³ unit cells (8.388.608 atoms), a cutoff radius of 4.0 and a "skin" of 0.5 over a duration of 10,000 time steps. Since the MD-Bench GPU implementation still has nonoptimal performance for building the neighbor-lists, MD-Bench is only used on CPU systems.

# 4 Challenges and best practices

# 4.1 Meaningful energy and performance profiling

Without the ability to accurately measure hardware metrics, energy studies are impossible. Key issues include which metrics are available, the scope of the measurements, the overhead introduced, and the minimum sampling rate at which metric values are updated at hardware level.

With Gromacs the process of profiling can result in the introduction of a substantial overhead, primarily due to the fine-grained nature of its computational phases and the significantly short runtime of each simulation timestep. For instance, when utilizing the two SPR sockets (104 threads) at a fixed frequency of 2.0 GHz, the runtime of the non-bonded force computation kernel per timestep is approximately  $10^{-3}$ s. Due to the short execution time of each step, even minor overhead can significantly impact the accuracy of measurements performed at the kernel level.

For this reason, the use of Likwid instrumentation markers is limited in this situation. These markers trigger system calls, which significantly increase runtime and alter the overall characteristics of the code, since more time is spent on instrumentation than on the actual measured code. In addition, the RAPL counters, which are used most often, usually have a low update frequency, which further influences the results for very small regions.

It is still possible to use instrumentation for metrics that are not sensitive to time or other types of profiling noise. Examples include total and arithmetic instructions. Table 2 displays data on single-precision floating-point arithmetic instructions for the Gromacs test-case B5, which was collected using Likwid instrumentation on the PP and PME kernels. It is even possible to estimate the performance in Tflop/s for each region by using the runtime from a plain, non-instrumented run. It is evident that PP kernels utilize significantly more compute units than PME phases. There are a

| Model                     | Xeon Platinum 8470         | Xeon Platinum 8360Y A40       |              | A100                         |

|---------------------------|----------------------------|-------------------------------|--------------|------------------------------|

| Micro-architecture        | Sapphire Rapids (SPR)      | Ice Lake server (ICX) Ampere  |              | Ampere                       |

| Base frequency            | 2.0 GHz                    | 2.4 GHz                       | 1.065 GHz    | 1.305 GHz                    |

| Boost clock               | 3.8 GHz                    | 3.4 GHz                       | 1.410 GHz    | 1.740 GHz                    |

| Memory clock              | _                          | _                             | 1.512 GHz    | 1.812 GHz                    |

| Cores/SMs per chip        | 52                         | 36                            | 84           | 108                          |

| Latest SIMD extension     | AVX512                     | AVX512                        | _            | _                            |

| TDP                       | 350W                       | 250W                          | 300W         | 400W                         |

| L1D capacity              | $52 \times 48  \text{KiB}$ | 36 × 48 KiB                   | 84 × 128 KiB | $108 \times 192  \text{KiB}$ |

| L2 capacity               | $52 \times 2 \text{ MiB}$  | $36 \times 1.25 \mathrm{MiB}$ | 6 MiB        | 80 MiB                       |

| L3 capacity               | 105 MiB                    | 54 MiB                        | _            | _                            |

| Memory configuration      | 6 ch. DDR4-2933            | 8 ch. DDR4-3200               | _            | _                            |

| Memory size               | _                          | _                             | 48 GiB       | 80 GiB                       |

| Peak FP32 Perf. (TFLOP/s) | 6.656                      | 5.529                         | 37.42        | 19.49                        |

| Peak Bandwidth            | _                          | _                             | 695.8 GB/s   | 1.94 TB/s                    |

Table 1: Specifications for testbed processors used.

| Kernel/Architecture     | PP/SPR                 | PP/ICX36               | PME/SPR                | PME/ICX                |

|-------------------------|------------------------|------------------------|------------------------|------------------------|

| Runtime@base_freq (s)   | 3470.811               | 6439.544               | 1481.100               | 3837.322               |

| Number of ranks         | 40                     | 30                     | 12                     | 6                      |

| Wait time (s)           | _                      | _                      | 2332.901               | 3415.535               |

| Giga cycles (%)         | 70.0                   | 9.0 + 14.1 (wait)      | 74.0                   | 8.8 + 7.8 (wait)       |

| All Instr               | $6.732 \times 10^{14}$ | $6.717 \times 10^{14}$ | $1.208 \times 10^{14}$ | $1.005 \times 10^{14}$ |

| FP32 Instr. AVX512      | $4.468 \times 10^{14}$ | $4.440 \times 10^{14}$ | $9.328 \times 10^{12}$ | $9.328 \times 10^{12}$ |

| FP32 Instr. AVX2        | $1.676 \times 10^{13}$ | $1.664 \times 10^{13}$ | $1.200 \times 10^{5}$  | $6.000 \times 10^4$    |

| FP32 Instr. SSE         | $1.782 \times 10^{12}$ | $1.785 \times 10^{12}$ | $8.618 \times 10^{12}$ | $8.618 \times 10^{12}$ |

| FP32 Instr. Scalar      | $2.130 \times 10^{12}$ | $2.121 \times 10^{12}$ | $1.051 \times 10^{13}$ | $9.903 \times 10^{12}$ |

| Arith. Instr. Ratio (%) | 69.43                  | 69.15                  | 23.55                  | 27.72                  |

| Estimated TFLOPS/s      | 2.1                    | 1.125                  | 0.131                  | 0.05                   |

| Theoretical peak@nranks | 5.12                   | 4.6                    | 1.53                   | 0.92                   |

Table 2: Performance and instruction metrics for PP and PME configurations on SPR and ICX systems.

substantial number of instructions for all SIMD sets, indicating the reduction of values within SIMD registers, such as the computed forces. Approximately 70% of the instructions are for arithmetic computation. The PME ranks spent a significant amount of time and cycles waiting for other ranks to complete, and only about 20-30% of the instructions are arithmetic. This is already valuable information which can be obtained via instrumentation despite the limitations described.

An alternative to instrumentation is to use the Linux *perf\_events* tool and perform sampling. This should provide less overhead since *perf\_events* operates directly in the kernel and sampling can be adjusted to a frequency that leads to less overhead. However, issues were encountered when using this approach with Gromacs:

- Overhead still significant: Despite utilizing a sampling frequency as low as 99 Hz, a 20-30% overhead is observed in the context of floating-point arithmetic and clock-related events.

- Large volume of data produced: For a single execution of a modest Gromacs benchmark, an aggregate of 28–40 GB of data is obtained from the *perf\_events* trace. This issue can be resolved by adjusting specific options and omitting sampling

- of the entire simulation. However, this remains a concern when executing multiple benchmarks and diverse scenarios.

- Sampling of energy events not possible: Energy events are counted per socket, hence when performing function-level profiling at the hardware threads level, the kernel cannot refer back from the socket energy to the contribution of each function call by the threads; This means that it is not possible to sample functions when events are counted per socket when using <code>perf\_events</code>.

- Inaccuracies with coarser, low-frequency sampling: Since Gromacs computational phases run for a very short amount of time, sampling at larger frequencies can provide misleading results as the number of samples per function execution is not significant enough; Even sampling at a 99Hz frequency, we already face significant overhead, so determining a frequency that can at the same time provide negligible overhead and provide statistically sound results has shown to be an obstacle for our case.

Due to the challenges and pitfalls of finer-granularity profiling, end-to-end measurements were chosen as an alternative for power, energy, and clock frequency metrics. While certain assumptions can be made, it is evident that it is not possible to determine the performance and energy characteristics of each individual kernel based on the counted events. Although this paper does not focus on HPM overhead evaluation or the capabilities and user-friendliness of HPM facilities, it is important to acknowledge that the situation has deteriorated considerably in recent years. Fine-grained, end-toend measurements are impossible due to the overhead introduced by recent hardware security mitigations in operating system kernels and processor firmware. HPM implementations on the CPU side are becoming more complicated, requiring more accesses and therefore system calls, which further contributes to large overheads. Finally, some chip vendors still do not regard HPM metrics as important core product features. For example, counters such as the Uncore clock ticks on Sapphire Rapids disappear between CPU generations, and no responsibility is taken for counter accuracy in general. As a workaround clock tick counters from the interfaces between the mesh and the Intel UPI link layer (M3UPI) and between the mesh and each IIO stack (M2PCIE) can be used on Sapphire Rapids to estimate the Uncore frequency.

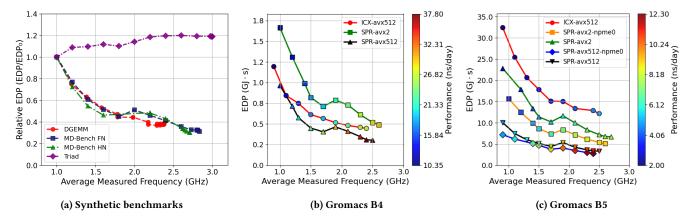

Another interesting approach to handle these limitations is the use of specific benchmark codes that resemble the original application. One example for MD workloads is MD-Bench, which contains several implementations of such kernels using different strategies. Synthetic benchmarks like DGEMM and Triad can also be used to understand how the runtime and energy behavior of the target machine behaves in situations where specific resources such as the compute units or the memory bandwidth are fully utilized. Figure 1 displays the Energy-Delay-Product (EDP) versus the measured frequency for synthetic benchmarks and for different Gromacs testcases. The best EDP case for Triad (memory-bound) occurs at the minimum frequency. For DGEMM, MD-Bench, and Gromacs, the EDP improves as the core frequency increases. The only exceptions occur when the base frequency is reached, at which point a leap in EDP can be seen.

As expected, the EDP behavior is similar for both MD-Bench and Gromacs. This reinforces that MD-Bench can be used for energy efficiency studies to have a better understanding of how MD codes behave with respect to performance and energy consumption; at the same time, it presents options that allow one to control the runtime execution for each phase and other parameters that affect its behavior (e.g. FN vs HN). In such situations, it is important to investigate how transferable the knowledge obtained with the proxy application is. This can be done by evaluating it against different scenarios with the real production code.

# 4.2 Application specific influences on the example of Gromacs

The performance and energy consumption of Gromacs are also affected by the choice of PP/PME rank decomposition. In our case, a set of MPI ranks, which correspond to specific CPU cores, is selected to compute long-range interactions using the PME algorithm, while the rest are used to compute short-range or particle-particle interactions. If not specified via parameters, Gromacs sets the number of ranks reserved for PME computations based on heuristics, hardware, and simulation settings. Not all settings are valid for the number of PME ranks. For example, on test-case B4 it is not possible

to use all ranks for PP and PME (i.e. setting npme to zero) on the full SPR socket due to the lack of a valid domain decomposition with 52 ranks

Allocating too few PME ranks can cause long-range computations to become a bottleneck, which limits parallel efficiency and increases time to solution. Conversely, assigning too many PME ranks reduces the number of ranks available for short-range computations and increases communication overhead between the PP and PME domains. Additionally, PME computation requires global synchronization between ranks, meaning that the communication cost is proportional to the number of ranks assigned to PME.

These decisions not only affect execution time but also alter the power distribution across compute nodes. For instance, heavily loaded PP ranks often run at higher frequency and power levels, whereas PME ranks are more communication-bound and power-efficient. Consequently, when conducting performance or energy studies, it is essential to understand the types of parallelism employed in the target applications and to analyze specific ranks or threads to see whether their behavior varies significantly. In this work, this is only addressed for the CPU experiments since no multi-GPU experiments were performed, and both PP and PME computations were offloaded to the single GPU.

In Figure 1b and Figure 1c it is possible to observe that the different benchmarks exhibit different characteristics with respect to EDP on different architectures. For test-case B4, the best EDP is achieved with AVX512 instructions on both SPR and ICX. However, for B5, all SPR runs (even those using AVX2 instructions) have a lower EDP than ICX runs using AVX512 instructions. Allocating all ranks to compute both PP and PME provides a lower EDP for B5, but as previously mentioned, this setting is not possible for B4 on SPR. It is worth noting that the outcome may differ when running with more MPI ranks and resources. Allocating more ranks for PME can lead to higher communication costs, which can worsen the EDP due to the impact of global reductions on performance.

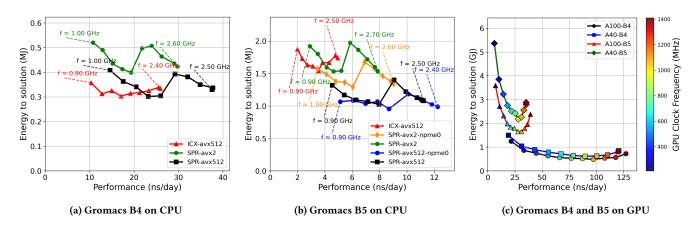

For a more detailed overview of EDP behavior, Figure 2a and Figure 2b display the energy-to-solution versus performance for the same cases when running at different frequencies. For test-case B4, the ICX version has worse performance at the highest frequencies than the AVX2 run on SPR. However, this is compensated for by the lower energy consumption. All AVX512 SPR cases perform better and consume less energy than their AVX2 counterparts. The effect is the same when all ranks are allocated to compute both the PP and PME phases.

In Figure 2c the results for both benchmarks on the A40 and A100 GPUs. The behavior matches the expectations [6] where a minimum energy-to-solution is achieved when running at about 1.0 GHz before it starts to increase at higher frequencies. Note that although the B4 curve looks more pronounced, this is actually caused by the energy-to-solution and performance scale. The general behavior is similar in both cases. Even though the A100 GPU has lower FP32 peak performance than the A40 GPU, Gromacs still runs on the A100 with slightly better performance. This means that other factors, such as higher bandwidth and performance for other data types, compensate for the fewer FP32 units available.

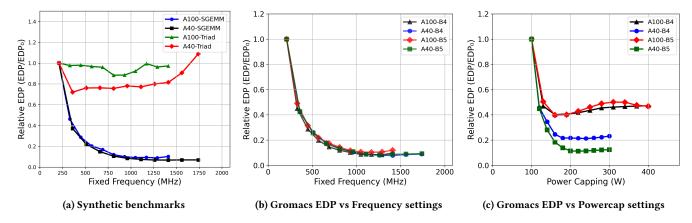

Figure 3b displays EDP versus fixed frequency for both SGEMM and Triad benchmarks, and Figure 3b displays the same plot for the Gromacs benchmarks. Both cases with a high computational

Figure 1: EDP versus measured frequencies for synthetic benchmarks on Sapphire Rapids and Gromacs (both Sapphire Rapids and Ice Lake). For Figure (a) with the synthetic benchmarks, the EDP is normalized. The marker colors represent the performance obtained on the Gromacs benchmarks in ns/day.

Figure 2: Z-plot showing the energy-to-solution versus performance when running different Gromacs benchmarks at different frequencies (measured) on both CPUs and GPUs. The marker colors on the Figure (c) represent the GPU graphics frequency setting.

workload reveal similar EDP behavior. There is a significant improvement from the minimum frequency to the base frequency. Then, the EDP starts to increase slightly, showing that the relationship between performance and energy consumption remains nearly linear. Figure 3c shows the relative EDP versus power capping settings with Gromacs. The EDP behavior is similar at different scales and for the frequency setting, but the EDP improvement is relatively smaller for the A100 GPU compared to the A40. Since EDP is normalized, this effect is likely due to better EDP measurements with the lowest power capping setting for the A100 and for the B4 (which has a smaller workload than the B5) for the A40.

These experiments and discussions make it clear that studies on energy and performance analysis must consider several factors related to the application and the hardware on which it runs. It is important to avoid overgeneralized claims and remember that results may be limited to the utilized benchmark and hardware.

# 4.3 Affinity control

Affinity control, which restricts which physical cores, threads and tasks can run on, is critical for meaningful energy measurements. On some CPUs, energy can only be measured at socket level. Since the frequency of the cores depends on how many are active, it is important to use all the cores on a socket for energy measurements. In modern HPC systems, tools and runtime environments influence or restrict affinity settings at several levels. The SLURM scheduler can either put the user context into a restricted OS CPU set, or, when used as a startup mechanism for an MPI or hybrid MPI+OpenMP application, it can enforce affinity settings. Common MPI startup tools such as OpenMPI's mpirun and Intel MPI's mpiexec also support proprietary affinity control. Some profiling tools, such as the Likwid tools, also provide affinity control. Finally, the application itself can control its affinity. When it comes to benchmarking, it is important that the available tools are utilized properly and do not interfere with each other. Often, a dedicated test program that

Figure 3: EDP versus frequencies and powercap settings for synthetic benchmarks and Gromacs on A40 and A100 GPUs. For Figure (a) with the synthetic benchmarks, the EDP is normalized.

only determines and prints the actual affinity settings is required to check that the settings are working as expected and debug any issues.

For instance, in our experiments with Gromacs there are three possible layers of pinning/CPU binding: (a) SLURM, which limits the available amount of CPUs according to its setting, (b) Likwid, which pins threads and properly bind ranks to the available resources in the compute nodes, and (c) Gromacs, which has its own default pinning mechanisms for performance purposes.

In Figure 4c we illustrate the importance to ensure that ranks are properly mapped to a single socket. As shown it is possible that inconsistent pinning led to strange behaviors like the CPU frequency on SPR operating at higher core frequencies than the expected average when using the full socket (about 3.6GHz in some cases, where core frequencies usually should not exceed 2.6GHz). The reason for these higher frequencies is that since the socket was not fully utilized, the CPU cores could clock higher and therefore reach better performance even though the same number of tasks was used. The fact that the average power draw plateaus at the TDP value for a single socket makes the issue harder to detect.

To mitigate this, SLURM is configured to restrict the available CPU cores to the ones in the same socket and then execute **likwid-mpirun** wrapped up around the **srun** command, meaning that the only options for Likwid to pin are on the restricted sockets. Since Gromacs is able to identify external pinning and then refrain from actually perform the pinning, it did not interfere with the external affinity settings. It still might be important to evaluate different pinning strategies, since Gromacs can perform pinning using application knowledge and even dynamically change pinning behavior during program execution.

# 4.4 Control over chip settings

For energy studies, the ability to set power cap limits or explicitly enforce frequencies is essential. Unfortunately, the dynamic frequency scaling behavior of modern CPUs and GPUs means that these settings are treated as mere suggestions by the processor. Even the base frequency is not guaranteed on Intel CPUs when running hot SIMD instruction code. In studies, it is also important

to include the Turbo frequency range, as this often comprises more than a third of the available frequency range. Even in situations where a specific behavior is expected for a certain parameter, it is important to confirm this via measurements and to use the measurements instead of the expected setting, if possible. However, it is not uncommon for studies to show the set frequency rather than the actual measured values.

Figure 4 shows an example where displaying the average frequency can be elucidative: starting from the base frequencies of both architectures, the power draw already reaches and remains close to the TDP. However, we can see that the measured frequency increases slightly when the frequency setting is increased, even though the power remains roughly constant. This is because the uncore frequency of the CPU socket decreases slightly, providing some room for the CPU cores to clock higher. Consequently, the energy and power consumption are moderately shifted towards the cores when the frequency setting is higher. The energy-to-solution is decreased in both cases as can be seen in Figure 2a and Figure 4b corroborates that this actually provides some marginal benefits to both performance and energy consumption, which makes evident that for these Gromacs benchmarks the bottleneck is the CPU cores and not the other domains.

If only the specified frequency were shown in this example, it would not be possible to perceive this effect because one could simply assume that the frequency remains fixed during the final executions in turbo mode. While one could make this assumption based on the shorter runtime, it would still not be evident because the runtime is influenced by many other factors. Therefore, in most cases, it is more interesting to show the actual frequency measurement than the setting itself because any divergence between the two makes the latter deceptive. Note that measurements can also be misleading or even inaccurate in some cases, either due to the previously discussed overhead situation or simply because the measurement tool is unreliable. To mitigate this, it is recommended that measurements are validated against benchmarks where their values can be estimated, such as synthetic benchmarks, and that they are cross-validated with other measurement tools.

Figure 4: Average power draw versus measured frequencies for Gromacs on CPUs. Dotted lines show the measurements from uncore frequencies for each case. Figure (c) shows the measurements for cases in which the ranks are distributed between the two sockets.

# 4.5 Benchmarking methodology

A systematic and consistent benchmarking methodology is essential to achieve meaningful and predictable results. Most important is to have a clear idea of the expected results. Without this, subtle errors and incorrect measurements cannot be identified. This requires experience; if none is available, it is recommended that one asks other researchers for advice or find comparable results from others. More experiments using different tools or settings need to be conducted, particularly when the results are too good or bad, or if the shape of a plot contradicts the expectation, to build trust in the result. When a result is unexpected, it can be difficult to find an explanation for it. Additional experiments can either provide an explanation or reveal errors in previous measurements. Although an automated benchmarking script using batch jobs is convenient, consistent, and allows more data to be gathered, there are reasons to do benchmarking manually in an interactive session first. With automated measurements, there is a tendency to acquire more data than is required. Having too much data makes it more difficult to identify errors, since it is usually no longer possible to examine all of the raw results. While automated scripts are convenient, the turnaround time is often much slower since running all benchmarks can take hours. Although doing all steps by hand might seem tedious, issues are detected faster and more easily since they are not buried in complicated scripts, but rather occur right before your eyes. There is also direct feedback if something takes longer than expected. For example, one might use this feedback to detect a large profiling overhead. In this case, fixing and repeating the test case is a matter of minutes, and the turnaround time is much faster, especially if multiple attempts are necessary to get it right.

# 5 Conclusion

This paper discussed the challenges and pitfalls of conducting energy efficiency studies on real application codes for modern high-performance computing (HPC) systems. It showed measurements for Gromacs and MD-Bench, a molecular dynamics prototyping harness, as well as multiple synthetic benchmarks for CPUs and

GPUs. Meaningful energy measurements are difficult to produce due to the dynamic frequency scaling of modern processors, which depends on the number of utilized cores, code characteristics, processor specimens, and server environmental conditions. Mitigating this issue requires complete control of affinity settings and measurement and displaying the average frequency rather than the set properties. Due to the high overhead and low sampling frequencies of energy counters, as well as the general lack of support for HPM metrics, a thorough measurement strategy is necessary for accurate results. While RAPL counters enabled much energy-related research, it would be desirable to query additional data sources, such as on-board management chips or PSUs, more easily. The same applies to GPUs, for which measurements can only be performed using the tools and drivers of GPU vendors, which cannot be verified further. In this case, too, a standardized, open interface on the motherboard for GPU power draw would be beneficial. Due to the difficult environment and the many sources of error, it is recommended to not rely solely on an automated benchmark script since errors are difficult to detect in this case. In this context, developing a clear result expectation is important for validating and challenging the measured results.

# Acknowledgments

This work was funded by the German Federal Ministry of Research, Technology, and Space (BMFTR) under the funding program Hochund Höchstleistungsrechnen für das digitale Zeitalter 2021-2024 – Forschung und Investitionen zum High-Performance Computing, Call Richtlinie zur Förderung von Verbundprojekten auf dem Gebiet des energieeffizienten High-Performance Computings (GreenHPC) as part of the EE-HPC project (Grant 16ME0583K).

# References

- [1] Jiawei Geng, Zongwei Zhu, Weihong Liu, Xuehai Zhou, and Boyu Li. 2024. PowerLens: An Adaptive DVFS Framework for Optimizing Energy Efficiency in Deep Neural Networks. In Proceedings of the 61st ACM/IEEE Design Automation Conference (San Francisco, CA, USA) (DAC '24). Association for Computing Machinery, New York, NY, USA, Article 228, 6 pages. doi:10.1145/3649329.3655956

- [2] Dominik Göddeke, Dimitri Komatitsch, Markus Geveler, Dirk Ribbrock, Nikola Rajovic, Nikola Puzovic, and Alex Ramirez. 2013. Energy efficiency vs. performance

- of the numerical solution of PDEs: An application study on a low-power ARM-based cluster.  $J.\ Comput.\ Phys.\ 237$  (2013), 132–150. doi:10.1016/j.jcp.2012.11.031

- [3] Georg Hager, Jan Treibig, Johannes Habich, and Gerhard Wellein. 2016. Exploring performance and power properties of modern multi-core chips via simple machine models. Concurrency and computation: practice and experience 28, 2 (2016), 189–210. doi:10.1002/cpe.3180

- [4] Azzam Haidar, Heike Jagode, Phil Vaccaro, Asim YarKhan, Stanimire Tomov, and Jack Dongarra. 2019. Investigating power capping toward energy-efficient scientific applications. Concurrency and Computation: Practice and Experience 31, 6 (2019), e4485. arXiv:https://onlinelibrary.wiley.com/doi/pdf/10.1002/cpe.4485 doi:10.1002/cpe.4485 e4485 cpe.4485.

- [5] Yunchu Han, Zhaojun Nan, Sheng Zhou, and Zhisheng Niu. 2025. DVFS-Aware DNN Inference on GPUs: Latency Modeling and Performance Analysis. In ICC 2025 - IEEE International Conference on Communications. 1274–1279. doi:10.1109/ ICC52391.2025.11161883

- [6] Johannes Hofmann, Georg Hager, and Dietmar Fey. 2018. On the Accuracy and Usefulness of Analytic Energy Models for Contemporary Multicore Processors. In *High Performance Computing*, Rio Yokota, Michèle Weiland, David Keyes, and Carsten Trinitis (Eds.). Springer International Publishing, Cham, 22–43. doi:10.1007/978-3-319-92040-5\_2

- [7] Adam Krzywaniak and Paweł Czarnul. 2020. Performance/Energy Aware Optimization of Parallel Applications on GPUs Under Power Capping. In Parallel Processing and Applied Mathematics, Roman Wyrzykowski, Ewa Deelman, Jack Dongarra, and Konrad Karczewski (Eds.). Springer International Publishing, Cham, 123–133.

- [8] João Vicente Ferreira Lima, Issam Raïs, Laurent Lefèvre, and Thierry Gautier. 2019. Performance and energy analysis of OpenMP runtime systems with dense linear algebra algorithms. The International Journal of High Performance Computing Applications 33, 3 (2019), 431–443. arXiv:https://doi.org/10.1177/1094342018792079 doi:10.1177/1094342018792079

- [9] Erik Lindahl, Berk Hess, and David van der Spoel. 2023. GROMACS 2023: Efficient, flexible, and reproducible molecular dynamics. *Journal of Chemical Theory and Computation* 19, 1 (2023), 475–487.

- [10] Rafael Ravedutti Lucio Machado, Jan Eitzinger, Jan Laukemann, Georg Hager, Harald Köstler, and Gerhard Wellein. 2023. MD-Bench: A performance-focused prototyping harness for state-of-the-art short-range molecular dynamics algorithms. Future Generation Computer Systems 149 (2023), 25–38. doi:10.1016/j. future.2023.06.023

- [11] Marco Savioli, Paolo Calligari, Ugo Locatelli, and Gianfranco Bocchinfuso. 2025. GROMODEX: Optimisation of GROMACS Performance through a Design of Experiment Approach. bioRxiv (2025). arXiv:https://www.biorxiv.org/content/early/2025/10/08/2025.10.08.681202.full.pdf doi:10.1101/2025.10.08.681202

- [12] Li Tan, Shashank Kothapalli, Longxiang Chen, Omar Hussaini, Ryan Bissiri, and Zizhong Chen. 2014. A survey of power and energy efficient techniques for high performance numerical linear algebra operations. *Parallel Comput.* 40, 10 (2014), 559–573. doi:10.1016/j.parco.2014.09.001

- [13] C. Terboven, R. Liem, J. Gracia, K. Haldar, J.F. Engels, P. Giesselmann, D. Brayford, T. Wilde, C. Simmendinger, M. Marquardt, J. Eitzinger, and T. Gruber. 2024. EE-HPC a Framework for Energy Efficient HPC System Management. In SC24-W: Workshops of the International Conference for High Performance Computing, Networking, Storage and Analysis. 1878–1882. doi:10.1109/SCW63240.2024.00236

- [14] Jan Treibig, Georg Hager, and Gerhard Wellein. 2010. LIKWID: A Lightweight Performance-Oriented Tool Suite for x86 Multicore Environments. In 2012 41st International Conference on Parallel Processing Workshops. IEEE Computer Society, Los Alamitos, CA, USA, 207–216. doi:10.1109/ICPPW.2010.38

- [15] Anna Yue, Pen-Chung Yew, and Sanyam Mehta. 2025. EVeREST: An Effective and Versatile Runtime Energy Saving Tool for GPUs. In Proceedings of the 30th ACM SIGPLAN Annual Symposium on Principles and Practice of Parallel Programming (Las Vegas, NV, USA) (PPoPP '25). Association for Computing Machinery, New York, NY, USA, 57–69. doi:10.1145/3710848.3710875