# SDQC: Distributed Quantum Computing Architecture Utilizing Entangled Ion Qubit Shuttling

Seunghyun Baek, <sup>1</sup> Seok-Hyung Lee, <sup>2,3,\*</sup> Dongmoon Min, <sup>2,4,†</sup> and Junki Kim<sup>1,2,‡</sup>

<sup>1</sup>Department of Nano Science and Technology & SKKU Advanced Institute of Nanotechnology (SAINT), Sungkyunkwan University, Suwon, 16419, Korea

<sup>2</sup>Department of Quantum Information Engineering, Sungkyunkwan University, Suwon 16419, Korea

<sup>3</sup>Centre for Engineered Quantum Systems, School of Physics,

The University of Sydney, Sydney, New South Wales 2006, Australia

<sup>4</sup>Department of Computer Science and Engineering, Sungkyunkwan University, Suwon, 16419, Korea

(Dated: December 3, 2025)

We propose Shuttling-based Distributed Quantum Computing (SDQC), a hybrid architecture that combines the strengths of physical qubit shuttling and distributed quantum computing to enable scalable trapped-ion quantum computing. SDQC performs non-local quantum operations by distributing entangled ion qubits via deterministic shuttling, combining the high-fidelity and deterministic operations of shuttling-based architectures with the parallelism and pipelining advantages of distributed quantum computing. We present (1) a practical architecture incorporating quantum error correction (QEC), (2) pipelining strategies to exploit parallelism in entanglement distribution and measurement, and (3) a performance evaluation in terms of logical error rate and clock speed. For a 256-bit elliptic-curve discrete logarithm problem (ECDLP) instance, which requires 2,871 logical qubits at code distance 13, SDQC achieves a logical error rate which is  $1.20^{+0.94}_{-0.45} \times 10^{-8}$  of Photonic DQC error rate and  $3.79^{+5.09}_{-2.84} \times 10^{-3}$  of Quantum Charge-Coupled Device (QCCD) error rate, while providing 2.82 times faster logical clock speed than QCCD.

#### I. INTRODUCTION

Quantum computing (QC) offers significant computational advantages over classical computing, with exponential speedups for specific problems such as prime factorization [1, 2] and quantum simulation [3]. These potential benefits have driven extensive efforts to build large-scale quantum systems. However, as the number of qubits increases, maintaining reliable performance becomes increasingly challenging due to the accumulation of noise and the complexity of control and communication [4]. This necessitates the design of scalable quantum architectures, systems that can grow in size, overcoming the compromise between fidelity and speed [5, 6]. Such architectures must also take into account the requirements of quantum error correction (QEC) [7, 8], which imposes structural and connectivity constraints on the physical lavout [9–11].

Trapped ion quantum computing [12] is one among the leading quantum computing platforms, and to realize a scalable architecture in trapped-ion quantum computing, two major approaches have been studied: photonic distributed quantum computing (DQC) [6] and the quantum charge-coupled device (QCCD) [5]. Photonic DQC enables non-local quantum operations by distributing entanglement pairs through ion-photon interfaces, allowing remote qubits to interact via gate teleportation [13–16] or quantum teleportation [17, 18]. QCCD, in

contrast, physically moves ion qubits using dynamically shaped electric potentials, supporting direct quantum state transfer and flexible all-to-all connectivity within a trap [5, 19–24]. While both approaches extend beyond the limitations of a single ion chain [25–29], they differ significantly in terms of communication latency, fidelity, and architectural complexity.

In this study, we propose a hybrid architecture, Shuttling-based Distributed Quantum Computing (SDQC), that combines the advantages of Photonic DQC and QCCD to enable scalable, high-fidelity non-local quantum operations. SDQC is structured as a multi-core system in which each core operates locally while communicating between cores through entangled ion qubits transported via deterministic shuttling. While QCCD moves qubits containing quantum data, directly affecting execution time, SDQC moves entanglement pairs without quantum data of quantum circuits during entanglement distribution. The architecture incorporates intercore communication protocols, pipelining to exploit parallelism, and a quantum error correction (QEC) model based on color codes [30, 31]. In the architecture assessment, we evaluate SDQC in comparison with Photonic DQC and QCCD in terms of gate execution time and logical error rate. We further assess application-level performance by estimating execution time and success rate for representative quantum algorithms with the Fermi-Hubbard model and Shor's algorithm.

The remainder of this paper is organized as follows. Section II provides background and motivation, including an overview of trapped-ion quantum computing, its scalability challenges, and the role of QEC. Section III introduces SDQC architecture in detail, covering the architectural model, QEC implementation, pipelining strategies,

<sup>\*</sup> seokhvunglee@skku.edu

<sup>†</sup> dongmoon.min@skku.edu

<sup>&</sup>lt;sup>‡</sup> junki.kim.q@skku.edu

and key properties. Section IV presents the evaluation methodology and results, focusing on time cost, logical error rates, and application performance, compared to other reference architectures.

### II. BACKGROUND AND MOTIVATION

# A. Trapped-ion QC

Trapped-ion quantum computing utilizes atomic ions as quantum information carriers [32], as shown in Fig. 1(a). The ions are spatially confined in ultrahigh vacuum (UHV) environments using electromagnetic potentials, and multiple ions naturally form a linear Coulomb crystal that shares quantized motional modes (phonons) [12, 33, 34]. The trapping potentials can be finely tuned by adjusting DC and RF voltages applied to the trap electrodes, which are often miniaturized to enable precise spatial control [23, 35].

Quantum information is encoded in the internal electronic states of atomic ions, which are naturally identical and highly stable. These well-isolated qubit states minimally interact with the environment, enabling coherence times exceeding one hour [36]. State discrimination is achieved via state-dependent fluorescence, which allows high-fidelity readout with state preparation and measurement (SPAM) errors as low as  $10^{-6}$  [37].

Qubit states are manipulated using external control fields either optical or microwave, and entangling operations are mediated by shared phonon modes, with a reported fidelity reaching 99.97(1) % [38, 39]. Individual optical addressing enables selective control over single ions in a chain, and programmable quantum operations with dozens of ion qubits have been demonstrated across multiple systems [40, 41]. Since the phononic mode is shared across all ions in the same chain, trapped-ion systems inherently provide all-to-all connectivity [41], in contrast to the limited interaction graphs of other qubit platforms.

Trapped-ion quantum computers exhibit high-fidelity qubit-level operations as well as strong system-level benchmarks [20, 41–43]. These capabilities have enabled proof-of-principle demonstrations of quantum error correction[44, 45] and experimental claims of quantum computational advantage over classical computing[46, 47].

# B. Scaling trapped-ion QC

To realize large-scale fault-tolerant quantum computation, approximately a few thousand logical qubits are required, with each logical qubit encoded using many physical qubits [48]. In trapped-ion systems, however, the number of physical qubits that can be accommodated in a single linear chain is limited to a few dozens, due to motional mode crowding and associated reduced gate perfor-

mance [25–29]. To address this limitation, two scalable architectural approaches have been proposed: Photonic DQC [6, 49–51] and QCCD [5, 19–24] architecture.

# 1. Photonic DQC

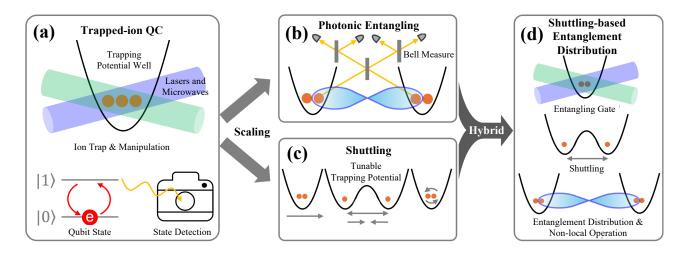

Photonic DQC extends trapped-ion QC by distributing and generating entanglement pairs between distant ion qubits using flying photonic qubits as shown in Fig. 1(b) [6, 49–51]. In this architecture, each ion chain operates as an independent module, and entangled pairs are generated via ion-photon interfaces that emit photons entangled with ion qubit states [15–18]. Bell state measurements are performed on photons from different modules using a beamsplitter and coincident detection, which, upon success, heralds entanglement pair generation between the remote ions [49, 50, 52–55]. Once entangled, the ion qubits can be used to implement non-local gates through a teleportation-based protocol involving local operation and classical communications (LOCC) [13–18].

Photonic DQC approach offers several architectural advantages for scaling trapped-ion qubits. First, it allows multiple modules to be interconnected, increasing the total number of qubits while enabling long-range connectivity across modules. These modules interact via distributed entanglements with photonic interfaces, without requiring physical interaction between data qubits in different modules. Entangled qubits can be prepared asynchronously and remain unentangled with data qubits until interaction, allowing for flexible scheduling in entanglement preparation [56, 57]. This enables pipelining, which can effectively eliminate the overhead associated with entanglement distribution.

However, realizing Photonic DQC in trapped-ion QC presents substantial experimental challenges. A primary challenge lies in the implementation of an efficient and reliable quantum interface between ion qubits and photonic qubits [58–60]. Current approaches typically rely on collecting spontaneously emitted photons via highnumerical-aperture objective lens, which inherently suffer from low success probabilities and limited process fidelity [58]. Photonic entanglement generation is a heralded process that is intrinsically probabilistic, often requiring tens of thousands of trials for a single successful event. These constraints result in a slow entanglement generation rate, with reported rates reaching only up to 250 Hz [58]. Moreover, the bulky and alignment-sensitive nature of current quantum interfaces poses a significant engineering barrier to scaling, particularly in the context of parallelizing remote entanglement generation across multiple modules.

Ion-photon quantum interfaces have been demonstrated using various photonic qubit encoding methods, including frequency [61], polarization [62], and time-bin encoding [58, 63], with gradual improvements in interface performance. Cavity quantum electrodynamics (QED) effects have also been employed to enhance ion-photon

FIG. 1. Trapped-ion QC and its scalable architectures. (a) In trapped-ion QC, ions are trapped in an electric potential well and form a Coulomb crystal that shares a motional mode. The quantum information is encoded into the electronic states of ions, which are manipulated by external fields such as lasers and microwaves and measured via state-dependent fluorescence. Two main architectures have been proposed for scaling trapped-ion quantum computing: (b) Photonic DQC and (c) QCCD. (b) In Photonic DQC, remote entanglement is generated by Bell-state measurements between photons scattered from ions located in separate modules, enabled by ion-photon interfaces. This approach provides asynchronous, modular connectivity with scale-independent distribution latency, while the probabilistic nature and low fidelity of remote entanglement generation remain key challenges. (c) QCCD architecture instead achieves scalability by directly shuttling ion qubits by dynamic control of the trapping potential. While it offers deterministic operations and high-fidelity gates, its performance is constrained by scale-dependent latency and ion loss risks during transportation. (d) SDQC integrates deterministic ion shuttling with a distributed architecture to enable non-local quantum operations with high fidelity and low latency via asynchronous and pipelined entanglement distribution.

coupling strength and improve interface efficiency [60]. These developments have enabled preliminary demonstrations of small-scale quantum algorithms based on Photonic DQC architecture [64].

# 2. Quantum charge-coupled device (QCCD)

QCCD architecture achieves scalability by dynamically shuttling ion qubits as shown in Fig. 1(c) [5, 19, 20, 23, 24]. In QCCD, the spatial configuration of ions is reconfigured to adjust qubit connectivity, enabling large-scale quantum computation without relying on limited interaction topology. Ion shuttling is implemented by dynamically controlling the voltages applied to segmented DC electrodes, which generate tunable trapping potentials. This control facilitates various operations, including linear transportation, chain splitting and merging, and positional swapping of ions [19, 23, 35, 65].

QCCD enables dynamic all-to-all connectivity by physically repositioning ion qubits through shuttling operations, eliminating the need for additional operations (i.e., SWAP gate [66, 67] or gate teleportation [13–16]) during quantum circuit execution. As ion shuttling does not disturb qubit states [35, 68], quantum information remains well preserved during transportation, and high-precision shuttling is achieved through accurate electric potential control. The shuttling operations have a lower error rate

than gate operations [68–70], which may offer a more reliable approach to long-range connectivity rather than SWAP gate or gate teleportation using photonic entangling

Although QCCD enables flexible qubit connectivity, several scalability challenges remain. First, as physical shuttling of ion qubits is required, the overall transportation time increases with system size [71–73], scaling approximately as the square root of the number of qubits for a two-dimensional QCCD architecture. While shortdistance shuttling can be performed rapidly, large-scale architectures may experience long latency due to longer transportation distances. As OCCD moves ions containing quantum data (different from DQC moving entanglement pairs), its long transportation time directly affects the operation speed of QCCD. Second, shuttlinginduced motional heating may degrade gate performance, as high-fidelity entangling gates require phonon modes to remain near the ground state [23, 65]. The motional heating during shuttling can necessitate re-cooling procedures [74, 75]. Recent advances in shuttling techniques are addressing this issue by reducing the phonon heating rate during transportation [23]. Third, simultaneous shuttling of multiple qubits necessitates complex control of electrode voltages, requiring fast and accurate multichannel analog control [23, 76]. Finally, efficient compilation (i.e., scheduling and routing) of shuttling operations for a large number of qubits is computationally challenging. The optimization of shuttling trajectories and schedules has been shown to be an NP-complete problem [77–79], and thus, practical implementations currently rely on heuristic approaches to approximate optimal solutions [71, 73, 78, 79].

Fundamental techniques essential for QCCD architecture, including ion transportation, merging and splitting of ion chains, reliable shuttling across junctions, and optimization of dynamic trapping potentials, have been incrementally demonstrated [19, 20, 23, 35, 65]. Based on these developments, experimental implementations of QCCD with dozens of qubits have been realized, enabling the execution of quantum algorithms and system-level benchmarks [20–22]. In summary, QCCD architecture provides an alternative scaling path instead of increasing Coulomb crystal size for trapped-ion QC and remains under active development toward large-scale realization.

### C. Quantum error correction

Precise manipulation of quantum information is limited due to its susceptibility to environmental noise and the imperfect fidelity of quantum gate operations. Furthermore, quantum information collapses when it is measured, thereby prohibiting the backup of quantum data, as stated by the no-cloning theorem [80]. To address these challenges, QEC protocols encode logical qubits across multiple physical qubits, introducing redundancy that allows errors to be detected and corrected without directly disturbing the stored quantum information. Various QEC codes have been proposed, including the Shor code [7, 8], surface code [9, 81, 82], and color code [30, 31, 83, 84], and are commonly characterized using the notation [n, k, d], where n denotes the number of physical qubits, k denotes the number of logical qubits, and  $d_{\text{code}}$  represents the code distance that determines the maximum number of physical errors that can be reliably detected and corrected by the code.

Fault-tolerant quantum computing (FTQC) is achieved by interleaving logical quantum operations with periodic QEC cycles. In FTQC, a fault-tolerant logical cycle (FT cycle) consists of a logical gate on logical qubits followed by  $d_{\rm code}$  rounds of QEC cycles. A typical FTQC workflow includes preparing physical qubits, encoding them into logical qubits, executing a sequence of FT cycles dictated by the target circuit, and finally measuring the logical qubits to obtain computational outcomes.

Each QEC cycle is structured into three stages: syndrome extraction, decoding, and error correction. In the syndrome extraction stage, specific qubit correlations defined by the QEC code are measured to detect possible deviations from the code space, without directly accessing the encoded quantum information. Decoding then interprets the syndrome outcomes to infer the most likely error configuration. Finally, error correction operations are applied to restore the logical qubit state, often imple-

mented virtually through the Pauli frame updates [85].

The two-dimensional color code [30, 31, 83, 84], which is employed in this study, is a widely used family of QEC codes defined on a two-dimensional trivalent threecolorable lattice, such as a hexagonal lattice. Each vertex of the lattice hosts a data qubit, and each face supports X and Z stabilizers for syndrome extraction. The color code enables transversal implementation of all Clifford gates, including the Hadamard, phase, and controlled-NOT (CNOT) gates [86–88], which can be leveraged to achieve highly efficient magic state preparation [89–92]. However, decoding the color code involves increased complexity, which results in lower circuit-level error thresholds than those of the surface code. Nevertheless, there are ongoing efforts to improve decoder performance and scalability, thereby steadily enhancing the viability of the color code as a practical alternative to the surface code [31, 93–95].

Motivated by these properties and its growing viability as an alternative to the surface code, we adopt the color code as our primary candidate for realizing FTQC within SDQC architecture. In particular, the superdense syndrome extraction circuit for the color code employs Bell pairs as ancilla qubits for stabilizer measurements, which naturally supports segmentation and enables an efficient DQC design (as discussed in detail later). Moreover, the smallest instance of the color code, the [7, 1, 3]Steane code, has already been demonstrated on trappedion platforms [85, 87], so our choice of the color code can be viewed as a natural continuation of this experimental trajectory. We emphasize, however, that the advantages of SDQC (e.g., reliable, deterministic entanglement distribution for non-local gates and pipelined auxiliary operations) are mainly code-agnostic, and thus we expect similar benefits to be achievable with other codes, including the surface code, although they are not explicitly analyzed in this work.

# III. SDQC: SHUTTLING-BASED DISTRIBUTED QUANTUM COMPUTING ARCHITECTURE

Here, we introduce our Shuttling-based Distributed Quantum Computing (SDQC) architecture, a hybrid design that combines the complementary advantages of Photonic DQC and QCCD, as shown in Fig. 1(d). To enable non-local operations at scale, SDQC asynchronously distributes entangled pairs, as in Photonic DQC, using the deterministic and high-fidelity shuttling mechanism of QCCD. This hybrid approach enables high fidelity and low-latency operations with scale-independent overhead.

In this section, we present a detailed SDQC architecture and describe physical two-qubit gate operations between remote nodes. We then propose a QEC protocol optimized for the architecture, along with a pipelined execution strategy. Finally, we discuss circuit compilation and highlight key architectural advantages inherited from both Photonic DQC and QCCD.

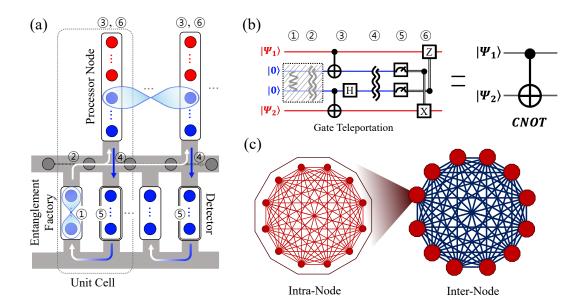

FIG. 2. Shuttling-based distributed quantum computing (SDQC) architecture. (a) Schematic of SDQC architecture. Each unit cell consists of a processor node, an entanglement factory, and a detector. Unit cells are repeated horizontally and connected via a shuttling network. Red and blue circles represent data qubits and entangled qubit pairs for gate teleportation or syndrome extraction (see Sec. III C), respectively. Arrows indicate shuttling flow, and numbers correspond to the gate teleportation steps described in (b) and in the main text. (b) Inter-node two-qubit gates are implemented via the gate teleportation protocol. An entangled pair is generated and transported from the entanglement factory (Steps 1–2), and they interact with data qubits  $\Psi_1$  and  $\Psi_2$  individually (Step 3). After the entangled qubits are shuttled to detectors and measured (Steps 4–5), feedforwards are applied to data qubits based on the measurement result. The overall result of the protocol results in a remote CNOT between the data qubits. Since Steps 1 and 2 do not involve data qubits, their latency can be hidden through pipelining. (c) Connectivity topology of SDQC. SDQC supports two types of two-qubit gates, intra-node and inter-node gates, resulting in a layered connectivity that reflects both local and non-local interactions.

# A. Overall SDQC architecture

Figure 2(a) illustrates the overall architecture of SDQC. SDQC comprises horizontally connected unit cells, each containing a processor node, an entanglement factory, and a detector. These components are interconnected by a shuttling network, which facilitates the transportation of entangled ion qubits.

**Processor node.** Each processor node can host multiple ion qubits confined in a single linear chain. High-fidelity two-qubit gates between arbitrary qubit pairs within a node are enabled by the shared motional mode. While the number of qubits in each node can vary, an upper limit is imposed to preserve gate performance within a node [25–29]. At the beginning of computation, the chain is initialized with data qubits occupying less than half of the available sites, while the remaining sites are left vacant to temporarily accommodate gate teleportation or syndrome extraction qubits.

Entanglement factory. An entanglement factory continuously and asynchronously prepares entangled pairs via local phonon-mediated interaction, operating independently of the processor nodes. These entangled pairs are then transported to processor nodes through the shuttling network and used either for remote two-qubit

gates between nodes or for syndrome extraction in QEC cycles (See Section III C). Each entanglement factory has the same qubit capacity as a processor node.

**Detector.** Once the entangled pairs interact with data qubits, they are shuttled to detectors for state measurement. The measurement outcomes are utilized to apply corrective operations to data qubits, completing either a non-local gate operation or QEC protocol. Detectors are spatially separated from both processor nodes and entanglement factories to minimize idle qubit decoherence and phonon heating during qubit measurement. After measurement, entangled pairs are returned to entanglement factories through the bottom recycling path, enabling qubit reuse.

Shuttling network. The shuttling network connects all components inside SDQC (i.e., processor nodes, entanglement factories, and detectors). Only entangled pairs for gate teleportation or syndrome extraction move through the shuttling network, while data qubits remain stationary in their processor nodes. To prevent deadlocks caused by bidirectional qubit transportation, the network enforces unidirectional shuttling (horizontal path in Fig. 2 (a)). Owing to the distributed nature of DQC, entangled pairs can be generated at any available factory and measured at any detector, regardless of the associ-

ated data qubit locations. This flexibility guarantees that all non-local operations can be executed without requiring bidirectional routing, thereby avoiding transportation conflict and simplifying scheduling.

For more details on architectural assumptions and hardware feasibility, please refer to Appendix A.

### B. Physical two-qubit gate operation

SDQC supports two types of physical two-qubit gates: intra-node and inter-node (non-local/remote) two-qubit gates. The intra-node two-qubit gate operates within a single ion chain utilizing shared motional modes [12, 34]. This mechanism allows arbitrary qubit pairs in a chain to interact, enabling all-to-all connectivity within a node. Recent advanced pulse techniques support not only fast and high-fidelity entangling gates [96, 97] but also the parallel execution of multiple two-qubit gates within a node [98].

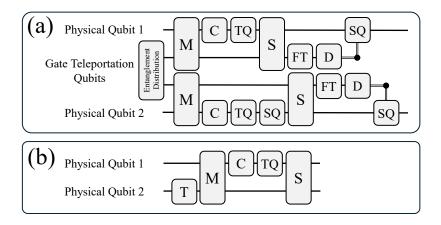

The inter-node two-qubit gate is a non-local quantum operation between processor nodes that relies on gate teleportation using distributed entangled pairs [15]. Figure 2(b) shows the process for implementing inter-node two-qubit gates. SDQC realizes the inter-node CNOT gates with the following steps:

- Step 1, Entangled pair generation. An entangled pair of gate teleportation qubits is generated and prepared in the entanglement factory.

- Step 2, Entanglement distribution. Each gate teleportation qubit of the entangled pair is shuttled to a processor node that hosts the corresponding qubit for the remote two-qubit gate.

- Step 3, Local intra-node operation. Data qubits interact with the delivered gate teleportation qubits by intra-node operations.

- Step 4, Shuttling to detectors. The gate teleportation qubits are shuttled to detectors for measurement.

- Step 5, Gate teleportation qubit measurement.

The gate teleportation qubit states are measured in detectors.

- Step 6, Feed-forward operations. Based on the measurement results, corrective operations are applied to the data qubits to complete the non-local gate.

Among these steps, entangled pair generation and distribution (Steps 1 and 2) can be executed in parallel without interfering with other ongoing operations at the processor nodes. The deterministic shuttling process in SDQC ensures that entangled qubits are delivered precisely when needed, as scheduled during circuit compilation. This enables the effective hiding of distribution latency, making the performance of inter-node gates independent of the system scale.

While the intra-node gates enable local all-to-all interactions within each chain, inter-node gates extend connectivity across nodes via distributed entanglement. This layered structure supports arbitrary qubit pair interactions throughout the entire system, independent of physical qubit placement. Furthermore, since all nodes operate independently, entangling gate operations in SDQC can be executed in parallel, enabling scalable non-local gate operations.

Finally, we note that the gate teleportation protocol can be extended to a broader class of operations, such as controlled-unitary gates and multiple CNOTs using additional entangled pairs [14]. In this work, however, we restrict our focus to remote CNOT gates to simplify the analysis and maintain a consistent evaluation framework.

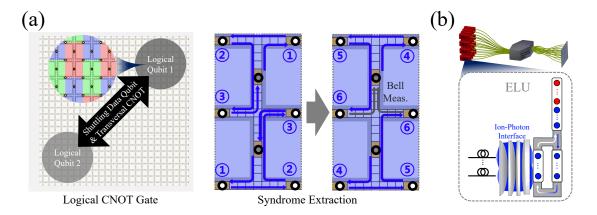

# C. QEC implementation

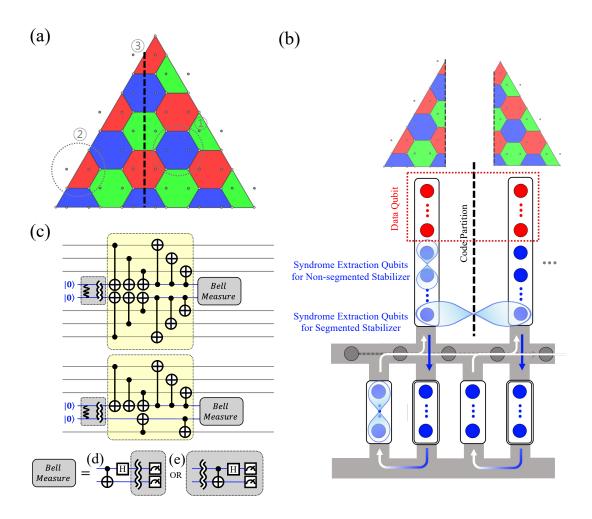

We propose a detailed QEC implementation optimized for SDQC architecture based on the color code as discussed in Sec. II C. As the code distance increases, the number of physical qubits required for a single logical qubit can exceed the capacity of a processor node in SDQC. In such cases, the color code must be partitioned across multiple nodes, leading to segmented stabilizers whose syndrome extraction demands inter-node communication for entangling gates between syndrome extraction qubits and data qubits. To mitigate this overhead, we adopt a superdense coding-based syndrome extraction protocol [31, 84] with distributed entanglement pairs for syndrome extraction, as shown in Fig. 3.

In the superdense syndrome extraction protocol, each face requires two syndrome extraction qubits, as illustrated in Fig. 3(a). The X and Z stabilizers on a face are measured via the circuit in Fig. 3(c): the two syndrome extraction qubits are first prepared in the Bell state, interacted with data qubits, and finally measured in the Bell basis.

The core of our strategy is to place segmentation lines (i.e., the dashed vertical line in Fig. 3(a)) that intersect multiple faces and divide the data qubits into partitions, each residing on a different node. As described in Fig. 3(b), syndrome extraction qubits for segmented stabilizers (supported on the faces crossed by a segmentation line) are distributed to each segment and entangle only with the local subset of data qubits. This is possible since the part of the superdense circuit that involves data qubits (yellow boxes in Fig. 3(c)) is already decomposable into two independent parallel circuits. After applying the entangling gates, the two syndrome extraction qubits are shuttled to a common detector and jointly measured in the Bell basis [Fig. 3(e)]. On the other hand, the process of measuring a non-segmented stabilizer is performed entirely within a single node, except for the initial Bell preparation and the final measurements of the syndrome extraction qubits [Fig. 3(d)]. We note that the partition ratio of segmented stabilizers can be chosen among mul-

FIG. 3. Quantum error correction model. (a) Superdense color code. Each vertex hosts a data qubit, and the circles on the faces or outside the boundary indicate syndrome extraction qubits. There are two types of faces: 1) hexagonal and 2) trapezoidal. To overcome the limitation of chain capacity, we place segmented lines such as the dashed line 3), which intersect multiple faces and divide the data qubits into partitions that are located in neighboring chains. The stabilizers under the segmentation lines are referred to as segmented stabilizers. (b) Physical implementation of syndrome extraction in SDQC. The red and blue circles represent data and syndrome extraction qubits, respectively. A pair of syndrome extraction qubits for a segmented stabilizer are shuttled to different nodes, interact with data qubits, and then shuttled back to a common detector to be measured in the Bell basis. On the other hand, syndrome extraction qubits for non-segmented stabilizers are shuttled to the same node and processed within it, except for the final measurements. (c) Superdense syndrome extraction circuit. The circuit comprises Bell state preparation and distribution, entangling gates between data and syndrome extraction qubits (yellow), and Bell measurements depicted separately in (d) or (e). The upper (lower) circuit measures X and Z stabilizers on a hexagonal (trapezoidal) face. Grey and blue lines indicate data and syndrome extraction qubits, respectively. Wavy double lines stand for shuttling. (d), (e) Bell measurement circuits for non-segmented and segmented stabilizers. Gray layers include shuttling and the following operations in detectors.

tiple options (e.g., 1:5, 2:4, and 3:3), with the superdense circuit adjusted accordingly. However, the circuit depth depends on this choice, and it is minimized when the partition is even (i.e., 3:3).

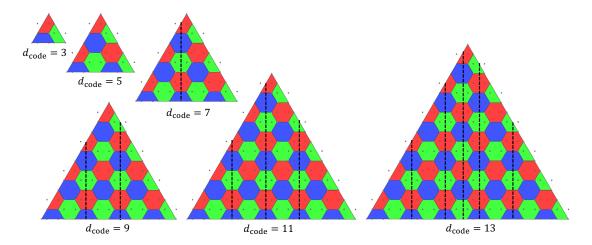

This approach allows the code distance to be extended without being limited by the qubit capacity of a single processor node. Figure 4 illustrates the code partitioning with code distance ranging from  $d_{\rm code}=3$  to  $d_{\rm code}=13$ . Even with the processor node capacity set to 60 qubits in this work, large-distance codes can be implemented with-

out significant overhead. In addition, the distributed syndrome extraction protocol can be applied to other DQC architectures, provided that entangled pairs for syndrome extraction can be distributed across nodes. For more details of their physical qubits mapping per logical qubit and QEC sequence, please refer to Appendix B and C.

For fault-tolerant logical gates, SDQC can leverage inter-node operations to realize transversal Clifford gates, including CNOT, Hadamard, and Phase gates, inherently supported by the color code [86–88]. The all-to-all con-

nectivity of inter-node physical two-qubit gates ensures full connectivity of logical qubits. Furthermore, internode operations in SDQC can be executed in parallel, enabling scalable logical gate parallelism.

For non-Clifford gates, including the T gate, SDQC requires a magic state factory (e.g., magic state cultivation [91] or its combination with magic state distillation [92]) to supply distilled magic states for injection. Once a high-fidelity magic state is available, the injection circuit can be implemented using only Clifford operations and logical qubit measurement, resulting in gate overhead comparable to that of Clifford gates. As this work represents a foundational step towards achieving a scalable architecture, we focus on the core operations such as transversal gates and syndrome extractions, leaving the explicit integration of magic state factories for future studies.

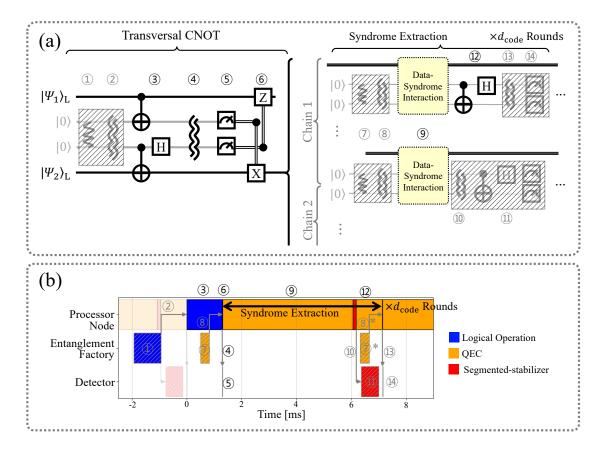

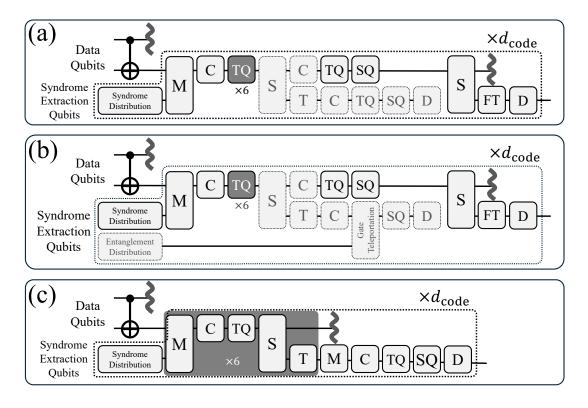

### D. Efficient logical operation protocol

In FTQC, a logical clock time is defined as the execution time for a single FT cycle, including one logical CNOT gate and  $d_{\rm code}$  rounds of QEC cycles. To reduce the logical clock time, we propose a pipelined gate execution protocol. Figure 5 shows the pipelined steps and the resulting time cost reduction for the FT cycle. Specifically, Steps 1–6 in Fig. 5(a) represent the transversal CNOT operation implemented by multiple parallel physical gate teleportation (Sec. III B), and Steps 7–14 represent a single QEC cycle for syndrome extraction, which repeats  $d_{\rm code}$  times.

Within this process, SDQC can pipeline two key stages involving gate teleportation (syndrome extraction) qubits: entangled pairs preparation (Steps 1, 2, 7, and 8) and parallel Bell measurements (steps 11, 13, and 14) as shown in Fig. 5(b). The pipelining allows SDQC to hide its latency behind data qubit operations (Steps 3, 6, 9, 10, and 12). As data qubit operations generally take longer execution time than gate teleportation (syndrome extraction) qubit operations, SDQC can hide non-data-interactive overhead behind the data qubit operation latency.

Implementing such pipelining requires fast and deterministic generation of a large number of entangled pairs. SDQC is expected to support a sufficient number of entangled pairs even for large code distances, which is feasible with currently available system performance (see Section IVB2).

### E. Compilation

Efficient compilation is essential to achieve optimal performance with QC architectures, although it requires costly processes such as optimal qubit mapping [79], shuttling path routing [71], and scheduling [73]. Since compilation process is computational hard [77–79], practical

approaches rely on heuristic algorithms for approximate solutions [71, 73, 78, 79].

Compilation is particularly challenging in shuttling-based architectures (e.g., QCCD) due to their dynamic qubit mapping. In QCCD systems, data register allocations change during circuit execution, making optimal quantum circuit mapping highly nontrivial. In contrast, SDQC shuttles only gate teleportation qubits, while data qubits remain stationary throughout execution. All data qubits exhibit all-to-all connectivity via gate teleportation, which significantly simplifies compilation. Moreover, gate teleportation qubits are transferred unidirectionally through the shuttling network, which simplifies the scheduling of shuttling operations.

In Photonic DQC architectures, entangled pairs are generated via probabilistic heralded processes, requiring circuits to wait for successful entanglement events before proceeding. This induces compilation overhead, as the compiler must handle conditional execution paths and uncertain gate timing. In contrast, SDQC employs a deterministic entangled pair distribution, ensuring a fixed execution flow without branching or timing uncertainty. This determinism further simplifies compilation by enabling static scheduling of communication operations.

# F. Summary: key properties and advantages of SDQC

The key idea of designing SDQC is to exploit the complementary advantages of Photonic DQC and QCCD. From DQC, SDQC inherits the ability to distribute entanglement with flexible timing. This flexibility enables asynchronous production of entanglement pairs independent of circuit execution applied to data qubits and enables aggressive pipelining, which hides most of the scale-dependent latency associated with entanglement distribution. Also, the resulting idle time gained from pipelining can be used to improve performance through operations such as entanglement purification, dynamical decoupling, phase shift compensation, and ion-loss recovery. [19, 20, 36, 74, 99–101]. The latency associated with these supplementary operations can also be largely hidden through the same pipelining mechanism.

On the other hand, the key property inherited from QCCD is the ability to extend the range of deterministic and high-fidelity local operations via qubit shuttling[16, 38]. A major limitation of Photonic DQC is the performance of the ion-photon interface, which is probabilistic and yields a low generation rate and limited fidelity compared to local gate operations [49, 50, 52–55]. SDQC overcomes this limitation by generating and distributing entanglement through local gate operations and shuttling, enabling fast and deterministic delivery of high-fidelity Bell pairs. Because the fidelity of locally generated entanglement is substantially higher than that of photonic interfaces, shuttling-based distribution significantly improves the fidelity of non-local gates and the

FIG. 4. Logical qubit segmentation for various code distances. Due to the limited qubit capacity of each chain, SDQC segments the physical qubits of a logical qubit across multiple processor nodes or chains to accommodate larger code distances  $(d_{\text{code}} \geq 7)$ . The dashed lines indicate segmentation boundaries. The layout details are provided in Appendix B.

overall architectural performance. The deterministic timing provided by shuttling further enables reliable pipelining by creating predictable idle windows in the execution schedule.

In summary, SDQC integrates high-fidelity entanglement generation with flexible and efficient execution, achieving deterministic operation and scalable performance at practically useful system sizes.

### IV. EVALUATION

In this section, we evaluate the execution time and error rate of SDQC compared with QCCD and Photonic DQC. Both metrics are analyzed for physical two-qubit gates and logical two-qubit gates, followed by QEC cycles. Finally, the architectures are benchmarked by estimating the total execution time and success rate for running quantum applications, specifically the Fermi-Hubbard model simulation [102, 103] and Shor's algorithm for the elliptic-curve discrete logarithm problem (ECDLP) [104].

### A. Evaluation setup

# 1. Baseline architectures for comparison

We evaluate SDQC against the two representative architecture designs: QCCD and Photonic DQC. For conservative comparison, we model QCCD and Photonic DQC with their optimistic setups.

**QCCD.** Figure 6(a) shows the architecture of QCCD. We assume QCCD as a two-dimensional grid structure following the demonstration of the previous work [23]. QCCD realizes two-qubit operations of remote qubits by

shuttling the target qubit to the location of other qubit and entangling them.

To generate the logical qubits with superdense color code, we assume that QCCD architecture locates the data qubits and syndrome extraction qubits on the transverse and longitudinal paths, respectively, as shown in Fig. 6(a). Each qubit is assumed to have a dedicated operational zone for state preparation, measurement, and logical operation (i.e., orange regions in Fig. 6(a)). QCCD shuttles syndrome extraction qubits to the operational zone of neighboring data qubits and entangles them to run the QEC cycles. Specifically, following the syndrome extraction process of the Superdense color code, QCCD moves syndrome extraction gubits in the direction of Steps 1-3 while entangling them with the stationary data qubits. These processes correspond to the X stabilizer of the color code. Then, QCCD again moves the syndrome extraction qubits in the direction of Steps 4–6, and measures them using Bell-based measurements. These processes correspond to the Z stabilizer operation of the Superdense color code.

On the other hand, to execute the logical operations among logical qubits, QCCD conducts long-distance shuttling of data qubits to those of another target logical qubit and then transversely entangles them (i.e., Shuttling Data Qubit & Transversal CNOT in Fig 6(a)). As the long-distance shuttling requires data qubits to traverse intermediate junctions and qubits, we consider the physical SWAP operation when one qubit faces other qubits during the shuttling. The shuttling path is optimized by using the routing algorithm proposed in Ref. [71].

For the conservative comparison for SDQC, we ignore the shuttling overhead of qubits moving back to the origin position after logical two-qubit gate operations. This assumption makes the shuttling overhead nearly half compared to the overhead without this assumption.

FIG. 5. Pipelined execution of the FT cycle in SDQC. (a) A sequence of a single FT cycle in SDQC, including one logical CNOT gate and repeated syndrome extractions. A logical CNOT gate is implemented as transversal gates via parallel gate teleportations (Steps 1–6). Following the gate operation, syndrome extractions are repeated for  $d_{\text{code}}$  rounds to perform quantum error correction (Steps 7–14). All syndromes can be extracted in parallel by leveraging intra-node gates parallelism and appropriate scheduling. Gray-colored steps indicate pipelined stages, while black-colored steps denote operations that effectively set the overall FT cycle latency. (b) Temporal diagram of the pipelined FT cycle. Entangled pair preparation of gate teleportation qubits (Steps 1–2) and syndrome qubits (Steps 7–8), as well as Bell measurement of syndrome qubits (Steps 10–11, 13-14), are hidden behind data qubit operations (Steps 3–6, 9, 12) by pipelining. Blue, orange, and red blocks represent the duration of the logical CNOT gate, QEC cycles, and Bell measurement for segmented-stabilizer, respectively. Gray arrows indicate ion shuttling operations across architectural components, where horizontal extent denotes average shuttling duration. Timing values in this diagram correspond to a code distance of  $d_{\text{code}} = 13$

Photonic DQC. Figure 6(b) shows the architecture of a Photonic DQC. Photonic DQC consists of many identical modules, called an elementary logical unit (ELU) [6]. We assume the ELU has a similar structure as SDQC's unit cell except for an ion-photon interface, as shown in Fig. 6(b). Each ELU is connected by the ion-photon interface, which generates Bell states between arbitrary ELUs. By utilizing the generated Bell states between ELUs, Photonic DQC can run QEC cycles and build a logical qubit using many ELUs. Photonic DQC can also realize remote two-qubit gates and logical two-qubit operations by utilizing the Bell states in a similar manner with SDQC.

For a conservative comparison of SDQC, we assume the following attributes for Photonic DQC. First, we assume that the entanglement pair (*i.e.*, Bell state) can be generated in a fully parallelized manner without incurring errors to other qubits. This is an optimistic setup

for Photonic DQC because the fully-parallel generation of Bell states has not been demonstrated yet, to the best of our knowledge. Also, we assume a deterministic generation rate equal to its average value, although the process is inherently probabilistic. In addition, we assume that the photon delivery error is independent of the delivery distance [105, 106]. Finally, we ignore the latency and loss of optical switches, which connect ELUs by using photonic interconnects.

The detailed QEC implementations for QCCD and Photonic DQC are summarized in Appendix C.

# 2. Number of physical qubits for each architecture

We classify the physical qubit count into three categories: qubit count for logical data storage, qubit count for syndrome extraction, and qubit count for gate tele-

FIG. 6. Architecture comparison. (a) QCCD. QCCD has a grid structure, and the color code stabilizers are projected onto the grid. The white and gray circles are the data and syndrome extraction qubits, respectively. The orange squares under the circles are the operation zones. The arrows and Steps 1-6 represent the shuttling routes and entangling gates between data and syndrome extraction qubits for syndrome extraction. (b) Photonic DQC adapted from Monroe et al., 2014 [6]. The architecture comprises the elements of a logical unit (ELU) and an optical switch. The ELU in this evaluation has a similar structure to SDQC unit cell, and the entanglement factory has an ion-photon interface.

portation. We derive the required qubit count for each architecture by starting with a baseline superdense color code layout and then adding the additional qubits needed to support the specific QEC cycles and logical operations for each architecture. The additional qubits belong to the qubit counts for syndrome extraction or gate teleportation. The physical qubit mapping of the baseline superdense code is summarized in Table VI in Appendix B. The qubit count for each architecture is determined based on the following rationale.

**SDQC.** The data qubit count of SDQC is set to be identical to that required for the superdense color code implementation shown in Fig. 4. For the qubit count of syndrome extraction, we allocate the twice number of syndrome extraction qubits of the baseline superdense color code. The doubled allocation is to enable the preparation of Bell states before the end of a QEC cycle, thereby minimizing the time cost by eliminating the delay between QEC cycles.

For the qubit count of gate teleportation, which transports Bell states for logical operations, we calculate the maximum qubit count required to run the target application. The required number of active Bell pairs is derived by multiplying the number of data qubits per logical qubit by the maximum number of logical two-qubit gates within a single application layer.

In addition to these active pairs, the qubit count for gate teleportation also includes spare qubits reserved to mitigate the impact of ion loss. The operational failure occurs when fewer qubits arrive than the required active qubits after accounting for ion loss events. We calculate the probability of such failure as a function of spare qubit counts and chose the number of spare qubits to ensure this probability remains below 1 % of the transversal gate error rate.

QCCD. We set the qubit counts for data and syn-

drome extraction based on the baseline QCCD structure shown in Fig. 6. For similar reasons to SDQC, we set data qubit count to be the same as those of the superdense color code, and the qubit count for syndrome extraction to twice that of the color code implementation. We set the number of communication and spare qubits to zero because QCCD directly shuttles data qubits instead of Bell states, and thus does not utilize these qubit types.

Photonic DQC Similar to SDQC, we set the data qubit count to match the color code implementation. For the qubit count for syndrome extraction, we not only allocate twice the number required by the color code, but also include additional qubits (i.e., the number of 'segmented syndrome extraction' in Table VI). This additional qubit count is necessary because Photonic DQC requires additional Bell states to enable remote Bell-state measurements between syndrome extraction qubits of segmented stabilizers of different ELUs. We derive the qubit count for gate teleportation by using the same method as SDQC. We set the number of spare qubits to zero, as the photonic entanglement process of Photonic DQC has low ion loss probability thanks to its short shuttling distance.

We summarize the detailed equation for calculating the qubit counts in Appendix G.

### 3. Time cost setup

Table I shows the time cost of unit operations. We select the values from the previously demonstrated works, showing a reasonable scale of latency. For two-qubit gate, we model its latency as linearly proportional to the number of qubits in a chain following the previous work [107, 108]. We use the latency of state detection [109] and electromagnetically induced transparency (EIT) cooling

| Operation type        | Time $[\mu s]$                               |

|-----------------------|----------------------------------------------|

| Single-qubit gate     | 5 [19]                                       |

| Two-qubit gate        | Max(13.33N-54, 100) [107, 108]               |

| Measurement           | 400 [109]                                    |

| Cooling               | 300 [75]                                     |

| Photonic entangling   | 4000 [58]                                    |

| Stable transportation | 46.9 (for 375 $\mu$ m) [23]                  |

| Fast transportation   | $4.6 \text{ (for } 375 \ \mu\text{m) } [65]$ |

| Split                 | 128 [19]                                     |

| Merge                 | 128 [19]                                     |

| Physical swap         | 200 [19]                                     |

TABLE I. Time Cost of Unit Operation. N denotes the number of physical qubits in a chain.

| Operation Type        | Error rate                 |

|-----------------------|----------------------------|

| Single-qubit gate     | $1.5 \times 10^{-7} [110]$ |

| Two-qubit gate        | $3.0 \times 10^{-4}$ [38]  |

| Measurement           | $9.0 \times 10^{-5} [109]$ |

| Photonic entangling   | $2.85 \times 10^{-2}$ [50] |

| Shuttling             | $1.0 \times 10^{-5}$ [69]  |

| Idle error (for 1 ms) | $3.7 \times 10^{-6}$ [111] |

TABLE II. Base Error Rate.

[75] from the previous experimental results. EIT cooling is used for sympathetic cooling, which reduces the phonon number of the qubit without disturbing the internal state. For photonic entangling, we use the average latency of the heralding process (i.e., 1 MHz attempt rate with  $2.5 \times 10^{-4}$  of success probability [58]) due to its probabilistic nature. For shuttling, we set the shuttling latency as the sum of linear transportation, splitting, merging, and physical swapping based on the experimental results [19, 23, 65]. We calculate the time cost for the transportation to move the qubit for a unit distance (375  $\mu$ m) with shuttling [23]. We assume two types of transportation: fast and stable transportation. Fast transportation can reduce the time cost with its high speed (82 m/s [65]), but the qubit heating during the fast transportation can incur a high entanglinggate error. Therefore, we use fast transportation only for the qubit movement for measurements, which is less susceptible to heating. For other types of transportation (e.g., Bell state provisioning), we use stable transportation with 8 m/s speed [23].

### 4. Base error rate setup

Table II shows the error rate used in our evaluation. All error rates are based on experimentally demonstrated results [38, 50, 69, 109–111] to evaluate the current reasonable quantum computers. In this setup, we use the single-qubit gate and two-qubit gate error rates of  $1.5 \times 10^{-7}$  and  $3.0 \times 10^{-4}$ , respectively, following the previous works [38, 110], while assuming that the platforms can support individual addressing [112–119]. For state detection error (i.e., measurement error), we refer to Ref. [109], which demonstrated high-fidelity measurement on the order of  $10^{-5}$  error without relying on a heralded process [37] or requiring excessively long measurement times [120]. For the photon entangling, shuttling, and coherence time, we use the results of the previous works demonstrating minimum errors [50, 69, 111]. Idle error arises from dephasing and technical imperfections affecting qubits in idle states, such as shuttling-induced phase noise and cross-talk. We adopt a dephasing-based error model, using parameters referenced from Ref. [111], to determine the idle error rate of  $3.7 \times 10^{-6}$  per ms.

For future scenarios, we assess architecture-level performance gains by proportionally reducing the base error rates with the operation improvement factor  $\lambda$ . We assumed uniform fractional improvements across all operations for simplicity.

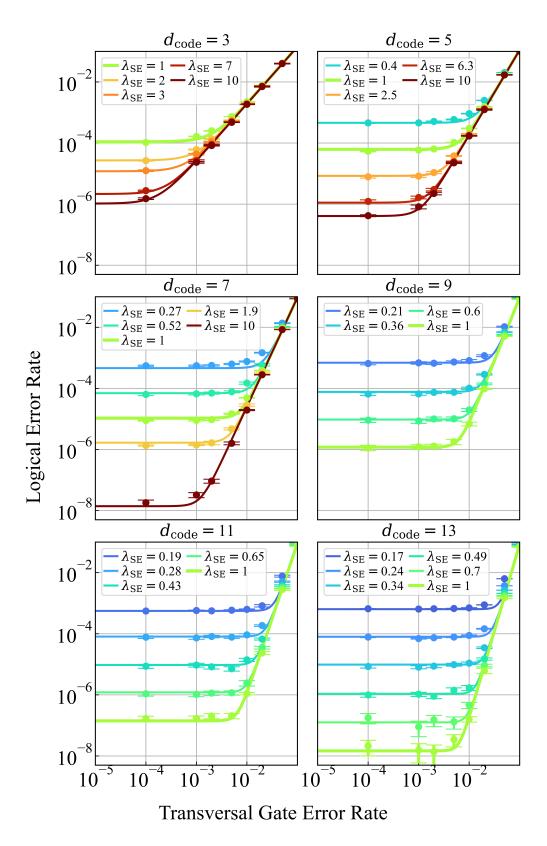

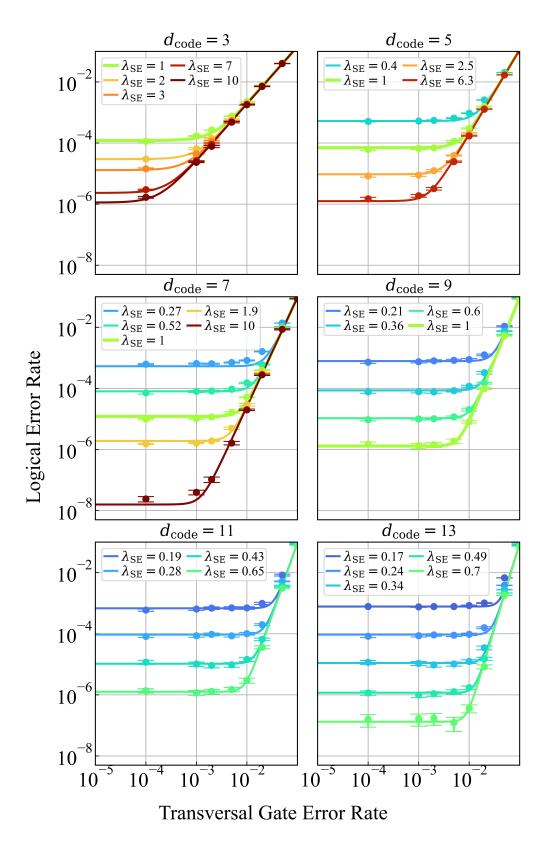

### 5. Logical error rate setup

To estimate the logical error rates of logical twoqubit gates for each architecture, we perform circuitlevel simulations of QEC processes, explicitly reflecting architecture-dependent operation sets. Even though the same error correction code and decoding algorithm were used for all architectures, the actual operation sets for QEC circuits, including qubit shuttling and entanglement distribution, differ significantly, resulting in distinct error accumulation characteristics. We implement architecture-specific QEC circuits using the Stim simulator [121] and apply the concatenated minimum-weight perfect matching (MWPM) decoder for syndrome decoding [94, 122] (See Appendix F).

Each circuit consists of one transversal two-qubit gate followed by  $d_{\rm code}$  rounds of syndrome extraction, corresponding to a single logical clock cycle. The transversal gates are implemented by parallel remote two-qubit gates, and the error during the transversal gates propagates across different code blocks, which ideally requires sophisticated correlated decoders jointly involving multiple code blocks [123]. However, to simplify our analysis, we ignore such correlations and simulate error propagation within a single code block, where the ordinary concatenated MWPM decoder suffices. Specifically, rather than including noisy two-qubit gates (with error rate p) between different code blocks explicitly, we place noisy idling gates with error rate (4/5)p on all physical qubits in a code block. This reflects the fact that 12 out of 15 nontrivial two-qubit Pauli operators acts nontrivially on each qubit. We note that this simplification renders it difficult to evaluate logical error correlations between

code blocks, which are therefore estimated conservatively in our application analysis (see Sec. IVA6).

The syndrome extraction circuit after the transversal gates is constructed in a way that heavily depends on the architecture and the code distance. Especially, for  $d_{\rm code} > 7$ , DQC architectures requires partitioning of the logical qubit into multiple nodes, which significantly changes the actual operation sets of syndrome extraction. The simulation circuits are constructed to reflect the architecture-dependent operation sets (SDQC, QCCD, and Photonic DQC) and are simulated up to code distance 13.

To evaluate logical error, the constructed circuit above is preceded and followed by logical initialization and measurement in the Z basis for obtaining the logical X error rate  $p_{\rm L}^X$ . Then the total logical error rate  $p_{\rm L}$  is calculated as  $p_{\rm L}=2p_{\rm L}^X$ , assuming that the logical Z error rate is the same as  $p_{\rm L}^X$  and logical Y errors are negligible.

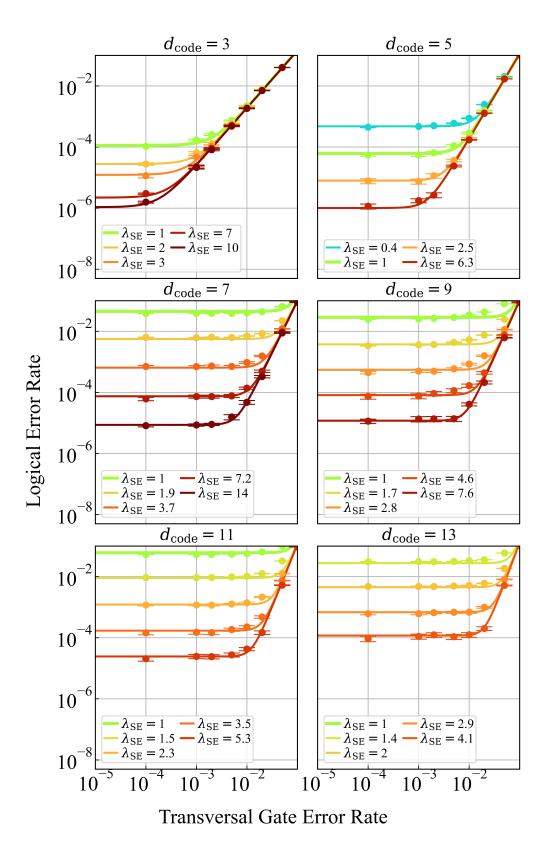

The transversal gates and syndrome extraction stages exhibit distinct physical characteristics and scaling behaviors in the studied architectures. To characterize the effect of these two distinct stages, we introduce two parameters: the transversal gate error rate  $p_{\rm trans}$  and the operation improvement factor for syndrome extraction  $\lambda_{\rm SE}$ . The transversal gate error rate represents the error probability of two-qubit gates acting between code blocks, which are modeled as idling gates with error rates of  $(4/5)p_{\text{trans}}$ , as described above. For syndrome extraction, which consists of multiple operations with different physical error rates, we introduce a uniform reduction factor  $\lambda_{\rm SE}$  that lowers all error rates rather than defining a single effective error rate. For example,  $\lambda_{\rm SE}=1$  corresponds to the current feasible error rates in Table II during syndrome extraction, and  $\lambda_{\rm SE} = 10$  represents a tenfold improvement across all operations. Although  $p_{\rm trans}$ actually depends on the underlying gate error rates, we treat it as independent in our simulations and later assign appropriate values when evaluating application-level performance.

Assuming the effects of the two stages on logical error are independent, we model the logical error rate  $p_{\rm L}$  as

$$p_{\rm L}(p_{\rm trans}, \lambda_{\rm SE}; d_{\rm code}) = A p_{\rm trans}^{\alpha d_{\rm code}} + B (1/\lambda_{\rm SE})^{\beta d_{\rm code}},$$

(1)

where  $d_{\rm code}$  is the code distance and  $A, B, \alpha$ , and  $\beta$  are fitting parameters. Note that we fit data for each fixed  $d_{\rm code}$  with varying  $p_{\rm trans}$  and  $\lambda_{\rm SE}$ , indicating that the parameters are functions on  $d_{\rm code}$  (although not explicitly specified for brevity). The model suggests two regimes: the transversal gate dominated regime and syndrome extraction dominated regime. For large  $p_{\rm trans}$ , the logical error rate is primarily determined by transversal gate errors and increases with  $p_{\rm trans}$ . On the other hand, when  $p_{\rm trans}$  becomes sufficiently small, the logical error rate is saturated and limited by the fidelity of syndrome extraction stage. The crossover error rate  $p_{\rm trans}^* = (B/A\lambda_{\rm SE}^{\beta d_{\rm code}})^{1/(\alpha d_{\rm code})}$ , defined as the point where the two contributions become equal, marks the

boundary between the two regimes and can be obtained by fitting the model to simulation results.

Due to the limited computational resources, our simulation was performed down to the level of  $10^{-8}$  logical error rate, and the lower regions were extrapolated from the fit parameters. The results are presented in Appendix F 2 together with the values of the fitted parameters, the coefficient of determination  $(R^2)$ , and  $p_{\rm trans}$  at  $\lambda_{\rm SE}=1$ , verifying that the model represents the data reasonably well within our simulated range. Although the fits become less accurate for Photonic DQC at  $d_{\rm code} \geq 7$  due to noisy photonic entangling operations, they still yield slightly optimistic estimates relative to the raw data, suggesting that the comparison between SDQC and Photonic DQC remains conservative.

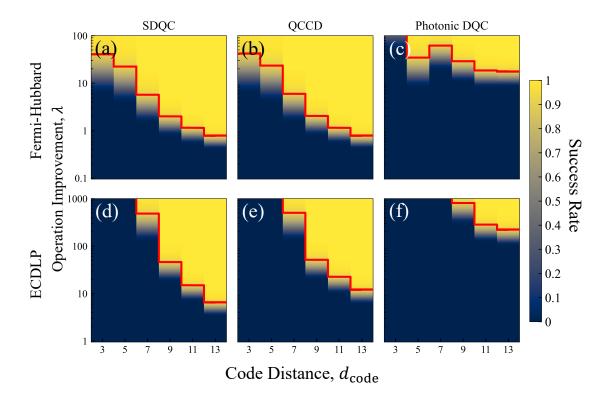

# 6. Application setup

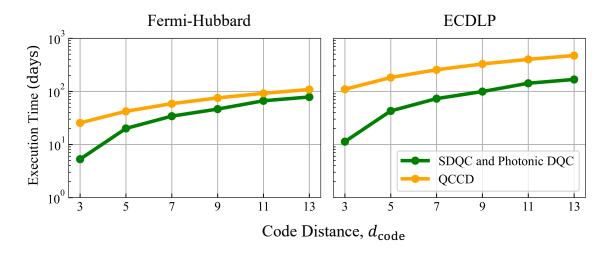

Overall architectural performance can be evaluated by the estimated execution time and the algorithmic success probability. We benchmark two representative applications: quantum simulation of the Fermi-Hubbard model with Trotterization [102, 103] and the elliptic-curve discrete logarithm problem (ECDLP) implemented with Shor's algorithm [104]. For the Fermi-Hubbard model, we simulate a  $6 \times 8$  lattice of spinful fermions, requiring 132 logical qubits [103]. Each shot comprises 8,787 layers of logical two-qubit gates (14,548 gates) and non-Clifford gates to compose arbitrary rotation gates (316,476 T gates for  $10^{-5}$  precision error [124]), and  $10^4$  shots are assumed to suppress statistical error. For ECDLP, we target a 256-bit elliptic-curve cryptography (ECC) instance. requiring 2,871 logical qubits [104]. The circuit depth is approximately  $1.88 \times 10^8$  logical layers, requiring approximately  $2.41 \times 10^{10}$  logical gates, including single-qubit non-Clifford gates. For each architectures, the number of idle operations is estimated by summing idle logical qubits across logical layers. Table III summarizes the application setup.

$$T_{\text{exec}} = N_{\text{laver}} \times T_{\text{L}} \times N_{\text{shots}},$$

(2)

$$P_{\text{success}} = (1 - 2p_{\text{L}})^{N_{\text{gate}}} \times (1 - p_{\text{idle}})^{N_{\text{idle}}}.$$

(3)

Equations (2) and (3) show the expressions for the total execution time  $T_{\rm exec}$  and the overall success rate  $P_{\rm success}$  of the benchmark applications. The execution time  $T_{\rm exec}$  is obtained by multiplying the number of gate layers for each shot  $N_{\rm layer}$ , the number of shots for executing the target application  $N_{\rm shots}$ , and the time duration required for executing a logical operation  $T_{\rm L}$  for each architecture. The success rate  $P_{\rm success}$  accounts for both the logical operation error rate  $p_{\rm L}$  and the idle operation error rate  $p_{\rm idle}$ . We calculate  $p_{\rm idle}$  as the logical qubit error without transversal gate error rate (i.e.,  $p_{\rm L}(0, \lambda_{\rm SE}; d)$ ) because the

| Application         | Number of logical qubits | Number of logical layers per shot $(N_{ m layer})$ | Number of logical gates per shot $(N_{\rm gate})$ | Number of idle operations per shot $(N_{\text{idle}})$ | Number of shots $(N_{ m shots})$ |

|---------------------|--------------------------|----------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|----------------------------------|

| Fermi-Hubbard [103] | 132                      | 8,787                                              | 331,024                                           | 828,860                                                | 10,000  shots                    |

| ECDLP [104]         | 2,871                    | $1.4\times2^{27}$                                  | $1.4 \times 2^{34}$                               | $4.91\times10^{11}$                                    | 1 shot                           |

TABLE III. Application setup.

transversal operations are not applied during an idle operation. The total success rate is computed by accumulating the success probabilities of all operations, weighted by their counts (i.e., total number of logical gates  $N_{\rm gate}$ , and idle operations  $N_{\rm idle}$ ). We conservatively increase the logical operation error by twice because a single logical operation can incur the logical error of up to two logical qubits. Note that both  $T_{\rm L}$  and  $p_{\rm L}$  depend on the architecture, the number of logical qubits, and the code distance. A target success rate of 90 % is set for both applications, and the required code distances and gate error improvements are analyzed for each architecture.

### B. Operation time cost

In this section, we compare three architectures with the time cost of remote physical two-qubit gates (inter-node two-qubit gates) and logical gates with QEC cycles.

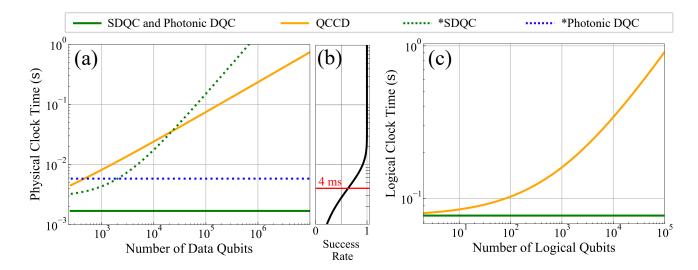

# 1. Remote physical two-qubit gates

Figure 7(a) presents the execution time analysis of remote physical two-qubit gates across three architectures. As the number of qubits increases, the total shuttling distance also increases in the two shuttling-based architectures, SDQC without pipelining (denoted as \*SDQC in Fig. 7) and QCCD, resulting in longer execution times for remote physical gates. In QCCD, the shuttling distance scales with the square root of the total number of qubits due to its two-dimensional grid structure. This distance can be mitigated through routing optimization, and our evaluation adopts the strategy proposed in Ref. [71]. In contrast, for \*SDQC, the time cost scales linearly with system size (i.e., the number of logical qubits), as it corresponds to a combinational average over all logical qubits. Details are discussed in Appendix D.

Crucially, QCCD requires the shuttling of data qubits, which cannot be pipelined and therefore contributes directly to cumulative latency. In \*SDQC, however, the increase in shuttling time arises solely from entanglement distribution. This overhead does not accumulate over successive two-qubit gates with a proper pipelining strategy, denoted as SDQC in Fig. 7 (see Section III D). Photonic DQC also utilizes pre-distributed entangled qubits for remote physical two-qubit gate, and such operations

do not scale with the system size since the photonic qubits propagate at the speed of light; \*Photonic DQC in Fig. 7(a) does not consider pipelining. With predistributed entangled qubits via proper pipelining, both SDQC and Photonic DQC exhibit scale-independent execution times for remote physical two-qubit gates. These execution times are effectively identical, as the two architectures share the same operational structure except for the entanglement distribution mechanism.

While both SDQC and Photonic DQC utilize distributed entanglement pairs to enable gate teleportation. their entanglement distribution mechanisms differ fundamentally. SDQC employs deterministic shuttling of entangled gate teleportation qubits between nodes, enabling reliable delivery on demand. In contrast, Photonic DQC relies on a heralded entanglement generation process, which involves probabilistic photon-mediated attempts repeated until success. As a result, the entanglement generation time in Photonic DQC can only be characterized statistically, and its probability distribution depends on the success rate of individual entanglement generation attempts (Figure 7(b)) [58]. This probabilistic nature of Photonic DQC may necessitate additional buffering and resource scheduling, potentially resulting in increased execution time.

# 2. Logical gates with QEC cycles

For fault-tolerant gate operations, each logical clock cycle involves transversal gates followed by  $d_{\rm code}$  rounds of syndrome extraction for error-correction. In the case of DQC architectures, we adopt the pipelined execution strategy discussed in Section IIID and Appendix D 2. In all architectures, transversal gates can be performed in a fully parallel manner, and their execution time is essentially identical to the remote physical gate time discussed above. The syndrome extraction is mostly scale-independent, as error correction codes are encoded into localized clusters of physical qubits.

Figure 7(c) shows the logical clock time across the three architectures. Similar to the behavior of physical two-qubit gates, both DQC architectures exhibit no scale-dependence. In contrast, the logical clock cycle of QCCD increases with the number of logical qubits, due to longer shuttling paths. As a result, DQCs exhibit the fastest logical clock speed, outperforming QCCD due

FIG. 7. Time cost with  $d_{code} = 13$ . (a) The remote physical two-qubit gate time (physical clock time) versus the number of data qubits. The dotted lines (\*SDQC and \*Photonic DQC) represent the time costs including entanglement distribution time. The green solid line shows the identical time cost for SDQC and Photonic DQC when the entanglement distribution time is removed by pipelining, exhibiting scale-independent behavior. The orange solid line shows the physical two-qubit gate time of QCCD, in which pipelining is not applicable. (b) The cumulative success probability of photonic entangling as a function of attempt duration. Photonic entangling is a probabilistic process following a geometric distribution, and the red line indicates the mean value (4 ms) used for architecture evaluation. (c) The logical clock time versus the number of logical qubits. For all architectures, the syndrome extraction qubits distribution is assumed to be fully pipelined.

to their ability to pipeline entanglement distribution, thereby reducing latency in transversal gates execution. For 2,871 logical qubits to run Shor's algorithm [104], as follows Section IV D, the logical clock speed of DQCs is 2.82 times faster than QCCD.

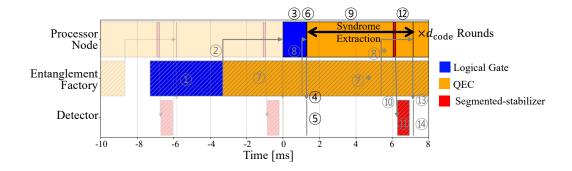

Although pipelining enables DQC architectures to achieve scale-independent logical clock speeds, this advantage holds only if entangled pair generation throughput exceeds the demand during logical operations. Here, the entanglement pair throughput is defined as the number of entangled pairs generated per unit time at a single entanglement factory, while the peak entanglement demand refers to the highest entanglement generation rate required by any single factory. If the available throughput falls short of this peak demand, pipelining fails to fully mask the latency of entanglement distribution, resulting in execution bottlenecks.

In SDQC, entangled pairs are generated using local two-qubit gates within each factory and distributed via shuttling, both of which can operate in parallel. For the code distance  $d_{\rm code}=13$ , up to 198 pairs are required in each factory per FT cycle, resulting in a peak entanglement demand of 2,568 Hz. The achievable throughput with a chain capacity of 60 is estimated at 39,958 Hz, which exceeds this demand by more than an order of magnitude.

In Photonic DQC, the maximum number of required entangled pairs is slightly higher (total 276 pairs with locally generated 91 pairs) due to additional gate teleportation for Bell measurements of segmented syndrome extraction qubits, resulting in a peak entanglement de-

mand of 3,580 Hz; for only photonic entangling, the peak entanglement demand is 2,399 Hz. Given the current record generation rate of 250 Hz, achieving pipelined execution requires substantial improvements in both the speed and parallelization of entanglement generation.

# C. Error rate

In this section, we evaluate the remote physical twoqubit gate error and logical two-qubit gate error of each architecture scaled by the number of qubits.

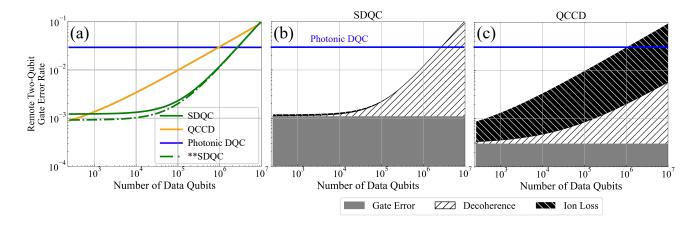

### 1. Remote physical two-qubit gates

Figure 8 shows the average remote physical two-qubit gate error for each architecture, with the error budget decomposed into its constituent sources. In all architectures, the total gate error is determined by three distinct error mechanisms: (1) accumulated errors from local gates and state detection, (2) ion loss at junctions during shuttling, and (3) decoherence over the total operation time. Because the shuttling path length and operation time vary depending on the architecture and system scale, we constructed a simplified error model that captures the scale-dependent gate performance of each architecture for comparison (See Appendix E).

In the two DQC architectures, the gate teleportation protocol introduces additional local gate operations, increasing the baseline error rate. In particular, the error of

FIG. 8. Remote physical two-qubit gate error rate. Remote physical two-qubit gate error rates used for transversal gates in each architecture with  $d_{\text{code}} = 13$  and their error budgets. (a) Physical two-qubit gate error rates scaled by the number of physical qubits. \*\*SDQC (the dashed-dotted line) represents the case in which the entanglement pair preparation error has been eliminated via entanglement purification, corresponding to the optimistic scenario. (b, c) Error budgets of SDQC (b) and QCCD (c). The error is analyzed into three categories: gate operation error, ion loss, and decoherence. The blue line indicates the remote two-qubit gate error rate of Photonic DQC, where photonic entangling error is the dominant contribution.

photonic entangling is approximately two orders of magnitude larger than that of local two-qubit gates, resulting in significantly higher error rates in Photonic DQC architecture. In contrast, QCCD architecture requires only a single two-qubit gate after reconfiguring connectivity through qubit shuttling, yielding a lower gate error at a small scale.

As the number of qubits increases, the number of junctions along the shuttling path increases in the two shuttling-based architectures, which increases the operation error due to ion loss. In QCCD, these quantities scale approximately with the square root of the number of qubits [71], and the growing number of junctions becomes a dominant source of physical gate error as the system scales. In contrast, in SDQC, data qubits remain stationary and are thus immune to ion loss during shuttling. gate teleportation qubits used for remote operations do not carry any quantum circuit information prior to their entangling gate with the data qubits. As a result, they can be replaced with spare ones when ion loss occurs, significantly suppressing the chance of operational failure by ion loss, which scales exponentially with the number of spare qubits (see Appendix G). As a result, the error due to ion loss during entanglement distribution in SDQC becomes negligible, in contrast to QCCD. In addition, if sufficient time slack is available, the entanglement purification can be used to remove errors of entanglement generation, as indicated by the dashed-dotted line in Fig. 8 (\*\*SDQC).

The operational time also increases as the qubit number grows (see Section IVB), which introduces decoherence-induced error, particularly in large-scale systems. When evaluating decoherence-induced error, the entanglement distribution time, though hidden in the time cost by pipelining, still contributes, because the

qubit coherence decays during this interval. At extremely large scales (on the order of  $10^6$  data qubits), the scale-dependent gate error of shuttling-based architectures becomes comparable to that of Photonic DQC.

The three architectures exhibit distinct scaling behaviors in their remote two-qubit gate errors. SDQC depends only on decoherence, as gate teleporation qubits can be replaced when ion loss occurs. Because the decoherence contribution remains smaller than the operational error over a wide range of system sizes, scale-dependent growth becomes apparent only at very large scales. In contrast, QCCD experiences error growth across all scales due to shuttling-induced ion loss, whose error rate is comparable to operational error even at small system size. Decoherence further contributes to the overall error at large scales, though its impact remains secondary to shuttlinginduced loss. Photonic DQC shows no scale dependence, and hence its error rate remains constant with system size. However, the intrinsic photonic entangling error is substantially higher than the local operational achievable in trapped-ion systems.

In summary, although QCCD architecture achieves low gate error at small system sizes, as the system scales, SDQC outperforms it in the intermediate-to-large scale regime ( $1000 < n_{\rm ph} < 10^7$ ). Furthermore, the gate error of SDQC can be further suppressed by up to a factor of 1.33 through the use of entanglement purification during the pipelined distribution process.

### 2. Logical Gates with QEC cycles

A logical two-qubit gate is implemented based on transversal gates of parallel remote two-qubit gates, followed by QEC cycles. Based on the results of the previ-

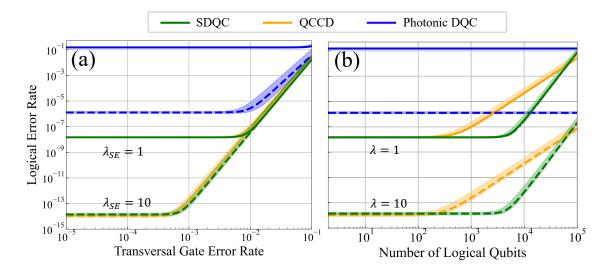

FIG. 9. Logical two-qubut gate error rate. Logical error rates  $p_{\rm L}$  of transversal two-qubit gates followed by  $d_{\rm code}$  rounds of syndrome extraction for code distance  $d_{\rm code}=13$  across all architectures, computed based on the setup shown in Sec. IV A 5. (a) Logical error rates as a function of the transversal gate error rate  $(p_{\rm trans})$  for different operation improvement factors for syndrome extraction ( $\lambda_{\rm SE}=1,10$ ), where the fitting parameters in Table IX are used for extrapolation. The color bands represent the upper/lower bounds with the standard deviations of each parameter. (b) Logical error rates of each logical qubit as a function of the number of logical qubits, for different operation improvement factors  $\lambda=1,10$ . Here, the number of logical qubits determines  $p_{\rm trans}$  as described in Section IV C 1.

ous section and QEC simulations, we estimate how the logical error rate scales with system size for each architecture.

Figure 9(a) shows the obtained logical error rates as a function of the transversal gate error rate  $p_{\rm trans}$ , for code distance  $d_{\text{code}} = 13$  across all architectures. We analyze logical error rates with two operation improvement factors for syndrome extraction,  $\lambda_{SE} = 1$  and  $\lambda_{SE} = 10$ , representing the current performance and a tenfold enhancement in operation fidelity during syndrome extraction. Photonic DQC exhibits a broad plateau at a relatively high logical error rate, indicating that its performance is limited by errors in syndrome extraction. This limitation arises because segmented stabilizers for Photonic DQC are measured using entangled qubits mediated by photonic interconnections, whose relatively low entanglement fidelity leads to a high logical error rate of  $6.36^{+1.19}_{-1.02} \times 10^{-7}$  for the  $\lambda_{\rm SE}=10$  case. In contrast, both SDQC and QCCD achieve significantly lower logical error rates in the syndrome extraction dominated regime, yielding  $6.89^{+1.93}_{-1.55} \times 10^{-15}$  and  $5.41^{1.62}_{-1.28} \times 10^{-15}$  at  $\lambda_{\rm SE} = 10$ , respectively. The corresponding crossover points  $p^*_{\rm trans}$  for SDQC are  $6.46^{+0.91}_{-1.17} \times 10^{-3}$  and  $5.63^{+1.21}_{-1.72} \times 10^{-4}$ for  $\lambda_{\rm SE} = 1$  and 10, respectively, whereas the currently available two-qubit gate fidelities lie below these crossover points.. This implies that further improving the transversal gate error rate below  $p_{\text{trans}}^*$  would not yield additional gains in logical performance.

From the simulation results, we estimate how the logical error rate scales with the system size for each architecture, as shown in Fig. 9(b). Here, the transversal gate error rate is taken from the remote two-qubit gate error