# Mapping code on Coarse Grained Reconfigurable Arrays using a SAT solver

Cristian Tirelli $^{1[0009-0002-5403-6255]}$  and Laura Pozzi $^{1[0000-0003-1083-8782]}$

Università della Svizzera Italiana, Switzerland {tirelc,pozzil}@usi.ch

Abstract. Emerging low-powered architectures like Coarse-Grain Reconfigurable Arrays (CGRAs) are becoming more common. Often included as co-processors, they are used to accelerate compute-intensive workloads like loops. The speedup obtained is defined by the hardware design of the accelerator and by the quality of the compilation. State of the art (SoA) compilation techniques leverage modulo scheduling to minimize the Iteration Interval (II), exploit the architecture parallelism and, consequentially, reduce the execution time of the accelerated workload. In our work, we focus on improving the compilation process by finding the lowest II for any given topology, through a satisfiability (SAT) formulation of the mapping problem. We introduce a novel schedule, called Kernel Mobility Schedule, to encode all the possible mappings for a given Data Flow Graph (DFG) and for a given II. The schedule is used together with the CGRA architectural information to generate all the constraints necessary to find a valid mapping. Experimental results demonstrate that our method not only reduces compilation time on average but also achieves higher quality mappings compared to existing SoA techniques.

**Keywords:** Compilers  $\cdot$  CGRA  $\cdot$  Hardware Accelerators  $\cdot$  SAT  $\cdot$  Modulo Scheduling  $\cdot$  Mapping  $\cdot$  Optimization

### 1 Problem Description

# 1.1 Introduction

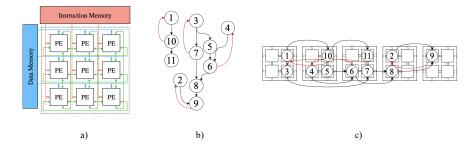

Achieving high efficiency with low power requirements is a recurring problem in hardware design and there are many architectures in the state-of-the-art trying to address this problem. A promising set of architectures that fits the specific are Coarse-Grain Reconfigurable Arrays (CGRAs) [7,6]. They are often used as co-processor to accelerate the most intensive part of a code, e.g. loops, and their most common structure is depicted in Figure 1.a. Typically, every Processing Element (PE) is connected with the nearest PE and is equipped with an Arithmetic-Logic Unit (ALU) and some internal registers. The PE network allows the exchange of data produced during the computation by the processing elements, while the connection to the main memory allows every PE to load

external data. Good code generation is necessary to enable high performance on this kind of architecture.

The key challenge in the compilation process is to find a space-time mapping that can fully exploit the intrinsic instruction-level parallelism offered by the architecture. Our research is currently focused on exploring new mapping techniques using a SAT-based approach [10,9], where constraints related to data dependency, architectural features, and scheduling are formulated as Boolean equations.

### 1.2 Mapping problem

Previous mapping techniques approached the problem in a different way. Some methods reduced the mapping problem to a graph theory problem [5, 3], while others solved the problem with linear programming [4]. However, many of these methods produced mappings of low quality, or alternatively, high-quality mappings but with significantly extended compilation times.

The CGRA mapping problem requires finding a valid space-time mapping from a DFG to the target CGRA architecture by entailing different challenges. In the context of CGRA this implies assigning the program instructions to the device PE and routing the data guaranteeing the functional correctness of the application. Figure 1.b depict a DFG and Figure 1.c shows a possible mapping of it on a  $2 \times 2$  CGRA, without applying modulo scheduling [8].

**Fig. 1.** a) Abstract  $3 \times 3$  CGRA architecture with 2d-mesh topology. b) Loop in DFG form. Red edges are loop-carried dependencies; black edges are data dependencies. c) One valid mapping of the DFG on the left in a  $2 \times 2$  CGRA

## 1.3 Modulo Scheduling

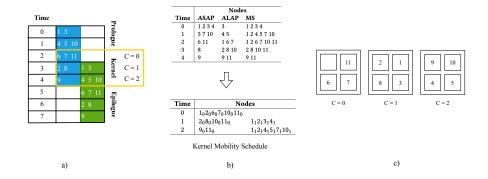

Modulo scheduling is a common compilation technique used to execute multiple iterations of a loop in an interleaved manner to reduce the execution time. After this optimization is applied, the code mapped on the device is divided into three sections: prologue, kernel and epilogue. As shown in Figure 3.a, Prologue and Epilogue are executed only once, while kernel is executed multiple times instead.

The length of the kernel is called Iteration Interval (II) and lower II corresponds to lower execution times. Minimizing the II is the objective of every mapping algorithm, since lower II corresponds to high-quality mappings. Figure 1.c shows how the DFG in Figure 1.b can be scheduled and mapped on a  $2 \times 2$  CGRA with an II of 3. The minimum iteration interval (mII) is computed according to the formula in [8], that is:

$$mII = max(ResII, RecII)$$

(1)

The first lower bound is given by the resource available on the CGRA and by the resource needed by the DFG,  $ResII = \left\lceil \frac{\#nodes_dfg}{\#PE} \right\rceil = \left\lceil \frac{11}{4} \right\rceil = 3$ . The second bound is given by the length of the longest loop l in the DFG,  $RecII = max \left( \left\lceil \frac{length(l)}{distance(l)} \right\rceil \right)_{l \in DFG} = 2$ .

According to equation 1 the lowest possible II for the DFG in Figure 1 is 3, so there is no possible better solution than the one shown in Figure 3.c.

# 2 Methodology

### 2.1 Compilation

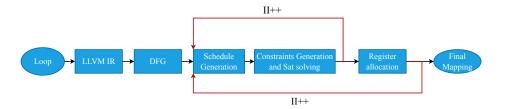

**Fig. 2.** SAT-MapIt tool-chain iteratively increases the II if no mapping is returned by the SAT solver or if the register allocation phase failed

The compilation process targets compute-intensive loops, which can be identified automatically or manually via pragma annotations. Since our research is focused more on the mapping phase, we manually mark the loops to be mapped with a pragma.

As shown in Figure 2 the first step of the compilation process we developed is to generate a semantically equivalent version of the loop with LLVM Intermediate Representation (LLVM IR) and from there extract the Data Flow Graph (DFG).

Next, in the Schedule Generation phase we introduce a novel schedule called Kernel Mobility Schedule (KMS), which is necessary to our SAT formulation to find the mapping with the lowest II. The first step to generate the KMS is the construction of the Mobility Schedule (MS). By using the As-Soon-As-Possible (ASAP) and As-Late-As-Possible (ALAP) schedules we create the MS, and then

#### 4 F. Author et al.

with a starting value for the II we iteratively fold the MS on itself by adding a label to every node after every folding. Figure 3.b shows this step applied to the graph in Figure 1.b. The KMS is then used with the DFG to generate the constraints the SAT solver needs to find a valid solution. Our formulation is register agnostic, so we need to have an additional phase, that is Register Allocation, to validate the output of the SAT solver.

**Fig. 3.** a) Modulo scheduling of the DFG in Figure 1.b, highlighting the division between prologue, kernel, and epilogue. b) Kernel Mobility Schedule generation. c) One valid mapping of the kernel on a  $2 \times 2$  CGRA.

### 2.2 Formulation

Our mapping methodology leverages the SAT solver's ability to efficiently navigate the problem's complex solution space. We encode the problem as conjunctive normal form (CNF) formula using literals in the form:  $x_{n,p,c,it}$ , where n denotes the node identifier in the DFG, p denotes a PE on the CGRA, c represents at which cycle a node is scheduled, and it to which iteration the node refers to. From an high-level point of view all statements can be divided in three main sets of clauses:

- C1: Each node is associated with a set of literals. Within each set, exactly one literal must be assigned as *True*.

- C2: Since a PE can only execute one instruction per cycle, at most one node can be mapped on a given PE at a given cycle.

- C3: Every node's predecessor and/or successor must be placed in a neighbour PE, to ensure that data can be shared through the PE network.

This formulation can also use modulo scheduling to reduce the execution time on the CGRA thanks to the Kernel Mobility Schedule. The full and more formal definition of the constraints is explained in detail in our recent work [9, 10].

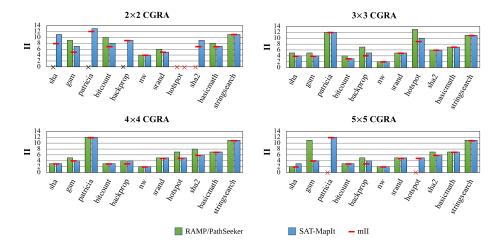

**Fig. 4.** Experimental results of the chosen benchmarks for 4 different CGRA sizes. We compare the best II obtained by RAMP and PathSeeker with the II found by our tool-chain SAT-MapIt. A red cross means that the process did not terminate before a timeout of 4000 seconds. A black cross means the process was terminated when it reached the max II allowed (50) without finding a feasible solution. Red dashes indicate the minimum II (mII). For the  $2 \times 2$  CGRA, hotspot had a mII of 17, which is not displayed.

# 3 Experimental Results

Using a set of benchmarks from MiBench and Rodinia, we compare our toolchain SAT-MapIt [10] against the SoA tools RAMP[5] and PathSeeker[1]. Figure 4 shows the II found by every tool for different CGRA sizes. Our methodology can explore the solution space fully and, consequentially, always return the best possible solution for every DFG considered.

It can be seen that SAT-MapIt outperforms the SoA in almost 50% of the benchmarks by finding mappings with low II. Compilation times are also lower on average in our experiments. In 26 out of 44 cases, our compilation time is is higher than the SoA, although the average time increase is only 15 seconds. While in the other cases, when our compilation times are lower, the time saved is on average 962 seconds.

# 4 Conclusion

During our research, we have introduced several novelties into the SoA. We proposed a new schedule called KMS and a novel SAT formulation that can exploit the modulo scheduling optimization technique to always return the best possible mapping for a given DFG. We also made open source the tool-chain (SAT-MapIt) [11] that implements all the steps needed to map on a CGRA. Our mapper's output is currently compatible with the *OpenEdgeCGRA* [2], but it can be easily adapted to any other architecture.

#### 4.1 Future work

The focus of our research is centered on compilation technique for CGRA and we are currently trying to further expand our methodology to support larger DFGs and CGRA sizes. However, we are also exploring promising emerging technologies, such as neuromorphic computing architectures, which currently require significant enhancements in compilation techniques.

**Acknowledgments.** This study is supported by the Swiss National Science Foundation under Grants: ML-Edge (200020-182009) and ADApprox (200020-188613).

### References

- Balasubramanian, M., Shrivastava, A.: PathSeeker: A Fast Mapping Algorithm for CGRAs. Proceedings of the Design, Automation and Test in Europe Conference and Exhibition (2022)

- Carpentieri, N., Sapriza, J., Schiavone, D., Jahier Pagliari, D., Atienza, D., Martina, M., Burrello, A.: Performance evaluation of acceleration of convolutional layers on openedgecgra. In: Workshop on Open-Source Hardware. pp. 1–4. ACM (2024)

- 3. Chen, L., Mitra, T.: Graph minor approach for application mapping on CGRAs. ACM Transactions on Reconfigurable Technology and Systems (TRETS) **7**(3), 1–25 (2014)

- 4. Chin, S.A., Anderson, J.H.: An Architecture-Agnostic Integer Linear Programming Approach to CGRA Mapping. In: Proceedings of the 55th Design Automation Conference. pp. 1–6 (2018)

- 5. Dave, S., Balasubramanian, M., Shrivastava, A.: RAMP: Resource-Aware Mapping for CGRAs. In: Proceedings of the 55th Design Automation Conference. pp. 1–6. IEEE (2018)

- Karunaratne, M., Mohite, A.K., Mitra, T., Peh, L.S.: HyCUBE: A CGRA with reconfigurable single-cycle multi-hop interconnect. In: Proceedings of the 54th Design Automation Conference. pp. 1–6 (2017)

- 7. Li, Z., Wijerathne, D., Chen, X., Pathania, A., Mitra, T.: ChordMap: Automated Mapping of Streaming Applications onto CGRA. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (2021)

- 8. Rau, B.R.: Iterative Modulo Scheduling. International Journal of Parallel Programming 24(1), 3–64 (1996)

- Tirelli, C., et al.: SAT-based Exact Modulo Scheduling Mapping for Resource-Constrained CGRAs. In: Journal on Emerging Technologies in Computing Systems. pp. 1–26. ACM (2024)

- 10. Tirelli, C., Ferretti, L., Pozzi, L.: SAT-MapIt: A SAT-based Modulo Scheduling Mapper for Coarse Grain Reconfigurable Architectures. In: 2023 Design, Automation & Test in Europe Conference & Exhibition (DATE). pp. 1–6 (2023). https://doi.org/10.23919/DATE56975.2023.10137123

- 11. Tirelli, C., Ferretti, L., Pozzi, L.: Sat-MapIt: An Open Source Modulo Scheduling Mapper for Coarse Grain Reconfigurable Architectures. Proceedings of the 20th ACM International Conference on Computing Frontiers pp. 383—384 (2023)