# Fabrication and Properties of NbN/NbN<sub>x</sub>/NbN and Nb/NbN<sub>x</sub>/Nb Josephson Junctions

Sergey K. Tolpygo, *Senior Member, IEEE*, Ravi Rastogi, David Kim, Terence J. Weir, Neel Parmar, and Evan B. Golden

Abstract-Increasing integration scale of superconductor electronics (SCE) requires employing kinetic inductors and selfshunted Josephson junctions (JJs) for miniaturizing inductors and JJs. We have been developing a ten-superconductor-layer planarized fabrication process with NbN kinetic inductors and searching for suitable self-shunted JJs to potentially replace high Josephson critical current density, Jc, Nb/Al-AlOx/Nb junctions. We report on the fabrication and electrical properties of NbN/NbNx/NbN junctions produced by reactive sputtering in Ar+N<sub>2</sub> mixture on 200-mm wafers at 200 °C and incorporated into a planarized process with two Nb ground planes and Nb wiring layer. Here NbN is a stoichiometric nitride with superconducting critical temperature  $T_c = 15 \text{ K}$  and NbN<sub>x</sub> is a high resistivity, nonsuperconducting nitride deposited using a higher nitrogen partial pressure than for the NbN electrodes. For comparison, we co-fabricated Nb/NbNx/Nb JJs using the same NbNx barriers deposited at 20 °C. We varied the NbNx barrier thickness from 5 nm to 20 nm, resulting in the range of  $J_c$  from about 1 mA/μm<sup>2</sup> down to ~10 μA/μm<sup>2</sup>, and extracted coherence length of 3 nm and 4 nm in NbN<sub>x</sub> deposited, respectively at 20 °C and 200 °C. Both types of JJs are well described by resistively and capacitively shunted junction model without any excess current. We found the J<sub>c</sub> of NbN/NbN<sub>x</sub>/NbN JJs to be somewhat lower than of Nb/NbNx/Nb JJs with the same barrier thickness, despite a much higher T<sub>c</sub> and energy gap of NbN than of Nb electrodes.  $I_cR_n$  products up to ~ 0.5 mV were obtained for JJs with  $J_{c} \sim 0.6 \text{ mA/}\mu\text{m}^2$ .  $J_{c}(T)$  dependences have been measured.

Index Terms—Josephson junctions, niobium nitride, SNS junctions, superconductor digital electronics, superconducting integrated circuits, superconductor-insulator-superconductor devices, superconductor-normal metal-superconductor devices

# I. INTRODUCTION

NCREASING integration scale of superconductor electronics (SCE) toward levels needed for advanced computations requires employing kinetic inductors instead of geometrical ones and self-shunted Josephson junctions (JJs) instead of externally shunted ones in order to enable miniaturization of these crucial components of superconductor integrated circuits [1], [2], [3]. During the last several years,

This material is based upon work supported by the Under Secretary of War for Research and Engineering under U.S. Air Force Contract No. FA8702-15-D-0001. (Corresponding author: Sergey K. Tolpygo).

All the authors are with Lincoln Laboratory, Massachusetts Institute of Technology, Lexington, MA 02421, USA (emails: <a href="mailto:sergey.tolpygo@ll.mit.edu">sergey.tolpygo@ll.mit.edu</a>; <a href="mailto:david.kim@ll.mit.edu">david.kim@ll.mit.edu</a>; <a href="mailto:weir@ll.mit.edu">weir@ll.mit.edu</a>; <a href=

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org

we have been developing at MIT Lincoln Laboratory (MIT LL) a ten-superconductor-layer process incorporating NbN and bilayer NbN/Nb kinetic inductors above the layer of Josephson junctions, the SFQ7ee process [3], [4]. At the same time, we have been searching for suitable self-shunted Josephson junctions to replaced externally shunted Nb/Al-AlO<sub>x</sub>/Nb JJs which are otherwise hysteretic at all  $J_c$  values used in the existing MIT LL process nodes up to about 0.6 mA/ $\mu$ m<sup>2</sup>. The self-shunted JJs should satisfy at least three requirements in addition to the scalability requirement:

- a) have sufficiently high  $I_cR_n$  products to support high clock rates which make SCE digital circuits, along with ultralow energy dissipation, competitive with semiconductor CMOS circuits;  $I_c$  is the junction critical current and  $R_n$  is the internal damping resistance.

- b) The minimum  $I_c$  of the JJs,  $I_{c,min}$  should be small enough to provide the ultralow energy dissipation and be limited from below only by the acceptable bit error rate of the circuits, e.g.,  $I_{c,min} \sim 50 \, \mu A$ . This sets the minimum required Josephson current density  $J_{c,min} = I_{c,min}/A_{J,min}$ , where  $A_{J,min}$  is the minimum fabrication-process-defined junction area.

- c) The most difficult requirement comes from the need to match impedance of the JJs and the wave impedance,  $Z_0$  of passive transmission lines (PTLs) providing onchip and chip-to-chip data transfer. For instance, the standard superconducting striplines in the SFQ5ee fabrication process at MIT LL have  $Z_0 \approx 10~\Omega$  at  $w=2~\mu m$  [5], where w is the stripline width. To enable a very large-scale integration (VLSI), it is highly desirable the PTL width to be in the micrometer or even sub-micrometer range. Since  $Z_0$  scales approximately as 1/w, impedance matching requires JJs with high  $R_n$  and  $R_n A_I$  product.

These requirements are relatively easy to satisfy using JJs with medium-to-high transparency tunnel barriers, having  $I_c R_n \sim 1$  mV at  $j_c \sim 1$  mA/ $\mu$ m<sup>2</sup> [6]. In this case,  $A_{J,min} \sim 0.05$   $\mu$ m<sup>2</sup> is provided by circular JJs with diameter  $d_{min} \sim 0.25$   $\mu$ m, having  $R_{n,max} = I_c R_n/I_{c,min} \sim 20$   $\Omega$  that matches  $Z_0$  of striplines with  $w \approx 0.8$   $\mu$ m; see [5, Fig. 4].

On the other hand, these requirements are practically impossible to satisfy using SNS-type JJs, where N is a normal metal, or using highly disordered, high resistivity materials and doped semiconductors with low carrier concertation and resonant tunneling type conduction as the N-barrier; see, e.g.

[7], [8], [9], [10], [11], [12], [13], [14], [15]. In the sandwichand bridge-type JJs, the only adjustable parameters are the barrier thickness (bridge length), t and the barrier (bridge) material resistivity,  $\rho_n$ . The junction resistance  $R_nA_J$  is proportional to t while  $j_c$  exponentially decreases with increasing t as  $\exp(-t/\xi_n)$ , where  $\xi_n$  is the coherence length in the barrier, which also decreases with increasing the barrier resistivity as approximately  $\rho_n^{-1/2}$ . In the high resistivity barriers,  $\xi_n$  becomes very short, a few nanometers. Therefore, it is practically impossible to achieve simultaneously the required high values of  $R_n$ ,  $j_c$ , and  $I_cR_n$  in the same junction.

To escape from the described conundrum, the authors of [16] proposed a bridge-type JJ with an additional adjustment relying on the contact resistance,  $R_c$  between the dissimilar N and S materials in their overlap area that can be changed independently of the N-bridge cross section. The total junction resistance  $R_n = 2R_c + R_{bridge}$  could then be made dominated by the  $R_c$  while the critical current mainly determined by the bridge length and  $\xi_n$ . Although interesting theoretically, such a JJ structure does not appear to be more practical, scalable or reproducible that the regular trilayer tunnel barrier junctions [17] from the fabrication standpoint. It requires a highly reproducible fabrication of more features than a tunnel JJ: a deep submicron-scale planar bridge, and two high-contactresistance interfaces between the N and S materials with tightly controlled overlap area, which are the analog of two sandwich iunctions.

In the SFQ7ee process node, JJs are directly contacted by the NbN kinetic inductance layer; see [3, Fig. 12] and [15, Fig. 1]. To eliminate any potential junction degradation caused by diffusion of nitrogen into the JJ top (counter) electrode during NbN deposition at elevated temperatures or other causes related to processing dissimilar wiring layer and counter electrode metals, we investigated Josephson junctions with NbN electrodes. Because of a limited number of deposition chambers and sputtering targets in our PVD deposition cluster, we utilized a nonsuperconducting, high resistivity NbN<sub>x</sub> as a barrier material [15] in NbN/NbN<sub>x</sub>/NbN trilayer junctions. For comparison, we fabricated in the same process run also Nb/NbN<sub>x</sub>/Nb trilayer junctions.

# II. FABRICATION OF NBN/NBN $_{\rm x}$ /NBN and NB/NBN $_{\rm x}$ /NB Trilayer Junctions

All trilayers were deposited in an Endura PVD (Applied Materials, Inc.) cluster using magnetron sputtering on 200 mm oxidized Si wafers containing a patterned 200-nm-thick Nb layer (layer M4 in our nomenclature) covered by a 200-nm-thick planarized layer of SiO<sub>2</sub> interlayer dielectric. The deposition parameters for Nb, NbN, and NbN<sub>x</sub> films are given in Table I. The thickness of the bottom and top electrodes of the JJs was 150 nm for both NbN and Nb electrodes. The resistivity data in Table I were calculated using the average of the sheet resistance measured in 49 points on the witness films deposited on SiO<sub>2</sub>-coated 200-mm wafers. The SiO<sub>2</sub> film was deposited using Plasma-Enhanced Chemical Vapor Deposition (PECVD).

$\label{eq:table_interpolation} TABLE\ I$  Deposition Parameters of Nb, NbN, and NbNx Films

| Material and junction type                                      | Power<br>(kW) | Pressure<br>(mT) | Ar flow<br>(seem) |     | N <sub>2</sub> partial<br>pressure,<br>N <sub>2</sub> /(N <sub>2</sub> +Ar) | Deposition<br>temperature<br>(°C) | Film<br>thickness<br>(nm) | Рзовк<br>(μΩ ст) | $RRR = R_{300}/R_{T>T_c}$ |

|-----------------------------------------------------------------|---------------|------------------|-------------------|-----|-----------------------------------------------------------------------------|-----------------------------------|---------------------------|------------------|---------------------------|

| Nb film                                                         | 1.2           | 4                | 40                | N/A | N/A                                                                         | 20                                | 200                       | 19.6             | 4.7                       |

| NbN film                                                        | 1.5           |                  | 60                | 20  | 0.25                                                                        | 200                               | 200                       | 190.6            | ~1                        |

| NbN <sub>x</sub> barrier<br>film for<br>Nb/NbN <sub>x</sub> /Nb | 1.5           |                  | 10                | 95  | 0.905                                                                       | 20                                | 50                        | 925°             | 0.47                      |

| NbN <sub>x</sub> film for<br>NbN/NbN <sub>x</sub> /NbN          | 1.0           |                  | 10                | 150 | 0.938                                                                       | 200                               | 20                        | 1018b            | 0.586                     |

<sup>a</sup>Measured on a film deposited on PECVD SiO₂ on Si wafer <sup>b</sup>Measured on a film deposited on PECVD SiO₂ on Si wafer

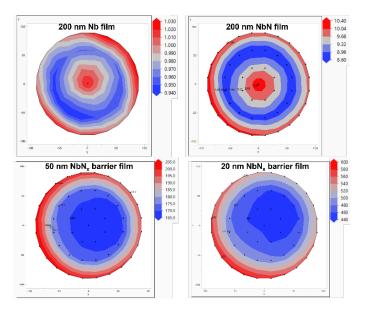

Fig. 1. Sheet resistance wafermaps at room temperature for the typical Nb, NbN, and NbN<sub>x</sub> films used in the fabrication of Josephson junctions. Deposition parameters for these films are given in Table I.

The typical sheet resistance wafermaps for the Nb and NbN films used for junction electrodes are shown in Fig. 1 (top row). These wafermaps have nearly cylindrical symmetry with the radial variation reflecting the sputtering rate pattern of a circular magnetron. The films are thinner near the rim and in the center of the wafers and thicker in the middle. The mean values are  $0.987 \Omega$ /sq and  $9.54 \Omega$ /sq for Nb and NbN, respectively, with standard deviations,  $1\sigma_R$  of 0.029  $\Omega$ /sq and 0.635  $\Omega$ /sq. The total variation range, from the minimum to the maximum value, for the Nb film is from 0.94 to 1.03  $\Omega$ /sq and from 8.56 to 10.35  $\Omega$ /sq for the NbN film. Both ranges closely correspond to  $3\sigma_R$ . The relative variation  $1\sigma_R/R_{mean}$  increases from about 3% for Nb to 6.7% for NbN films. This is a result of the sputtering gas mixture delivery and distribution in the Endura PVD sputtering chambers which, strictly speaking, are not designed and optimized for reactive sputtering.

It is well known that increasing nitrogen content in Ar+ $N_2$  sputtering gas mixture above the optimum composition for producing NbN film with  $T_c$  in the range from 14 to 16 K increases the film resistivity and eventually results in high-resistivity, nonsuperconducting NbN<sub>x</sub> (x>1) films [4], [15].

Fig. 2. Scanning Transmission Electron Microscope (STEM) images of the cross sections of Nb/NbN<sub>x</sub>/Nb (left, top) and NbN/NbN<sub>x</sub>/NbN (left bottom and right) junctions. A top via to the junction's counter electrode (CE) was etched in the SiO<sub>2</sub> dielectric planarizing the junction mesa, and either Nb or NbN interconnect layer was deposited and patterned.

Because of a limited number of different sputtering targets that can be accommodated in the same PVD cluster, we decided to use the high-resistivity NbN<sub>x</sub> films as the junction barrier [15].

We used slightly different parameters for depositing the barrier in NbN/NbN<sub>x</sub>/Nb and in Nb/NbN<sub>x</sub>/Nb trilayer junctions. NbN films with  $T_c \approx 15$  K require deposition at 200 °C and, hence, the NbN<sub>x</sub> barrier films were deposited at the same temperature. In contrast, our Nb films are deposited at room temperature. To prevent their potential degradation at the interface with NbN<sub>x</sub> due to nitrogen diffusion at elevated temperatures, the NbN<sub>x</sub> barrier on Nb electrodes was deposited also at room temperature. Consequently, the sputtering power and gas mixture were adjusted to obtain nearly the same NbN<sub>x</sub> film resistivity as for the NbN<sub>x</sub> films deposited at 200 °C; see Table I.

The barrier film thickness was varied from 5 nm to 20 nm by adjusting the deposition time. The typical sheet resistance wafermaps for the NbN<sub>x</sub> films are shown in Fig. 1 (bottom row). These wafermaps are not as symmetrical as the stoichiometric NbN films and also show larger sheet resistance variations. For the 50-nm NbN<sub>x</sub> film deposited at 20 °C:  $R_{mean} = 185.0 \,\Omega/\text{sq}$ ,  $1\sigma_R = 14.7 \,\Omega/\text{sq}$ ,  $1\sigma_R/R_{mean} = 7.9\%$ , and the min-to-max range is from 166 to 206  $\Omega/\text{sq}$ . For the 20-nm NbN<sub>x</sub> film deposited at 200 °C:  $R_{mean} = 509.5 \,\Omega/\text{sq}$ ,  $1\sigma_R = 46.7 \,\Omega/\text{sq}$ ,  $1\sigma_R/R_{mean} = 9.2\%$ , and the min-to-max range is from 447.8 to 587.3  $\Omega/\text{sq}$  or  $3\sigma_R$ .

The described nonuniformities are caused mainly by the film thickness and nitrogen content nonuniformities. The latter slightly increases from the center toward the edges of wafer because of the way  $N_2$  and Ar are delivered and distributed in the Endura PVD chamber. It is possible that the thickness nonuniformity increases even more with decreasing the average film thickness but we have not investigated this issue. The barrier thickness uniformity directly affects the uniformity of the Josephson critical current density on the wafers,  $j_c$  which will be presented in the next section. From the sheet resistance data in Fig. 1, the  $j_c$  uniformity is not expected to be great and expected to be worse than for  $Nb/Al-AlO_x/Nb$  tunnel junctions having the min-to-max  $j_c$  variation of less than 10% [18], [19].

STEM images of the fabricated junctions are shown in Fig. 2.

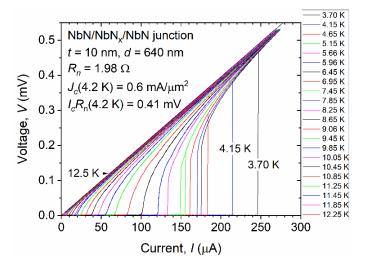

Fig. 3. I-V characteristics of a NbN/NbN $_x$ /NbN junctions with t =10 nm NbN $_x$  barrier at different temperatures from 3.70 K to 12.25 K, from right to left in the graph. The critical temperature of NbN electrodes is  $T_c$  =14.8 K. Above  $\sim$  9 K, the I-V characteristics become noticeably affected by thermal noise.

The junction fabrication is similar to the fabrication of Nb/Al-AlOx/Nb junctions in [3], [20], except that we used shallow top vias to the junctions' counter (top) electrode (CE), which were etched in the SiO<sub>2</sub> dielectric planarizing the junction mesa after pattering the CE and the base (bottom) electrode (BE) of the junctions. Junction anodization processed used to protect the tunnel barrier in Nb/Al-AlOx/Nb junctions [20] was not used for NbN<sub>x</sub>-barrier junctions. Optical emission end-point detection and timed overetching was used to stop the etching on the base electrode after etching through the NbN<sub>x</sub> barrier. This overetching roughens the top surface of the remaining NbN base electrode outside the junctions as visible in the cross section in the left part of Fig. 2.

# III. ELECTRICAL TESTING RESULTS

# A. Current-Voltage (I-V) Characteristics

Current-voltage characteristics (CVCs) of the junctions were measured using both a liquid helium immersion probe and a closed cycle cryocooler. The typical I-V characteristics of a circular NbN/NbN $_x$ /Nb junction with diameter d =680 nm and the barrier thickness t =10 nm at various temperatures from 3.70 K to 12.25 K are shown in Fig. 3. At low temperatures, the junctions with this and lower barrier thicknesses are hysteretic with the Stewart-McCumber parameter  $\beta_c = 2\pi I_c R_n^2 C/\Phi_0 > 1$ , where C is the junction capacitance and  $\Phi_0$  the flux quantum. Hysteresis quickly disappears with increasing temperature because the critical current decreases and  $\beta_c$  becomes less than 1; see below.

CVCs of the junctions with thicker barriers are nonhysteretic at 4.2 K as shown in Fig. 4 for NbN/NbN<sub>x</sub>/NbN junctions with t=15 and 20 nm. The junctions are well described by the RCSJ model without any excess current. CVCs of all junctions with t=20 nm can be fitted very well by the resistively shunted junction (RSJ) model  $V=V_c(i^2-1)^{1/2}$ , where  $V_c=I_cR_n$  and  $i=I/I_c$ , neglecting the junction capacitance and indicating that

Fig. 4. I-V characteristics of the circular NbN/NbN<sub>x</sub>/NbN junctions with t=15 nm (wafer w18, location B3) and t=20 nm (wafer w20, location B3) NbN<sub>x</sub> barriers at LHe temperature. At this barrier thickness, the junctions are nonhysteretic and are well described by the RSCJ model without any excess current.

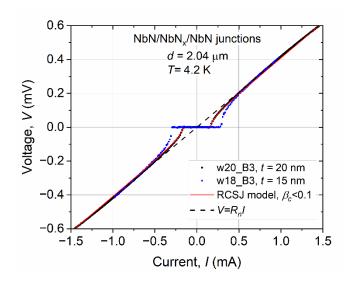

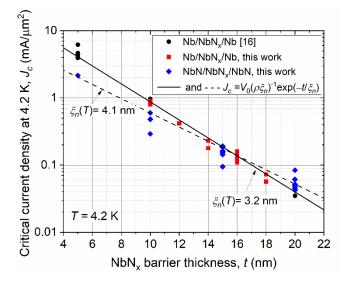

Fig. 5. Dependences of the Josephson critical current density at 4.2 K of Nb/NbN<sub>x</sub>/Nb and NbN/NbN<sub>x</sub>/NbN Josephson junctions on the thickness of the NbN<sub>x</sub> barriers. The data for Nb/NbNx/Nb junctions from [16], fabricated with the same NbN<sub>x</sub> deposition parameters, were also included. Solid and dashed lines are dependences (1). For Nb/NbN<sub>x</sub>/Nb JJs (solid line), parameters  $V_0$ ,  $\xi_n(4.2\text{K})$  and the barrier resistivity values are identical to those determined in [16]:  $V_0 = 4.4 \text{ mV}$ ,  $\xi_n(4.2\text{K}) = 3.2 \text{ nm}$ ,  $\rho = 0.0071 \,\Omega \cdot \text{cm}$ . The dash line corresponds to  $V_0 = 2.0 \,\text{mV}$ ,  $\xi_n(4.2\text{K}) = 4.1 \,\text{nm}$ , and  $\rho = 0.0071 \,\Omega \cdot \text{cm}$ , and seems to better describe NbN/NbN<sub>x</sub>/NbN JJs.

# $\beta_c \lesssim 0.1$ ; see solid red curve in Fig. 4.

CVCs and parameters of the fabricated  $Nb/NbN_x/Nb$  junctions were nearly identical to those presented in [16] and will not be repeated here.

# B. Scaling of $J_c$ and $I_cR_n$ with Barrier Thickness

Dependences of the Josephson critical current density on the barrier thickness are shown in Fig. 5. For Nb/NbN<sub>x</sub>/Nb junctions, we used identical deposition parameters to those used in [16]. The solid line is the dependence

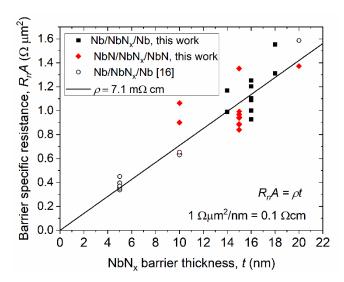

Fig. 6. Dependence of the junction specific resistance  $R_nA$  of Nb/NbN<sub>x</sub>/Nb and NbN/NbN<sub>x</sub>/NbN Josephson junctions on the thickness of the NbN<sub>x</sub> barriers. The data for Nb/NbN<sub>x</sub>/Nb junctions from [16], fabricated with the same NbN<sub>x</sub> deposition parameters, were also included.

$$J_c = \frac{V_0}{\rho \xi_n(T)} \exp\left(-\frac{t}{\xi_n(T)}\right) \tag{1}$$

following from the basic theory of SNS junctions [22], [23]. We used parameters  $V_0$  =4.4 mV,  $\xi_n(4.2\text{K})$  = 3.2 nm, the barrier resistivity  $\rho$  = 0.0071  $\Omega$ ·cm, very similar to those previously determined in [16] for the NbN<sub>x</sub> barriers deposited at 20°C using N<sub>2</sub>/(N<sub>2</sub>+Ar)=0.905, the same as in this work. The data [16] obtained in 2022 and the new data agree very well indicating a good repeatability of the junction fabrication process.

The spread of the  $j_c$  and junction resistance  $R_nA$  values in Figs. 5,6 is caused by the variation of these parameters across the wafers as will be discussed separately.

Note also a factor of  $\sim 3x$  difference between the extracted resistivity of the NbN<sub>x</sub> barrier of about 7 m $\Omega$  cm and the inplane resistivity of NbN<sub>x</sub> films in Table I and Fig. 1.

#### C. Across-Wafer Variation of $I_c$

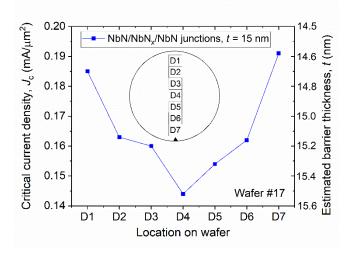

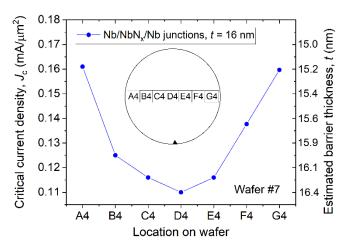

Fig. 7 shows the typical variation of the Josephson critical current density of NbN/NbNx/NbN junction on 200-mm wafers. Twelve JJs with diameters from 0.7  $\mu$ m to 2.2  $\mu$ m were measured at each location specified in Fig. 7, and  $j_c$  was determined from the slope of the linear dependence  $I_c^{1/2} = (\frac{\pi j_c}{4})^{1/2}d$ . The observed center-to-edge change in  $j_c$  is about 34%. This change is caused by the center to edge variation of the barrier thickness which is seeing in the wafermaps in Fig. 1. Because of the very short coherence length in the barrier, even small changes in the deposited barrier thickness can cause large changes in the  $j_c$ . The observed change in  $j_c$  in Fig. 7 requires only 1 nm change in t from center-to-edge, as shown by the right axis in Fig. 7. The similar across-wafer radial variation of  $j_c$  was also found for Nb/NbN<sub>x</sub>/Nb junctions and shown in the bottom panel in Fig. 7.

The observed variation can be reduced by improving the

Fig. 7. The typical across-the-wafer variation of the critical current density of NbN/NbN<sub>x</sub>/NbN (top panel, variation along the y-axis) and Nb/NbN<sub>x</sub>/Nb (bottom panel, variation along the x-axis) Josephson junctions with reactively sputtered NbN<sub>x</sub> barriers with the nominal thickness of 15 nm and 16 nm, respectively. The right axis in both panels shows the estimated variation of the barrier thickness based on (1) with the coherence length extracted from the data in Fig. 5. The measurements were done on a junction test chip located on each 22 mm x 22 mm process control monitor (PCM) die corresponding to a 7x7 exposure matrix (A,B,...,G; 1,2,...,7) of a 248-nm Canon EX4 stepper used for the junction photolithography.

barrier film thickness uniformity. This could possibly be done using a deposition system with wafer rotation and improved sputtering gas mixture distribution. For instance, for 40 nm Mo<sub>2</sub>N films used as kinetic inductors [2], we were able to achieve the thickness standard deviation of  $1\sigma = 2\%$  on 200-mm wafers, using a Connexion PVD tool from Veeco Instruments Inc. Nevertheless, a 2% thickness variation for the 10 nm barrier would result into more than 10% standard deviation of the  $j_c$ .

### D. Temperature Dependence of the Critical Current

Yet another important characteristic for JJ applications in VLSI circuits is temperature dependence of the critical current,  $I_c(T)$  in the temperature range of the circuit operation. Due to unavoidable heat generation during the circuit operation and poor thermal conductivity in multilayered

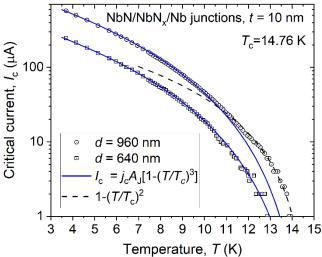

Fig. 8. The typical temperature dependence of the critical current of NbN/NbN<sub>x</sub>/NbN Josephson junctions with reactively sputtered NbN<sub>x</sub> barrier with the nominal thickness of 10 nm. Solid and dash curves show  $1 - (T/T_c)^3$  and  $1 - (T/T_c)^2$  dependences, respectively.

stacks, temperature of the circuit or of its parts may rise decreasing  $I_c$ . To remain operational, the critical current change  $\Delta I_c/I_c$  must be smaller than some value determined by the circuit design, typically less than 20-30%. Hence, using junctions with a weak  $I_c(T)$  dependence near the operating temperature allows for a higher on-chip heat dissipation and larger integration scale, and gives larger operating margins than using JJs with a strong  $I_c(T)$  dependence.

Fig. 8 shows the typical  $I_c(T)$  dependence for NbN/NbN<sub>x</sub>/NbN JJs with 10 nm barriers. In almost the entire temperature range from 4 K to ~ 13 K, the critical current strongly decreases with temperature as  $I_c(T) \propto 1 - (T/T_c)^3$ . Only very close to  $T_c$ , at  $T/T_c \gtrsim 0.8$ , the dependence becomes closer to  $1 - (T/T_c)^2$  which is expected for the SNS and other proximity effect junctions with thick barriers,  $t > \xi_N$  [22], [23], [24], [25]. Contrary to this strong dependence,  $I_c$  of SIS junctions becomes almost temperature independent at  $T \lesssim T_c/2$  [25], [26], [27]. For a comparison of the  $I_c(T)$  dependence of Nb/NbN<sub>x</sub>/Nb and Nb/Al-AlO<sub>x</sub>/Nb junctions see [16].

# V. CONCLUSION

In conclusion, we investigated NbN/NbN<sub>x</sub>/NbN and Nb/NbN<sub>x</sub>/Nb self-shunted Josephson junctions to evaluate whether they can potentially replace Nb/Al-AlO<sub>x</sub>/Nb tunnel barrier junctions with high transparency barriers. We find that, unfortunately, all proximity-type junctions with deposited barriers demonstrate many features that make them inferior to the tunnel barrier junctions for applications in VLSI integrated circuits: larger nonuniformity of the properties across the wafers, lower  $I_c R_n$  products, and stronger temperature dependence of the junction critical current.

Because of relatively low  $I_cR_n$  products and a substantial  $I_c(T)$  dependence, the best potential application of the

proximity-type junctions with deposited barriers, in our view, is in adiabatic quantum flux parametron (AQFP) circuits [28]. AQFPs do not require high  $I_cR_n$  products because they, anyway, need to operate at frequencies below ~7 GHz to be in the adiabatic regime [28]. Energy dissipation in AQFPs circuits is extremely low [29] and the circuit density is low as well [30], resulting in the extremely low heat power densities and making a potential temperature rise during the AQFP circuits operation the smallest possible among all other types of superconductor logics.

For the next round of NbN junctions development, we are planning to utilize the Connexion PVD tool providing about 2% barrier thickness nonuniformity. Unfortunately, we have not been able to get access to and evaluate commercial PVD, chemical vapor deposition (CVD), and atomic layer deposition (ALD) tools capable of achieving a variation in reactive growth of 1% or less. Theoretically, a custom system could be designed and built to alleviate the thickness variation constraint if necessary. One of the purposes of this work has been determining if such an investment of funds and labor is warranted based on the characteristics of the deposited-barrier junctions.

#### ACKNOWLEDGMENT

The STEM imaging of the junctions was done at the Center for Functional Nanomaterials at Brookhaven National Laboratory. We are very grateful to Kim Kisslinger for making the junction cross sections and taking the STEM images.

Any opinions, findings, conclusions, or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the Under Secretary of Defense for Research and Engineering or the U.S. Government. Notwithstanding any copyright notice, U.S. Government rights in this article are defined by DFARS 252.227-7013 or DFARS 252.227-7014 as detailed above. Use of this article other than as specifically authorized by the U.S. Government may violate any copyrights that exist in this article. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright annotation thereon.

#### REFERENCES

- [2] S.K. Tolpygo, "Superconductor digital electronics: Scalability and energy efficiency issues (Review Article), *Low. Temp. Phys.*, vol. 42, pp. 361-379, May 2026, doi: 10.10631/1.4948618

- [3] S. K. Tolpygo et al., "Superconductor electronics fabrication process with MoN<sub>x</sub> kinetic inductors and self-shunted Josephson junctions," *IEEE Trans. Appl. Supercond.*, vol. 28, no. 4, Jun. 2018, Art no. 1100212, doi: 10.1109/TASC.2018.2809442.

- [4] S. K. Tolpygo, "Scalability of superconductor electronics: Limitations imposed by AC clock and flux bias transformers," *IEEE Trans. Appl. Supercond.*, vol. 33, no. 2, Mar. 2023, Art no. 1300419, doi: 10.1109/TASC.2022.3230373.

- [5] S. K. Tolpygo et al., "Progress toward superconductor electronics fabrication process with planarized NbN and NbN/Nb layers," IEEE Trans. Appl. Supercond., vol. 33, no. 5, Aug. 2023, Art no. 1101512, doi: 10.1109/TASC.2023.3246430.

- [6] S. K. Tolpygo, E.B. Golden, T.J. Weir, and V. Bolkhovsky, "Inductance of superconductor integrated circuit features with sizes down to 120 nm," *Supercond. Sci. Technol.*, vol. 34, no. 8, Jun. 2021, Art. no 085005, doi: 10.1088/1361-6668/ac04b9.

- [7] S. K. Tolpygo et al., "Properties of unshunted and resistively shunted Nb/AlO<sub>x</sub>-Al/Nb Josephson junctions with critical current densities from 0.1 to 1 mA/μm²," *IEEE Trans. Appl. Supercond.*, vol. 27, no. 4, June 2017, Art no. 1100815, doi: 10.1109/TASC.2017.2667403.

- [8] H. Kroger, C. Potter, and D. Jillie, "Niobium Josephson junctions with doped amorphous silicon barriers," *IEEE Trans. Magnetics*, vol. 15, no. 1, pp. 488-489, January 1979, doi: 10.1109/TMAG.1979.1060117.

- [9] L. Smith, J. Thaxter, D. Jillie and H. Kroger, "Sputtered a-silicon tunneling barriers for Nb-Nb Josephson junctions," *IEEE Trans. Magnetics*, vol. 18, no. 6, pp. 1571-1576, Nov. 1982, doi: 10.1109/TMAG.1982.1062214.

- [10]A.L. Gudkov, M.Y. Kupriyanov, and K.K. Likharev, "Properties of Josephson junctions with amorphous-silicon interlayers," Sov. Phys. JETP, vol. 68, no. 1, pp. 178-1485, July 1988.

- [11] A.L. Gudkov, M.Y. Kupriyanov, and A.N. Samus', "Properties of planar Nb/α-Si/Nb Josephson junctions with various degrees of doping of the α-Si layer," *J. Exp. Theor. Phys.*, vol. 114, no. 5 pp. 818–829, June 2012. https://doi.org/10.1134/S1063776112030144 and references therein.

- [12] B. Baek, P. D. Dresselhaus and S. P. Benz, "Co-sputtered amorphous Nb<sub>x</sub>Si<sub>1-x</sub> barriers for Josephson-junction circuits," *IEEE Trans. Appl. Supercond.*, vol. 16, no. 4, pp. 1966-1970, Dec. 2006, doi: 10.1109/TASC.2006.881816.

- [13] D. Olaya, B. Baek, P. D. Dresselhaus, and S. P. Benz, "High-speed Nb/Nb–Si/Nb Josephson junctions for superconductive digital electronics," *IEEE Trans. Appl. Supercond.*, vol. 18, no. 4, pp. 1797-1800, Dec. 2008, doi: 10.1109/TASC.2008.2007652

- [14] D. Olaya, P.D. Dresselhaus, and S.P. Benz, "Niobium-silicide junction technology for superconducting digital electronics," *IEICE Trans. Electronics*, vol. E93, no. 4, pp. 463-467, 2010, doi: 10.1587/trasele.E93.C.463

- [15] H. Yamamori, H. Sasaki, and A. Shoji, "Dependence of electrical characteristics of NbN/TiN/NbN Josephson junctions on barrier thickness and temperature," *Jpn. J. Appl. Phys.*, vol. 39, part 2, no. 12B, pp. L1289-L1291, Dec. 2000.

- [16] S. K. Tolpygo, R. Rastogi, T. Weir, E. B. Golden, and V. Bolkhovsky, "Development of self-shunted Josephson junctions for a tensuperconductor-layer fabrication process: Nb/NbN<sub>x</sub>/Nb junctions," *IEEE Trans. Appl. Supercond.*, vol. 34, no. 3, pp. 1-8, May 2024, Art no. 1101008, doi: 10.1109/TASC.2024.3364128.

- [17]I.I. Soloviev, S.V. Bakurskiy, V.I. Ruzhickiy, N.V. Klenov, M.Y. Kupriyanov, A.A. Golubov, O.V. Skryabina, and V.S. Stolyarov, "Miniaturization of Josephson junctions for digital superconducting circuits," *Phys. Rev. Applied*, vol. 16, 044060, Oct. 2021.

- [18] M. Gurvitch, M. A. Washington, and H. A. Huggins, "High quality refractory Josephson tunnel junctions utilizing thin aluminum layers," *Appl. Phys. Lett.*, vol. 42, no. 5, pp. 472-474, Mar. 1983, doi: 10.1063/1.93974.

- [19] S. K. Tolpygo et al., "Advanced fabrication processes for superconductor electronics: Current status and new developments," *IEEE Trans. Appl. Supercond.*, vol. 29, no. 5, pp. 1-13, Aug. 2019, Art no. 1102513, doi: 10.1109/TASC.2019.2904919.

- [20] S. K. Tolpygo et al., "Planarized fabrication process with two layers of SIS Josephson junctions and integration of SIS and SFS π-junctions," IEEE Trans. Appl. Supercond., vol. 29, no. 5, pp. 1-8, Aug. 2019, Art no. 1101208, doi: 10.1109/TASC.2019.2901709.

- [21] S. K. Tolpygo, V. Bolkhovsky, T. J. Weir, L. M. Johnson, M. A. Gouker, and W. D. Oliver, "Fabrication process and properties of fully-planarized deep-submicron Nb/Al–AlO<sub>x</sub>/Nb Josephson junctions for VLSI circuits," *IEEE Trans. Appl. Supercond.*, vol. 25, no. 3, pp. 1-12, June 2015, Art no. 1101312, doi: 10.1109/TASC.2014.2374836.

- [22]P. G. De Gennes, "Boundary effects in superconductors," *Rev. Mod. Phys.*, vol. 36, pp. 225-237, Jan. 1964

- [23] P.G. De Gennes, Superconductivity of Metals and Alloys (Benjamin, New York), 1966.

- [24]A.A. Golubov and M.Y. Kupriyanov, "Josephson effect in SNINS and SNIS tunnel structures with finite transparency of the SN boundaries," Sov. Phys. JETP, vol 69, no. 4, pp. 805-812, Oct. 1989.

- [25]A.A. Golubov et al., "Proximity effect in superconductor-insulator-superconductor Josephson tunnel junctions: Theory and experiment," Phys. Rev. B, vol. 51, no. 2, pp. 1073-1089, Jan. 1995.

- [26] R. F. Broom, "Some temperature-dependent properties of niobium tunnel junctions," J. Appl. Phys., vol. 47, no. 12, pp. 5432-5439, Dec. 1976.

- [27] V. Ambegaokar and A. Baratoff, "Tunneling between superconductors," Phys. Rev. Lett., vol. 11, no. 2, p. 104, July 1963.

- [28] N. Takeuchi, D. Ozawa, Y. Yamanashi, and N. Yoshikawa, "An adiabatic quantum flux parametron as an ultra-low-power logic device," *Supercond. Sci. Technol.*, vol. 26, Art. No. 035010, Jan. 2013.

- [29]N. Takeuchi, T. Yamae, C. L. Ayala, H. Suzuki, and N. Yoshikawa, "An adiabatic superconductor 8-bit adder with 24 k<sub>B</sub>T energy dissipation per junction," *Appl. Phys. Lett.*, vol. 114, Art no. 042602, Jan. 2019, doi: 10.1063/1.5080753.

- [30]S. K. Tolpygo, "Scalability of superconductor electronics: Limitations imposed by AC clock and flux bias transformers," *IEEE Trans. Appl. Supercond.*, vol. 33, no. 2, pp. 1-19, March 2023, Art no. 1300419, doi: 10.1109/TASC.2022.3230373.