# An innovative circuit for testing hot carrier and trap generation in GaN Devices

Moshe Azoulay

Electrical Engineering

Ariel University

Ariel, Israel

mosheaz@ariel.ac.il

Gilad Orr

Physics

Ariel University

Ariel, Israel

gilad.orr@ariel.ac.il

Gady Golan

Electrical Engineering

Ariel University

Ariel, Israel

gadygo@ariel.ac.il

Abstract-Microelectronic devices in modern systems are working continuously for prolonged periods of many years. Thus, there is a crucial need for reliability model that will enable us to predict precisely the life cycle of the device and point out on the governing failure mechanisms that are responsible for degradation and failure. This is even more important when high power and frequency devices, especially Normally Off Switch Power transistors are concerned, since the reliability research on those devices lay far behind that of low power digital devices. Our main goal in our lab is to investigate the failure mechanisms of GaN transistors, aimed at determining the reliability factors of the innovative MTOL model. The main goal is to understand the reason for the transformation of the failure mechanism. Employing the recorded data may enable us to predict the performance and life time of the device at different operation parameters such as current, voltage, frequency and temperatures. In this study we employ a new different use for the well-known boost convertor circuit, based on GaN Devices in order to stress the transistor to the maximum values of voltage and current which allows us to examine the reliability of the transistor and accelerating Hot Carrier And Trap Generation failures mechanisms. The acceleration of the failure mechanism should be done in a way that will not affect the electronic device detrimentally and on the other hand we would not need to wait a long time in order to observe the degradation. In this work we will present our new boost converter circuit based on high power GaN HEMT.

Index Terms—GaN, HEMT, test circuit, hot carriers, degradation mechanism

## I. INTRODUCTION

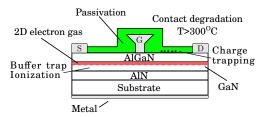

Over the last few years, the research in the field of GaN power transistors has shown impressive advancements [1]. Gallium nitride has a wide energy gap (3.4 eV) that allows operation at high temperature. GaN transistors can remain fully functional well above 300°C, with excellent control of the channel current [2]. In addition, GaN has a breakdown field of 6 MV/cm [3], which is approximately ten times higher than that of silicon. For the same breakdown voltage, GaN-based transistors are ~10 times shorter/thinner with respect to the silicon counterpart, and this results in a significant reduction of the on-resistance of the devices. GaN transistors with breakdown voltages higher than 1900V have already been demonstrated [4], due to the optimization of the buffer structure and/or the adoption of specific methods for substrate removal. In AlGaN/GaN transistors, the channel is formed

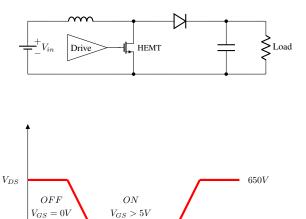

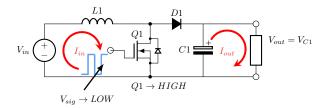

at the hetero-interface between a larger band-gap material (AlGaN) and GaN, due to the spontaneous and piezoelectric polarization that occurs without any doping. For this reason, the mobility of the channel is extremely high (>  $2000cm^2/V$ . s [5]), resulting in current densities  $> 1,000,000 \mu A/mm$ . Commercial 650V/60A devices can have a very low onresistance ( $< 25m\Omega$ , [6]), this has a positive impact on the resistive losses of the transistors, when they are used in switching mode power converters and various pulsed high current applications [7]. Finally, GaN transistors have a low Figure of Merit (FOM)  $FOM = R_{DS(on)} \times Q_g$  (product of on-resistance and gate charge), smaller than a specific value,  $1nC \cdot \Omega$ , and consequently very low switching loss. Compared to the silicon counterparts, power converters based on GaN will therefore be lighter (since they will require smaller heat sinks), smaller (the lower switching losses enable to increase the switching frequency, and to use smaller passives), and more efficient (thanks to the lower resistive and switching losses). However, what about reliability? In a switching-mode power converter (see the simplified boost circuit in Figure 1), the transistor is continuously switched from the off-state to the on-state and vice versa. When the transistor is in off-state, a high voltage (maximum stress) is applied between drain and substrate, drain and source, and between drain and gate. This may result in:

- Buffer trapping processes that are responsible for the increase in dynamic on-resistance; charge trapping may take place due to both the ionization of acceptor states [8], and to the injection of electrons from the substrate [9].

- Injection of electrons at the gate-drain surface, which can be avoided by using an optimized passivation layer.

- Time-dependent (permanent) degradation of the devices, consisting of an increase in source-to-drain leakage [10], or in the generation of short circuit paths between the gate and the channel [11].

When the transistor is in the on-state, the gate is positively biased at voltages higher than 5-6 V (we consider the case of a normally-off device here). Normally-off GaN transistors can be fabricated via the use of MIS/MOS structures with a partially-recessed gate [12], or by using a p-type gate stack

Figure 1. (top) simplified representation of a switching mode power converter (boost configuration); (bottom) simplified representation of the different operating regimes of the transistor in a boost converter.

$I_D > 0A$

Time [s]

[13]. Both technologies can show reliability issues when the devices are stressed at high gate voltages [14], [15]. Finally, when the transistor in Figure 1 switches from the off state to the on-state, it crosses a semi-on condition, in which the voltage and current on the drain may be simultaneously high. This "hard-switching" condition can originate from the discharge of the drain-source capacitance of the transistor (when the HEMT is switched from off- to on-state [16], [17]), and/or from a poor optimization of the dead times of the switching events (in a half-bridge circuit). The simultaneous presence of high current and voltage on the drain may favor hot electron trapping/degradation effects, which reduces the performance and/or reliability of the devices.

### II. TESTING METHOD & SETUP CONFIGURATIONS

#### A. Boost Converter

$I_D = 0A$

Switched-mode supplies can be used for many purposes, including DC-to-DC converters. Often, a DC power source, such as a battery, may not provide the required voltage by a given system. For example, the motors used in driving electric automobiles require much higher voltages than the ones directly accessible from batteries. Operating voltages of modern electric cars are in the region of 500V. Even if banks of batteries were used, the extra weight and space consumed would be too great to be practical. The answer to this problem is to use fewer batteries and to boost the available DC voltage to the required level by using a boost converter. Another problem with batteries, large or small, is that their output voltage varies as the available charge is used up, and at some point, the battery voltage becomes too low to power the circuit being supplied. However, if this low output level can be boosted back up to a useful level again, by using a boost converter, the life of the battery can be extended. The DC input to a boost converter can be from many sources as well

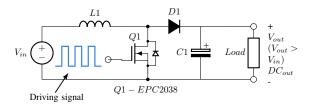

as batteries, such as rectified AC from the mains supply, or DC from solar panels, fuel cells, dynamos and DC generators. The boost converter is different to the Buck Converter in that its output voltage is equal to, or greater than its input voltage. Keeping in mind that power needs to be conserved, any voltage conversion results in a change in current. Thus, increasing the voltage results in a reduced current. Due to the high switching frequencies and currents, boost converters stress their components considerably. In this paper, we present reliability tests for GaN transistors in a boost converter design. As demonstrated earlier, using a classic boost converter circuit, we were able to stress test the GaN transistors to the full extent of their maximum voltages and currents. This showcases that the circuits are excellent for reliability testing. Figure 2 illustrates the basic design of a Boost converter with GaN transistor.

Figure 2. Current Path with GaN Off

# B. Boost Converter Operation

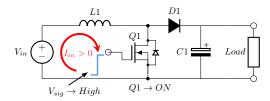

Figure 3 illustrates the circuit action during the initial high period of the high frequency square wave applied to the GaN gate at start up. During this time GaN conducts, placing a short circuit from the right-hand side of L1 to the negative input supply terminal. Therefore a current flows between the positive and negative supply terminals through L1, which stores energy in its magnetic field. There is virtually no current in the remainder of the circuit as the combination of D1, C1 and the load represent a much higher impedance than the path directly through the heavily conducting GaN transistor. Figure 4 shows

Figure 3. Boost Converter Operation at Switch On

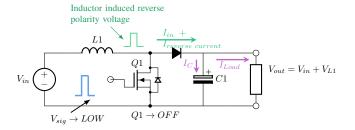

the current path during the low period of the switching square wave cycle. As the GaN transistor is rapidly turned off the sudden drop in current causes L1 to produce a back e.m.f. in the opposite polarity to the voltage across L1 during the on period, to keep current flowing. This results in two voltages, the supply voltage  $V_{in}$  and the back e.m.f. $(V_L)$  across L1 in series with each other. This higher voltage  $(V_{in}+V_L)$ , now that there is no current path through the GaN transistor, forward

biases D1. The resulting current through D1 charges up C1 to  $V_{in} + V_L$  minus the small forward voltage drop across D1 and also supplies the load. Figure 5 shows the circuit action during

Figure 4. Current Path with GaN Off

GaN on periods after the initial start-up. Each time the GaN conducts, the cathode of D1 is more positive than its anode, due to the charge on C1. D1 is therefore turned off so the output of the circuit is isolated from the input, however the load continues to be supplied with  $V_{in} + V_L$  from the charge on C1. Although the charge C1 drains away through the load during this period, C1 is recharged each time the GaN switches off, so maintaining an almost steady output voltage across the load. The theoretical DC output voltage is determined by the input voltage  $(V_{in})$  divided by 1 minus the duty cycle (D) of the switching waveform, which will be some figure between 0 and 1 (corresponding to 0 to 100%) and therefore can be determined using the following formula:

$$V_{out} = \frac{V_{in}}{1-D}$$

Figure 5. Current Path with GaN On

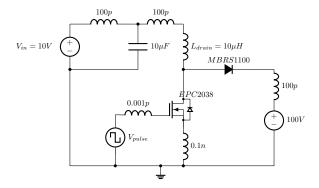

1) Boost convertor based on the EPC 2038 GaN transistor: The boost converter that we are showing in this paper is based on GaN n-channel transistor (EPC 2038) which used as switch, similar to the traditional Boost converter circuit with one main difference: the output is connected to a high-voltage supply instead of a regular load (Figure 6). We present the GaN EPC 2038 characteristics in Table I.

| Parameter     | Pulsed Input | Continuous Input | Unit        |

|---------------|--------------|------------------|-------------|

| $V_{DS}(max)$ | 120          | 100              | V           |

| $I_D(max)$    | 0.5          | 0.5              | Α           |

| $V_{GS}(max)$ | 6            | 6                | V           |

| $V_{GS}(min)$ | -5           | -5               | V           |

| $T_J$         | -40:150      | -40:150          | $^{\circ}C$ |

| $R_{DS(ON)}$  | 3.3          | 3.3              | $\Omega$    |

| Table I       |              |                  |             |

GaN EPC 2038 CHARACTERISTICS

a. Objectives of the boost converter circuit: A new boost converter test vehicle for High Voltage Reverse Bias (HVRB) where it will allow us to stress the devices at full rated voltage and maximum expected current. The test will be performed using a modified Boost-converter circuit where a high duty cycle will allow the maximum voltage output at the drain using a minimal input voltage. A diode is connected to the drain so that the maximum voltage is seen across the EPC device while the gate is biased to 0V (Off state). This test will be performed in a matrix of high voltage and temperature in order to find an expression for time to fail versus Voltage and Temperature (giving us an Arrhenius relation too). All our testing will include careful monitoring of the gate voltage since there is a known failure mechanism relating to leakage in the gate junction.

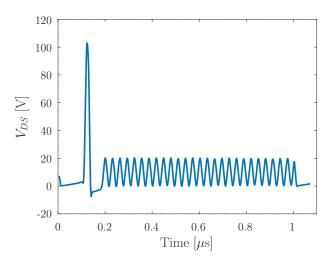

b. Concept and approach of boost converter circuit: The principle of operation of the circuit in Figure 6 is similar to the regular boost converter that was presented in the previous section, as the following: the current through the inductor  $L_{drain}$  (10 $\mu H$ ) increases linearly under constant voltage, while the average voltage of the inductor is zero. Hence, the applied voltage  $(V_{in})$  is equal to the average voltage applied to the Drain. When the Pulse Generation (PG) is on, the current increases across the inductor and the voltage on the inductor is positive, and while the PG is off the voltage on  $V_{DS}$  increases rapidly across the device under test and the inductor voltage turns negative while the current decreases. The energy from the inductor goes into the capacitor and the capacitance of the device and when the voltage exceeds the maximum output voltage, the spikes flow through the diode to the output voltage supply. To test the logic operation of the circuit we employed the DUT with NFET GaN (2038). All the parameters of the other components of the circuit kept identical for the entire circuits and experiments of the test:  $L = 10\mu H$ ,  $C_{in} = 100pF$ , Vout = 100V and  $C_{out} = 25pF$ . The average source voltage  $(V_{in})$  is the voltage across the inductor plus the voltage across the device. Since the voltage across an inductor is by definition equal to zero, then we can say that the average voltage across the device is equal to the average voltage at the input. The Duty cycle, D, describes the ON-time over the total ON plus OFF time. Hence:

$$\bar{V}_{in} = I(on) \times R_{DS(on)} \times D + V_{max} \cdot \frac{(1-D)}{2}$$

(1)

where we assume that the rise and fall times of the output voltage is triangular. With an output diode, there may be more time at  $V_{max}$ , so we may need to modify a factor of 2. Nonetheless, we see that most of the on-time relates to the voltage drop across the transistor when it is ON. Then, by rearranging Equation 1 we can find an expression for  $R_{DS(ON)}$ :

$$R_{DS(on)} = \frac{\left(V_{in} - V_{max} \frac{(1-D)}{2}\right)}{\bar{I} \cdot D} \tag{2}$$

Figure 6. Electrical diagram of Boost Converter circuit

Figure 7. GaN Based boost converter assembled board

# III. GaN DEGRADATION MECHANISMS

As the device design and material processing technology for AlGaN/GaN HEMTs has matured over the recent years, several failure mechanisms that limited device lifetime have been addressed and improved. These mechanisms can be grouped together into three main categories that effects lifetime: Contact degradation, hot electron effect (HCI), and inverse piezoelectric effect. Both Schottky and Ohmic contacts have shown excellent stability below 300 °C [18]. Piazza et al. [19] have reported an increase in contact resistance and passivation cracking due to Ga out-diffusion and Au interdiffusion after a 100 h thermal storage test stress at 340 °C. Nickel based Schottky contacts were found to form nickel nitrides on GaN at annealing temperatures as low as 200 °C, resulting in a significant decrease in Schottky barrier height [20], [21]. The observed current collapse and gate lag in AlGaN/GaN HEMTs under high voltage and high current operation have been attributed to hot electrons. These are electrons that have been accelerated in a large electric field, resulting in very high kinetic energy, which can cause trap formation. Creation of traps can occur in both the AlGaN layer and the buffer, leading to reversible degradation of transconductance and saturated drain current [2], [13]. In this paper we are focusing on both hot Carriers and Trap Generation and Contact Degradation as we are trying to reach the ideal conditions for both mechanisms using the boost converter circuit as we mentioned before.

Figure 8. Simulation result which presents the voltage of  $V_{DS}$  versus time,  $V_{DS}$  is reaching  $100\mathrm{V}$

Figure 9. Simulation result which presents the current versus time, the peak current is reaching almost 1A

# A. Hot -Carriers and Trap Generation

Permanent device degradation after high VDG stress under on-state conditions has been attributed to the presence of hot electrons. In GaAs-based devices, hot electrons generate holes which are accumulated near the gate resulting in a negative shift of VT [22]–[24]. Typically, IG is used to derive field-acceleration laws for failure. Impact ionization, however, is negligible in GaN HEMTs. This is due to the fact that tunneling injection dominates gate current, preventing gate current from being used as an indicator for hot electron degradation [1,4]. However, these hot electrons likely lead to trap generation at the AlGaN/GaN interface and/or at the passivation GaN cap interface. As in GaAs and InP based HEMTs, traps lead to an increase in the depletion region between the gate and the drain, ultimately resulting in an increase in drain resistance and subsequently a decrease in

saturated drain-source current. Comparatively, under reverse bias or so-called off-state conditions the degradation is greatly reduced due to the reduction of electrons present in the channel. Sozza et al. [8] showed that GaN/AlGaN/GaN HEMTs that underwent a 3000 h on-state stress resulted in an increase in surface traps with an activation energy of about 0.55 eV. On the other hand, devices stressed under off-state conditions saw a very small increase in traps. Meneghesso et al. have employed electroluminescence (EL) to study the effect of hotcarriers and its dependence on stress conditions [2]. Uniform EL emission was observed along the channel for devices stressed at  $V_{GS} = 0V$  and  $V_{DS} = 20V$ , which is due to hot electrons. However, there is no presence of hot spots or current crowding. On the other hand, under OFF state conditions with  $V_{GS} = -6V$  and  $V_{DS} = 20V$  (resulting in a  $V_{GD} = -26V$ ), the EL emission from the channel is not uniform. These hot spots may be due to injection of electrons from the gate into the channel. Due to the high bias conditions, the electrons acquire enough energy to give rise to photon emission.

# B. Contact Degradation

Contact degradation and gate sinking are significant degradation mechanisms at elevated temperatures in GaAs and InP based HEMTs. This has not yet proven to be a significant issue with AlGaN/GaN HEMTs at temperatures below 400 °C for Pt/Au Schottky contacts and Ti/Al/Pt/Au annealed Ohmic contacts [1], [13], [25]–[30]. An increase in Schottky barrier height was observed for Ni/Au Schottky contacts after DC stress at elevated junction temperatures (200 °C) [1], [13], [31]–[35]. This was due to consumption of an interfacial layer between the Schottky contact and the AlGaN layer. Though the resulting positive shift in the Schottky barrier height, and thus the pinch-off voltage, is ideal, the subsequent change in IDSS is not favorable. Unstressed devices were subjected to an anneal after the Schottky contact was deposited in order to decrease the interfacial layer between the gate and semiconductor. Devices that underwent the gate anneal showed 50% less degradation during a 24 h stress test as opposed to devices that did not receive a gate anneal [1], [13]. Thermal storage tests up to 2000 h on Ti/Al/Ni/Au ohmic contacts at and above 290 °C showed an increase in contact resistance as well as surface roughness due to growth of Au-rich grains that ultimately led to cracks in passivation [31]–[34], [36]–[40]. The two primary degradation mechanisms were determined to be Au inter-diffusion within the metal layers and Ga outdiffusion from the semiconductor into the metallic compounds. Similar degradation was observed after DC stress tests that resulted in junction temperatures equivalent to the thermal storage tests. Due to the high-power capability of AlGaN/GaN HEMTs, proper temperature management is needed in order to optimize device performance under high current and high voltage operation [20], [21], [41]-[44]. Self-heating of devices can ultimately result in poor device performance through contact degradation. Reliability of contacts is highly dependent upon both metal schemes as well as processing during fabrication, EPC's eGaN transistors that were used in this research do not use a Schottky gate and therefore are not vulnerable to this whole contact mechanism.

Figure 10 summarizes the reported degradation mechanisms in AlGaN/GaN HEMTs during electrical stressing at temperatures up to the typical operating temperature.

Figure 10. Schematic of degradation mechanisms in AlGaN/GaN HEMTs

### IV. RESULTS OF THE EXPERIMENTAL TESTS

In this section we will present the preliminary results of the very first tests that were done using the boost convertor circuit.

#### A. Boost converter HVRB continues test

Boost convertor circuit was activated with a constant drain current source of 400 mA, while VD voltage was continuously measured during the test, the analysis sequence of every experiment was a result of monitoring VD voltage continuously the test was performed in four different voltages gradually to make sure that the system is working fine. The purpose of this test is to show that the charge trapping mechanism responsible for a long-term increase of  $R_{DS(on)}$  follows a log (time) trend. The calculation of the  $R_{DS(on)}$  was based on Equation 2

In this case the  $V_{in}$  is equal to the measured  $V_{DS}$ ,  $V_{max}$  was measured from the oscilloscope, and it varies from experiment to experiment,  $\bar{I}$  is the constant drain current source that was mentioned before and were limited to 400 mA here. Where D is the duty cycle, which is set to be 0.7 for this experiment. For example, for the test that we will present next, the test was performed with 40V stress which led to the  $V_{max}$  of 60v which measured from the scope, the first sample of the  $V_{DS}$  was equal to 9.95v, let's put all the values in the Equation2:

$$R_{DS}(on) = \frac{\frac{9.95-60(1-0.7)}{2}}{0.4 \times 0.7} = R_{DS}(on) = \frac{0.95}{0.28} = 3.39\Omega$$

As we can see, the result of the calculated  $R_{DS}$  on is very close to the  $R_{DS}$  on of the EPC 2038 transistor which is 3.33  $\Omega$ , in the following graphs we will show the results of  $R_{DS}$  on vs time and normalized  $R_{DS}$  on vs time based on the equation and the calculations that were shown above.

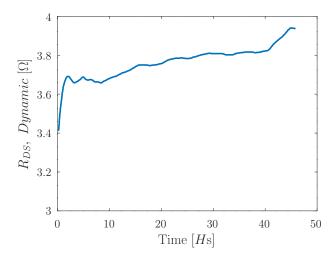

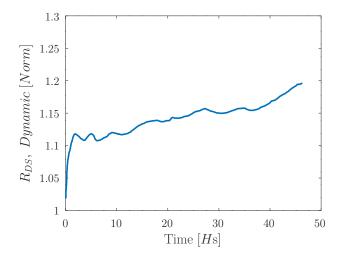

1) Test with 40V stress, 400mA: This test was performed with a constant drain current of 400 mA and constant output voltage of 40v , $V_{max}$  reached 60 v; below in Figure 11 we present the change of the  $R_{DS(on)}$  during this test which affected by the change of  $V_{DS}$ :

Figure 11.  $R_{DS(on)}$  versus time voltage 40v

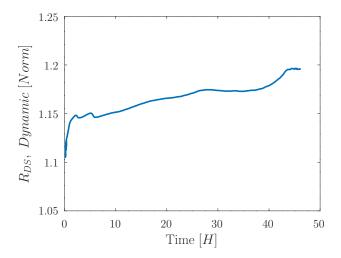

Figure 12. Normalized  $R_{DS(on)}$  versus time voltage 40v

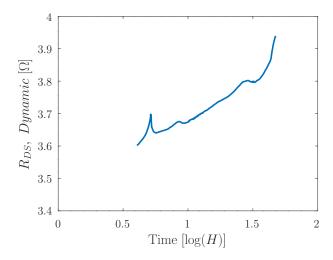

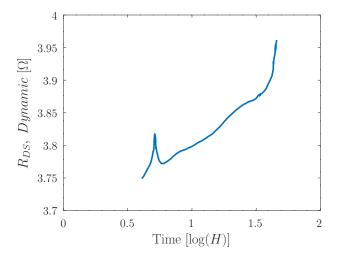

As we can see from Figure 11, the graph of  $R_{DS(on)}$  fits the log law of time, Figure 12shows the Normalized  $R_{DS(on)}$  vs time and it also fits the log law of time. In Figure 13 we had adjusted the time scale to log scale, as we can see that it almost fits a linear line which gives the indication that the  $R_{DS(on)}$  is fitting the log law of time as well here.

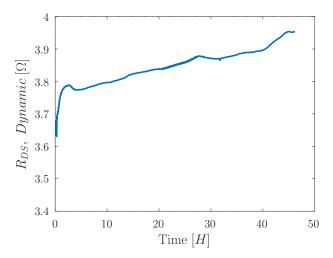

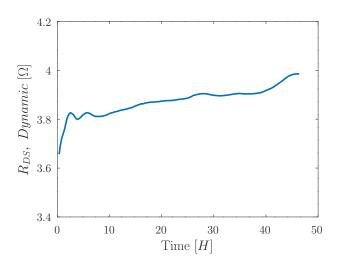

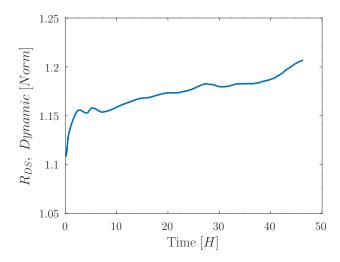

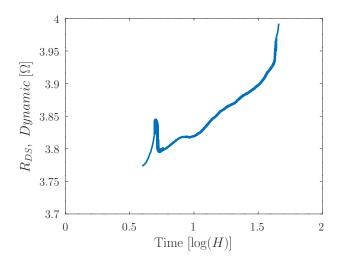

2) Test with 70V stress, 400mA: This test was performed with a constant drain current of 400 mA and constant output voltage of 70v , $V_{max}$  reached 85 v . Below in Figure 14 we present the change of the  $R_{DS(on)}$  during this test which affected by the change of  $V_{DS}$ :

As we can see from Figure 14, the graph of  $R_{DS(on)}$  fits the log law of time, Figure 15 shows the Normalized  $R_{DS(on)}$  vs time and it's also fit the log law of time. In Figure 16 we had adjusted the time scale to log scale, as we can see that it almost fits a linear line which gives the indication that the  $R_{DS(on)}$  is fitting the log law of time as well here.

Figure 13.  $R_{DS(on)}$  versus log time voltage 40v

Figure 14.  $R_{DS(on)}$  on versus time voltage 70v

3) Test with 100V stress, 400mA: This test was performed with a constant drain current of 400 mA and constant output voltage of 100v , $V_{max}$  reached 110 v; below in Figure 17 we present the change of the  $R_{DS(on)}$  during this test which affected by the change of  $V_{DS}$ : As we can see from Figure 17, the graph of  $R_{DS(on)}$  fits the log law of time, Figure 18 shows the Normalized  $R_{DS(on)}$  vs time and it's also fit the log law of time. In Figure 19 we had adjusted the time scale to log scale, as we can see that it almost fits a linear line which gives the indication that the  $R_{DS(on)}$  is fitting the log law of time as well here.

### V. DISCUSSION

In this research, we showed new circuit with new approach and new methodology that was designed, developed and assembled in our lab for main use and goal of investigation and reaching and stressing GaN transistor to full range and maximum values as was explained and presented before and

Figure 15. Normalized  $R_{DS(on)}$  versus time voltage 70v

Figure 16.  $R_{DS(on)}$  versus log time voltage 70v

was tested with different conditions and methods as mentioned in pervious sections. In this paper we have measured and calculated the changes of  $R_{DS(on)}$  vs. time based on the circuit that we showed before. The preliminary results showed that changes fit the log law of time which was also reported by the EPC phase 12 report [43]. The EPC group also mentioned the following conclusions:

- $R_{DS(on)}$  grows with time as log(t)

- The slope of  $R_{DS(on)}$  over time has a negative temperature coefficient (i.e., lower slope at higher temperature)

- Switching frequency does not affect the slope, but causes a small vertical offset

- Switching current does not affect the slope, but causes a small vertical offset

- Negligible difference between inductive and resistive hard switching EPC has also developed a first-principles mathematical model to describe the dynamic  $R_{DS(on)}$

Figure 17.  $R_{DS(on)}$  on versus time voltage 100v

Figure 18. Normalized  $R_{DS(on)}$  versus time voltage 100v

effect in eGaN FETs from the basic physics of hot carrier scattering into surface traps:

$$\frac{\Delta R}{R} = a + b \log \left( 1 + \exp \left( \frac{V_{DS} - V_{FD}}{\alpha} \right) \right) \sqrt{T} \exp \left( \frac{\hbar \omega_{LO}}{kT} \right)$$

# **Independent Variables:**

$V_{DS}$  = Drain voltage (V)

T = Device temperature (K)

t = Time (min)

#### **Parameters:**

a = 0.00 (unitless)

$b = 2.0E - 5(E^{-1/2})$

$\hbar\omega_{LO}=92~{\rm meV}$

$V_{FD}$ = 100V (appropriate for Gen5 100V products only)

a = 10 [V]

Equation above models  $R_{DS(on)}$  as a function of time, temperature, and drain voltage. It involves five device-dependent

Figure 19.  $R_{DS(on)}$  versus log time voltage 100v

parameters. The values of the parameters shown in Table I are appropriate for an EPC2038 or other 100 V, 5'th Generation, FETs listed in Appendix B. Natural log (base e) was used for fitting. While the general form of this equation applies to all eGaN FETs.

Our next goal is to confirm the equation that the EPC has developed for  $R_{DS(on)}$  changes by using our presented methodology. We further intend to inquire into the physics that resides behind their findings in order to improve our current understanding resulting in an improved physical.

#### REFERENCES

- [1] M. Meneghini, G. Meneghesso, and E. Zanoni, *Power GaN devices: Materials, applications and reliability*. Springer, 2017.

- [2] R. Gaska, M. Gaevski, J. Deng, and R. Jain, "Novel AlInN / GaN integrated circuits operating up to 500 °c," in *Proc. Solid State Device Res. Conf. (ESSDERC)*, 44th Eur., pp. 142–145, 2014.

- [3] G. Orr, M. Azoulay, G. Golan, and A. Burger, "Gallium Nitride High-Electron-Mobility Transistor-Based High-Energy Particle-Detection Preamplifier," *Metrology*, vol. 5, no. 2, p. 21, 2025.

- [4] N. Herbecq, I. Roch-Jeune, N. Rolland, D. Visalli, J. Derluyn, S. Degroote, M. Germain, and F. Medjdoub, "1900v, 1.6mΩ cm² AlN/GaN-on-Si power devices realized by local substrate removal," Appl. Phys. Express, vol. 7, p. 034103, 2014.

- [5] J.-T. Chen, I. Persson, D. Nilsson, C.-W. Hsu, J. Palisaitis, U. Forsberg, P. O. Persson, and E. Janzén, "Room-temperature mobility above 2200 cm²/v· s of two-dimensional electron gas in a sharp-interface AlGaN/GaN heterostructure," Applied Physics Letters, vol. 106, no. 25, 2015.

- [6] "Gs66516t top-side cooled 650 v e-mode GaN transistor preliminary datasheet." http://www.gansystems.com/datasheets/GS66516T\%20DS\ %20Rev\%20161007.pdf.

- [7] G. Orr and M. Roth, "Safe and consistent method of spot-welding platinum thermocouple wires and foils for high temperature measurements," *Review of scientific instruments*, vol. 83, no. 8, 2012.

- [8] P. Moens, A. Banerjee, M. J. Uren, M. Meneghini, S. Karboyan, I. Chatterjee, P. Vanmeerbeek, M. CÀsar, C. Liu, A. Salih, E. Zanoni, G. Meneghesso, M. Kuball, and M. Tack, "Impact of buffer leakage on intrinsic reliability of 650v AlGaN / GaN HEMTs," in *IEEE Electron Device Meet. IEDM 2015 Techical Dig.*, pp. 903–906, 2015.

- [9] D. Bisi, M. Meneghini, F. A. Marino, D. Marcon, S. Stoffels, M. Van Hove, S. Decoutere, G. Meneghesso, and E. Zanoni, "Kinetics of buffer-related r<sub>on</sub>-increase in GaN-on-Silicon MISHEMTs," *IEEE Electron Device Lett.*, vol. 35, no. 10, pp. 1004–1006, 2014.

- [10] M. Meneghini, G. Cibin, M. Bertin, A. G. M. Hurkx, P. Ivo, J. Šon-skÜ, J. A. Croon, G. Meneghesso, and E. Zanoni, "Off-state degradation of AlGaN / GaN power HEMTs: Experimental demonstration of time-dependent drain-source breakdown," *IEEE Trans. Electron Devices*, vol. 61, no. 6, pp. 1987–1992, 2014.

- [11] I. Rossetto, M. Meneghini, S. Pandey, M. Gajda, G. A. M. Hurkx, J. A. Croon, J. ŠonskÜ, G. Meneghesso, and E. Zanoni, "Field-related failure of GaN-on-Si HEMTs: Dependence on device geometry and passivation," *IEEE Trans. Electron Devices*, vol. 64, no. 1, pp. 73–77, 2017.

- [12] T. Wu, D. Marcon, B. De Jaeger, M. Van Hove, B. Bakeroot, S. Stoffels, G. Groeseneken, S. Decoutere, and R. Roelofs, "Time dependent dielectric breakdown (TDDB) evaluation of PE-ALD SiN gate dielectrics on AlGaN/GaN recessed gate D-mode MISHEMTs and e-mode MISFETs," in *Reliab. Phys. Symp. (IRPS)*, 2015 IEEE Int., p. 6C.4.1, 2015.

- [13] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, "Gate injection transistor (GIT) - A normally-off AlGaN/GaN power transistor using conductivity modulation," *IEEE Trans. Electron Devices*, vol. 54, no. 12, pp. 3393–3399, 2007

- [14] M. Ťapajna, O. Hilt, E. Bahat-Treidel, J. Würfl, and J. Kuzmík, "Investigation of gate-diode degradation in normally-off p-GaN / AlGaN / GaN high-electron-mobility transistors," Appl. Phys. Lett., vol. 107, p. 193506, 2015.

- [15] T. Wu, D. Marcon, M. B. Zahid, M. Van Hove, S. Decoutere, and G. Groeseneken, "Comprehensive investigation of on-state stress on d- mode AlGaN / GaN MIS-HEMTs," *IEEE Int. Reliab. Phys. Symp.*, pp. 1–7, 2013.

- [16] J. Joh, N. Tipirneni, S. Pendharkar, and S. Krishnan, "Current collapse in GaN heterojunction field effect transistors for highvoltage switching applications," in *IEEE Int. Reliab. Phys. Symp. Proc.*, pp. 4–7, 2014.

- [17] S. R. Bahl, D. Ruiz, and D. S. Lee, "Product-level reliability of GaN devices," in *IEEE Int. Reliab. Phys. Symp.*, 2016.

- [18] G. Golan, M. Azoulay, T. Avraham, I. Kremenetsky, and J. B. Bernstein, "An improved reliability model for Si and GaN power FET," *Microelectronics Reliability*, vol. 81, pp. 77–89, 2018.

- [19] F. Gao, B. Lu, L. Li, and et al., "Role of oxygen in the off-state degradation of AlGaN/GaN high electron mobility transistors," *Appl. Phys. Lett.*, vol. 99, no. 22, p. 223506, 2011.

- [20] F. Gao, S. Tan, J. del Alamo, and et al., "Impact of water-assisted electrochemical reactions on the off-state degradation of AlGaN/GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 437–444, 2014

- [21] O. Ambacher, J. Majewski, C. Miskys, and et al., "Pyroelectric properties of Al(In)GaN/GaN hetero- and quantum well structures," J. Phys. Condens. Matter, vol. 14, no. 13, pp. 3399–3434, 2002.

- [22] D. Marcon, T. Kauerauf, F. Medjdoub, and et al., "A comprehensive reliability investigation of the voltage-, temperature- and device geometry-dependence of the gate degradation on state-of-the-art GaN-on-Si HEMTs," in 2010 Int. Electron Devices Meeting, pp. 20.3.1–20.3.4, 2010.

- [23] J. Suehle, "Ultrathin gate oxide reliability: physical models, statistics, and characterization," *IEEE Trans. Electron Devices*, vol. 49, no. 6, pp. 958–971, 2002.

- [24] I. Rossetto, M. Meneghini, O. Hilt, and et al., "Time-dependent failure of GaN-on-Si power HEMTs with p-GaN gate," *IEEE Trans. Electron Devices*, vol. 63, no. 6, pp. 2334–2339, 2016.

- [25] I. Rossetto, M. Meneghini, V. Rizzato, and et al., "Study of the stability of e-mode GaN HEMTs with p-GaN gate based on combined DC and optical analysis," *Microelectron. Reliab.*, vol. 64, pp. 547–551, 2016.

- [26] M. Meneghini, I. Rossetto, F. Hurkx, and et al., "Extensive investigation of time-dependent breakdown of GaN-HEMTs submitted to off-state stress," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2549–2554, 2015.

- [27] R. Degraeve, G. Groeseneken, R. Bellens, and et al., "New insights in the relation between electron trap generation and the statistical properties of oxide breakdown," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 904–911, 1998.

- [28] J. Stathis, "Percolation models for gate oxide breakdown," J. Appl. Phys., vol. 86, no. 10, p. 5757, 1999.

- [29] M. Meneghini, O. Hilt, C. Fleury, and et al., "Normally-off GaN-HEMTs with p-type gate: off-state degradation, forward gate stress and ESD failure," *Microelectron. Reliab.*, vol. 58, pp. 177–184, 2016.

- [30] A. Inberg, Y. Shacham-Diamand, E. Rabinovich, G. Golan, and N. Croitoru, "Material and electrical properties of electroless Ag-W thin film," *Journal of electronic materials*, vol. 30, no. 4, pp. 355–359, 2001.

- [31] I. Rossetto, M. Meneghini, M. Barbato, F. Rampazzo, D. Marcon, G. Meneghesso, and E. Zanoni, "Demonstration of field and power dependent ESD failure in AlGaN/GaN RF HEMTs," *IEEE Transactions* on Electron Devices, vol. 62, no. 9, pp. 2830–2836, 2015.

- [32] S. Chen, A. Griffoni, P. Srivastava, and et al., "HBM ESD robustness of GaN-on-Si Schottky diodes," *IEEE Trans. Device Mater. Reliab.*, vol. 12, no. 4, pp. 589–598, 2012.

- [33] B. Shankar and M. Shrivastava, "Unique ESD behavior and failure modes of AlGaN/GaN HEMTs," in 2016 IEEE Int. Reliability Physics Symp. (IRPS), pp. EL-7-1-EL-7-5, 2016.

- [34] J. Kuzmík, D. Pogány, E. Gornik, P. Javorka, and P. Kordoš, "Electrical overstress in AlGaN/GaN HEMTs: Study of degradation processes," *Solid-State Electronics*, vol. 48, no. 2, pp. 271–276, 2004.

- [35] A. Axelevitch, B. Gorenstein, and G. Golan, "Application of gold nanoparticles for silicon solar cells efficiency increase," *Applied surface* science, vol. 315, pp. 523–526, 2014.

- [36] M. A. Khan, M. S. Shur, Q. C. Chen, and J. N. Kuznia, "Current/voltage characteristic collapse in AlGaN/GaN heterostructure insulated gate field effect transistors at high drain bias," *Electron. Lett.*, vol. 30, pp. 2175– 2176, Dec. 1994.

- [37] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans. Electron Devices*, vol. 48, pp. 560–566, Mar. 2001.

- [38] X. Hu, A. Koudymov, G. Simin, J. Yang, M. A. Khan, A. Tarakji, M. S. Shur, and R. Gaska, "Si<sub>3</sub>N<sub>4</sub>/AlGaN/GaN-metal-insulator-semiconductor heterostructure field-effect transistors," *Appl. Phys. Lett.*, vol. 79, pp. 2832–2834, Oct. 2001.

- [39] H. Leirer, A. Vescan, R. Dietrich, A. Wieszt, and H. H. Sledzik, "RF characterization and transit behavior of AlGaN/GaN power HFETs," *IEICE Trans. Electron.*, vol. E84-C, no. 10, pp. 1442–1447, 2001.

- [40] G. Golan and A. Axelevitch, "Novel sputtering method for Pd–Al2O3 UV transparent conductive coatings," *Microelectronics Journal*, vol. 31, no. 6, pp. 469–473, 2000.

- [41] H. Kim, R. M. Thompson, V. Tilak, T. R. Prunty, J. R. Shealy, and L. F. Eastman, "Effects of SiN passivation and high-electric field on AlGaN-GaN HFET degradation," *IEEE Electron Device Lett.*, vol. 24, pp. 421–423, July 2003.

- [42] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors," *Appl. Phys. Lett.*, vol. 77, pp. 250–252, July 2000.

- [43] J. Joh and J. del Alamo, "Critical voltage for electrical degradation of GaN high-electron mobility transistors," *IEEE Electron Device Lett.*, vol. 29, no. 4, pp. 287–289, 2008.

- [44] P. Valizadeh and D. Pavlidis, "Effects of RF and DC stress on AlGaN/GaN MODFETs: A low-frequency noise-based investigation," *IEEE Transactions on Device and Materials Reliability*, vol. 5, no. 3, pp. 555–563, 2005.