# A Systematic Characterization of LLM Inference on GPUs

HAONAN WANG, XUXIN XIAO, MINGYU YAN\*, ZHUOYUAN ZHU, DENGKE HAN, DUO WANG, WENMING LI, and XIAOCHUN YE, State Key Lab of Processors, Institute of Computing

Technology, Chinese Academy of Sciences, China

CUNCHEN HU, China Telecom Cloud Computing Research Institute, China

HONGYANG CHEN, Zhejiang Lab, China

GUANGYU SUN, Peking University, China

This work presents a systematic characterization of Large Language Model (LLM) inference to address fragmented understanding. Through comprehensive experiments, we establish a four-dimensional analytical framework: (1) Two-Phase Heterogeneity Observation; (2) Microarchitectural Root Cause Analysis; (3) System Scaling Principles; and (4) Emerging Paradigm Boundaries. Our investigation progresses systematically from observation to foresight: identifying performance phenomena, revealing hardware causes, validating system behavior, and exploring new paradigms. This study not only consolidates a reliable empirical foundation for existing research but also provides new discoveries and practical optimization guidance for LLM inference.

#### 1 Introduction

The inference of Large Language Models (LLMs) has emerged as a critical workload spanning from data centers to edge devices [6, 16, 36, 50, 55, 58, 60]. As LLM deployment expands across diverse applications—from real-time conversational systems [24, 34, 49] to complex retrieval-augmented generation [10, 14, 22, 30] pipelines—optimizing inference efficiency has become increasingly vital [29, 31, 32, 38, 41, 56, 59, 63]. Unlike conventional deep learning workloads, LLM inference exhibits a distinctive two-phase execution pattern: the parallelizable Prefill phase and the sequential Decode phase [25, 62]. This inherent computational heterogeneity generates conflicting hardware demands that dictate system performance across latency, throughput, and energy efficiency metrics.

Although the compute-bound nature of Prefill and memory-bound characteristics of Decode have gained broad recognition, current research predominantly treats this dichotomy as a static assumption rather than examining it through dynamic quantitative analysis. The growing complexity of model architectures—particularly the shift toward Mixture-of-Experts (MoE) [4, 11, 43] paradigms—coupled with expanding deployment scenarios encompassing edge computing and sophisticated Retrieval-Augmented Generation (RAG) workflows, has further complicated the interplay between hardware constraints and software characteristics. This landscape creates a pressing need for a systematic characterization that can not only validate established understandings with rigorous microarchitectural evidence but also reveal fundamental relationships between execution patterns, memory hierarchy behavior, and energy consumption profiles.

Existing characterization studies exhibit significant fragmentation across research domains. Device- and energy-focused analyses profile platform-specific latency and power patterns [3, 12, 26, 35, 40], while quantization research examines precision-performance trade-offs [44]. Kernel- and compiler-level investigations dissect attention/GEMM operations and optimization strategies [5, 7, 51, 57], and system-oriented studies explore serving, scheduling policies, and cache management [20,

Authors' Contact Information: Haonan Wang, wanghaonan241@mails.ucas.ac.cn; Xuxin Xiao, xiaoxuxin25e@ict.ac.cn; Mingyu Yan, yanmingyu@ict.ac.cn; Zhuoyuan Zhu, zhuzhuoyuan24s@ict.ac.cn; Dengke Han, handengke21s@ict.ac.cn; Duo Wang, wangduo18z@ict.ac.cn; Wenming Li, liwenming@ict.ac.cn; Xiaochun Ye, yexiaochun@ict.ac.cn, State Key Lab of Processors, Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China; Cunchen Hu, hucc12@chinatelecom.cn, China Telecom Cloud Computing Research Institute, Beijing, China; Hongyang Chen, hongyang@zhejianglab.com, Zhejiang Lab, Hangzhou, China; Guangyu Sun, gsun@pku.edu.cn, Peking University, Beijing, China.

<sup>\*</sup>Corresponding author.

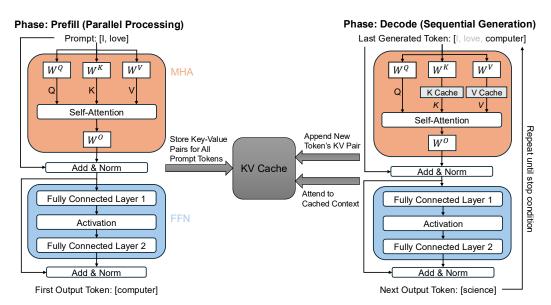

Fig. 1. Illustration of the LLM inference process, comprising the Prefill and Decode phases.

28, 42, 46, 47, 52, 53, 62]. Despite this breadth, current work remains siloed—lacking the cross-layer, component-integrated perspective needed for holistic LLM inference characterization.

To bridge this gap, our research introduces a unified experimental framework that systematically synthesizes existing knowledge while exploring new analytical directions. This integrated approach enables us to provide architectural-level verification and refinement of established conclusions while yielding new insights in previously underexplored domains. Our systematic investigation progresses through four interconnected analytical dimensions. (1) Two-Phase Heterogeneity: We establish the fundamental dichotomy between Prefill and Decode phases through cross-scenario measurements, defining phase heterogeneity as a core paradigm for LLM inference. (2) Microarchitectural Root Causes: Using Roofline modeling and stall analysis, we identify the hardware origins of phase divergence through operator characteristics and data reuse patterns. (3) Scaling Behavior: We validate phase-aware parallelization strategies across multi-GPU systems, and shows how the bottlenecks of Prefill and Decode phases are amplified at the edge device. (4) Emerging Paradigms: We characterize sparse activation tradeoffs in MoEs models and bottleneck migration in RAG workflows, informing next-generation system design.

Our findings establish a systematic framework for understanding LLM inference. These insights provide both theoretical foundations for future model-system co-design and practical optimization guidances for real-world deployment across diverse hardware environments.

### 2 Background

### 2.1 LLM Inference

We focus on decoder-only Transformer architectures (e.g., Llama-3, Qwen2.5). As shown in Fig. 1, the inference process naturally decomposes into two distinct phases. (1) Prefill Phase. The model processes the entire input prompt in parallel. The self-attention mechanism computes the Key and Value tensors for all prompt tokens and stores them in the *KV Cache*. This parallel computation establishes the initial context required for subsequent generation. (2) Decode Phase. The model generates output tokens autoregressively, one step at a time. Each step processes only the single newly generated token. To maintain context, the attention mechanism uses the *KV Cache* to retrieve

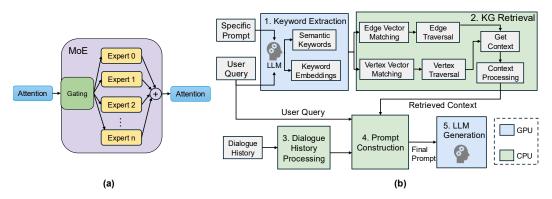

Fig. 2. Overview of Emerging Paradigms: (a) MoE architecture; (b) RAG workflow.

the Key and Value tensors of all preceding tokens, computing attention scores against the full history before appending the current step's KV pairs to the cache.

### 2.2 Emerging Paradigms: MoE and RAG

While dense Transformer architectures have dominated early LLM development, two emerging paradigms are fundamentally reshaping the computational characteristics of LLM inference.

Mixture-of-Experts. MoE represents a fundamental architectural shift from dense computation to sparse activation. By replacing dense feed-forward networks with specialized expert layers, MoE architectures achieve unprecedented decoupling of model capacity from computational cost. As illustrated in Fig. 2(a), a routing network dynamically selects only the top-k experts per token, enabling massive parameter counts while activating minimal computational paths. This sparse activation dramatically reduces FLOPs per token but introduces distinct system challenges: significant routing overhead emerges during sequential Decode, while expert partitioning creates fragmented memory access patterns, establishing new phase-dependent optimization frontiers.

Retrieval-Augmented Generation. RAG transforms LLM inference by integrating explicit knowledge retrieval components. These systems create a heterogeneous CPU-GPU pipeline where external knowledge retrieval precedes LLM execution, fundamentally redistributing system bottlenecks. As shown in Fig. 2(b), performance constraints shift from GPU computational throughput to CPU-side retrieval latency and memory bandwidth saturation. Furthermore, the integration of retrieved knowledge substantially expands effective context length during the Prefill phase, introducing additional computational complexity and memory demands that reshape the entire inference profile.

The RAG workflow comprises five distinct stages. Keyword Extraction: LLM processes the input query to extract semantic keywords and generate embeddings. Knowledge Graph (KG) Retrieval: Hybrid vector and graph-based searches retrieve relevant contextual information. Dialogue History Processing: Management and preparation of previous conversation turns. Prompt Construction: Integration of retrieved context, dialogue history, and current query into the final prompt. LLM Generation: Standard inference execution on the augmented prompt.

The KG Retrieval stage further decomposes into six functional sub-stages. <u>Edge/Vertex Vector Matching</u>: Compute vector similarities to identify relevant graph entities. <u>Edge/Vertex Traversal</u>: Navigate graph structure to expand retrieval scope. <u>Get Context</u>: Acquire textual content associated with retrieved entities. <u>Context Processing</u>: Preprocess and prepare retrieved text for integration. The matching sub-stages handle similarity computation, while the traversal and processing substages manage graph navigation and text preparation, respectively.

# 3 Characterization Methodology

This section details our characterization methodology, experimental setup, and profiling approaches.

### 3.1 Methodology

Our characterization methodology is designed to systematically unravel the performance landscape of LLM inference, moving from symptomatic observation to prescriptive insight. The four steps form a causal chain: we first <u>establish what</u> the core performance phenomena are, then <u>determine why</u> they occur at the hardware level, subsequently <u>validate how</u> these principles govern behavior in realistic systems, and finally <u>explore where</u> the performance boundaries are being redefined by emerging paradigms. These steps are implemented as follows.

- (1) Phenomenon Observation: Establishing the "What" Two-Phase Heterogeneity.

- Objective: Identify the fundamental macroscopic performance characteristics.

- Action: We systematically measure latency distribution, throughput, and energy across diverse application scenarios of LLM inference.

- Outcome: This step establishes the core empirical fact of a fundamental dichotomy between the Prefill and Decode phases, documenting their distinct bottleneck profiles, dynamic migration, and predictable behaviors. It answers what the system's performance symptoms are.

- (2) Root Cause Explanation: Uncovering the "Why" Microarchitectural Etiology.

- Objective: Diagnose the root causes of the two-phase performance dichotomy.

- Action: We employ Roofline modeling to quantify arithmetic intensity, warp stall analysis to pinpoint pipeline bottlenecks, and memory behaviors profiling to assess memory locality.

- Outcome: This step connects macroscopic symptoms to microarchitectural root causes, revealing that Prefill is inherently compute-bound due to high-intensity GEMMs, while Decode is memory-bound due to low-intensity, KV-cache-dominated data access.

- (3) Scaling Effect Analysis: Validating the "How" System-Level Governing Principles.

- Objective: Test how phase-aware principles generalize to scaled and constrained environments.

- Action: We extend the analysis to multi-GPU setups (evaluating Tensor and Pipeline Parallelism) and edge devices (profiling under resource constraints).

- Outcome: This step demonstrates how the root causes dictate system design. It validates that the compute-bound Prefill scales with Tensor Parallelism, while the memory-bound Decode is better served by Pipeline Parallelism, and shows how these bottlenecks are amplified at the edge.

- (4) Boundary Redefinition: Exploring the "Where" Paradigm Shifts.

- Objective: Investigate how new architectural and workflow innovations reshape the established performance boundaries.

- Action: We characterize sparse MoE models and RAG workflows, quantifying their new efficiency trade-offs and bottleneck migrations.

- Outcome: This step looks forward to where the landscape is evolving. It shows how MoE decouples total parameters from active computation, and how RAG shifts the bottleneck from GPU to CPU, thereby redefining the optimization frontier for next-generation systems.

This structured progression from observation to explanation, validation, and foresight ensures our characterization is not merely descriptive, but fundamentally explanatory and prescriptive.

### 3.2 Experimental Setup

To implement our characterization methodology, we established a comprehensive experimental framework comprising the platforms, models, workloads, and profiling methods detailed below.

Model Params (B) Layers Hidden Dim. Attn. Heads (Q/KV) Arch. Experts Llama-3-8B-Instruct 8 4096 32 / 8 Dense Owen2.5-7B-Instruct 7 28 3584 28 / 4 Dense Qwen2.5-32B-Instruct 32 64 5120 40 / 8 Dense Qwen3-30B-A3B-Instruct-2507 30.5 / 3.3<sup>†</sup> 32 / 4 48 2048 MoE | 128 (top-8)

Table 1. Information of evaluated LLMs.

Table 2. Summary of evaluation workloads.

| Scenario  | Dataset                | Input length                 | Output length | #Prompts |

|-----------|------------------------|------------------------------|---------------|----------|

| Chat      | ShareGPT-V3 (sharegpt) | variable (from dataset)      | 128           | 16       |

| Summary   | Sonnet (sonnet)        | 8192                         | 256           | 8        |

| Translate | Synthetic (random)     | 512                          | 512           | 16       |

| Code      | InstructCoder (HF, hf) | variable (from dataset) 2048 |               | 8        |

| Story     | Synthetic (random)     | 256                          | 3072          | 4        |

**Platforms.** We employ two platforms spanning the compute spectrum: a high-performance server with two Intel Xeon Platinum 8350C CPUs and four NVIDIA A100 80GB SXM GPUs (interconnected via NVLink in pairs and PCIe across pairs); and an NVIDIA Jetson AGX Orin for edge-device characterization. All experiments use vLLM v0.9.2 [27] with BF16 precision.

**Models.** Our evaluation covers four instruction-tuned LLMs (see Table 1): the dense models Llama-3-8B-Instruct [9] and Qwen2.5-7B/32B-Instruct [48], which share architectural similarity but differ in scale; and the sparse model Qwen3-30B-A3B-Instruct [54], an MoE model activating 3.3B of its 30.5B total parameters per token. This selection provides a comprehensive testbed covering parameter scales from 7B to 32B across both dense and MoE architectures.

**Workloads.** We evaluate five representative workloads covering common LLM application scenarios, as configured in Table 2. These workloads are strategically chosen to elicit the two-phase behavior central to our analysis: 1) Chat (ShareGPT-V3), interactive dialogue with variable-length inputs; 2) Summary (Sonnet corpus), long-context processing with 8K input tokens; 3) Translation (Synthetic), balanced input-output task; 4) Code Generation (InstructCoder): long-output scenario; 5) Story Writing (Synthetic): creative writing with extended generation.

All experiments use vLLM's offline inference benchmark with fixed request batches to isolate intrinsic execution behavior from arrival dynamics. The synthetic dataset enables precise control over prompt lengths, while real-world datasets provide realistic usage patterns.

**Profiling Methods.** We employ NVIDIA Nsight Systems/Compute for GPU analysis and Intel PCM for CPU microarchitecture characterization in RAG workflows. Experiments run in eager execution mode with high-frequency power sampling via nvidia-smi for energy measurements. All configurations are repeatedly executed and averaged to ensure statistical reliability.

### 4 Phenomenon Observation – Establishing Two-phase Heterogeneity

We begin our characterization by establishing the fundamental macroscopic performance phenomena of LLM inference. Through systematic measurements, we objectively document the intrinsic dichotomy between Prefill and Decode phases—two execution phases that exhibit fundamentally distinct performance signatures. Our analysis reveals that these phases differ radically in their GPU resource utilization patterns and energy efficiency characteristics. Furthermore, we observe dynamic bottleneck migration between phases as input/output lengths and model scales vary, alongside identifying strong predictable relationships: Prefill latency demonstrates a linear dependence on the number of uncached tokens, while total energy consumption scales linearly with output length. This phase establishes the essential "symptom profile" of LLM inference performance, providing the empirical foundation for subsequent root-cause investigation.

<sup>†</sup>Total / activated parameters per token, as reported by the official model card of Qwen3-30B-A3B-Instruct-2507.

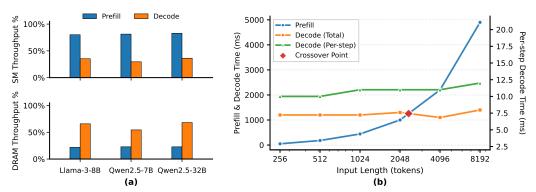

Fig. 3. (a) Overview of SM utilization and DRAM throughput across Prefill and Decode in the Chat scenario. (b) Transition of latency dominance from Decode to Prefill phase under increasing input length and fixed output (128 tokens), measured on Qwen2.5-7B with a single GPU.

### 4.1 Resource Utilization Divergence Between Prefill and Decode Phases

We observe pronounced differences in how the two phases utilize GPU resources. As shown in Fig. 3(a), Prefill exhibits significantly higher Streaming Multiprocessor (SM) utilization than Decode, indicating its stronger dependence on computational throughput. Conversely, Decode demonstrates notably higher memory bandwidth utilization, reflecting its greater demand for data access. This fundamental disparity in resource utilization patterns reveals the intrinsic difference in performance bottlenecks between the two phases. These observations lead to a key insight: ① The Prefill and Decode phases are bottlenecked by different resources: Prefill by computational throughput and Decode by memory bandwidth.

### 4.2 Dynamic Performance Behavior of Prefill and Decode Phases

LLM inference exhibits inherently dynamic performance characteristics, shaped by the complex interplay of workload properties (e.g., input/output lengths), model scales, and system configurations (e.g., batch size). To systematically deconstruct this behavior, we analyze its manifestations across three critical dimensions: first, we examine how latency bottlenecks migrate between phases and principal operators under varying conditions; second, we characterize the dynamic trade-off between throughput and latency as a function of batching strategy; and third, we investigate the predictability of Prefill latency, establishing its deterministic relationship with workload.

4.2.1 Bottleneck Migration. LLM inference is characterized by a dynamic bottleneck migration, where the dominant performance constraint shifts between execution phases and core operators. This subsection systematically unpacks how critical factors—namely input/output length and model scale—govern these transitions, revealing the context-dependent nature of inference performance.

Phase-Level Bottleneck Migration. As illustrated in Fig. 3(b) for Qwen2.5-7B with a fixed output of 128 tokens  $L_{out}$ , the Decode phase accounts for most of the latency at short input lengths  $L_{in}$ . However, as input length grows, the Prefill latency share increases progressively, surpassing Decode after a critical point (around 2k tokens) to become the dominant bottleneck. Notably, the per-step Decode latency remains largely stable, independent of input length. This empirical analysis across models and workloads reveals a consistent pattern: A clear crossover point exists in the latency breakdown between Prefill and Decode as input length increases: Decode dominates at shorter inputs (forming Decode-Dominant regions), while Prefill becomes the bottleneck beyond a critical length (creating Prefill-Dominant regions). This crossover originates in the fundamental complexity differences between the two phases: Prefill performs one-time self-attention over the entire input, with quadratic complexity  $O(L_{in}^2)$ , whereas

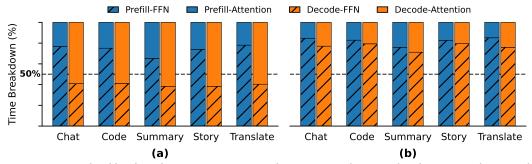

Fig. 4. Operator-level bottleneck migration: transition between FFN-dominated and Attention-dominated latency as context length varies: (a) Llama-3-8B. (b) Qwen2.5-32B.

Table 3. Dominant operator types under different phases, context lengths, and model scales.

| Phase   | Context Length (n)                 | Small Model (8B) | Large Model (32B) |  |

|---------|------------------------------------|------------------|-------------------|--|

| Prefill | Typical context (1K-8K)            | FFN              | FFN               |  |

|         | Extremely long context (>16K-32K+) | Attention        | Attention         |  |

| Decode  | Typical context (1K-8K)            | Attention        | FFN               |  |

|         | Extremely long context (>16K-32K+) | Attention        | Attention         |  |

Decode reuses the KV cache and computes incrementally per token, leading to approximately linear complexity  $O(L_{out})$  and stable per-step cost.

Operator-Level Bottleneck Migration. Within LLM architectures, the FFN and Attention modules collectively account for the majority of inference latency, representing 94% to 96% of the total execution time across phases and scenarios. This predominance reveals that: The vast majority of inference latency is occupied by the FFN and Attention operators. We therefore investigate how the dominant operator shifts between FFN and Attention under varying conditions. As shown in Fig. 4, measurements across typical context lengths (1k–8k) reveal consistent trends. For extremely long contexts (16k–32k+), prior studies [23, 37] have established that Attention emerges as the primary bottleneck in both phases, owing to its rapidly escalating computational and memory overhead. In summary: The bottleneck operator in LLM inference shifts between FFN and Attention as model scale and context length change.

Table 3 details this switching pattern. The underlying mechanism lies in the differing computational complexities of FFN and Attention with respect to context length n. In the *Prefill phase*, FFN scales as O(n) while Attention scales as  $O(n^2)$ . For typical contexts (1K–8K), the quadratic term of Attention is not yet dominant, so the substantial fixed cost of FFN prevails. In extremely long contexts, however, Attention's quadratic cost surpasses FFN, making it the primary bottleneck. In the *Decode phase*, FFN cost per step is roughly constant O(1), while Attention grows linearly O(n) due to full KV-cache traversal. Thus, under typical contexts, large models (e.g., 32B) are FFN-dominated due to high fixed costs, while small models (e.g., 8B) are Attention-dominated. As context length extends further, Attention's linear growth eventually exceeds FFN's fixed cost, causing both model scales to become Attention-dominated in extremely long contexts.

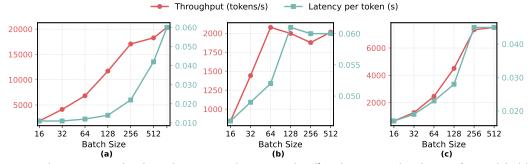

4.2.2 Throughput-Latency Trade-off. We systematically characterize the fundamental yet conflicting relationship between throughput and latency in LLM inference, focusing on how batch size serves as the critical control parameter for balancing this trade-off.

As illustrated in Fig. 5, we characterize the throughput and latency trends under varying batch sizes across three representative models. Our analysis reveals a consistent pattern: 3 A dynamic throughput-latency trade-off exists: as batch size increases, system throughput (tokens/s) rises initially but exhibits diminishing returns, while average decoding latency grows

Fig. 5. Characterizing the throughput versus latency trade-off under varying batch sizes for models (a) Qwen2.5-7B, (b) Qwen2.5-32B, and (c) Qwen3-30B-A3B.

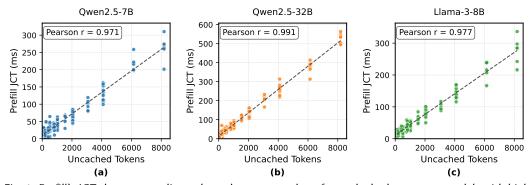

Fig. 6. Prefill's JCT shows strong linear dependence on number of uncached tokens across models with high correlation and slope indicating per-token cost: (a) Qwen2.5-7B, (b) Qwen2.5-32B, and (c) Llama-3-8B.

monotonically, creating a fundamental performance conflict. This behavior stems from two competing effects: larger batches improve GPU utilization and amortize fixed overheads (e.g., kernel launching and scheduling), thereby boosting throughput. However, they also introduce increased queuing delays—since requests within a batch must complete jointly and decoding proceeds token-by-token, inter-step dependencies prolong average waiting time. Beyond a critical batch size, throughput gains plateau while latency penalties accelerate, leading to a *latency trap*.

4.2.3 Predictability of Prefill Latency. The predictability of Prefill phase latency (Job Completion Time, JCT) is crucial for understanding system behavior and constructing effective scheduling models. Unlike the autoregressive Decode phase, which involves sequential dependencies and sampling variability, the computational workload of Prefill is determined solely by the number of input tokens, suggesting inherent deterministic behavior. Our experimental results confirm this hypothesis:

TCT of Prefill phase exhibits a strong linear relationship with the number of uncached tokens, enabling highly accurate latency prediction.

We systematically evaluate Prefill's JCT across three representative models. Input lengths covered short to long contexts  $n_{\text{input}} \in \{1,024, 2,048, 4,096, 8,192\}$ , with KV cache hit ratios varied as  $r \in \{0\%, 25\%, 50\%, 75\%, 90\%\}$ . For each  $(n_{\text{input}}, r)$  combination, we execute prefill-only inference—generating exactly one output token—multiple times, recording the Prefill's JCT and the number of uncached tokens, defined as:  $n_{\text{uncached}} = n_{\text{input}} - n_{\text{cached}}$ . As shown in Fig. 6, Prefill's JCT exhibits a strong linear correlation with  $n_{\text{uncached}}$  across all three models. The Pearson correlation coefficients are: c = 0.971 for Qwen2.5-7B, c = 0.991 for Qwen2.5-32B, c = 0.977 for Llama-3-8B. The relationship is well-approximated by the linear model: JCT  $\approx a + b \times n_{\text{uncached}}$ , where the coefficient b reflects the average computational cost per uncached token, measured as approximately

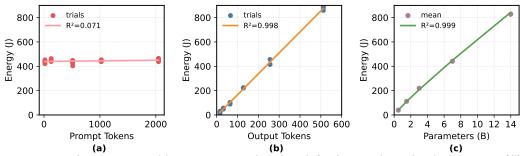

Fig. 7. Energy characterization: (a) Energy vs. input length with fixed output (256 tokens), showing Prefill's minimal contribution; (b) Energy vs. output length with fixed input (64 tokens), demonstrating strong linear dependence; (c) Energy scaling with model parameters under fixed workload (64-input, 256-output tokens).

0.0312 ms/token (Qwen2.5-7B), 0.0612 ms/token (Qwen2.5-32B), and 0.0324 ms/token (Llama-3-8B). Notably, the unit cost increases with model scale, indicating higher computational demand for larger models. A marginally weaker correlation observed at shorter input lengths ( $\sim$  1K) is due to the relatively larger impact of fixed overheads and measurement jitter in such regimes.

### 4.3 Energy Analysis

Energy efficiency has become a critical concern in LLM inference, especially for large-scale deployments where power consumption directly impacts operational costs and environmental sustainability. This subsection presents a comprehensive analysis of energy consumption patterns across different phases, output lengths, and model scales, with the goal of establishing predictable energy models. We conduct energy measurements in a single A100 GPU environment. Our measurement methodology employs a precise power sampling approach. Before each inference task, we record GPU idle power for 10 seconds and compute the average as  $P_{\text{baseline}}$ . During inference execution, we sample instantaneous power  $P_{\text{sample}}(t)$  at 100ms intervals using nvidia-smi-query-gpu=power.draw. Finally, we compute net energy consumption by integrating baseline-adjusted power over the task duration:  $E_{\text{net}} = \int_{\text{start}}^{\text{end}} \max \left(P_{\text{sample}}(t) - P_{\text{baseline}}, 0\right) dt$ .

4.3.1 Energy vs. Workload. To dissect the energy contributions of Prefill and Decode phases, we systematically varied input and output lengths while measuring total energy consumption.

When fixing output length at 256 tokens and increasing input length from 16 to 2048 tokens (Fig. 7(a)), total net energy remains nearly constant at  $\approx 440$  J (fluctuation within  $\pm 2\%$ ), exhibiting extremely low correlation with input length ( $R^2=0.071$ ). This leads to our first energy insight:

**②** LLM inference energy consumption is dominated by the Decode phase, with Prefill contributing negligibly to total energy. Although Prefill is computationally intensive, its one-time execution contributes minimal energy compared to the hundreds of memory-access-dominated iterations in Decode phase, where KV Cache operations accumulate to dominate total energy.

Conversely, when fixing input length and varying output length (Fig. 7(b)), we observe a fundamentally different pattern: § Energy consumption exhibits a highly linear relationship with the number of output tokens ( $R^2 = 0.999$ ). The fitted relationship  $E = 1.72 \times L_{out} - 6.48$  reveals a marginal energy cost of approximately 1.72 J per generated token. The small intercept ( $\approx 6.5$  J) further confirms the minimal energy contribution of Prefill.

4.3.2 Energy vs. Model Scale. We further investigate the relationship between energy consumption and model scale by measuring total net energy across models ranging from Qwen2.5-0.5B to 14B under a fixed workload (64 input tokens, 256 output tokens).

As shown in Fig. 7(c), energy consumption exhibits a strong dependence on model scale: **9 Energy consumption scales near-linearly with model parameter count**  $P(R^2 = 0.998)$ **.** The

experimental data is well-characterized by both a power-law fit ( $E = 76.6 \times P^{0.91}$ ) with exponent close to 1, and a linear relationship (E = 28.2 + 57.7P). The observed near-linear energy scaling stems from larger models concurrently elevating instantaneous power draw and prolonging execution time, with their product dictating the total energy consumption.

4.3.3 Predictability of Inference Energy. Our analysis establishes that **10 LLM inference energy consumption can be accurately predicted from prompt features prior to execution.** This capability derives from a composite function: prior work [61] enables output length prediction from prompts ( $L_{out} \approx g(\text{Prompt})$ ), while our results confirm a strong linear energy-length relationship ( $E \approx f(L_{out})$ ). Thus,  $E \approx f(g(\text{Prompt}))$  provides early energy estimation for incoming requests.

# 5 Root Cause Explanation: Determining the "Why" - Microarchitectural Etiology

While above analysis established the pronounced two-phase heterogeneity in LLM inference, these findings remain at the level of aggregate performance metrics. Fundamental questions persist: which underlying operators drive these phase differences, and how are GPU execution resources utilized—or wasted—in each phase? To uncover the microarchitectural mechanisms behind the macroscopic observations, this section systematically investigates the computational roots of phase divergence. We first identify and quantify the core CUDA kernels dominating execution time, then employ Roofline analysis to diagnose their resource constraints, followed by warp stall analysis to pinpoint hardware-level inefficiencies, and finally examine memory access patterns.

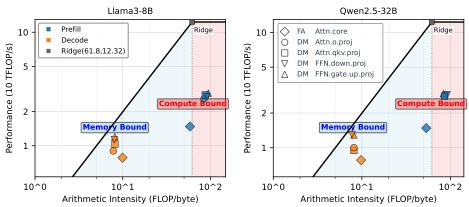

#### 5.1 Execution Bounds Analysis

This subsection identifies and categorizes the CUDA kernels responsible for the majority of execution time, analyzing their computational characteristics and hardware resource constraints.

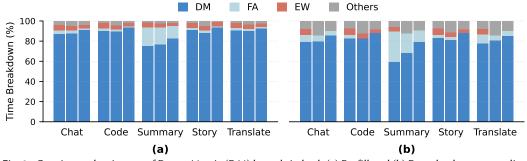

5.1.1 Kernel Classification and Time Distribution. We focus on the top-5 most time-consuming CUDA kernels, which collectively account for >90% of Prefill and >85% of Decode execution time. Analyzing these critical kernels reveals the core computational patterns in each phase.

We classify these dominant kernels into three categories based on their computational roles in LLM architectures: 11 The top-5 kernels fall into three categories: DM (Dense Matrix), FA (Fused Attention), and EW (Element-wise). The DM comprises dense matrix multiplications (GEMM) for FFN (gate-up, down) and attention (Q/K/V, output) projections. The FA includes fused attention kernels (e.g., FlashAttention) that minimize memory movement. The EW covers element-wise operations like activation, normalization, and positional encoding.

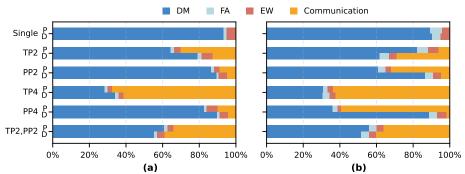

From Fig. 8(a) and (b), we observe a striking pattern: Despite fundamental performance differences, Prefill and Decode share remarkably similar kernel-type distributions, with

Fig. 8. Consistent dominance of Dense Matrix (DM) kernels in both (a) Prefill and (b) Decode phases, revealing similar computational structures despite divergent performance characteristics. In each scenario group, the three bars represent Llama-3-8B, Qwen2.5-7B, and Qwen2.5-32B respectively from left to right.

Fig. 9. Roofline analysis of major kernels under the Chat scenario, measured on Tensor Cores.

**DM kernels dominating execution time in both phases.** This distribution similarity despite phase heterogeneity indicates that the core computational patterns remain consistent, while kernel efficiency and resource utilization differ substantially.

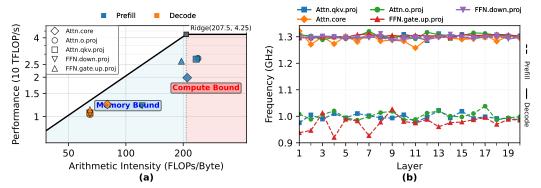

*5.1.2 Roofline Analysis.* The Roofline model relates arithmetic intensity (AI) to achievable performance, offering an intuitive method to diagnose whether an operator is compute-bound or memory-bound. Fig. 9(a) and (b) illustrates the Roofline distributions of key kernels for two representative models—Llama3-8B and Qwen2.5-32B—under the Chat scenario.

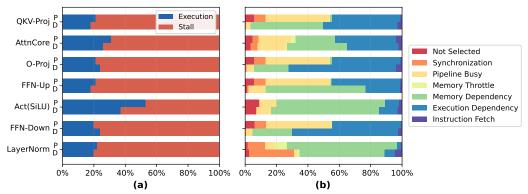

### 5.2 Issue Stall Analysis

While Roofline analysis identifies resource bounds, GPU stall behavior explains the performance divergence between Prefill and Decode. Our warp-level analysis in Fig. 10(a) reveals that both phases exhibit low GPU *Execution* (Prefill: 27%, Decode: 24%), meaning 70%–80% of cycles are spent stalled. However, the root causes differ fundamentally between phases, as detailed in Fig. 10(b).

5.2.1 Prefill Phase Stalls. In Prefill, GEMM-intensive kernels including QKV-Proj, O-Proj, FFN-Up, and FFN-Down are predominantly stalled by Execution Dependency ( $\approx$ 39%) and Pipeline Busy ( $\approx$ 37%), as shown in Fig. 10(b). This pattern uncovers the microarchitectural basis for Prefill's compute-bound nature: Prefill experiences dual saturation of computational throughput

Fig. 10. Issue stall analysis for **Llama3-8B** inference in the **Chat** scenario. (a) Proportion of stall time to total execution time; (b) Detailed breakdown of stall causes across Prefill and Decode phases. Abbreviations: QKV-Proj: Query/Key/Value projection; AttnCore: Core attention computation (e.g., FlashAttention); O-Proj: Output projection of Attention; FFN-Up: Up-projection and gating fusion in the feed-forward network; Act (SiLU): Activation and element-wise multiplication in FFN; FFN-Down: Down-projection layer in FFN; LayerNorm: Layer normalization; P: Prefill; D: Decode.

and instruction latency: high Pipeline Busy indicates sustained Tensor Core utilization, while Execution Dependency reflects warps waiting for long-latency HMMA instructions.

The low Memory Dependency (24%) confirms effective memory latency masking through high AI and data reuse. Attention kernels show balanced stall distributions, aligning with their memory-aware design, while element-wise operations like Act (SiLU) remain memory-dependent.

5.2.2 Decode Phase Stalls. Decode's stall profile shifts fundamentally: Pipeline Busy plunges to 3~4%, while Memory Dependency dominates. This reveals that **6** Decode is primarily memory-bound, as limited parallelism and intensive KV-cache access make memory latency the primary bottleneck. This shift is particularly evident in Attention kernels (AttnCore), where the dominant stall transitions from Execution Dependency (32.8% in Prefill) to Memory Dependency (32.7% in Decode), consistent with intensive KV-cache operations. Further analysis reveals heterogeneous bottlenecks among Decode's GEMM kernels: FFN-Up is memory-bound, with Memory Dependency reaching 58% due to GEMV-like computation patterns that cannot hide HBM weightloading latency. O-Proj/FFN-Down are execution-bound, with Execution Dependency reaching 51% due to extreme register pressure (≈130 live registers) that limits schedulable warps and prevents HMMA latency hiding. This reveals: **17** Decode's GEMM kernels exhibit heterogeneous bottlenecks: FFN-Up is memory limited, while O-Proj/FFN-Down are instruction-dependency bound. Additionally, LayerNorm shows significantly increased Synchronization stalls (from 11.0% to 27.7%), revealing: **18** Small-batch reduction operations in Decode exacerbate synchronization overhead, as early-finishing warps wait at barriers, creating tail latency effects.

# 5.3 Memory Pattern Analysis

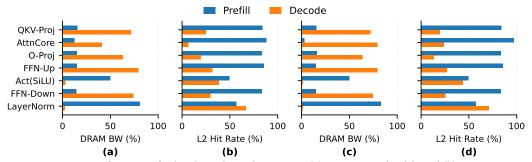

We complete our microarchitectural characterization by examining the memory behavior that distinguishes Prefill and Decode phases. Using DRAM bandwidth utilization and L2 cache hit rate as key metrics, we analyze kernel-level memory patterns across Chat (Fig. 11(a) and (b)) and Summary (Fig. 11(c) and (d)) scenarios in Llama-3-8B. Phase transitions are quantified via median per-kernel differences between Decode and Prefill, providing a robust measure of trend shifts.

Fig. 11. Memory performance for key kernels in Llama-3-8B. (a) DRAM Bandwidth and (b) L2 Hit Rate in Chat scenario; (c) DRAM Bandwidth and (d) L2 Hit Rate in Summary scenario.

a clear shift toward higher DRAM bandwidth dependence and lower data locality. This fundamental divergence stems from intrinsic computational differences: Prefill leverages large GEMM operations with extensive data reuse, while Decode's token-by-token execution and frequent KV-cache accesses result in insufficient arithmetic intensity to hide memory latency.

5.3.2 Operator-Level Memory Patterns. We analyze how memory behavior shifts across operators from Prefill to Decode. Attention Kernels suffer severe locality degradation, with L2 hit rates dropping 81.9% (Chat) and 73.3% (Summary), while DRAM utilization increases up to 76.4%. Attention kernels transition from compute-friendly to memory-bound due to exhaustive KV-cache scanning. Prefill's consolidated access maximizes reuse, whereas Decode's scattered reads across the KV-cache destroy locality, making performance bandwidth-bound. FFN Kernels exhibit a bottleneck shift, with DRAM utilization rising 62% and arithmetic intensity plummeting from ~95 to ~8 FLOP/byte. FFN transitions from compute-bound to memory-bound, with weight-loading bandwidth as the primary constraint. Prefill's batch GEMM reuses weights, while Decode's per-token GEMVs reload weights from DRAM. LayerNorm shows improved locality (DRAM utilization drops 78%–82%, L2 hit rates slightly increase). Its small working set fits in on-chip caches, preventing it from becoming a bottleneck.

5.3.3 Scenario-Dependent Memory Behavior. We dissect how memory behavior varies across scenarios, focusing on how context length interacts with phase-specific memory characteristics. Comparative analysis reveals contrasting trends between Chat and Summary scenarios: AttnCore DRAM utilization increases by an additional 38.1% in Decode when transitioning to the long-context Summary scenario, while Prefill utilization decreases by 9.3%. This divergence confirms: Extended context lengths systematically amplify the memory bottleneck in attention kernels. This occurs because Prefill leverages enhanced data reuse, while Decode's linearly growing KV-cache footprint intensifies bandwidth pressure, further entrenching its memory-bound nature.

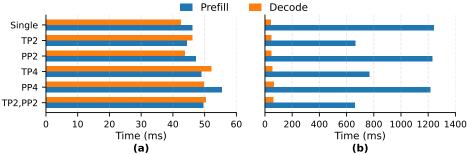

## 6 Scaling Analysis: Validating the "How" - System-Level Governing Principles

With the root causes established, we examine how these phase-aware principles govern performance in deployment scenarios. In multi-GPU environments, we demonstrate that the compute-intensive Prefill achieves optimal scaling through Tensor Parallelism (TP) [45], while the memory-intensive Decode benefits more from Pipeline Parallelism (PP) [21] due to reduced communication overhead. When extending to edge devices, we observe that resource constraints amplify these phase-specific characteristics: memory bandwidth limitations exacerbate Decode bottlenecks, while thermal constraints trigger frequency throttling that particularly impacts Prefill performance. These scaling experiments validate that the two-phase paradigm persists across system scales.

Table 4. Performance comparison of different parallelization strategies across two representative workloads: Chat with short input and long output; Summary with long input and short output.

| Workload | Metric                | Single | TP2   | PP2    | TP4    | PP4    | TP2+PP2 |

|----------|-----------------------|--------|-------|--------|--------|--------|---------|

| Chat     | Throughput (tokens/s) | 22.16  | 20.53 | 21.08  | 18.55  | 18.54  | 18.18   |

|          | Latency (ms/token)    | 45.12  | 48.72 | 47.43  | 53.92  | 53.94  | 55.01   |

| Summary  | Throughput (tokens/s) | 8.19   | 11.21 | 8.22   | 8.77   | 7.40   | 10.65   |

|          | Latency (ms/token)    | 122.16 | 89.19 | 121.67 | 114.06 | 135.17 | 93.94   |

Fig. 12. Prefill and decode (per-step) latency under different parallelization strategies across two representative workloads: (a) Chat with short input and long output; (b) Summary with long input and short output.

### 6.1 Multi-GPU Scaling Laws

Building on the phase-aware scaling foundation, we evaluate parallelization strategies against the distinct computational profiles of Prefill and Decode in multi-GPU environments. We systematically compare tensor, pipeline, and hybrid parallelism. Using Qwen2.5-32B on four A100s, we test five configurations: Single (1-GPU baseline), TP2 (2-GPU tensor parallelism), PP2 (2-GPU pipeline parallelism), TP4 (4-GPU tensor parallelism), PP4 (4-GPU pipeline parallelism), and TP2+PP2 (4-GPU hybrid parallelism with two TP2 groups forming pipeline stages). Two workloads represent key scenarios: Chat (64-input, 128-output) for Decode-dominant and Summary (4096-input, 16-output) for Prefill-dominant patterns, enabling a comprehensive study of phase-dependent parallelization.

6.1.1 Overall Performance. We evaluate end-to-end performance across workloads to establish how parallelization interacts with phase-specific patterns, with results shown in Table 4 and Fig. 12.

Chat Scenario: Decode-Dominant. Single-GPU achieves optimal throughput (22.2 tokens/s), while parallel configurations reduce it (TP2: 20.5, PP2: 21.1) and increase latency (45.1 ms/token to 53.9−55.0 ms/token). Phase-level analysis in Fig. 12(a) reveals that while TP2 slightly reduces Prefill latency (46.1 ms → 44.4 ms), Decode latency consistently increases due to communication and synchronization overhead. This leads to a critical finding: To Decode-dominant workloads, communication and synchronization costs outweigh computational parallelism benefits, making single-GPU execution optimal for both latency and throughput.

Summary Scenario: Prefill-Dominant. Tensor parallelism excels: TP2 boosts throughput by 36.6% (11.2 tokens/s) and cuts latency by 27% (89.2 ms/token). TP dramatically shortens Prefill (1.24 s  $\rightarrow$  0.66 s) as shown in Fig. 12(b). Pipeline parallelism shows minimal gains (PP2: 8.2 tokens/s) or degradation (PP4: 7.4 tokens/s), establishing: 24 Prefill-dominant workloads benefit substantially from tensor parallelism, which effectively distributes GEMM computation, while pipeline parallelism suffers from stage serialization and bubble overhead.

These results reveal fundamental phase-dependent scaling, leading to a crucial design insight:

Optimal parallelization is phase-aware: Prefill scales with tensor parallelism, while Decode performs best on single-GPU or tuned pipeline parallelism.

Fig. 13. Kernel-level time decomposition under different parallelization strategies: (a) Chat scenario (Decode-dominated workload) and (b) Summary scenario (Prefill-dominated workload). P and D denote Prefill and Decode phases respectively. Stacked bars show the proportional time spent in DM (Dense Matrix), FA (Fused Attention), EW (Element-Wise), and Communication operations.

*6.1.2 Time Breakdown.* To elucidate performance variations, we decompose kernel time into DM, FA, EW, and Communication, with breakdowns for both Chat and Summary shown in Fig. 13.

Chat Scenario: Decode-Dominant. Single-GPU execution is dominated by DM kernels (>93%), with FA and EW contributing 7%. Multi-GPU configurations diverge sharply: TP introduces substantial Communication overhead (30% in Prefill, >60% in Decode for TP4), while PP maintains high DM share (83–90%) with low Communication (5–10%). The hybrid TP2+PP2 shows intermediate Communication levels. This divergence stems from communication patterns: TP requires frequent collective operations (e.g., All-Reduce) per layer, and in Decode-dominant workloads, minimal per-step computation cannot amortize this overhead, making communication dominant. PP, with only infrequent activation transfers at stage boundaries, preserves computational efficiency.

Summary Scenario: Prefill-Dominant. TP2 introduces modest Communication (6%) while drastically reducing Prefill latency (1.24 s  $\rightarrow$  0.66 s) by parallelizing DM kernels. PP2, however, incurs high Communication (32%) without proportional computational benefit, maintaining similar Prefill latency (1.23 s). Aggressive configurations (TP4/PP4) become communication-dominant (59–64%).

Our analysis establishes: 26 Multi-GPU scaling efficiency is governed by the computation-communication balance. Tensor parallelism justifies its cost in compute-intensive Prefill but fails in Decode, where per-step computation is too small to amortize overhead.

### 6.2 Edge-Scaling Characteristics

Edge devices present fundamentally different computational constraints compared to data-center GPUs, characterized by limited compute capability, reduced memory bandwidth, and strict power budgets. To understand how LLM inference behavior scales under these constraints, we deploy Llama3-8B on an NVIDIA Jetson AGX Orin platform. By contrasting Roofline distributions and SM frequency characteristics with our A100 findings, we characterize how performance bottlenecks transform when the same model executes on resource-constrained edge systems.

*6.2.1 Kernel-level Roofline.* We examine how computational patterns translate to edge devices via Roofline analysis (Fig. 14), revealing how constraints reshape performance boundaries.

<u>Prefill Phase.</u> Self-attention kernels (QKV-Proj, O-Proj, FlashAttention) maintain high AI near the compute-bound region, indicating stable computational characteristics across platforms. In contrast, FFN GEMM kernels shift dramatically: limited cache and LPDDR bandwidth force frequent data movement, reducing AI and causing a fundamental bottleneck transformation: **27** FFN kernels transition from compute-bound on data-center GPUs to memory-bound on edge devices, exhibiting heightened sensitivity to memory bandwidth and cache resources.

Fig. 14. Computational characteristics of Llama3-8B on Jetson AGX Orin: (a) Roofline analysis showing AI versus achieved performance for key kernels across Prefill and Decode; (b) SM frequency distribution across transformer layers under 1.3 GHz frequency cap, revealing phase-dependent DVFS behavior.

<u>Decode Phase.</u> Both attention and FFN kernels cluster strongly in the bandwidth-limited region with low AI. The combination of small per-step computation and intensive KV-cache access creates overwhelming memory pressure: Decode performance becomes dominated by KV-cache data movement, exhibiting extreme memory-bandwidth sensitivity that amplifies the Prefill-Decode bottleneck divergence.

Collectively, LLM inference in edge devices exhibits systematically stronger memory-bound characteristics compared to data-center environments, especially impacting FFN and Decode.

6.2.2 Frequency Behavior and DVFS Effects. Building on Roofline analysis, we examine how dynamic voltage and frequency scaling (DVFS) interacts with phase-specific patterns. Fig. 14(b) presents SM frequency distributions of key kernels under Jetson's 1.3 GHz frequency cap.

<u>Prefill Phase.</u> In Prefill, compute-intensive GEMM kernels (QKV-Proj, O-Proj, Gate-Up-Proj) operate at significantly reduced average frequencies compared to the maximum cap, while FlashAttention maintains frequencies closer to the maximum due to its more balanced compute-memory profile. This frequency throttling indicates that on power-constrained edge devices, compute-bound kernels trigger aggressive DVFS mechanisms, sacrificing peak performance to manage instantaneous power consumption and thermal dissipation.

<u>Decode Phase.</u> In contrast, Decode phase exhibits substantially different frequency behavior. Dominated by memory-intensive KV-cache operations rather than computational workloads, Decode maintains smoother frequency profiles that remain closer to the maximum cap across layers. The reduced computational intensity generates lower instantaneous power demand, minimizing thermal pressure and DVFS-induced frequency reductions.

This frequency analysis reveals a crucial dimension of phase heterogeneity: 22 Edge devices exhibit phase-dependent DVFS behavior: compute-intensive Prefill triggers significant frequency throttling to manage power/thermal constraints, while memory-bound Decode maintains higher frequencies due to reduced computational pressure. Prefill thus faces dual computational and power constraints, while Decode remains memory-subsystem limited.

### 7 Redefining Boundaries: Exploring the "Where" - Paradigm Shifts

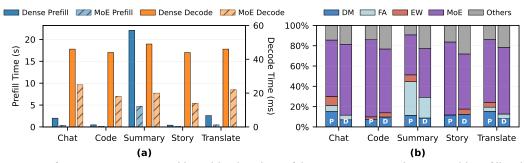

Finally, we investigate how emerging model architectural and workflow innovations are redefining LLM inference performance boundaries. For model architecture, we characterize how MoE designs decouple total parameter count from computational cost via sparse activation, reducing latency while introducing new routing overheads that become pronounced in Decode. In workflow integration, we reveal how RAG shifts system bottlenecks from GPU computation to CPU-side memory

Fig. 15. Performance comparison and kernel-level analysis of dense versus MoE architectures: (a) Prefill and per-step Decode latency comparison between Qwen2.5-32B (dense) and Qwen3-30B-A3B (MoE); (b) Kernel time decomposition for the MoE model across five application scenarios.

Fig. 16. Decode-phase FFN efficiency comparison under varying batch sizes: (a) Arithmetic intensity evolution; (b) SM and DRAM utilization patterns; (c) L2 cache behavior for dense versus MoE architectures.

access during retrieval operations, creating a new heterogeneous execution paradigm. These investigations demonstrate that while the two-phase perspective remains relevant, new architectures and workflows are actively reshaping where and how performance bottlenecks manifest.

#### 7.1 Tradeoffs in MoE Architecture

We explore MoE tradeoffs and how architecture transforms inference bottlenecks by comparing dense and MoE models across five scenarios. Measurements of Prefill/Decode latency and kernel-level time distributions reveal how sparse activation introduces distinct overhead patterns.

Performance-Overhead Tradeoffs. To uncover MoE's performance-cost trade-offs, we examine kernel-level time distributions. Our analysis compares end-to-end latency between architectural paradigms (Fig. 15(a)) and decomposes MoE execution (Fig. 15(b)) using DM/FA/EW categories augmented with "MoE" (expert operation) and "Others" (routing and auxiliary operations). The model achieves significant speedups (4.56× Prefill, 2.39× Decode) over dense equivalents, revealing:

MoE architectures decouple model capacity from computational cost, with inference performance determined by activated parameters rather than total parameter count. Time decomposition shows Prefill is dominated by expert operation (39.4%–76.0%) with minimal routing overhead (9.3%–16.3%). In Decode, expert operation remains substantial (48.0%–69.8%) but routing overhead surges to 18.6%–28.1%, becoming the second-largest cost. This phase-dependent pattern arises because Prefill's parallelization amortizes routing latency, while Decode's sequential generation exposes it, establishing:

MoE exhibits phase-dependent patterns: Prefill is dominated by expert operations, while Decode incurs substantial routing overhead that becomes a major performance factor alongside expert computation.

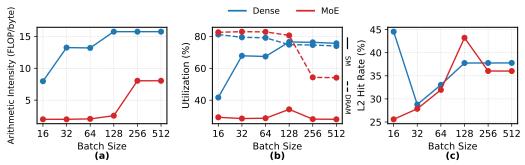

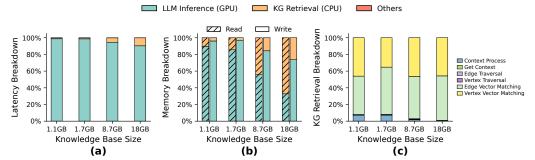

Fig. 17. Characterizing RAG scalability: (a) Latency distribution between GPU inference and CPU retrieval across knowledge base sizes; (b) Memory traffic breakdown; (c) Detailed time breakdown of KG retrieval.

FFN Efficiency Tradeoffs. We now focus on Decode-phase FFN efficiency, comparing dense and MoE models across batch sizes in: arithmetic intensity (Fig. 16(a)), SM and DRAM utilization (Fig. 16(b)), and cache behavior (Fig. 16(c)). Arithmetic intensity reveals a fundamental gap: the dense model's FFN intensity grows to 15.74 FLOP/byte, while MoE remains low (8 FLOP/byte) due to 2 MoE routing distributes global batches across experts, creating small per-expert effective batches that prevent computational intensity from reaching dense model levels, fundamentally constraining GEMM efficiency. Hardware utilization further illuminates the divergence: dense FFNs scale strongly toward compute-bound operation (SM utilization 41.7%→76.5%, decreasing DRAM pressure), while MoE FFNs sustain both low SM utilization (28%-34%) and high DRAM pressure (>80% at small batches). This reveals: 33 MoE FFNs operate under simultaneous computational underutilization and memory bandwidth saturation, demonstrating how sparse expert partitioning trades computational efficiency for model capacity. Cache analysis completes the picture and reveals MoE's batch-sensitive locality: at small batches, L2 hit rates are poor (25.6% vs. dense 44.6%) due to fragmented expert weight reuse; however, at larger batches (128), it surpasses dense models (43.2% vs. 37.8%) as token concentration within experts improves. This demonstrates: 31 MoE cache efficiency exhibits strong batch size dependence, requiring substantial concurrency to achieve effective weight reuse through expert-focused token routing.

Collectively, MoE Decode-phase FFNs face compounded challenges from fragmentation, bandwidth saturation, and sensitive cache behavior.

### 7.2 Workflow Design: RAG-in-the-Loop

Retrieval-augmented generation [30] has become a standard paradigm to incorporate external knowledge. While prior analysis focused on GPU-centric inference, we examine how integrating retrieval reshapes system bottlenecks. We implement a hybrid RAG workflow using LightRAG [15].

End-to-End Workflow Scalability. Fig. 17(a) shows workload evolution with knowledge base scale: CPU-side KG retrieval incurs increasingly higher latency share as the knowledge base grows (1.1 GB to 18 GB), becoming non-negligible at large scales. Memory analysis (Fig. 17(b)) confirms this shift, showing KG retrieval dramatically increases CPU-side memory traffic while GPU patterns remain stable. This reveals: Scaling knowledge bases triggers a bottleneck shift from GPU computation to CPU-side retrieval and memory overhead. This establishes a new heterogeneous paradigm where the pipeline is jointly constrained by GPU throughput and CPU memory efficiency.

<u>Time Decomposition of KG Retrieval.</u> Time breakdown in Fig. 17(c) pinpoints the CPU bottleneck: with large knowledge bases, Edge and Vertex Matching dominate retrieval time, while graph

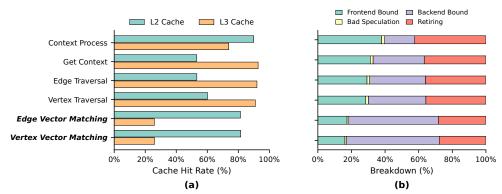

Fig. 18. CPU microarchitectural analysis of retrieval stage (18 GB knowledge base): (a) Cache hierarchy efficiency across sub-stages; (b) Pipeline utilization patterns revealing bottleneck sources.

traversal (Edge/Vertex Traversal) and text processing (Get Context, Context Process) are minimal. This shows the primary cost is similarity matching computation over the expanding vector store, not complex graph operations. As the knowledge base grows, the linear-scaling vector store drives computation overhead, while sparse graph connectivity limits traversal growth. This divergence leads to a crucial architectural insight: 36 Graph-RAG workloads are ultimately constrained by similarity computations rather than graph traversal: similarity matching dominates CPU cost, while graph operations contribute minimally to overall latency.

Microarchitectural Characteristics of KG Retrieval. We now examine the microarchitectural manifestations of KG retrieval bottlenecks. Cache analysis (Fig. 18(a)) shows the dominant matching operations exhibit high L2 hit rates but low L3 utilization, characteristic of a streaming workload with strong spatial but weak temporal locality. Pipeline analysis (Fig. 18(b)) further reveals these operations are predominantly Backend Bound, indicating CPU cores stall waiting for data despite efficient control flow. Combining these perspectives yields: Similarity matching in Graph-RAG is a memory-bandwidth-bound streaming workload, constrained by memory throughput, not compute capability.

#### 8 Optimization Guidelines

The key insights are summarized in Table 5.

Grounded in our systematic characterization and insights, we propose the following guidelines. **System Architecture and Scheduling.** (1) Phase-Decoupled Serving. Route Prefill to compute-optimized instances and Decode to bandwidth-rich hardware (1), (3) [19, 39, 62]. Use Chunked Prefill for interleaved execution where hardware disaggregation is infeasible, mitigating the *latency trap* in mixed workloads (3) [1]. (2) Predictability-Driven Scheduling. Employ Shortest Remaining Processing Time scheduling based on linear Prefill latency scaling with uncached tokens (6) [8]. Implement energy-aware throttling and placement strategies using the predictable linear relationship between energy consumption and output length (3), (10).

Microarchitecture and Kernel Optimization. (1) Prefill Latency Hiding. Address Tensor Core saturation and HMMA instruction latency through instruction-level parallelism, software pipelining, and K-tile double buffering [17] (13, 15, 14). Utilize persistent GEMM-style kernels and warp-level prefetching to sustain pipeline occupancy [7]. (2) Decode Weight Optimization. Apply weight-only quantization to memory-bound FFN-Up layers to alleviate bandwidth pressure [13, 33](17, 21). For execution-bound O-Proj/FFN-Down kernels, optimize register allocation or employ operator fusion (17). (3) KV-Cache Bandwidth Management. Reduce memory footprint via Grouped Query Attention [2] and KV-cache quantization [18] (19, 20, 22).

## (1) Performance Bottlenecks are Phase-Dependent and Dynamic

- A clear crossover point exists in the latency breakdown between Prefill and Decode as input length increases: Decode dominates at shorter inputs, while Prefill becomes the bottleneck beyond a critical length.

- At the operator level, the bottleneck migrates between the Feed-Forward Network and Attention. Feed Forward Network typically dominates at typical context lengths, whereas Attention becomes the primary bottleneck under extremely long contexts due to its quadratic (Prefill) or linear (Decode) complexity scaling.

- Microarchitecturally, Prefill is fundamentally compute-bound, with high Arithmetic Intensity and Tensor Core utilization, whereas Decode is memory-bound, constrained by frequent KV-Cache accesses and low Arithmetic Intensity.

#### (2) Energy Consumption is Predictable and Decode-Centric

- Total energy is dominated by the Decode phase and exhibits a strong linear relationship with the number of output tokens ( $R^2 > 0.99$ ). The Prefill phase contributes negligibly to total energy.

- Energy consumption scales near-linearly with model parameter count, as larger models incur both higher instantaneous power draw and longer execution times.

- Combined with the predictability of output length from prompts, energy consumption can be accurately forecasted before request execution.

### (3) Scaling Laws are Governed by Phase Characteristics

- In multi-GPU setups, Prefill benefits from Tensor Parallelism due to its compute-bound nature, achieving near-linear scaling. In contrast, Decode gains little from Tensor Parallelism and is often optimal on a single GPU or with Pipeline Parallelism, as communication overhead outweighs computational benefits.

- On resource-constrained edge devices, constraints are amplified: memory bandwidth limitations exacerbate Decode bottlenecks, while thermal/power constraints trigger frequency throttling that particularly impacts Prefill performance.

### (4) Emerging Architectures and Workflows Reshape Bottlenecks

- MoE decouples model capacity from computational cost, achieving superior latency and throughput by activating a subset of parameters. However, they introduce significant routing overhead in Decode, which becomes a major performance factor.

- In RAG workflows, scaling the knowledge base triggers a bottleneck shift from GPU computation to CPUside memory access during retrieval operations, forming a heterogeneous CPU-GPU execution paradigm.

Parallelism Strategy Selection. (1) Phase-Adaptive Parallelism. Assign Tensor Parallelism to Prefill-heavy workloads and Pipeline Parallelism (or single-GPU execution) to Decode-heavy scenarios(23), 24, and 25). Employ dynamic parallelism switching or heterogeneous configurations. (2) Communication-Computation Overlap. Split projection matrices into moderate-sized chunks to enable overlapping of collective communication with GEMM computation (23), 26).

**Domain-Specific Optimizations.** (1) Bandwidth-Aware Edge Execution. Prioritize bandwidth conservation and thermal stability over peak throughput (28, 27, 29). Limit batch sizes and optimize memory layouts for LPDDR characteristics (29). (2) Locality-Aware MoE Routing. Implement expert-affinity scheduling to improve weight locality under small effective batches (31, 34). Group requests activating the same experts while balancing load (32). (3) Accelerated Retrieval in RAG. Offload similarity computation to near-memory accelerators when feasible (33, 37).

### 9 Conclusion

This study establishes a systematic multi-level characterization for LLM inference optimization, encompassing microarchitectural profiling, energy consumption analysis, and system scaling evaluation. The resulting insights provide both foundational principles for architecture-system co-design and actionable optimization strategies, enabling efficient LLM deployment across heterogeneous computing environments spanning from cloud data centers to resource-constrained edge devices.

#### References

- [1] Amey Agrawal, Nitin Kedia, Ashish Panwar, et al. 2024. Taming Throughput-Latency Tradeoff in LLM Inference with Sarathi-Serve. In 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI 24).

- [2] Joshua Ainslie, James Lee-Thorp, Michiel de Jong, et al. 2023. GQA: Training Generalized Multi-Query Transformer Models from Multi-Head Checkpoints. In *Proceedings of the 2023 Conference on Empirical Methods in Natural Language Processing (EMNLP)*.

- [3] Afsara Benazir and Felix Xiaozhu Lin. 2025. Profiling Large Language Model Inference on Apple Silicon: A Quantization Perspective. arXiv preprint arXiv:2508.08531 (2025).

- [4] Weilin Cai, Juyong Jiang, Fan Wang, Jing Tang, Sunghun Kim, and Jiayi Huang. 2025. A survey on mixture of experts in large language models. *IEEE Transactions on Knowledge and Data Engineering* (2025).

- [5] Alejandro Carmona-Martínez, Gregorio Bernabé, and José M. García. 2025. Characterization of Machine Learning Compilers for LLM Inference on NVIDIA GPUs. *Research Square* (2025). doi:10.21203/rs.3.rs-7652970/v1

- [6] Le Chen, Dahu Feng, Erhu Feng, Yingrui Wang, Rong Zhao, Yubin Xia, Pinjie Xu, and Haibo Chen. 2025. Characterizing Mobile SoC for Accelerating Heterogeneous LLM Inference. In Proceedings of the ACM SIGOPS 31st Symposium on Operating Systems Principles. 359–374.

- [7] Tri Dao, Daniel Y. Fu, Stefano Ermon, Atri Rudra, and Christopher Ré. 2022. FlashAttention: Fast and Memory-Efficient Exact Attention with IO-Awareness. In *Advances in Neural Information Processing Systems (NeurIPS)*.

- [8] Kuntai Du, Bowen Wang, Chen Zhang, Yiming Cheng, Qing Lan, Hejian Sang, Yihua Cheng, Jiayi Yao, Xiaoxuan Liu, Yifan Qiao, et al. 2025. PrefillOnly: An Inference Engine for Prefill-only Workloads in Large Language Model Applications. In Proceedings of the ACM SIGOPS 31st Symposium on Operating Systems Principles. 399–414.

- [9] Abhimanyu Dubey, Abhinav Jauhri, Abhinav Pandey, Abhishek Kadian, Ahmad Al-Dahle, Aiesha Letman, Akhil Mathur, Alan Schelten, Amy Yang, Angela Fan, et al. 2024. The Llama 3 Herd of Models. arXiv preprint arXiv:2407.21783 (2024).

- [10] Wenqi Fan, Yujuan Ding, Liangbo Ning, Shijie Wang, Hengyun Li, Dawei Yin, Tat-Seng Chua, and Qing Li. 2024. A survey on rag meeting llms: Towards retrieval-augmented large language models. In Proceedings of the 30th ACM SIGKDD Conference on Knowledge Discovery and Data Mining. 6491–6501.

- [11] William Fedus, Barret Zoph, and Noam M. Shazeer. 2021. Switch Transformers: Scaling to Trillion Parameter Models with Simple and Efficient Sparsity. arXiv preprint arXiv:2101.03961 abs/2101.03961 (2021).

- [12] Jared Fernandez, Clara Na, Vashisth Tiwari, Yonatan Bisk, Sasha Luccioni, and Emma Strubell. 2025. Energy considerations of large language model inference and efficiency optimizations. arXiv preprint arXiv:2504.17674 (2025).

- [13] Elias Frantar, Saleh Ashkboos, Torsten Hoefler, and Dan Alistarh. 2023. GPTQ: Accurate Post-Training Quantization for Generative Pre-trained Transformers. In *International Conference on Learning Representations (ICLR)*.

- [14] Yunfan Gao, Yun Xiong, Xinyu Gao, Kangxiang Jia, Jinliu Pan, Yuxi Bi, Yixin Dai, Jiawei Sun, and Haofen Wang. 2023. Retrieval-augmented generation for large language models: A survey. arXiv preprint arXiv:2312.10997 2, 1 (2023).

- [15] Zirui Guo, Lianghao Xia, Yanhua Yu, Tu Ao, and Chao Huang. 2025. LightRAG: Simple and Fast Retrieval-Augmented Generation. In Findings of the Association for Computational Linguistics: EMNLP 2025, Christos Christodoulopoulos, Tanmoy Chakraborty, Carolyn Rose, and Violet Peng (Eds.). Association for Computational Linguistics, Suzhou, China, 10746–10761. doi:10.18653/v1/2025.findings-emnlp.568

- [16] Muhammad Usman Hadi, Rizwan Qureshi, Abbas Shah, Muhammad Irfan, Anas Zafar, Muhammad Bilal Shaikh, Naveed Akhtar, Jia Wu, Seyedali Mirjalili, et al. 2023. Large language models: a comprehensive survey of its applications, challenges, limitations, and future prospects. Authorea preprints 1, 3 (2023), 1–26.

- [17] Ke Hong, Guohao Dai, Jiaming Xu, et al. 2024. FlashDecoding++: Faster Large Language Model Inference with Asynchronization, Flat GEMM Optimization, and Heuristics. In *Proceedings of the 7th MLSys Conference (MLSys)*.

- [18] Coleman Hooper, Sehoon Kim, Hiva Mohammadzadeh, et al. 2024. KVQuant: Towards 10 Million Context Length LLM Inference with KV Cache Quantization. In *Advances in Neural Information Processing Systems (NeurIPS)*.

- [19] Cunchen Hu, HeYang Huang, Liangliang Xu, et al. 2025. ShuffleInfer: Disaggregate LLM Inference for Mixed Downstream Workloads. ACM Transactions on Architecture and Code Optimization (TACO) 22, 1 (2025), 1–24.

- [20] Qi Hu, Zhisheng Ye, Zerui Wang, Guoteng Wang, Mengdie Zhang, Qiaoling Chen, Peng Sun, Dahua Lin, Xiaolin Wang, Yingwei Luo, Yonggang Wen, and Tianwei Zhang. 2024. Characterization of Large Language Model Development in the Datacenter. In Symposium on Networked Systems Design and Implementation.

- [21] Yanping Huang, Youlong Cheng, Ankur Bapna, Orhan Firat, Dehao Chen, Mia Chen, HyoukJoong Lee, Jiquan Ngiam, Quoc V Le, Yonghui Wu, et al. 2019. GPipe: Efficient training of giant neural networks using pipeline parallelism. Advances in Neural Information Processing Systems 32 (2019).

- [22] Yizheng Huang and Jimmy Huang. 2024. A survey on retrieval-augmented text generation for large language models. arXiv preprint arXiv:2404.10981 (2024).

- [23] Huiqiang Jiang, Yucheng Li, Chengruidong Zhang, Qianhui Wu, Xufang Luo, Surin Ahn, Zhenhua Han, Amir H Abdi, Dongsheng Li, Chin-Yew Lin, et al. 2024. Minference 1.0: Accelerating Pre-filling for Long-context LLMs via Dynamic

- Sparse Attention. arXiv preprint arXiv:2407.02490 (2024). https://arxiv.org/abs/2407.02490

- [24] Jean Kaddour, Joshua Harris, Maximilian Mozes, Herbie Bradley, Roberta Raileanu, and Robert McHardy. 2023. Challenges and applications of large language models. arXiv preprint arXiv:2307.10169 (2023).

- [25] Aditya K Kamath, Ramya Prabhu, Jayashree Mohan, Simon Peter, Ramachandran Ramjee, and Ashish Panwar. 2024.

POD-Attention: Unlocking Full Prefill-Decode Overlap for Faster LLM Inference. Proceedings of the 30th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2 (2024).

- [26] Benjamin Kubwimana and Qijing Huang. 2025. EdgeReasoning: Characterizing Reasoning LLM Deployment on Edge GPUs. 2025 IEEE International Symposium on Workload Characterization (IISWC) (2025), 99–115.

- [27] Woosuk Kwon, Zhuohan Li, Siyuan Zhuang, Ying Sheng, Lianmin Zheng, Cody Hao Yu, Joseph Gonzalez, Hao Zhang, and Ion Stoica. 2023. Efficient Memory Management for Large Language Model Serving with PagedAttention. In Proceedings of the 29th Symposium on Operating Systems Principles (SOSP). 611–626.

- [28] Malgorzata Lazuka, Andreea Anghel, and Thomas P. Parnell. 2024. LLM-Pilot: Characterize and Optimize Performance of your LLM Inference Services. SC24: International Conference for High Performance Computing, Networking, Storage and Analysis (2024), 1–18.

- [29] Wonbeom Lee, Jungi Lee, Junghwan Seo, and Jaewoong Sim. 2024. InfiniGen: Efficient generative inference of large language models with dynamic KV cache management. In 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI 24). 155–172.

- [30] Patrick Lewis, Ethan Perez, Aleksandra Piktus, Fabio Petroni, Vladimir Karpukhin, Naman Goyal, Heinrich Küttler, Mike Lewis, Wen-tau Yih, Tim Rocktäschel, et al. 2020. Retrieval-augmented generation for knowledge-intensive NLP tasks. Advances in Neural Information Processing Systems 33 (2020), 9459–9474.

- [31] Baolin Li, Yankai Jiang, Vijay Gadepally, and Devesh Tiwari. 2024. Llm inference serving: Survey of recent advances and opportunities. In 2024 IEEE High Performance Extreme Computing Conference (HPEC). IEEE, 1–8.

- [32] Jinhao Li, Jiaming Xu, Shan Huang, Yonghua Chen, Wen Li, Jun Liu, Yaoxiu Lian, Jiayi Pan, Li Ding, Hao Zhou, et al. 2024. Large language model inference acceleration: A comprehensive hardware perspective. arXiv preprint arXiv:2410.04466 (2024).

- [33] Ji Lin, Jiaming Tang, Haotian Tang, et al. 2024. AWQ: Activation-aware Weight Quantization for On-Device LLM Compression and Acceleration. In *Proceedings of the 7th MLSys Conference (MLSys)*.

- [34] Aixin Liu, Bei Feng, Bing Xue, Bingxuan Wang, Bochao Wu, Chengda Lu, Chenggang Zhao, Chengqi Deng, Chenyu Zhang, Chong Ruan, et al. 2024. DeepSeek-V3 Technical Report. arXiv preprint arXiv:2412.19437 (2024).

- [35] Mona Moghadampanah, Adib Rezaei Shahmirzadi, and Dimitrios S. Nikolopoulos. 2025. Energy-Efficient Multimodal LLM Inference: Stage-Level Characterization and Input-Aware Controls. In Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis (SC '25). ACM, St. Louis, MO, USA, 1–3. Poster.

- [36] Karthik Namboori, Rohit P. Suresh, Sathwik Hj, Shriansh Mohanty, and Jayashree Rangareddy. 2025. Distributed Inference of Large Language Models on Edge Devices. Proceedings of the 2025 14th International Conference on Software and Computer Applications (2025).

- [37] Piotr Nawrot, Robert Li, Renjie Huang, Sebastian Ruder, Kelly Marchisio, and Edoardo M Ponti. 2025. The sparse frontier: Sparse attention trade-offs in transformer LLMs. arXiv preprint arXiv:2504.17768 (2025).

- [38] Sihyeong Park, Sungryeol Jeon, Chaelyn Lee, Seokhun Jeon, Byung-Soo Kim, and Jemin Lee. 2025. A Survey on Inference Engines for Large Language Models: Perspectives on Optimization and Efficiency. arXiv preprint arXiv:2505.01658 (2025).

- [39] Pratyush Patel, Esha Choukse, Chaojie Zhang, et al. 2024. Splitwise: Efficient Generative LLM Inference Using Phase Splitting. In 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA). 118–132.

- [40] Pratyush Patel, Esha Choukse, Chaojie Zhang, Iñigo Goiri, Brijesh Warrier, Nithish Mahalingam, and Ricardo Bianchini. 2024. Characterizing Power Management Opportunities for LLMs in the Cloud. Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3 (2024).

- [41] Ruoyu Qin, Zheming Li, Weiran He, Jialei Cui, Heyi Tang, Feng Ren, Teng Ma, Shangming Cai, Yineng Zhang, Mingxing Zhang, et al. 2024. Mooncake: A kvcache-centric disaggregated architecture for llm serving. ACM Transactions on Storage (2024).

- [42] Zebin Ren, Krijn Doekemeijer, Tiziano De Matteis, Christian Pinto, Radu Stoica, and Animesh Trivedi. 2025. An I/O Characterizing Study of Offloading LLM Models and KV Caches to NVMe SSD. In *Proceedings of the 5th Workshop on Challenges and Opportunities of Efficient and Performant Storage Systems.* 23–33.

- [43] Noam Shazeer, Azalia Mirhoseini, Krzysztof Maziarz, Andy Davis, Quoc Le, Geoffrey Hinton, and Jeff Dean. 2017. Outrageously large neural networks: The sparsely-gated mixture-of-experts layer. arXiv preprint arXiv:1701.06538 (2017).

- [44] Tianyao Shi and Yi Ding. 2025. Systematic Characterization of LLM Quantization: A Performance, Energy, and Quality Perspective. arXiv preprint arXiv:2508.16712 (2025).

- [45] Mohammad Shoeybi, Mostofa Patwary, Raul Puri, Patrick LeGresley, Jared Casper, and Bryan Catanzaro. 2019. Megatron-LM: Training multi-billion parameter language models using model parallelism. arXiv preprint arXiv:1909.08053 (2019).

- [46] Mohammad Siavashi, Faezeh Keshmiri Dindarloo, Dejan Kostić, and Marco Chiesa. 2025. Priority-Aware Preemptive Scheduling for Mixed-Priority Workloads in MoE Inference. Proceedings of the 5th Workshop on Machine Learning and Systems (2025).

- [47] Jovan Stojkovic, Chaojie Zhang, Iñigo Goiri, Josep Torrellas, and Esha Choukse. 2024. DynamoLLM: Designing LLM Inference Clusters for Performance and Energy Efficiency. 2025 IEEE International Symposium on High Performance Computer Architecture (HPCA) (2024), 1348–1362.

- [48] Qwen Team. 2025. Qwen2.5 Technical Report. arXiv:2412.15115 [cs.CL] https://arxiv.org/abs/2412.15115

- [49] Romal Thoppilan, Daniel De Freitas, Jamie Hall, Noam Shazeer, Apoorv Kulshreshtha, Heng-Tze Cheng, Alicia Jin, Taylor Bos, Leslie Baker, Yu Du, et al. 2022. LaMDA: Language Models for Dialog Applications. arXiv preprint arXiv:2201.08239 (2022).

- [50] Chunlin Tian, Xinpeng Qin, Kahou Tam, Li Li, Zijian Wang, Yuanzhe Zhao, Minglei Zhang, and Chengzhong Xu. 2025.

CLONE: Customizing LLMs for Efficient Latency-Aware Inference at the Edge. In USENIX Annual Technical Conference.

- [51] Prabhu Vellaisamy, Thomas Labonte, Sourav Chakraborty, Matt Turner, Samantika Sury, and John Paul Shen. 2025. Characterizing and Optimizing LLM Inference Workloads on CPU-GPU Coupled Architectures. 2025 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS) (2025), 49–61.

- [52] Jiahao Wang, Jinbo Han, Xingda Wei, Sijie Shen, Dingyan Zhang, Chenguang Fang, Rong Chen, Wenyuan Yu, and Haibo Chen. 2025. KVCache Cache in the Wild: Characterizing and Optimizing KVCache Cache at a Large Cloud Provider. arXiv preprint arXiv:2506.02634 (2025).

- [53] Lang Xu, Kaushik Kandadi Suresh, Quentin Anthony, Nawras Alnaasan, and Dhabaleswar K Panda. 2025. Characterizing Communication Patterns in Distributed Large Language Model Inference. arXiv preprint arXiv:2507.14392 (2025).

- [54] An Yang, Anfeng Li, Baosong Yang, Beichen Zhang, Binyuan Hui, Bo Zheng, Bowen Yu, Chang Gao, Chengen Huang, Chenxu Lv, et al. 2025. Qwen3 Technical Report. arXiv:2505.09388 [cs.CL] https://arxiv.org/abs/2505.09388

- [55] Rongjie Yi, Liwei Guo, Shiyun Wei, Ao Zhou, Shangguang Wang, and Mengwei Xu. 2023. EdgeMoE: Fast on-device inference of MoE-based large language models. arXiv preprint arXiv:2308.14352 (2023).

- [56] Zhihang Yuan, Yuzhang Shang, Yang Zhou, Zhen Dong, Zhe Zhou, Chenhao Xue, Bingzhe Wu, Zhikai Li, Qingyi Gu, Yong Jae Lee, et al. 2024. Llm inference unveiled: Survey and roofline model insights. arXiv preprint arXiv:2402.16363 (2024).

- [57] Hengrui Zhang, August Ning, Rohan Baskar Prabhakar, and David Wentzlaff. 2024. Llmcompass: Enabling efficient hardware design for large language model inference. In 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA). IEEE, 1080–1096.

- [58] Wayne Xin Zhao, Kun Zhou, Junyi Li, Tianyi Tang, Xiaolei Wang, Yupeng Hou, Yingqian Min, Beichen Zhang, Junjie Zhang, Zican Dong, et al. 2023. A survey of large language models. arXiv preprint arXiv:2303.18223 1, 2 (2023).

- [59] Ranran Zhen, Juntao Li, Yixin Ji, Zhenlin Yang, Tong Liu, Qingrong Xia, Xinyu Duan, Zhefeng Wang, Baoxing Huai, and Min Zhang. 2025. Taming the Titans: A Survey of Efficient LLM Inference Serving. arXiv preprint arXiv:2504.19720 (2025).

- [60] Yue Zheng, Yuhao Chen, Bin Qian, Xiufang Shi, Yuanchao Shu, and Jiming Chen. 2025. A review on edge large language models: Design, execution, and applications. Comput. Surveys 57, 8 (2025), 1–35.

- [61] Zangwei Zheng, Xiaozhe Ren, Fuzhao Xue, Yang Luo, Xin Jiang, and Yang You. 2023. Response length perception and sequence scheduling: An LLM-empowered LLM inference pipeline. Advances in Neural Information Processing Systems 36 (2023), 65517–65530.