# IVE: An Accelerator for Single-Server Private Information Retrieval Using Versatile Processing Elements

Sangpyo Kim<sup>†</sup>, Hyesung Ji<sup>‡</sup>, Jongmin Kim<sup>‡</sup>, Wonseok Choi<sup>‡</sup>, Jaiyoung Park<sup>‡</sup>, and Jung Ho Ahn<sup>‡</sup>

†CryptoLab Inc., <sup>‡</sup>Seoul National University

spkim@cryptolab.co.kr, {kevin5188, jongmin.kim, wonseok.choi, jeff1273, gajh}@snu.ac.kr

Abstract-Private information retrieval (PIR) is an essential cryptographic protocol for privacy-preserving applications, enabling a client to retrieve a record from a server's database without revealing which record was requested. Single-server PIR based on homomorphic encryption has particularly gained immense attention for its ease of deployment and reduced trust assumptions. However, single-server PIR remains impractical due to its high computational and memory bandwidth demands. Specifically, reading the entirety of large databases from storage, such as SSDs, severely limits its performance. To address this, we propose IVE, an accelerator for single-server PIR with a systematic extension that enables practical retrieval from large databases using DRAM. Recent advances in DRAM capacity allow PIR for large databases to be served entirely from DRAM, removing its dependence on storage bandwidth. Although the memory bandwidth bottleneck still remains, multi-client batching effectively amortizes database access costs across concurrent requests to improve throughput. However, client-specific data remains a bottleneck, whose bandwidth requirements ultimately limits performance. IVE overcomes this by employing a large on-chip scratchpad with an operation scheduling algorithm that maximizes data reuse, further boosting throughput. Additionally, we introduce sysNTTU, a versatile functional unit that enhances area efficiency without sacrificing performance. We also propose a heterogeneous memory system architecture, which enables a linear scaling of database sizes without a throughput degradation. Consequently, IVE achieves up to 1,275× higher throughput compared to prior PIR hardware solutions.

## I. INTRODUCTION

Private information retrieval (PIR) allows users to query a remote database (DB) without revealing their query, offering a cryptographic basis for privacy-preserving access to public data. Amid the rapid expansion of cloud computing and growing emphasis on data governance, PIR is emerging as a critical building block for privacy-preserving applications, such as web search, location-based services, contact tracing, and AI inference [2], [5], [43], [45], [47], [63], [64], [69], [75], [98].

Among various PIR protocols, those based on homomorphic encryption (HE) stand out due to their general applicability and low communication costs [2]–[4], [15], [49], [71], [76]. HE [12], [24], [26] is an encryption scheme that enables direct computation on encrypted data, allowing a server to process PIR queries without decryption. Unlike other PIR protocols [27], [29], [33], [41] requiring additional assumptions, complex infrastructures with multiple servers, or both, HE-based PIR relies on strong cryptographic guarantees to ensure privacy with only a single server. Its strong security has led

to its gradual adoption in practical applications [6], [48], [68], as exemplified by Apple's use in private visual search.

This simplicity, however, comes at the cost of heavy server-side computation. The high computational complexity of HE operations incurs long retrieval latencies, limiting its practical use. For example, state-of-the-art PIR protocols [32], [49], [65], [67], [71], [72] take 1.1–18.6 seconds for retrieving a 1B–32KB record from an 8GB DB on a CPU-based system [67].

Numerous acceleration studies have been conducted for HE, leveraging CPUs/GPUs [9], [39], [53], [55]–[57], [61] or custom FPGAs/ASICs [1], [58], [59], [62], [88], [89]. They focus on number-theoretic transforms (NTTs), with an emphasis on bootstrapping [23], [25], [46], which dominate the runtime in typical HE workloads.

However, PIR's memory-intensive nature hinders its acceleration: as concealing the target record requires scanning the entire DB, for large DBs exceeding DRAM capacity, the low bandwidth of secondary storage devices (e.g., SSDs) significantly degrades performance. This limitation motivated INSPIRE [66] to adopt in-storage ASICs to accelerate HE-based PIR. Unfortunately, even with such efforts, PIR remains impractical, requiring 36 seconds to retrieve a 288B entry from a 288GB DB for anonymous communication [2].

To overcome this limitation, we propose IVE, an accelerator for single-server HE-based PIR with a systematic extension to support large DBs efficiently. Technology scaling now allows modern hardware systems to support terabyte-scale DRAM configurations, which open up new opportunities to accelerate the retrieval process by providing DB data with notably higher DRAM bandwidth. Our in-depth analysis shows that, although the memory bandwidth bottleneck for scanning DB persists even with DRAM, batching multi-client queries can amortize the overheads, improving PIR throughput.

However, batching cannot resolve the bandwidth demands caused by client-specific data, limiting further improvements. IVE addresses this challenge by using a large on-chip scratch-pad, combined with algorithmic optimizations that maximize on-chip data reuse during PIR. Moreover, leveraging the sequential computational patterns inherent in PIR, we develop a versatile functional unit, *sysNTTU*, that consolidates multiple core PIR operations into a unified hardware block, boosting area efficiency without degrading PIR performance.

Further, we propose a scale-up systematic extension that leverages two heterogeneous memory types: higher-bandwidth HBM for data being processed and larger but lower-bandwidth LPDDR for offloading the full DB. We observe that, batching

effectively amortizes DB access costs to render potential PIR throughput degradations caused by low LPDDR bandwidth to be minimal. For further DB size scaling, we also introduce a scale-out system that connects multiple scale-up IVE systems. Our optimized parallelization strategy efficiently partitions DB across these systems, enabling near-linear scaling of PIR throughput. As a result, IVE delivers up to 1,275× higher throughput over the state-of-the-art hardware solution for HE-based PIR [66] in practical applications [2], [4], [70].

In this paper, we make the following key contributions:

- We identify that batching multiple clients' requests exposes new opportunities for PIR acceleration on recent hardware by mitigating the bandwidth bottleneck caused by full-DB scan. However, batching cannot solely address all the bandwidth demands due to client-specific data.

- We propose IVE, a PIR accelerator with a large scratchpad and algorithmic techniques that maximize the on-chip reuse of client-specific data. IVE effectively mitigates the memory bandwidth bottleneck to significantly enhance throughput. IVE includes a versatile functional unit, sysNTTU, that improves area efficiency without performance degradation.

- We offer a scalable, systematic solution that leverages a heterogeneous memory system, enabling IVE to support PIR over large DBs in practice.

# II. BACKGROUND

The practicality of various PIR schemes [2], [15], [49], [71], [76] is hindered by high computational and communication costs. To reduce the costs, numerous studies employed additional assumptions. Multi-server PIRs [27], [29], [33], [41] assume that multiple non-colluding servers cooperate to process a client's query. However, their underlying assumption is fragile as servers may collude through side channels and covert communication mechanisms [18], [36]. Also, establishing and maintaining a non-colluding-server environment is operationally complex. These challenges make multi-server PIR less viable in practice [2], [15], [31], [49], [76].

Thus, we focus on simple (yet viable and useful) single-server PIR schemes. Table I summarizes the major symbols. All vectors are column vectors. We use  $1TB = 2^{10}GB = 2^{20}MB = 2^{30}KB = 2^{40}B$ .

# A. Naïve one-dimensional PIR

For an unencrypted database (DB) with D records residing at a server, PIR allows a client to retrieve a record  $\mathrm{DB}[i^*]$  without revealing the index  $i^*$ . A client encrypts the index  $i^*$  and sends it to the server. The server must compute  $\mathrm{DB}[i^*]$  with the unencrypted DB and the encrypted  $i^*$  (ciphertexts,  $\mathbf{cts}$ ).

Homomorphic encryption (HE), a cryptographic primitive allowing oblivious computations on ciphertexts encrypted with small errors, is a perfect fit. Numerous studies [15], [49], [67], [71], [76] have proposed efficient single-server PIR schemes using HE, where they mostly share common structures.

We first describe the structure of a naïve PIR. HE has a linear property; we can add two  $\mathbf{ct}$ s ( $\text{Enc}(\mathcal{X})$  and  $\text{Enc}(\mathcal{Y})$ ) or multiply unencrypted data ( $\mathcal{Z}$ ), denoted as *plaintext*, to a  $\mathbf{ct}$ .

$\label{table I} \textbf{TABLE I} \\ \textbf{Symbols and their values we use for evaluation}.$

| Sym.   Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Value                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{ c c c c }\hline D & \text{Number (\#) of records in the database DB.}\\ \hline D_0 & \text{Initial dimension size.}\\ \hline d & \# \text{ of subsequent dimensions. } D = D_0 \cdot 2^d.\\ \hline N & \text{Degree of } \mathcal{R}_Q = \mathbb{Z}_Q[X]/(X^N+1).\\ \hline Q & \text{Ciphertext modulus of } \mathcal{R}_Q.\\ \hline P & \text{Plaintext modulus of } \mathcal{R}_P.\\ \hline z \ \& \ \ell & \text{Decomposition base and length. } z^\ell \geq Q.\\ \hline \end{array}$ | $ \begin{array}{c c} 2^{16}-2^{24} \\ 2^{8} \\ 8-16 \\ 2^{12} \\ < 2^{112} \\ 2^{32} \\ 2^{14}-2^{22} & 5-8 \end{array} $ |

- $\operatorname{Enc}(\mathcal{X}) + \operatorname{Enc}(\mathcal{Y}) \to \operatorname{Enc}(\mathcal{X} + \mathcal{Y})$

- $\mathcal{Z} \cdot \operatorname{Enc}(\mathcal{Y}) \to \operatorname{Enc}(\mathcal{Z} \cdot \mathcal{Y})$

The client uses a one-hot representation to send D ciphertexts  $\mathbf{ct}[0], \cdots, \mathbf{ct}[D-1]$  encrypting 0 (if  $i \neq i^*$  for  $\mathbf{ct}[i]$ ) or 1 (if  $i = i^*$ ). Then, the server uses the linearity of HE to compute

$$\sum_{i=0}^{D-1} DB[i] \cdot \mathbf{ct}[i] \to Enc(DB[i^*])$$

(1)

and returns the ciphertext encrypting  $DB[i^*]$  to the client.

HE-based PIR schemes start from this naïve implementation accessing the entire DB; in fact, even for advanced schemes, accessing the entire DB is a critical requirement for PIR [27]. PIR based on Regev encryption: Eq. 1 can be implemented with Regev encryption [85]. A representative PIR scheme, SimplePIR [49], is based on this method. Each ct<sub>Regev</sub> encrypts a single integer in  $\mathbb{Z}_P$  for a plaintext modulus P (i.e., an integer in a range of [0, P-1]), obtaining a length-n (e.g.,  $n=2^{10}$  in SimplePIR) vector of integers in  $\mathbb{Z}_Q$  for a ciphertext modulus Q ( $Q \gg P$ ) as the encryption result. Here, Q represents the budget for error amplification. Each HE operation amplifies the errors in a ciphertext, eventually making them undecryptable. Increasing Q allows more computations on a ciphertext without requiring extra error mitigation procedures. Each DB[i] is an unencrypted scalar in  $\mathbb{Z}_P$ . After the client sends D  $\mathbf{ct}_{regev}$   $(nD \log Q)$  bits of data) for the onehot representation of  $i^*$ , the server computes Eq. 1 by scalarvector multiplications (mults) and vector-vector additions.

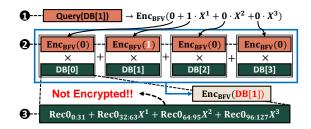

**PIR based on BFV encryption:** To mitigate this massive data communication cost, numerous studies [15], [67], [71], [76] use BFV encryption [11], [38] to represent  $i^*$ . BFV can encrypt a degree-(N-1) polynomial with its coefficients in a range of [0, P-1] ( $\mathcal{R}_P = \mathbb{Z}_P[X]/(X^N+1)$ ). Instead of sending D cts, the client prepares a single query ct containing all bits for the one-hot index representation (see Fig. 1-①) by encrypting  $X^{i^*} = 0 + 0 \cdot X + \cdots + 1 \cdot X^{i^*} + \cdots + 0 \cdot X^{N-1}$  (suppose D = N for simplicity). This process of combining multiple values in the range [0, P-1] into a polynomial is referred to as packing. The resulting BFV ciphertext,  $\operatorname{ct}_{BFV}$ , is a pair of polynomials in  $\mathcal{R}_Q$  (e.g.,  $(a,b) \in \mathcal{R}_Q^2$ ) with a ciphertext modulus Q (again,  $Q \gg P$ ). Thus, BFV substantially reduces the PIR communication cost  $(2D \log Q)$  bits of data) compared to that of Regev  $(nD \log Q)$  bits).

ExpandQuery, Subs, and evks: From a query encrypting  $X^{i^*}$ , the server can generate D ciphertexts corresponding to the one-hot representation of  $i^*$  (see Fig. 1-2) by per-

Fig. 1. Naïve PIR based on BFV encryption [11], [38] when D = N = 4.

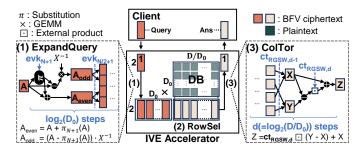

Fig. 2. Server-side PIR computation process composed of (1) ExpandQuery, (2) RowSel, and (3) ColTor.

forming a sequence of substitution (Subs) operations [4]. Subs( $\mathbf{ct_{BFV}}, r$ ) replaces X with  $X^r$  (e.g.,  $\mathrm{Enc_{BFV}}(X+X^2) \to \mathrm{Enc_{BFV}}(X^r+X^{2r})$ ) for the polynomial  $\mathbf{ct_{BFV}}$  encrypts. From Query =  $\mathrm{Enc_{BFV}}(c_0+c_1X+\cdots+c_{N-1}X^{N-1})$ , we can extract two BFV ciphertexts, each encrypting the odd/even terms. We use Subs(Query, N+1) to negate the odd terms  $(X^{2k+1})$  as  $(X^{N+1})^{2k+1} = -X^{2k+1}$  (:  $X^N = -1$  in  $\mathcal{R}_Q$ ):

$$\begin{split} & \operatorname{Subs}(\operatorname{Query},N+1) \to \operatorname{Enc}_{\operatorname{BFV}}(c_0-c_1X+c_2X^2-\cdots-c_{N-1}X^{N-1}) \\ & \operatorname{Query} + \operatorname{Subs}(\operatorname{Query},N+1) \to \operatorname{Enc}_{\operatorname{BFV}}(c_0+c_2X^2+\cdots) \\ & X^{-1} \cdot (\operatorname{Query} - \operatorname{Subs}(\operatorname{Query},N+1)) \to \operatorname{Enc}_{\operatorname{BFV}}(c_1+c_3X^2+\cdots) \end{split}$$

We elaborate on the computation of Subs in §II-D.

The server iteratively uses the previous extraction results and performs Subs with  $r=N/2+1,N/4+1,\cdots$  to obtain four, eight,  $\cdots$  BFV ciphertexts containing  $1/4,1/8,\cdots$  of the total terms in Query. We refer to the whole process as ExpandQuery, which forms a binary-tree computational flow as shown in Fig. 2. For each r value in Subs, a unique public key evk<sub>r</sub> needs to be prepared by the client. Thus, ExpandQuery needs a distinct evk<sub>r</sub> per tree depth, requiring up to  $\log N$  evks in total. Eventually, the server obtains  $\mathbf{ct}[i] = \mathrm{Enc}_{\mathrm{BFV}}(c_i)$   $(i=0,\cdots,D-1)$ , used to compute Eq. 1.

# B. Computational optimizations for Eq. 1

**Residue number system (RNS):** RNS simplifies handling Q by decomposing it as  $Q=q_0q_1q_2q_3$ . Chinese remainder theorem (CRT, Eq. 2) is applied to replace each coefficient c with four 28-bit residues  $([c]_{q_i})$  for moduli  $q_i \in (2^{27}, 2^{28})$ . Inverse CRT (iCRT, Eq. 3) reconstructs c from these residues.

$$\text{CRT: } ([c]_{q_0},\cdots,[c]_{q_3}) \leftarrow (c \bmod q_0,\cdots,c \bmod q_3) \qquad (2)$$

iCRT:

$$c \leftarrow \sum_{i=0}^{3} ([c]_{q_i} \cdot (\frac{Q}{q_i})^{-1} \mod q_i) \cdot (\frac{Q}{q_i}) \mod Q$$

(3)

With RNS, a polynomial in  $\mathcal{R}_Q$  becomes a length-4N 28-bit vector (56KB when  $N=2^{12}$  as in Table I), also viewed as the concatenation of coefficients from four length-N polynomials in  $\mathcal{R}_{q_i}$ 's. A polynomial addition/mult over  $\mathcal{R}_Q$  is equivalent to four independent additions/mults over  $\mathcal{R}_{q_i}$ 's. With RNS, a  $\mathbf{ct}_{\mathrm{BFV}}$  becomes a  $2\times 4N$  structure (112KB).

Number-theoretic transform (NTT): NTT, a Fourier-transform variant, reduces the  $\mathcal{O}(N^2)$  computational cost of a polynomial mult in  $\mathcal{R}_Q$ , which is equivalent to a negacyclic convolution of the corresponding coefficient vectors. With RNS, NTT is applied separately to each  $\mathcal{R}_{q_i}$ , making it four independent N-point fast Fourier transforms (FFTs) with  $\mathcal{O}(N\log N)$  complexity. NTT reduces a polynomial mult under RNS to an element-wise mult between two length-4N vectors. The 4N modular mults can be performed independently, known as coefficient-level parallelism (CLP). Polynomials are typically kept in their NTT form to support repeated mults without converting back by inverse NTT (iNTT).

**Preprocessing** DB: BFV-based PIRs typically represent each DB[i] using a large plaintext domain ( $\mathcal{R}_P$ ). For a record  $\mathbf{Rec0}$  with  $N\log P=32N$  bits of information (assuming  $P=2^{32}$  from Table I), we can simply reinterpret  $\mathbf{Rec0}$  as N chunks of 32-bit data and set DB[0] =  $\mathbf{Rec0}_{0:31} + \mathbf{Rec0}_{32:63}X + \cdots + \mathbf{Rec0}_{32(N-1):32N-1}X^{N-1}$  (see Fig. 1-③) for  $\mathbf{Rec0}_{i:j}$  representing the data from the i-th bit to the j-th bit of  $\mathbf{Rec0}$ . For smaller record sizes, we can construct DB[i] by packing multiple records into a single polynomial.

Then, calculating Eq. 1 requires D polynomial mults involving  $\mathrm{DB}[i]$  for  $D = \frac{\mathrm{DB}_{\mathrm{size}}}{NlogP}$ . To facilitate this, we preprocess  $\mathrm{DB}[i]$  to apply CRT and NTT in advance, after which  $\mathrm{DB}[i]$  is in  $\mathcal{R}_Q$  instead of  $\mathcal{R}_P$ . This requires  $\log Q/\log P \times (<3.5 \times$  based on Table I) more storage for the DB. Nevertheless, the preprocessing approach significantly speeds up PIR computation by more than  $3.9 \times$  based on our CPU evaluation.

## C. Multi-dimensional PIR

The naïve implementation in §II-A scales poorly with the DB size (D) due to the  $\mathcal{O}(D)$  communication cost. Interpreting the DB as a (d+1)-dimensional structure  $(D_0 \times D_1 \times \cdots \times D_d)$  alleviates this problem. Here, we use a three-dimensional example based on OnionPIR [76], Spiral [71], and Respire [15]. Suppose the client wants to retrieve DB $[i^*][j^*][k^*]$ .

**Row selection** (RowSel): ExpandQuery can produce  $\operatorname{ct_{BFV}}[0]$ ,  $\operatorname{ct_{BFV}}[1]$ ,  $\cdots$ ,  $\operatorname{ct_{BFV}}[D_0-1]$  corresponding to the one-hot representation of the initial dimension index  $i^*$ . Then, we apply an Eq. 1-like method, denoted RowSel, to compute

$$\mathbf{ct}_{\mathrm{BFV},\mathrm{DB}}^{(0)}[j][k] \leftarrow \textstyle\sum_{i=0}^{D_0-1} \mathrm{DB}[i][j][k] \cdot \mathbf{ct}_{\mathrm{BFV}}[i] \quad \forall j,k.$$

We obtain "a row of DB" ciphertexts  $\mathbf{ct}_{\mathrm{BFV,DB}}^{(0)}$  with  $D_1 \cdot D_2$  entries each encrypting  $\mathrm{DB}[i^*][j][k]$ .

**RGSW encryption & external product:** For  $j^*$  and  $k^*$ , one might consider repeating the same process as RowSel. However, with  $\mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(0)}$  given instead of unencrypted DB, we need inter-ciphertext mults. Early PIR work [3] directly performed inter- $\mathbf{ct}_{\mathsf{BFV}}$  mults, introducing *multiplicative increases in errors*. It requires relatively larger parameters (N and Q) to

separate the error from data in a ciphertext. This makes PIR computation and communication significantly more costly.

For a more lightweight PIR construction, OnionPIR [76] uses RGSW ciphertexts [40] ( $ct_{RGSW}$ s) to perform  $ct_{RGSW}$ - $ct_{BFV}$  mults, referred to as external products ( $\boxdot$ ). An external product produces a  $ct_{BFV}$  as an output ( $ct_{RGSW} \boxdot ct_{BFV} \rightarrow ct_{BFV}$ ) with just additive increases in error, enabling the use of relatively small N and Q values to reduce the PIR cost. Like  $ct_{BFV}$ , a  $ct_{RGSW}$  encrypts a polynomial in  $\mathcal{R}_P$ . However, a  $ct_{RGSW}$ , which is composed of  $4\ell$  polynomials ( $2 \times 2\ell \times 4N$ ) data structure, 1120KB for  $\ell = 5$ ), is  $2\ell \times 1$  larger than a  $ct_{BFV}$ .

We can derive  $D_1$   $ct_{RGSW}$ s required for the one-hot representation of  $j^*$  from a single  $ct_{BFV}$  by following the same process as ExpandQuery but with minor additional computations [34]. Moreover, it is possible to pack all data required for  $i^*, j^*, k^*$  into a single polynomial in  $\mathcal{R}_P$ , encrypt it into one  $ct_{BFV}$ , and perform ExpandQuery to extract the necessary  $ct_{BFV}$ s/ $ct_{RGSW}$ s for all dimensions at once.

Practical implementation & column tournament (ColTor): With  $D_1$  ct<sub>RGSWs</sub> corresponding to the one-hot representation of  $j^*$ , we can use a RowSel-like accumulation method, albeit using external products instead. Reducing the  $D_1 \cdot D_2$  entries in ct<sup>(0)</sup><sub>BFV,DB</sub> to  $D_2$  would require  $D_1 \cdot D_2$  external products for  $j^*$ . However, the external product is much more computationally expensive than the polynomial-ct<sub>BFV</sub> mults in RowSel (described in §II-D). Thus, it is beneficial to reduce the size of the subsequent dimensions. In practice,  $D_1 = D_2 = 2$  and a high  $D_0$  value would be used [71] for our three-dimensional example. Further, when  $D_1 = 2$ , we need only one RGSW ciphertext ct<sub>RGSW,j\*</sub> directly encrypting  $j^*$  (0 or 1) [15]. To select DB entries for  $j^*$ , we compute the following:

$$\begin{aligned} \mathbf{ct}_{\mathsf{BFV},\mathsf{diff}}[k] &\leftarrow \mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(0)}[1][k] - \mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(0)}[0][k], \\ \mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(1)}[k] &\leftarrow \mathbf{ct}_{\mathsf{RGSW},j^*} \boxdot \mathbf{ct}_{\mathsf{BFV},\mathsf{diff}}[k] + \mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(1)}[0][k] & \forall k \end{aligned}$$

Likewise, we finally compute the following for  $k^*$ :

$$\mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(2)} \!\leftarrow\! \mathbf{ct}_{\mathsf{RGSW},k^*}\!\!\!=\!\!\! (\mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(1)}[1] \!-\! \mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(1)}[0]) \!+\! \mathbf{ct}_{\mathsf{BFV},\mathsf{DB}}^{(1)}[0].$$

This process after RowSel is called ColTor. As shown in Fig. 2, ColTor halves the number of selected DB ciphertexts for every dimension. The final result  $\mathbf{ct}_{\mathrm{BFV,DB}}^{(2)}$  encrypts  $\mathrm{DB}[i^*][j^*][k^*]$ . ColTor also follows a binary-tree computational flow, with each tree depth corresponding to a dimension. **Error analysis:** As an external product introduces additive error increases, the error [76] included in the PIR response ciphertext  $(\mathbf{ct}_{\mathrm{resp.}} = \mathbf{ct}_{\mathrm{BFV,DB}}^{(2)})$  in the above example) is bounded as  $\mathrm{Err}(\mathbf{ct}_{\mathrm{resp.}}) \leq \mathrm{Err}(\mathbf{ct}_{\mathrm{BFV,DB}}^{(0)}) + \mathcal{O}(d) \cdot \mathrm{Err}(\mathbf{ct}_{\mathrm{RGSW}})$ . Typically,  $\mathrm{Err}(\mathbf{ct}_{\mathrm{RGSW}})$  is much smaller than  $\mathrm{Err}(\mathbf{ct}_{\mathrm{BFV,DB}}^{(0)})$ , which is largely determined by  $D_0$  and P. As d grows logarithmically with the DB size, the error remains stable under fixed  $D_0$  and P values, allowing PIR for practically large DBs without extra error control measures such as bootstrapping.

# D. HE operations

**Linear BFV operations:** Linear BFV operations are performed in a polynomial-wise manner: i.e., for  $\mathbf{ct}_{BFV} = (a, b) \in$

Fig. 3. Computational flow of an external product (.).

$$\begin{array}{l} \mathcal{R}_Q^2,\,\mathbf{ct}_{\mathrm{BFV}}'=(a',b')\in\mathcal{R}_Q^2,\,\mathrm{and}\,\,p\in\mathcal{R}_Q,\,p\cdot\mathbf{ct}_{\mathrm{BFV}}+\mathbf{ct}_{\mathrm{BFV}}'=\\ (p\cdot a+a',p\cdot b+b'). \end{array}$$

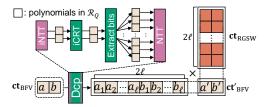

**External product**( $\boxdot$ ): For  $\operatorname{ct}_{RGSW} \boxdot \operatorname{ct}_{BFV}$ , we first perform base decomposition (Dcp) to extend a and b of  $\operatorname{ct}_{BFV}$  with a base z (e.g.,  $2^{22}$ ). Dcp(a) produces polynomials  $a_{k \in [0,\ell)}$  (see Fig. 3), where each coefficient represents the k-th digit in base z of the corresponding coefficient in a, falling within the range [0,z-1]. For Dcp(a), we reconstruct each coefficient of a with RNS by performing iNTT followed by iCRT (Eq. 3) and extract bits for  $a_0, a_1, \cdots, a_{\ell-1}$ . Similarly, we obtain  $b_0, b_1, \cdots, b_{\ell-1}$ . We reinterpret  $a_k$  and  $b_k$  as polynomials in  $\mathcal{R}_Q$  under RNS with four moduli  $q_{i \in [0,3]}$  and perform four NTT operations on each to facilite polynomial mults, resulting in a total of  $4 \times 2\ell$  NTTs. The decomposed polynomials of  $\operatorname{ct}_{BFV}$  can then be multiplied with  $\operatorname{ct}_{RGSW}$  as follows:

$$\mathbf{ct}_{RGSW} \boxdot \mathbf{ct}_{BFV} = \mathbf{ct}_{RGSW} \cdot (\mathrm{Dcp}(a), \mathrm{Dcp}(b)) = \mathbf{ct}'_{BFV},$$

$$\mathbf{Dcp}(x) = (x_0, x_1, \cdots, x_{\ell-1}) \in \mathcal{R}_O^{\ell}, \quad x = \sum_{i=0}^{\ell-1} x_i \cdot z^i.$$

We regard a  $\mathbf{ct}_{RGSW}$  as a  $2 \times 2\ell$  matrix of polynomials and perform matrix-vector mult with the length- $2\ell$  vector of polynomials  $(a_0, \cdots, a_{\ell-1}, b_0, \cdots, b_{\ell-1})$ , resulting in a length-2 vector of polynomials, which is the output  $\mathbf{ct}'_{BFV}$ . Subs & automorphism: Subs also has a similar computation process. The main computational cost of Subs for  $\mathbf{ct}_{BFV} = (a,b)$  comes from computing  $\mathrm{Dcp}(a_{\mathrm{Aut},r})$  (length- $\ell$  vector of polynomials) and multiplying it with  $\mathbf{evk}_r$  ( $2 \times \ell$  matrix of polynomials, 560KB for  $\ell=5$ ).  $a_{\mathrm{Aut},r}$  and  $b_{\mathrm{Aut},r}$  are the polynomials obtained by automorphism on a and b, which shuffles the order of coefficients according to r.

$$Subs(\mathbf{ct}_{BFV}, r) = \mathbf{evk}_r \cdot Dcp(a_{Aut,r}) + (0, b_{Aut,r})$$

## III. PIR ACCELERATION: OPPORTUNITIES&CHALLENGES

Even with the high computational complexity of HE, accessing the full DB renders PIR ill-suited for hardware acceleration. For large SSD-resident DBs, storage latency dominates, motivating INSPIRE [66] to use in-storage ASICs with modest arithmetic throughput for PIR.

However, technology scaling brings new opportunities for PIR acceleration through increases in DRAM capacity. Recent hardware systems now support TB-scale DRAM configurations [79], [96], enough to handle practical large DB sizes. This eliminates the need for low-bandwidth storage access during PIR, addressing the key bottleneck identified in INSPIRE. Motivated by this, we explore an advanced hardware solution fully utilizing the high arithmetic throughput of modern

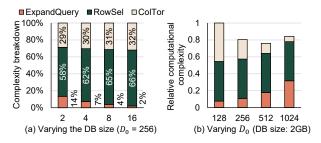

Fig. 4. Computational complexity breakdown based on the number of integer mults required for PIR depending on (a) the DB size and (b)  $D_0$ .

hardware for HE-based PIR. We used an optimized variant of OnionPIR (see Fig. 2) as our main scheme. OnionPIR shares structural similarities with numerous PIR schemes [4], [15], [67], [71] and incorporates most of the core operations from other HE-based PIR approaches [21], [49], [67], [68], making our acceleration strategy easily extendable to them (§VI-D).

# A. Computational characteristics of PIR

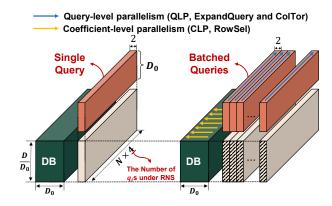

While ExpandQuery and ColTor both have a binary-tree computational flow with similar operations (Subs and external product), RowSel only requires mults between DB plaintexts and  $\mathbf{ct}_{\mathrm{BFV}}$ . RowSel can be expressed as a matrix-matrix mult (GEMM) between a  $\frac{D}{D_0} \times D_0$  matrix (DB) and a  $D_0 \times 2$  matrix ( $D_0$   $\mathbf{ct}_{\mathrm{BFV}}$ s), where each element is a polynomial in  $\mathcal{R}_Q$ . With RNS and NTT, a polynomial mult becomes an elementwise mult between two length-4N vectors. This allows us to reinterpret RowSel as 4N independent GEMMs with modular integer arithmetic between a  $\frac{D}{D_0} \times D_0$  matrix slice of the DB and a  $D_0 \times 2$  slice of the query matrix (see Fig. 5, left), where each element of a slice is a 28-bit integer.

Despite this simple structure, RowSel is the most computationally demanding step. A computational cost estimation based on the number of integer mults reveals that RowSel accounts for 58-66% of the total complexity for 2-16GB DB (see Fig. 4a). Also, RowSel dominates the total complexity for preferable  $D_0$  values of 256-512, which minimize the total cost (see Fig. 4b).

The large DB size and poor DB reusability become fundamental limiting factors as we attempt hardware acceleration for PIR. As each DB element is barely reused, limited DRAM bandwidth bottlenecks performance, hindering full use of abundant computing resources in modern hardware.

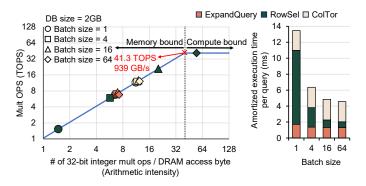

# B. Multi-client query batching

We observe that batching PIR queries, possibly from multiple clients, presents a key opportunity for acceleration through hardware-friendly execution. In general HE applications, batching is limited by client-specific cryptographic contexts that prevent data sharing. By contrast, PIR is naturally amenable to batching as it operates over a shared, *unencrypted* DB. Without batching, RowSel is severely bottlenecked by memory bandwidth as it merely involves 1–2 integer mults per byte of DRAM access (Fig.6, left). Batching mitigates

Fig. 5. Computation of RowSe1 without (left) and with (right) batching expressed as matrix-matrix mults.

Fig. 6. Theoretical roofline plot and execution time breakdown for each PIR step on RTX 4090 for various multi-client batch sizes (1–64) for a 2GB DB.

this bottleneck by amortizing the DB access cost across multiple queries, substantially increasing arithmetic intensity and enabling higher throughput. Consequently, RowSel throughput improves with larger batch sizes; thus, its share of the total PIR execution time decreases with larger batch sizes, as observed on an RTX 4090 GPU (Fig. 6, right). Batching is applicable to most PIR schemes, not only HE-based ones, as they all require a full DB scan that can be amortized through batching.

However, batching cannot alleviate the memory bandwidth bottleneck in the other steps. Since ExpandQuery and ColTor operate on client-specific data (e.g., evk), the amortization cannot be applied, keeping the arithmetic intensity unchanged (see Fig. 6, left). As a result, these steps remain bounded by memory bandwidth due to their inherently low arithmetic intensity values. Their execution time increases nearly linearly with the batch size, eventually accounting for non-negligible portions of the total PIR execution time (see Fig. 6, right).

# IV. ARCHITECTING AN ACCELERATOR FOR PIR

The memory bandwidth bottlenecks in ExpandQuery and ColTor limit the achievable PIR throughput of an accelerator as memory bandwidth scales more slowly than technology nodes. Therefore, before detailing the architectural design of a PIR accelerator, we introduce several techniques designed to mitigate these bottlenecks within the accelerator.

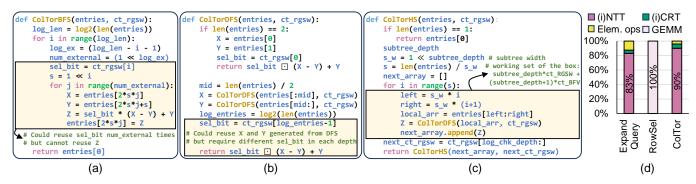

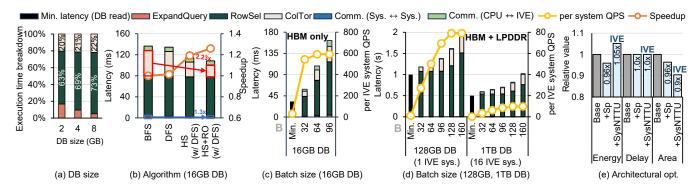

Fig. 7. Operation scheduling of ExpandQuery, represented by a binary tree structure, when using (a) breadth-first search (BFS), (b) depth-first search (DFS), and (c) hierarchical search, which can be used for both ExpandQuery and ColTor. (d) Computational complexity breakdown of three primary steps in PIR.

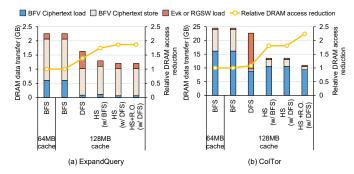

## A. Optimizations for ExpandQuery and ColTor

To mitigate the DRAM access overhead during these steps, we introduce a hierarchical search (HS) algorithm to maximize data reuse during ExpandQuery and ColTor. Common tree search algorithms, such as breadth-first search (BFS) and depth-first search (DFS) present distinct trade-offs for these steps. When using BFS for ColTor (see Fig. 7a), ct<sub>RGSW</sub> (sel\_bit) can be highly reused across external products at the same depth, reducing ct<sub>RGSW</sub> access overhead. However, limited on-chip memory forces temporary outputs (Z) to be written back to and reloaded from DRAM for each subsequent depth, incurring significant memory access. In contrast, DFS-based ColTor (see Fig. 7b) reduces DRAM access for temporary outputs by immediately processing intermediate results (X and Y) from prior depth. However, as a separate ct<sub>RGSW</sub> is required for each depth, its reuse becomes severely limited.

HS combines the advantages of BFS and DFS while mitigating their drawbacks. HS partitions the entire tree into subtrees whose working sets fit in the on-chip memory during processing, improving the reuse rate of  $\mathbf{ct}_{RGSW}$  (or evk) and  $\mathbf{ct}_{BFV}$ . For example, in ColTor using HS (see Fig.7c), the ct<sub>RGSW</sub>s (ct rgsw) are reused across the entire loop and the temporary outputs (Z) are also reused in subsequent depth computations within each subtree. This is enabled by selecting a proper subtree size that makes the working set fit in the on-chip memory. Thus, HE requires only 2<sup>depth</sup>subtree DRAM reads for the initial  $\mathbf{ct}_{BFV}$  loads, and one DRAM store for the final result for each subtree. This translates to a  $\frac{2^{\text{depth}_{\text{subtree}}}+1}{3\cdot 2^{\text{depth}_{\text{subtree}}}-3} \times$ reduction in DRAM access for ct<sub>BFV</sub> over BFS. Although HS reorders the operation scheduling sequences, it does not alter the order of operations applied to each ciphertext; thus, it does not introduce any additional error growth.

Our HS method favors a DFS-based approach for processing each subtree, rather than BFS, as DFS involves a smaller working set for a given subtree depth. While larger subtree depth leads to greater reductions in DRAM access, increasing the depth also expands the working set, whose size can exceed the on-chip memory capacity. In the ColTor utilizing BFS-based HS, the required memory capacity is given by

$$depth_{subtree} \cdot \mathbf{ct}_{RGSW} + 2^{depth_{subtree} - 1} \cdot \mathbf{ct}_{BFV}$$

Fig. 8. Amounts of DRAM access during (a) ExpandQuery and (b) ColTor for 32-batched PIR queries for an 8GB DB for different scheduling methods. R.O. denotes reduction overlapping.

to accommodate all  $ct_{BFV}$  corresponding to the subtree width. DFS-based approach, in contrast, computes external products as soon as possible, requiring a memory capacity of

$$depth_{subtree} \cdot ct_{RGSW} + (depth_{subtree} + 1) \cdot ct_{BFV}$$

when one  $\mathbf{ct_{BFV}}$  is waiting for tree reduction in each depth. Thus, the DFS-based approach requires less space for  $\mathbf{ct_{BFV}}$ ; conversely, it enables a larger subtree depth usage for a fixed on-chip memory capacity to maximize the benefits of HS. HS is also applicable to ExpandQuery, as its computational process is a mirror image of ColTor.

To further mitigate the bottlenecks, we introduce *reduction* overlapping (R.O.) for Dcp. During an external product, Dcp expands a polynomial into  $\ell$  polynomials, requiring a temporary memory space of  $\ell \times \operatorname{ct}_{\operatorname{BFV}}$  (see Fig. 3), which limits the HS subtree depth. To address this, we overlap the reduction process with bit extraction and NTT computations for each  $a_i$  and  $b_i$ . By leveraging dedicated units for NTT and elementwise operations, intermediate polynomials are reduced justin-time via partial GEMM, preventing them from occupying additional memory space. R.O. is also applicable to Subs computations in ExpandQuery as they contain Dcp.

HS and R.O. significantly reduce DRAM access during ExpandQuery and ColTor, alleviating the bandwidth bottlenecks. Compared to a BFS baseline, BFS-based HS achieves  $1.75 \times$  and  $1.81 \times$  reductions in DRAM data transfers for

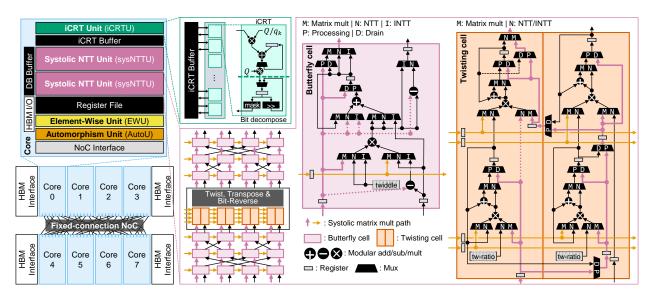

Fig. 9. IVE architecture simplified to eight cores and eight lanes per core  $(N=2^6)$ , and the microarchitectures of our systolic NTT unit (sysNTTU) and iCRT unit (iCRTU). The full IVE configuration features 32 cores and 64 lanes per core  $(N=2^{12})$ .

ExpandQuery and ColTor, respectively (Fig. 8). DFS also reduces DRAM access over BFS, but its benefit is limited due to heavy access for evks in ExpandQuery and  $ct_{RGSW}$  in ColTor. DFS-based HS enables deeper subtree depths during ExpandQuery, yielding an extra 7% reduction over BFS-based HS. In ColTor, R.O. further shrinks working sets, supporting even larger subtree depths to reduce DRAM access by  $1.23\times$  over DFS-based HS. Overall, our optimizations reduce DRAM traffic by  $1.87\times$  and  $2.24\times$  in ExpandQuery and ColTor, respectively (Fig. 8). These benefits hold regardless of the DB size as they depend only on the subtree configuration. We further analyze their performance impacts in §VI-C.

# B. IVE: An accelerator for batched single-server PIR

Building on these optimizations, we propose IVE, an efficient accelerator for batched single-server PIR, leveraging Versatile processing Elements. RowSel is dominated by GEMM, while other steps are NTT-heavy (Fig.7d), requiring support for both computations (§III-A). However, as PIR steps execute sequentially (§IV-C), hardware specialized for a single type of computation would often remain idle. To address this inefficiency, IVE introduces systolic NTT unit (sysNTTU), a versatile engine capable of performing both NTT and GEMM. IVE comprises 32 vector cores interconnected via a networkon-chip (NoC) that adapts data movement to the parallelism of each step. Each core follows a 64-lane vector core design from F1 [88], also adopted in [58], [59], [89]. Each core contains two sysNTTUs, an iCRT unit (iCRTU), an element-wise unit (EWU), an automorphism unit (AutoU), and 5MB of managed SRAM partitioned into register file (RF) and buffers.

# C. Versatile systolic NTTU (sysNTTU)

Due to the strong data dependency between the steps, the PIR computation is inherently sequential (ExpandQuery  $\rightarrow$  RowSel  $\rightarrow$  ColTor). Pipelining offers no benefit as it increases

data movement. For example, consider pipelining RowSel with ExpandQuery by chunking the  $D_0$  BFV ciphertexts  $(\mathbf{ct}_{BFV}[0], \cdots, \mathbf{ct}_{BFV}[D_0-1])$ , which function as the output of ExpandQuery and the input for RowSel, to start partial RowSel computation right after ExpandQuery computation is finished for each chunk. However, this approach incurs  $(\# \text{ of chunks}) \times \text{ more memory access to accumulate partial outputs from RowSel, which degrades PIR throughput.}$

We design our sysNTTU to support both (i)NTT and GEMM within a unified unit, instead of using separate functional units for them. With the sequential processing of PIR, the sysNTTU improves hardware area efficiency without sacrificing performance. Fig. 9 shows the microarchitecture of sysNTTU. We start from a fully pipelined vector NTT unit design from prior studies [59], [88], placing  $\frac{\sqrt{N}}{2} \log N$  butterfly cells, which directly follow the FFT dataflow, with additional twisting, transposition, and bit-reversal circuits. While mostly reusing the existing datapath, we add GEMM datapath based on the output-stationary systolic array dataflow [20] (see Fig. 9). Each butterfly cell also function as a systolic array cell. Furthermore, a pair of twisting cells, which utilizes onthe-fly twisting [59], is repurposed as four systolic array cells. The resulting sysNTTU function as a  $\frac{\sqrt{N}}{2} \times (\log N + 4) =$ 32×16 systolic array, switching between NTT and GEMM via configurable MUXes. For GEMM, the DB buffer streams the database matrix horizontally, while the RF supplies the query matrix vertically (pink path in Fig. 9). Final outputs are drained through the query path by asserting the drain flag (D) on the MUXes. Two sysNTTUs per core, operating at 1GHz, deliver 1TOPS of modular multiply-and-add (MMAD) throughput for GEMM, while also supporting (i)NTT with high throughput.

# D. Parallelization strategies

Batched PIR execution exposes abundant parallelism that can be exploited by the cores in IVE. First, RowSel can

Fig. 10. Data exchange methods using the hierarchical network-on-chip (NoC) structure of IVE simplified to four cores and eight lanes per core. Different colors represent different queries, while different numbers indicate distinct coefficients.

leverage CLP (§II-B) as it can be regarded as a 4N-parallel GEMMs (see Fig. 5); NTT has transformed a polynomial mult into an element-wise mult between length-4N coefficient vectors. To exploit CLP, each set of 4N coefficients is evenly distributed across the cores of IVE. Then, each core computes  $\frac{4N}{\text{\# of cores}}$  GEMM operations in parallel.

ExpandQuery and ColTor cannot exploit CLP as their (i)NTT and iCRT operations involve inter-coefficient computations. Instead, we utilize another type of parallelism stemming from batching: *query-level parallelism (QLP)*. To exploit QLP, each core independently performs ExpandQuery and ColTor for different queries, preventing inter-core communication.

# E. Network-on-chip (NoC)

Due to the intersecting data distribution methods in the two parallelization strategies (§IV-D), we need to 'transpose' the data layout by swapping the 'axis' for batches with that of coefficients. To enable data layout transposition between adjacent PIR steps, IVE leverages a hierarchical NoC structure with local data transpose units and fixed-wire global interconnects. Fig. 10 exemplifies the transition from QLP to CLP. At start, each core holds data from different queries for QLP (Fig. 10-(1). For the transition to CLP, IVE first performs a local transposition at each core, loading a data element from each lane and transposing each  $\frac{\text{(# of lanes)}}{\text{(# of cores)}} \times \frac{\text{(# of lanes)}}{\text{(# of cores)}}$  data block (Fig. 10-2). The local transpose unit design is inspired by CraterLake [89]. Then, the cores can exchange data globally in a fixed transposition pattern, requiring each lane to connect to only one other lane in a different core through a fixed-wire global interconnect. Overhead due to the global interconnects linearly increases with the number of cores, allowing us to scale the system for many cores with small NoC overheads. After the global transposition, each core contains coefficients for the same coefficient index, but from (# of lanes) different queries (Fig. 10-(3)), the data distribution of which fits CLP.

# F. Other hardware components

**iCRT unit (iCRTU):** Fig. 9 shows the microarchitecture of an iCRTU used in IVE. An iCRTU consists of  $\sqrt{N}$  iCRTU cells, each responsible for two key computations required during Dcp: iCRT and bit extraction. Each iCRTU cell operates independently, processing separate coefficients of the same polynomial in parallel. To calculate Eq. 3, sysNTTUs are

in charge of calculating  $[a]_{q_k} \cdot (Q/q_k)^{-1} \mod q_k$  and each iCRTU cell is in charge of multiplying  $(Q/q_k) \mod Q$ . This process reconstructs a coefficient of the original polynomial from its RNS representation. The following bit extraction stage iteratively extracts least significant bits from the reconstructed coefficient through masking and right-shifting.

Element-wise operation unit (EWU): For each cycle, an EWU can handle basic element-wise operations, such as  $\sqrt{N}=64$  MMAD operations, and also support small GEMMs between  $2\times 2$  and  $2\times \sqrt{N}$  integer matrices used for external products and Subs. We enable data forwarding from the sysNTTUs to the EWU; thus, the NTT results can be directly used for R.O., reducing RF bandwidth pressure.

**Automorphism unit (AutoU):** For automorphism, we adopted the fully pipelined design of ARK [59].

Memory hierarchy: IVE deploys three on-chip SRAM types: the main RF, an iCRT buffer, and a DB buffer. The RF, the largest at 4MB per core, stores ciphertexts and evks for reuse. Exploiting sequential N-granular access pattern, it employs wide ports (2 words per lane) and interleaved banks to maximize bandwidth. The 448KB iCRT and DB buffers hold intermediate iNTT/iCRT results and DB plaintexts for RowSel, respectively. For an even bandwidth distribution and simplified access, each HBM channel is statically mapped to a core, leveraging the uniform data distribution across the cores.

## G. Exploiting special primes

Due to the small number of primes needed for PIR, we leverage special primes resembling Solinas primes [92] to reduce modular reduction circuit costs. It reduces area and power overhead by replacing costly mults with bit shifts. The scarcity of such primes prevented prior HE accelerators from adopting this strategy. We use four primes with the form of  $2^{27} + 2^k + 1$  ( $k \in \{15, 17, 21, 22\}$ ) for IVE. Utilizing special primes reduces the area of a modular mult circuit based on Montgomery reduction by 9.1% compared to the circuit based on primes satisfying  $q_k = 1 \mod 2^{14}$  [73] used in F1 [88].

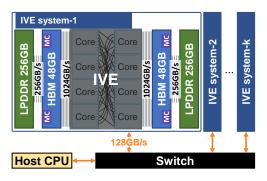

#### V. DESIGNING SCALABLE DEPLOYMENT SYSTEMS

We enable scalability for large DB sizes through a deployment system combining scale-up and scale-out approaches. **Scale-up:** We propose a scale-up *IVE system*, which uses LPDDR memory as an expander to store DB (see Fig. 11).

While LPDDR provides lower bandwidth than HBM, it offers larger capacity [83]. We integrate an LPDDR memory controller [93] onto the logic die of custom HBM. Custom HBM [17] leverages the logic die area for computation, enhancing chip area efficiency. This approach is actively adopted in various research fields [60], [100]. Our design employs four 3D-stacked LPDDR modules [83], each providing 128GB of capacity and 128GB/s of bandwidth.

Our system adaptively uses HBM and LPDDR according to

DB size. For DB fitting in HBM, only HBM is used to avoid the latency overhead of accessing DB from LPDDR. A larger DB exceeding the HBM capacity is offloaded to LPDDR and accessed in a streaming manner during RowSel, while HBM continues to serve memory-bound ExpandQuery and ColTor steps. Since DB data is accessed only in RowSel, where multiquery batching mitigates the bandwidth bottlenecks, the lower bandwidth of LPDDR has negligible impact on PIR throughput as batch size grows (later discussed with Fig. 13d). In our configuration, an IVE system supports up to 128GB of DB. **Scale-out:** A scale-out IVE system, denoted as *IVE cluster*, enables a linear scaling of supported DB size by increasing the number of IVE systems. In an IVE cluster, numsystem IVE systems are connected via a central PCIe switch, providing up to 128GB/s of interconnect bandwidth. We introduce recordlevel parallelism (RLP), which enables parallel processing across the IVE systems. In RLP, the DB matrix is partitioned along the  $\frac{D}{D_0}$  dimension (see Fig.5), with each node receiving a  $\frac{D}{D_0 \cdot \text{num}_{\text{system}}} \times D_0 \times 4N$  matrix slice. Each system performs RowSel on its assigned DB slice and can independently execute ColTor on the RowSel output because the early stages of ColTor involve tournament-style selection among adjacent column entries within the local slice. Finally, the partial ColTor outputs from systems are gathered into a single

**Batch scheduler:** To use multi-client batching in reality, we need a batch scheduler. We employ a basic batch scheduler that has a time window waiting for queries, termed a *waiting window*, to bound the latency overhead of batching. We set the duration of this window based on the DB access time in RowSel. As batching only amortizes the cost of DB access, waiting beyond this threshold increases latency without improving throughput. In this way, the latency overhead remains below  $2\times$  while fully leveraging the benefits of multi-client query batching. A detailed analysis of the latency overhead introduced by our batch scheduler is provided in \$VI-F.

IVE system for the final ColTor processing. The gathering

overhead is negligible (Comm. in Fig. 13d) as each node sends

## VI. EVALUATION

# A. Implementation and experimental setup

only a single ciphertext after local ColTor.

Hardware modeling: We modeled IVE's hardware cost primarily through RTL synthesis using the ASAP7 7.5-track 7nm predictive process design kit [28]. SRAM and long wiring were evaluated with a modified version of FinCACTI [91], incorporating published 7nm process data [16], [50], [52], [54], [78], [94], [99] for calibration. The hardware components

Fig. 11. Architecture of the deployment system using scale-up and scale-out system of IVE.

run at 1GHz (RF at 1.25GHz). The RF, DB buffer, and iCRT buffer use single-ported SRAM banks, providing 2.04TB/s, 0.81TB/s, and 0.41TB/s of per-core bandwidth, respectively. Each 24GB HBM stack offers 512GB/s of bandwidth [82], with four stacks used chip-wide. DRAM power and HBM PHY area follow prior estimates [54], [81]. The default 32-core IVE configuration with 5MB SRAM per core occupies 155.3mm<sup>2</sup> of area and consumes up to 239.1W of power (see Table II), including HBM.

**Performance modeling:** We developed a cycle-level simulator that models each functional unit. Given parameters, such as  $D_0$ , d, and batch size, as input, it constructs an operation graph for respecting data dependencies and avoiding hazards. Operations are issued once dependencies are cleared, decomposed into core functions (e.g., (i)NTT), and dispatched to appropriate units. Each functional unit maintains a separate queue and executes instructions based on pipeline availability. **Data scheduling:** We adopted the decoupled data orchestration approach from CraterLake [89]. As HE workloads form static directed acyclic computational graphs [88], the compiler can precompute an optimal schedule, prefetching data independently of the compute flow to hide memory latency.

Compared systems: We used the latest open-source implementations of OnionPIRv2 [21], which is an optimized version of OnionPIR. Performance was measured on an Intel Xeon Max 9460 CPU system with 1TB of DDR5-4800 memory. Additionally, we implemented an OnionPIR-based PIR protocol on GPUs for computational analysis (§III) and performance comparisons, using NVIDIA RTX4090 and H100 GPUs. Our GPU implementation includes optimized kernel implementations of primitive functions and leverages both CLP and QLP across all kernels to maximize parallelism.

**PIR configuration:** Table I lists each parameter value used for evaluation. This parameter setting is aligned with OnionPIR but adjusted for 128-bit security constraints [10] by reducing Q. For IVE, a batch size of 64 was used unless otherwise specified. For GPUs, the maximum batch size from the device memory capacity was used. We used queries processed per second (QPS) as the primary metric for comparison. We used both synthesized small DBs and real workloads, including voice

TABLE II AREA AND PEAK POWER CONSUMPTION OF 32-CORE IVE

| Component    | Area (mm <sup>2</sup> ) | Peak power (W) |

|--------------|-------------------------|----------------|

| sysNTTU      | 0.77                    | 2.17           |

| iCRTU        | 0.05                    | 0.13           |

| EWU          | 0.10                    | 0.37           |

| AutoU        | 0.07                    | 0.11           |

| RF & buffers | 1.38                    | 1.63           |

| 1 core       | 2.91                    | 5.12           |

| 32 cores     | 93.1                    | 163.8          |

| NoC          | 2.6                     | 6.7            |

| HBM          | 59.6                    | 68.6           |

| Sum          | 155.3                   | 239.1          |

calling (Vcall) [2], anonymous communication (Comm) [4], [5], and file system (Fsys) [70].

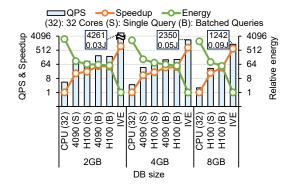

#### B. Performance evaluation

IVE achieves superior throughput than both prior studies and our GPU implementation across all evaluated DB sizes. In terms of geometric mean (gmean), IVE achieves 687.6× higher QPS than 32-core CPU implementations for 2–8GB DBs. GPUs outperform CPUs due to higher DRAM bandwidth and integer computation throughput, even without batching. While batching further improves QPS on GPUs, IVE achieves up to 18.7× higher average throughput compared to the best GPU-based batched PIR. Finally, as IVE mitigates the bandwidth bottlenecks in ExpandQuery and ColTor, each step's execution time (Fig. 13a) closely aligns with its computational complexity (Fig. 4a), exhibiting compute-bound characteristics.

Further, IVE consume less energy than the baseline platforms. We measured energy of the CPU and the GPU using Intel's Running Average Power Limit (RAPL) [51] and NVIDIA Management Library (NVML) API [80], respectively. We estimated IVE's total energy consumption based on each component's utilization. CPUs consumed 72J, 107J, and 176J per query for 2GB, 4GB, and 8GB DBs, respectively. The GPU implementation with batching showed, on average, 43.3× lower energy consumption compared to the CPU across all database sizes. Finally, IVE, achieving the shortest latency, consumed 0.03J, 0.05J, and 0.09J per query for 2GB, 4GB, and 8GB databases, respectively, resulting in an average of 51.3× energy consumption reduction compared to the GPU.

IVE outperforms state-of-the-art PIR hardware acceleration studies as shown in Table III. Compared to CIP-PIR [44] and DPF-PIR [87], both of which utilize GPUs to accelerate multiserver PIR schemes, IVE processes 74.1× and 5.0× higher throughput in gmean, respectively, while providing stronger security guarantees with single-server PIR. Further, an IVE cluster with 16 IVE systems achieves 413.0, 544.6, and 127.5 QPS for Vcall, Comm, and Fsys, respectively, with a batch size of 128. Compared to INSPIRE [66], which uses in-storage ASICs for HE-based PIR, IVE delivers 1,243× higher QPS per system on average by exploiting  $\sim$ 1K× greater arithmetic

Fig. 12. Comparison of PIR throughput and energy consumption (J/query) between IVE, OnionPIRv2 [22], and our GPU implementation of OnionPIRv2.

TABLE III

Number of PIR queries handled in a second (QPS) of IVE and that of prior PIR hardware acceleration studies.

|                       |                          | CIP-PIR<br>[44] <sup>‡</sup> | DPF-PIR<br>[87]*  | INSPIRE<br>[66] <sup>‡</sup> | IVE                                                            | per IVE system<br>(vs. INSPIRE)             |

|-----------------------|--------------------------|------------------------------|-------------------|------------------------------|----------------------------------------------------------------|---------------------------------------------|

| Server co             | -                        | Multi<br>GPU                 | Multi<br>GPU      | Single<br>ASIC               | Single<br>ASIC                                                 | -                                           |

| Workload   DB size    |                          | QPS                          |                   |                              |                                                                |                                             |

| Synthesized DB        | 2GB<br>4GB<br>8GB        | 33.2<br>16.0                 | 956<br>466<br>225 | -<br>-<br>-                  | 4,261<br>2,350<br>1,242                                        | 4,261 (-)<br>2,350 (-)<br>1,242 (-)         |

| Vcall<br>Comm<br>Fsys | 384GB<br>288GB<br>1.25TB | -<br>-<br>-                  | -<br>-<br>-       | 0.021<br>0.028<br>0.006      | 413.0 <sup>†</sup><br>544.6 <sup>†</sup><br>127.5 <sup>†</sup> | 25.8 (1229×)<br>34.0 (1225×)<br>8.0 (1275×) |

- We used the reported values in the paper.

- We evaluated its open-source implementation [87] on RTX4090.

- We used an IVE cluster with 16 IVE systems and 128 batch size.

throughput enabled by the high bandwidth of DRAM. Notably, the IVE cluster achieves a latency of 0.24s for the Comm workload, which is  $150\times$  faster than INSPIRE's single-query processing of 36s, despite batching.

# C. Sensitivity study

Algorithmic optimizations: Our algorithmic optimizations significantly improve the overall PIR throughput. For a 16GB DB (see Fig. 13b), applying DFS-based HS reduces the execution time of ExpandQuery and ColTor by  $1.3\times$  and 1.75×, respectively, leading to an end-to-end latency reduction of 1.2×. Reduction overlapping (R.O.) achieves an additional 1.06× improvement over DFS-based HS by accelerating ColTor 1.28×. Finally, combining our optimizations yields an additional 1.26× reduction in end-to-end latency, improving ExpandQuery and ColTor by  $1.3 \times$  and  $2.23 \times$ , respectively. Query batch size: Regardless of DB size, batching effectively reduces DB access bandwidth demands, making RowSel compute-bound. Fig. 13c and 13d present the latency breakdown and throughput for a single IVE (16GB), an IVE system (128GB), and an IVE cluster (1TB with 16 systems) across various batch sizes. For a 16GB DB fitting in HBM, throughput increases until a batch size of 64, yielding 1.1× higher QPS than at 32. Beyond this, the benefits of batching plateau

Fig. 13. Sensitivity study of IVE with (a) different database sizes, (b) different algorithms, (c) batch size scaling for 16GB DB, (d) batch sizes scaling for large-scale DBs (128GB and 1TB), and (e) architectural optimizations.

as RowSe1 becomes compute-bound and other steps remain non-amortizable, resulting in a linear latency growth and a saturation QPS of 591. For larger 128GB and 1TB DBs, which require LPDDR offloading, our system requires a larger batch size of 128 to reach saturation in order to compensate for the lower bandwidth of LPDDR, achieving 79.9 and 9.89 QPS per system, respectively. At saturation, the product of QPS per IVE and DB size remains nearly constant, showing scalability.

While batching significantly boosts throughput, it incurs only a modest increase in service latency— $3.46\times$ ,  $1.60\times$ , and  $1.62\times$  for 16GB, 128GB, and 1TB DBs, respectively (Fig. 13c and 13d). As each query transfers only a few MBs of client-specific data through PCIe, communication overhead (Comm.) is negligible (<8%), dropping below 1% for larger DBs. Throughput gains are substantial at  $18.9\times(16\text{GB})$ ,  $79.9\times(128\text{GB})$ , and  $79.1\times(11\text{TB})$ , far outweighing the latency increase and underscoring the effectiveness of batching.

Architectural optimizations: Using special primes reduces both energy consumption and system area. Compared to the baseline (Base in Fig. 13e), which uses separate computing units for (i)NTT and GEMM (each with the same throughput as a sysNTTU), special primes reduce area and energy by 4% (+Sp in Fig.13e). Meanwhile, there is a trade-off in adopting sysNTTU. As all PIR steps are processed sequentially, the system (+SysNTTU in Fig. 13e) incurs no performance loss and achieves a 7% area reduction. However, energy consumption increases by  $1.1\times$  due to extra circuits required to support both (i)NTT and GEMM within a single unit.

# D. Applicability of IVE to other PIR schemes

Although HE-based PIR schemes differ in structure, they share core HE operations. SimplePIR [49] mainly performs modular GEMMs, while KsPIR [67] and InsPIRe [68], a concurrent PIR work, rely on automorphism, key-switching, and external-products, which are all efficiently supported by IVE. Using 2–4 GB DBs, IVE achieves 1,904–2,063× and 3,246–3,347× higher QPS than the CPU versions of SimplePIR and KsPIR (Table IV). As most HE-based PIR protocols [15], [31], [68], [71] rely on similar primitives, IVE can potentially support them with minimal changes.

TABLE IV

PERFORMANCE COMPARISON OF CPU IMPLEMENTATIONS AND IVE FOR OTHER SINGLE-SERVER PIR SCHEMES.

|                |         | QF                                | PS  |                |

|----------------|---------|-----------------------------------|-----|----------------|

| Scheme         | 2GB 4GB |                                   |     | 4GB            |

|                | CPU     | IVE                               | CPU | IVE            |

| SimplePIR [49] | 6.2     | 11,766 (1,904×)                   | 2.9 | 5,883 (2,063×) |

| KsPIR [67]     | 0.8     | 11,766 (1,904×)<br>2,555 (3,347×) | 0.4 | 1,288 (3,246×) |

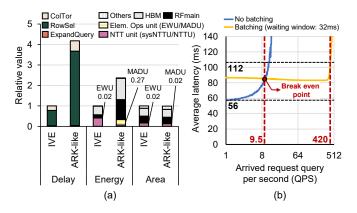

Fig. 14. (a) Energy, delay, and area comparison of IVE and an ARK [59]-like system, and (b) load-latency curve under our batch scheduling strategy, both measured with a 16GB DB.

## E. Comparison to prior HE accelerator architectures

To evaluate IVE's hardware efficiency, we compare it against an ARK-like system [59], representative of state-of-the-art HE accelerators [58], [88], [89]. We downscale ARK, which is designed for  $N=2^{16}$ , to match our parameters ( $N=2^{12}$ ). The ARK-like baseline includes 64 cores, each equipped with an NTTU (matching IVE's total NTT throughput), two multiply-add units (MADUs) [59], 2MB of scratchpad memory, and other functional units from IVE. As ARK lacks a dedicated GEMM unit, GEMM operations are mapped to the MADUs. For other configurations, to ensure a fair comparison, we applied the same settings, including special-prime usage, on both IVE and ARK.

IVE outperforms the ARK-like system in both latency and energy efficiency (Fig. 14a). While the sysNTTUs in IVE fully exploit the increased arithmetic intensity of batched RowSel, the ARK-like system suffers from the limited GEMM throughput of the MADUs. As a result, IVE achieves 4.2× higher PIR throughput for a 16GB DB. Also, MADU-based GEMM operations require repeated data access to the RF, leading to higher energy consumption. Moreover, the smaller per-core on-chip memory in ARK limits data reuse, resulting in additional energy consumption due to increased DRAM access. Consequently, the ARK-like system consumes 2.4× more energy to retrieve a record from the DB. Finally, as the sysNTTUs introduce only a 1.4% area overhead, the total area of IVE remains comparable to that of the ARK-like system. Overall, IVE achieves an 9.7× better energy-delayarea product (EDAP) than the ARK-like system.

#### F. Batch scheduling system

Even in practical deployment scenarios with random query arrivals and limited concurrency, IVE with a batch scheduler can accommodate a wide range of load conditions through its high throughput, while restricting the latency overhead to at most 2× compared to the non-batching case. We demonstrate this by modeling request arrivals with a Poisson distribution and measuring the PIR latency of a 16GB DB under different load conditions (see Fig. 14b). Our strategy reaches a breakeven point at 9.5 QPS, where the average latency of the non-batching case rises sharply as it approaches its throughput limit, which is the reciprocal of the single-query processing rate (17.8 in Fig. 14b). Beyond this point, batching keeps the latency within the 2× bound up to 420 QPS, whereas the latency of the non-batching case continues to increase rapidly, resulting in a 44.2× throughput advantage.

# VII. RELATED WORK

Other HE-based PIR: Numerous studies have proposed PIR protocols based on HE. SimplePIR [49] and FrodoPIR [31] reduce computation by offloading part of the work to an offline phase, but this comes at the cost of client-side storage and preprocessing overhead. FastPIR [2] leverages homomorphic automorphism to reduce computational complexity, and INSPIRE [66] builds on this by optimizing the algorithm to lower query data transfer. Other studies [3], [4], [15], [71], [76] focus on reducing communication overhead while balancing computational cost. Some approaches [3], [4] use query compression, accepting additional server-side cost for decompression. Others [15], [71], [76] mitigate HE-induced data expansion through external product.

**GPU/ASIC** acceleration of **PIR**: Despite growing interest in PIR, only a few studies [44], [64], [66] have explored hardware acceleration using GPUs or ASICs, each targeting different PIR protocols. [64] focuses on two-server computational PIR based on distributed point functions (DPFs), rooted in multi-party computation, while [44] enhances multi-server information-theoretic PIR. Most relevant to our work, INSPIRE [66] proposes an in-storage accelerator for HE-based

single-server PIR. These studies highlight the diversity of PIR acceleration strategies, each addressing distinct challenges and optimization opportunities specific to their target protocol.

Alternative privacy solutions: PIR is often compared to oblivious RAM (ORAM), which similarly enables private access to a database. For example, Compass [102] builds a semantic search system based on ORAM. While it typically incurs  $\mathcal{O}(\log D) - \mathcal{O}(\log^2 D)$  overhead per data access [86], [95], its design focuses on concealing access patterns for encrypted private data. In contrast, PIR works over public or shared data for multiple clients. While numerous studies [74], [90], [97], [101] use trusted execution environments (TEEs) for enhanced performance, its fundamental risks lie in microarchitecturebased attacks, as continue to be discovered in [13], [14], [19], [30], [42], [77]. Meanwhile, anonymous networks, such as Tor [35] and dummy queries [8], [37], [84] can be used to provide privacy; Wally [7] uses both of them to implement private semantic search. Although these alternative solutions often achieve asymptotically lower costs than PIR, they mostly rely on additional assumptions or provide privacy guarantees less rigorous than those offered by cryptographic PIR.

# VIII. CONCLUSION

We have proposed IVE, a hardware accelerator for singleserver private information retrieval (PIR) based on homomorphic encryption (HE). We identified that, after mitigating the memory access burden from database reads via batching, the memory bandwidth demand for client-specific data access emerges as the primary bottleneck, limiting overall throughput. In response, IVE employs a large on-chip scratchpad memory and an optimized binary tree search algorithm that maximizes on-chip reuse of the data, thereby achieving high throughput. We also introduced a versatile functional unit capable of handling major computations in PIR, improving the area efficiency of IVE. We proposed a scalable deployment system that combines a scale-up design of IVE using a heterogeneous memory hierarchy and a distributed scale-out cluster. As a result, IVE delivers up to 1,275× higher throughput compared to prior hardware solutions for HE-based PIR on practical workloads.

#### ACKNOWLEDGMENT

This research was in part supported by Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) [RS-2021-II211343, RS-2024-00469698, RS-2025-02217656, RS-2025-02304125]. The EDA tool was supported by the IC Design Education Center (IDEC), Korea. This work was conducted while Sangpyo Kim was with Seoul National University (SNU). Hyesung Ji and Jongmin Kim are with the Interdisciplinary Program in Artificial Intelligence, SNU. Wonseck Choi and Jaiyoung Park are with the Department of Intelligence and Information, SNU. Jung Ho Ahn, the corresponding author, is with the Department of Intelligence and Information and the Interdisciplinary Program in Artificial Intelligence, SNU.

#### REFERENCES

- R. Agrawal, L. de Castro, G. Yang, C. Juvekar, R. T. Yazicigil, A. P. Chandrakasan, V. Vaikuntanathan, and A. Joshi, "FAB: An FPGAbased Accelerator for Bootstrappable Fully Homomorphic Encryption," in HPCA, 2023.

- [2] I. Ahmad, Y. Yang, D. Agrawal, A. El Abbadi, and T. Gupta, "Addra: Metadata-private Voice Communication over Fully Untrusted Infrastructure," in USENIX Symposium on Operating Systems Design and Implementation, 2021.

- [3] A. Ali, T. Lepoint, S. Patel, M. Raykova, P. Schoppmann, K. Seth, and K. Yeo, "Communication-Computation Trade-offs in PIR," in USENIX Security Symposium, 2021.

- [4] S. Angel, H. Chen, K. Laine, and S. Setty, "PIR with Compressed Queries and Amortized Query Processing," in *IEEE Symposium on Security and Privacy*, 2018.

- [5] S. Angel and S. Setty, "Unobservable Communication over Fully Untrusted Infrastructure," in USENIX Symposium on Operating Systems Design and Implementation, 2016.

- [6] Apple, "Live caller id lookup example," 2024, gitHub repository, Accessed: 2025-02-16. [Online]. Available: https://github.com/apple/ live-caller-id-lookup-example

- [7] H. Asi, F. Boemer, N. Genise, M. H. Mughees, T. Ogilvie, R. Rishi, K. Talwar, K. Tarbe, A. Wadia, R. Zhu et al., "Scalable Private Search with Wally," arXiv preprint arXiv:2406.06761, 2024.

- with Wally," arXiv preprint arXiv:2406.06761, 2024.

[8] E. Balsa, C. Troncoso, and C. Diaz, "OB-PWS: Obfuscation-Based Private Web Search," in 2012 IEEE Symposium on Security and Privacy, 2012, pp. 491–505.

- [9] F. Boemer, S. Kim, G. Seifu, F. D. M. de Souza, and V. Gopal, "Intel HEXL: Accelerating Homomorphic Encryption with Intel AVX512-IFMA52," in Workshop on Encrypted Computing & Applied Homomorphic Cryptography, 2021.

- [10] J.-P. Bossuat, R. Cammarota, J. H. Cheon, I. Chillotti, B. R. Curtis, W. Dai, H. Gong, E. Hales, D. Kim, B. Kumara, C. Lee, X. Lu, C. Maple, A. Pedrouzo-Ulloa, R. Player, L. A. R. Lopez, Y. Song, D. Yhee, and B. Yildiz, "Security Guidelines for Implementing Homomorphic Encryption," *IACR Cryptology ePrint Archive*, no. 463, 2024.

- [11] Z. Brakerski, "Fully Homomorphic Encryption without Modulus Switching from Classical GapSVP," in *Annual cryptology conference*. Springer, 2012, pp. 868–886.

- [12] Z. Brakerski, C. Gentry, and V. Vaikuntanathan, "(Leveled) Fully Homomorphic Encryption without Bootstrapping," ACM Transactions on Computing Theory, vol. 6, no. 3, pp. 1–36, 2014.

- [13] F. Brasser, U. Müller, A. Dmitrienko, K. Kostiainen, S. Capkun, and A.-R. Sadeghi, "Software Grand Exposure: SGX Cache Attacks Are Practical," in 11th USENIX Workshop on Offensive Technologies (WOOT 17), 2017.

- [14] J. V. Bulck, M. Minkin, O. Weisse, D. Genkin, B. Kasikci, F. Piessens, M. Silberstein, T. F. Wenisch, Y. Yarom, and R. Strackx, "Foreshadow: Extracting the Keys to the Intel SGX Kingdom with Transient Out-of-Order Execution," in 27th USENIX Security Symposium (USENIX Security 18), 2018, pp. 991–1008.

- [15] A. Burton, S. J. Menon, and D. J. Wu, "Respire: High-Rate PIR for Databases with Small Records," in ACM Conference on Computer and Communications Security, 2024.

- [16] J. Chang, Y. Chen, W. Chan, S. P. Singh, H. Cheng, H. Fujiwara, J. Lin, K. Lin, J. Hung, R. Lee, H. Liao, J. Liaw, Q. Li, C. Lin, M. Chiang, and S. Wu, "A 7nm 256Mb SRAM in High-K Metal-Gate FinFET Technology with Write-Assist Circuitry for Low-VMIN Applications," in *IEEE International Solid-State Circuits Conference*, 2017, pp. 206– 207.

- [17] K. Chatterjee, Y. Li, H. Chang, M. Damadam, P. Asrar, J. Kim, G. Jeong, and W. Kim, "Thermal and Mechanical Simulations of 3D Packages with Custom High Bandwidth Memory (HBM)," in *IEEE Electronic Components and Technology Conference*, 2024, pp. 1054–1059, https://doi.org/10.1109/ECTC51529.2024.00169.

- [18] D. Chaum, "The dining cryptographers problem: Unconditional sender and recipient untraceability," *Journal of cryptology*, vol. 1, no. 1, pp. 65–75, 1988.

- [19] G. Chen, S. Chen, Y. Xiao, Y. Zhang, Z. Lin, and T. H. Lai, "SgxPectre: Stealing Intel Secrets from SGX Enclaves Via Speculative Execution," in 2019 IEEE European Symposium on Security and Privacy (EuroS&P), 2019, pp. 142–157.

- [20] Y.-H. Chen, J. Emer, and V. Sze, "Eyeriss: A Spatial Architecture for Energy-Efficient Dataflow for Convolutional Neural Networks," in ISCA, 2016, pp. 367–379.

- [21] Y. Chen, "OnionPIRv2: Efficient Single-Server PIR," https://github. com/chenyue42/OnionPIRv2, 2025, accessed: 2025-10-17.

- [22] Y. chen and L. Ren, "OnionPIRv2: Efficient Single-Server PIR," IACR Cryptology ePrint Archive, no. 1142, 2025.

- [23] J. H. Cheon, K. Han, A. Kim, M. Kim, and Y. Song, "Bootstrapping for Approximate Homomorphic Encryption," in *Annual International Con*ference on the Theory and Applications of Cryptographic Techniques, 2018.

- [24] J. H. Cheon, A. Kim, M. Kim, and Y. S. Song, "Homomorphic Encryption for Arithmetic of Approximate Numbers," in *International Conference on the Theory and Applications of Cryptology and Infor*mation Security, 2017.

- [25] I. Chillotti, N. Gama, M. Georgieva, and M. Izabachene, "Faster fully homomorphic encryption: Bootstrapping in less than 0.1 seconds," in International Conference on the Theory and Application of Cryptology and Information Security, 2016.

- [26] I. Chillotti, N. Gama, M. Georgieva, and M. Izabachène, "TFHE: Fast Fully Homomorphic Encryption over the Torus," *Journal of Cryptology*, vol. 33, no. 1, pp. 34–91, 2020.

- [27] B. Chor, E. Kushilevitz, O. Goldreich, and M. Sudan, "Private Information Retrieval," *Journal of the ACM (JACM)*, vol. 45, no. 6, pp. 965–981, 1998.

- [28] L. T. Clark, V. Vashishtha, L. Shifren, A. Gujja, S. Sinha, B. Cline, C. Ramamurthy, and G. Yeric, "ASAP7: A 7-nm FinFET Predictive Process Design Kit," *Microelectronics Journal*, vol. 53, pp. 105–115, 2016.

- [29] H. Corrigan-Gibbs, D. Boneh, and D. Mazières, "Riposte: An anonymous messaging system handling millions of users," in 2015 IEEE Symposium on Security and Privacy (SP), 2015, pp. 321–338.

- [30] J. Cui, J. Z. Yu, S. Shinde, P. Saxena, and Z. Cai, "SmashEx: Smashing SGX Enclaves Using Exceptions," in *Proceedings of the 2021 ACM SIGSAC Conference on Computer and Communications Security*, 2021, pp. 779–793.

- [31] A. Davidson, G. Pestana, and S. Celi, "FrodoPIR: Simple, Scalable, Single-Server Private Information Retrieval," *Proceedings on Privacy Enhancing Technologies*, 2023.

- [32] L. de Castro, K. Lewi, and E. Suh, "WhisPIR: Stateless Private Information Retrieval with Low Communication," *IACR Cryptology* ePrint Archive, no. 266, 2024.

- [33] D. Demmler, A. Herzberg, and T. Schneider, "RAID-PIR: practical multi-server PIR," in *Proceedings of the 6th edition of the ACM Workshop on Cloud Computing Security, CCSW '14, Scottsdale, Arizona, USA, November 7, 2014*, G. Ahn, A. Oprea, and R. Safavi-Naini, Eds. ACM, 2014, pp. 45–56. [Online]. Available: https://doi.org/10.1145/2664168.2664181

- [34] S. Devadas, M. Van Dijk, C. W. Fletcher, L. Ren, E. Shi, and D. Wichs, "Onion ORAM: A Constant Bandwidth Blowup Oblivious RAM," in Theory of Cryptography: 13th International Conference, TCC 2016-A, Tel Aviv, Israel, January 10-13, 2016, Proceedings, Part II 13. Springer, 2016, pp. 145–174.

- [35] R. Dingledine, N. Mathewson, and P. Syverson, "Tor: The Second-Generation Onion Router," in 13th USENIX Security Symposium (USENIX Security 04), 2004.

- [36] R. Dingledine, N. Mathewson, and P. F. Syverson, "Tor: The second-generation onion router," in *USENIX Security Symposium*, vol. 4, 2004, pp. 303–320.

- [37] J. Domingo-Ferrer, A. Solanas, and J. Castellà-Roca, "h(k)-Private Information Retrieval from Privacy-Uncooperative Queryable Databases," Online Information Review, vol. 33, no. 4, pp. 720–744, 2009.

- [38] J. Fan and F. Vercauteren, "Somewhat Practical Fully Homomorphic Encryption," Cryptology ePrint Archive, 2012.

- [39] S. Fan, Z. Wang, W. Xu, R. Hou, D. Meng, and M. Zhang, "TensorFHE: Achieving Practical Computation on Encrypted Data Using GPGPU," in HPCA, 2023, pp. 922–934.

- [40] C. Gentry, A. Sahai, and B. Waters, "Homomorphic Encryption from Learning with Errors: Conceptually-Simpler, Asymptotically-Faster, Attribute-Based," in *Annual International Cryptology Conference*, 2013.

- [41] N. Gilboa and Y. Ishai, "Distributed Point Functions and Their Applications," in Annual International Conference on the Theory and Applications of Cryptographic Techniques, 2014, pp. 640–658.

- [42] J. Götzfried, M. Eckert, S. Schinzel, and T. Müller, "Cache Attacks on Intel SGX," in *Proceedings of the 10th European Workshop on Systems Security*, 2017.

- [43] M. Green, W. Ladd, and I. Miers, "A Protocol for Privately Reporting Ad Impressions at Scale," in ACM Conference on Computer and Communications Security, 2016.

- [44] D. Günther, M. Heymann, B. Pinkas, and T. Schneider, "GPU-accelerated PIR with Client-Independent Preprocessing for Large-Scale Applications," in *USENIX Security Symposium*, 2022.

- [45] T. Gupta, N. Crooks, W. Mulhern, S. Setty, L. Alvisi, and M. Walfish, "Scalable and Private Media Consumption with Popcorn," in *USENIX symposium on networked systems design and implementation*, 2016.

- [46] S. Halevi and V. Shoup, "Bootstrapping for HElib," *Journal of Cryptology*, vol. 34, no. 1, p. 7, 2021.

- [47] R. Henry, F. Olumofin, and I. Goldberg, "Practical PIR for electronic commerce," in ACM Conference on Computer and Communications Security, 2011.

- [48] A. Henzinger, E. Dauterman, H. Corrigan-Gibbs, and N. Zeldovich, "Private web search with tiptoe," in *Proceedings of the 29th symposium on operating systems principles*, 2023, pp. 396–416.

- [49] A. Henzinger, M. M. Hong, H. Corrigan-Gibbs, S. Meiklejohn, and V. Vaikuntanathan, "One server for the price of two: Simple and fast single-server private information retrieval," in *USENIX Security* Symposium, 2023, pp. 3889–3905.

- [50] IEEE, "International Roadmap for Devices and Systems: 2018," Tech. Rep., 2018. [Online]. Available: https://irds.ieee.org/editions/2018/

- [51] Intel Corporation, "Running average power limit (rapl) energy reporting," 2024, accessed: 2025-10-18. [Online]. Available: https://www.intel.com/content/www/us/en/developer/articles/technical/ software-security-guidance/advisory-guidance/running-averagepower-limit-energy-reporting.html