# hls4ml: A Flexible, Open-Source Platform for Deep Learning Acceleration on Reconfigurable Hardware

JAN-FREDERIK SCHULTE\*, Purdue University, USA

BENJAMIN RAMHORST\*, ETH Zurich, Switzerland

CHANG SUN\*, California Institute of Technology, USA

JOVAN MITREVSKI, Fermi National Accelerator Lab, USA

NICOLÒ GHIELMETTI, ENRICO LUPI, DIMITRIOS DANOPOULOS, and VLADIMIR LONČAR<sup>†</sup>, Eu-

ropean Organization for Nuclear Research (CERN), Switzerland

JAVIER DUARTE, University of California San Diego, USA

DAVID BURNETTE, Catapult HLS - Siemens EDA, USA

LAURI LAATU, Imperial College London, United Kingdom

STYLIANOS TZELEPIS, National Technical University of Athens, Greece

KONSTANTINOS AXIOTIS and QUENTIN BERTHET‡, University of Geneva, Switzerland

HAOYAN WANG, PAUL WHITE, and SULEYMAN DEMIRSOY, Altera Corporation, USA

MARCO COLOMBO, Discovery Partners Institute, USA

THEA KLAEBOE AARRESTAD, ETH Zurich, Switzerland

SIONI SUMMERS and MAURIZIO PIERINI, European Organization for Nuclear Research (CERN), Switzerland

GIUSEPPE DI GUGLIELMO, JENNIFER NGADIUBA, JAVIER CAMPOS, BEN HAWKS, ABHIJITH

GANDRAKOTA, FARAH FAHIM, and NHAN TRAN, Fermi National Accelerator Lab, USA

GEORGE A. CONSTANTINIDES, ZHIQIANG QUE, WAYNE LUK, and ALEXANDER TAPPER, Imperial College London, United Kingdom

DUC HOANG, NOAH PALADINO, and PHILIP HARRIS, Massachusetts Institute of Technology, USA

BO-CHENG LAI, National Yang Ming Chiao Tung University, Taiwan

MANUEL VALENTIN, RYAN FORELLI, and SEDA OGRENCI, Northwestern University, USA

LINO GERLACH, Princeton University, USA

RIAN BROOKS FLYNN and MIA LIU, Purdue University, USA

DANIEL DIAZ, ELHAM E KHODA, MELISSA QUINNAN, and RUSSELL MARROQUIN SO-

LARES, University of California San Diego, USA

SANTOSH PARAJULI and MARK S. NEUBAUER, University of Illinois Urbana-Champaign, USA

CHRISTIAN HERWIG, University of Michigan, USA

## HO FUNG TSOI and DYLAN RANKIN, University of Pennsylvania, USA SHIH-CHIEH HSU and SCOTT HAUCK, University of Washington, USA

We present HLS4ML, a free and open-source platform that translates machine learning (ML) models from modern deep learning frameworks into high-level synthesis (HLS) code that can be integrated into full designs for field-programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs). With its flexible and modular design, HLS4ML supports a large number of deep learning frameworks and can target HLS compilers from several vendors, including Vitis HLS, Intel oneAPI and Catapult HLS. Together with a wider eco-system for software-hardware co-design, HLS4ML has enabled the acceleration of ML inference in a wide range of commercial and scientific applications where low latency, resource usage, and power consumption are critical. In this paper, we describe the structure and functionality of the HLS4ML platform. The overarching design considerations for the generated HLS code are discussed, together with selected performance results.

CCS Concepts: • Hardware  $\rightarrow$  Hardware accelerators; Reconfigurable logic applications; • Computing methodologies  $\rightarrow$  Machine learning.

Additional Key Words and Phrases: FPGA, Hardware Acceleration, Machine Learning Acceleration, High-Level Synthesis

#### 1 Introduction

Recent advances in machine learning (ML) and artificial intelligence (AI) have driven the widespread adoption and deployment of neural networks. For example, cloud vendors are increasingly deploying large language models (LLMs) and deep learning recommendation models as part of their services [52, 102]. Similarly, there is an ever-increasing demand for specialized, highly efficient deep learning models for latency- and power-constrained environments, such as real-time systems or edge devices [35]. Some examples include high-energy physics (HEP) systems at CERN [28, 29], robotics [100, 107], network infrastructure [12], industrial manufacturing facilities [101], and satellites and other spacecraft [74, 108]. To tackle the computational and memory requirements of modern neural networks, focus has

Authors' Contact Information: Jan-Frederik Schulte, jschulte@cern.ch, Purdue University, USA; Benjamin Ramhorst, bramhorst@ethz.ch, ETH Zurich, Switzerland; Chang Sun, chsun@cern.ch, California Institute of Technology, USA; Jovan Mitrevski, jmitrevs@fnal.gov, Fermi National Accelerator Lab, USA; Nicolò Ghielmetti, nicolo ghielmetti@cern.ch; Enrico Lupi, enrico.lupi@cern.ch; Dimitrios Danopoulos, dimitrios.danopoulos@cern.ch; Vladimir Lončar, vloncar@cern.ch, European Organization for Nuclear Research (CERN), Switzerland; Javier Duarte, jduarte@ucsd.edu, University of California San Diego, USA; David Burnette, david.burnette@siemens.com, Catapult HLS - Siemens EDA, USA; Lauri Laatu, l.laatu@imperial.ac.uk, Imperial College London, United Kingdom; Stylianos Tzelepis, stylianos.tzelepis@cern.ch, National Technical University of Athens, Greece; Konstantinos Axiotis, kaxiotis1.0@gmail.com; Quentin Berthet, quentin.berthet@hesge.ch, University of Geneva, Switzerland; Haoyan Wang, harry.wang@altera.com; Paul White, paul.white@altera.com; Suleyman Demirsoy, suleyman.demirsoy@altera.com, Altera Corporation, USA; Marco Colombo, mcolom4@uillinois.edu, Discovery Partners Institute, USA; Thea Klaeboe Aarrestad, thea.aarrestad@cern.ch, ETH Zurich, Switzerland; Sioni Summers, sioni@cern.ch; Maurizio Pierini, maurizio.pierini@cern.ch, European Organization for Nuclear Research (CERN), Switzerland; Giuseppe Di Guglielmo, gdg@fnal.gov; Jennifer Ngadiuba, ngadiuba@fnal.gov; Javier Campos, jcampos@fnal.gov; Ben Hawks, bhawks@fnal.gov; Abhijith Gandrakota, abhijith@fnal.gov; Farah Fahim, farah@fnal.gov; Nhan Tran, ntran@fnal.gov, Fermi National Accelerator Lab, USA; George A. Constantinides, g.constantinides@imperial.ac.uk; Zhiqiang Oue, z.que@imperial.ac.uk; Wayne Luk, w.luk@imperial.ac.uk; Alexander Tapper, a.tapper@imperial.ac.uk, Imperial College London, United Kingdom; Duc Hoang, dhoang@mit.edu; Noah Paladino, npaladin@mit.edu; Philip Harris, pcharris@mit.edu, Massachusetts Institute of Technology, USA; Bo-Cheng Lai, bclai@nycu.edu.tw, National Yang Ming Chiao Tung University, Taiwan; Manuel Valentin, manuel.valentin@u.northwestern.edu; Ryan Forelli, rforelli@u.northwestern.edu; Seda Ogrenci, seda@northwestern.edu, Northwestern University, USA; Lino Gerlach, lino.oscar.gerlach@cern.ch, Princeton University, USA; Rian Brooks Flynn, rbflynn@purdue.edu; Mia Liu, liu3173@purdue.edu, Purdue University, USA; Daniel Diaz, d4diaz@ucsd.edu; Elham E Khoda, ekhoda@ucsd.edu; Melissa Quinnan, mquinnan@ucsd.edu; Russell Marroquin Solares, rmarroquinsolares@ucsd.edu, University of California San Diego, USA; Santosh Parajuli, santoshp@illinois.edu; Mark S. Neubauer, msn@illinois.edu, University of Illinois Urbana-Champaign, USA; Christian Herwig, herwig@umich.edu, University of Michigan, USA; Ho Fung Tsoi, hftsoi@sas.upenn.edu; Dylan Rankin, dsrankin@sas.upenn.edu, University of Pennsylvania, USA; Shih-Chieh Hsu, schsu@uw.edu; Scott Hauck, hauck@uw.edu, University of Washington, USA.

<sup>\*</sup>Equal contribution.

<sup>&</sup>lt;sup>†</sup>Also at Institute of Physics Belgrade.

<sup>‡</sup>Currently at HEPIA, HES-SO University of Applied Sciences and Arts Western Switzerland.

shifted from conventional CPUs to specialized hardware, such as GPUs, TPUs, and FPGAs [117]. Complementary to specialized hardware, model compression techniques [22, 49] and novel architectures [64, 137] are also explored.

In low-latency, real-time systems, FPGAs and ASICs have become the de facto platforms for accelerating neural network, achieving low latency by implementing deeply pipelined designs, specifically tailored to the target model [83]. Heterogeneously quantized models [20, 31], or extremely low quantization schemes (e.g., binary and ternary models [85, 131]), take advantage of their high configurability to map operations directly to custom logic elements. FPGAs, in particular, have been deployed in various real-time systems [7, 8, 25, 28, 29], due to their high flexibility and lower entry barrier compared to ASICs. However, traditional FPGA development workflows, even when using higher levels of abstractions, such as High-Level Synthesis (HLS), are poorly suited to adapt the functionality of modern deep learning frameworks (e.g., PyTorch [11], TensorFlow [3]) as they mainly target CPUs and GPUs. Therefore, deploying neural networks on FPGAs still requires considerable experience and significant time investment.

Aiming to solve these issues, there has been a growing number of platforms automating neural network deployment on FPGAs (see Section 12). While these platforms raise the level of abstraction and represent a significant step forward, each platform provides a range of somewhat arbitrary and application-specific features. For example, many of these platforms only support models defined in a single deep learning framework, or target only a single type of FPGA [9, 43, 67]. Additionally, the resulting hardware implementations are typically tailored to specific model architectures and precisions, such as convolutional neural networks (CNNs) [56, 110, 124, 126, 127, 130] or multilayer perceptron (MLPs) [103, 114]. Moreover, these platforms rarely allow the user to choose between different implementations of the models on hardware, which significantly reduces flexibility when balancing latency and resource consumption. Finally, many of these frameworks [54, 103, 114] are no longer actively maintained.

In this work, we present HLS4ML [46]<sup>1</sup>, a free and open-source, easy-to-use, and modular platform that translates models from common deep learning frameworks (e.g. PyTorch, Keras), into low-latency, dataflow designs for FPGAs and ASICs. HLS4ML acts as a compiler, providing user-facing *front ends* that parse trained models and translate them into an *internal representation* (IR), which is iteratively optimized before hardware lowering through a set of *optimizers*. *Back ends* targeting different HLS compilers map the optimized IR to HLS implementations of layers and operators, and create IP cores for the target model that can be synthesized and integrated into larger applications.

HLS4ML supports all major deep learning frameworks, including PyTorch [11], Keras [24], and ONNX [13], as well as their quantized counterparts: QKeras [31], HGQ [20], Brevitas [87], and QONNX [88, 121]. On the back end side, HLS4ML supports a growing set of HLS compilers from different vendors, including Vitis HLS [6] from AMD and OneAPI [66] from Intel. In addition to designs for FPGAs, HLS4ML facilitates the deployment of neural networks on ASICs [39, 89] through Catapult HLS [106]. Model architectures that have been implemented using HLS4ML include MLPs [41], CNNs [2, 48], recurrent neural networks (RNNs) [75], graph neural networks (GNNs) [44, 65, 86], and transformers [70, 71]. Additionally, the Extension API allows users to easily add support for any missing layers or operators, while still leveraging the rest of HLS4ML's implementations and optimizations. Configuring the implementation strategy, hardware parallelization, and variable precision, users can optimize their designs for latency or resource usage without modifying or understanding the HLS code directly. This flexibility allows for rapid prototyping and the co-design of models and hardware. Finally, HLS4ML provides multiple environments for model verification. In addition to conventional software emulation, HLS4ML enables users to directly deploy their model on specific FPGAs (e.g., Zynq or Alveo cards) with a few

lines of Python code. Owing to HLS4ML's modularity and standardized interfaces, it is straightforward to integrate it with any platform for FPGA deployment, with out-of-the-box support for commercial [5, 66] or academic [97] shells.

As a platform, HLS4ML can be used in two ways: first, as a deployment platform for various applications, including HEP experiments [28, 29], quantum computing [14, 38], network firewalls [61], self-driving cars [48], heart signal monitoring [80], and space exploration [108]. Second, HLS4ML can be used as a starting point for research in efficient deep learning and hardware-model co-design [20, 92–94, 98, 118, 119, 134]. Originally presented in [41] for HEP applications at CERN, HLS4ML has since grown into a widely used, open-source project for deep learning acceleration and research on custom hardware (see Section 10 for more details on HLS4ML use cases and applications). The project is actively maintained with contributions from both academia and industry, is well documented and tested, and frequent supporting tutorials, workshops, and seminars are held to foster the user community.

#### 2 Background

FPGAs have emerged as suitable platforms for low-latency, low-power neural network inference, due to their low-level hardware control and high configurability. While development for ASICs is also supported in HLS4ML, FPGAs are the primary target device and the focus of this paper. In the following, we present a brief overview of common design techniques for model inference on FPGAs. More in-depth overviews are given elsewhere [18, 63, 83].

To achieve high throughput and low latency inference, there are many established design techniques. *Parallelization* splits the calculations between multiple processing units (PUs), for example by partitioning the input data between different instances of the layer implementations (data parallelization) or distributing the computation for the neurons of a layer between PUs (model parallelization). *Pipelining* partitions the calculation in depth so that, for example, subsequent layers are assigned to different PUs, allowing continuous data flow through the design. This allows the design to accept new inputs before the overall inference is completed, resulting in a low initiation interval (II). Most frameworks [15, 41, 110, 124] use both techniques to achieve maximum performance.

Many frameworks [41, 56, 122] store weights and intermediate results in on-chip memory to avoid the overhead of accessing off-chip memory. These implementations can achieve very low latency and high throughput for models that fit within the limited on-chip logic resources. For larger models, such as transformers, previous studies [55, 69, 123] have proposed using high-bandwidth memory (HBM) on recent FPGAs.

For computations, many FPGAs include hardened digital signal processors (DSPs) optimized for multiply-accumulate (MAC) operations with wide bit-widths in deep learning models. Compared to the higher abstraction in CPU and GPU programming, arithmetic operations with these blocks reduce instruction overhead and enable more granular control over data flow. Look-up tables (LUTs) and, sometimes, fast carry chains allow implementing MAC operations without the need for dedicated multiplier blocks like DSPs, either by shift-and-add operations, such as the Booth multiplication algorithm [16], or by table look-ups for small bit-width multiplications. Recent works [10, 120] propose training neural networks that can be mapped directly to FPGA LUTs, often achieving high operating frequencies and low resource usage with minimal accuracy loss.

Compared to the commonly used floating-point precisions on CPUs and GPUs, FPGA designs typically represent variables in fixed-precision with lower bit-width. Quantizing a model trained with full precision to lower bit-widths with no or little retraining is known as post-training quantization (PTQ). Higher degrees of quantization can be achieved while maintaining accuracy by training the model directly with the intended bit-width, a technique known as quantization-aware training (QAT). Quantization is a method particularly suited for FPGA acceleration, as the arbitrary-precision operation can be efficiently mapped to low-level logic elements in hardware. Examples of quantization Manuscript submitted to ACM

for FPGAs include heterogeneously quantized models [20, 31], as well as binary and ternary models [85, 120, 131]. Additionally, models can also be compressed by pruning parameters, setting some weights or activations to zero. The level of pruning is selected to balance model size with an acceptable inference accuracy loss [22, 93]. On FPGAs, pruning can be structured to be compatible with the low-level hardware implementation [98].

Traditionally, register-transfer level (RTL) design in languages such as VHDL, (System)Verilog, or Chisel have been used to program FPGAs. While allowing for more granular control, producing designs in this way is usually more challenging and comes with a steep learning curve. *High-level synthesis* (HLS) abstracts FPGA programming significantly by compiling high-level C/C++ or SystemC code into RTL code for specific target hardware using an *HLS compiler*, such as VITIS HLS or CATAPULT HLS. Preprocessor directives, or so-called *pragmas*, are used to guide the compiler in the hardware implementation of the design. This significantly reduces the difficulty of implementing complex designs for ML inference. While this approach sacrifices some direct control over exact implementations, HLS has been shown to achieve performance on par with hand-written RTL designs [72, 73] for neural networks (Section 9.6).

#### 3 Overview

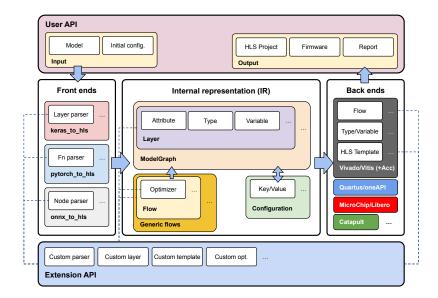

To achieve high performance, high portability, and easy extensions in the fast-moving field of ML, HLS4ML is structured in a modular fashion, mimicking modern compilers. HLS4ML includes a set of *front ends*, which parse high-level models into an internal representation (IR), a set of *optimizer passes*, which optimize the model graph for the target hardware, and a set of *back ends*, which create high-performance IPs for different flavors of HLS targeting FPGAs from different vendors. Additionally, it includes a rich set of features for model simulation and hardware validation on FPGAs/SoCs.

The flow from the initial model to the FPGA IP is illustrated in Figure 1. The users provide a trained model and a configuration file that specifies options such as parallelization factors, variable precisions, and target clock period, which are then parsed by the front-end parsers.<sup>2</sup> Generally, HLS4ML supports fixed-point, exponential, ternary, and binary data types. In the case of PTQ, variable quantization is determined by the precision set in the user configuration, and in the case of QAT, it is automatically inferred from the quantized model (e.g., from QKERAS, QONNX). Following that, the model graph is iteratively optimized and refined, given the user configuration and the target back end. Finally, an FPGA/HLS project containing the generated HLS code and the supporting scripts for simulation, synthesis, and deployment is returned to the user.

HLS4ML supports all major deep learning frameworks through dedicated front ends for Keras, PyTorch, and ONNX. Additionally, HLS4ML is able to process quantized models from these frameworks; namely models implemented in QKeras, HGQ, Brevitas, and QONNX. We describe the front ends in more detail in Section 4. On the back-end side, HLS4ML keeps the same design principles of modularity and extendability. Currently available are the *Vitis* and *Vivado* back ends for Vitis HLS, and its deprecated counterpart Vivado HLS, for AMD/Xilinx FPGAs, the *oneAPI* and *Quartus* back ends for oneAPI, and its deprecated counterpart Intel HLS, for Intel/Altera FPGAs, and the *Catapult* back end for Catapult HLS, targeting the Siemens EDA flow. These back ends are discussed in more detail in Section 6. To translate between the different front and back ends, HLS4ML converts the model into an IR. The IR initially replicates the structure of the model before a set of optimizers modifies it to better suit the hardware architecture and performance requirements. The IR and optimizers are described in more detail in Section 5. Following a similar modular approach, HLS4ML implements a library of HLS kernel templates, each implementing the functionality of a model layer or parts thereof. Here, each back end has its own set of templates, which is hand-optimized for the target HLS compiler. To

$<sup>^2</sup>$ For more information on the configuration parameters and commands to run these steps, see https://fastmachinelearning.org/hls4ml/api/configuration.html and https://fastmachinelearning.org/hls4ml/intro/setup.html.

Fig. 1. Model conversion and compilation flow in HLS4ML.

allow greater flexibility and design space exploration different templates are often available that minimize either latency or resources. The user has full control over which of these configurations is used and can also control the degree of parallelism and variable precisions, both of which can be set on a per-layer basis.

Finally, it is important to note that public releases of HLS4ML support most types of commonly used neural networks. MLPs and CNNs are fully supported in all front and back ends. RNNs are also supported, though currently not in the ONNX front end. While some graph neural networks (GNNs) have been realized using HLS4ML [65, 86, 95], support for generic GNNs is currently still in development. Specifically, no support for any PyTorch Geometric functionality is currently available. Support for multi-head attention (MHA) transformer models has been introduced in HLS4ML v1.2.0 via the HGQ 2 front end and is currently only available in the Vitis back end. A detailed overview of the availability of common operators is given in Tables 1 and 2. In addition, HLS4ML supports a large number of activation functions, such as ReLU or softmax, as well as general tensor operations (e.g. reshaping, concatenation, or addition). Even though many layers are supported, a model may not necessarily be suitable for acceleration with HLS4ML. Very large or complex models can fail to pass HLS compilation due to the on-chip, low-latency dataflow implementation of HLS4ML designs which can lead to high resource utilization and congestion (more details on the limitation of HLS4ML can be found in Section 11). Such models should be compressed through quantization and pruning, or, in some cases, consider alternative acceleration techniques, leveraging for e.g., overlay architectures or off-chip memory. If a model contains currently unavailable operations/layers, HLS4ML offers an Extension API to add support for additional layers (Section 8), while still relying on the implementations for existing layers, optimizers, and scripts.

## 4 Front ends for different ML libraries

The front end converts models from the supported frameworks mentioned above into the IR. For each deep learning framework, there is a dedicated front end that (1) parses the model graph, and (2) extracts relevant information from each individual layer or operation. The second step is implemented with an extensive repository of layer handlers, one Manuscript submitted to ACM

Table 1. Support for different NN layers or types in the HLS4ML front ends. Support is indicated by **☑**, while not supported layers are marked □. Layers not supported in the respective NN frameworks are marked −.

| T                          |         |            |            | Froi       | nt end     |            |            |            |

|----------------------------|---------|------------|------------|------------|------------|------------|------------|------------|

| Layer                      | Keras 2 | QKeras     | HGQ        | Keras 3    | HGQ 2      | РуТоксн    | ONNX       | QONNX      |

| Linear/Dense               |         | lacksquare |

| 1D/2D Convolution          |         | lacksquare |            |            |            |            |            | lacksquare |

| LSTM/GRU                   |         | lacksquare | _          |            | _          |            |            |            |

| Einsum                     |         | _          | _          |            |            |            |            | _          |

| Multihead Attention        |         | _          | _          |            |            |            |            | _          |

| <b>Batch Normalization</b> |         |            |            |            |            | lacksquare |            | lacksquare |

| Layer Normalization        |         |            |            |            |            | lacksquare |            |            |

| GNN                        |         |            |            |            |            |            |            |            |

Table 2. Support for different layers in the нLs4мL back ends. Support is indicated by 🗹, while not supported layers are marked 🗅.

| T                          |              | Back end       |          |

|----------------------------|--------------|----------------|----------|

| Layer                      | Vitis/Vivado | Quartus/oneAPI | Catapult |

| Linear/Dense               | <b>☑</b>     | <b>☑</b>       |          |

| 1D/2D Convolution          |              |                |          |

| LSTM/GRU                   |              |                |          |

| Einsum                     |              |                |          |

| Multihead Attention        |              |                |          |

| <b>Batch Normalization</b> |              |                |          |

| Layer Normalization        |              |                |          |

| GNN                        |              |                |          |

for an individual, or a family of supported layers or operations. Each layer handler accepts a layer object and returns a dictionary with the necessary configuration and data for representing the layer in HLS4ML's IR. All weights in the model are converted to NumPy arrays at this stage, and front-end specific objects are eliminated for compatibility.

## 4.1 Keras

Traditionally, HLS4ML has focused on models created in Keras 2 and supports the most commonly used layers in this framework. For Keras 2, both Keras objects and serialized representations of the model, which contain detailed information about the model architecture and layer configurations, are accepted. This allows the conversion of models that are saved in the HDF5 format without requiring the Keras library to be installed. Direct parsing of .keras files is not supported due to the absence of a public API for reading model configurations. However, such models can be loaded in Keras and passed to HLS4ML as in-memory objects. Keras 3 introduces major changes to the Keras library. Therefore, the Keras 3 parser does not inherit from the Keras 2 parser. The Keras 3 parser directly ingests a keras .api .Model object, and reconstructs the model architecture via data dependency solving. Keras 3 layer handlers also ingest keras .api .layers.Layer objects directly, and return a dictionary with the layer configuration and weights. When a layer type is not supported, the parser will attempt to fall back to the Keras 2 layer handler (if available) to extract the configuration.

The Keras 2 parser supports models quantized by two different QAT libraries, QKeras and HGQ, while the Keras 3 parser currently only supports HGQ. For quantized layer types, the quantization parameters are included in the IR of the quantized layer configuration. Quantization parameters derived from QAT libraries are enforced in HLS4ML and will

Manuscript submitted to ACM

override any user-provided configurations. QKeras supports three major quantization types: fixed-point integer based, binary, and power-of-two quantization, of which are all supported by HLS4ML, while the power-of-two quantization may only be used for the weights. For HGQ models, a dedicated optimizer pass in the IR is invoked for precision configuration. This involves symbolic precision propagation through the model, and all quantization parameters are derived from explicit quantization layers converted from HGQ, along with the weights provided. User-provided precision configurations are discarded when converting from HGQ, and conversions from properly defined HGQ models are always bit-exact up to the floating point representation limits.

#### 4.2 PyTorch

Symbolic tracing in the TORCH FX framework is used to infer the architecture and configuration of PyTorch models. In general, HLS4ML supports operations implemented as both torch.nn.Module objects and stateless operators in the torch.nn.functional module. The support for PyTorch layers generally matches that of Keras 2. A custom tracer inheriting from the Torch.fx.Tracer class is used to enable the parsing of custom layers in the Extension API (Section 8). Since HLS4ML was first developed to support Keras 2 models, which adopts the "channels-last" convention for multi-dimensional tensors, many HLS kernel templates only have a "channels-last" version implemented. PyTorch uses the "channels-first" convention in most of its operations. Therefore, an optimizer adds the necessary transpose operations to the HLS4ML IR to ensure compatibility with the "channels-last" convention.

Models trained using QAT in Brevitas can be converted to the QONNX format using the Brevitas-ONNX export functionality, allowing them to be ingested by the ONNX front end described below. This approach is also common in other frameworks [15, 122]. In addition, support for direct parsing of Brevitas models, without reliance on QONNX, as part of the PyTorch front end is in development.

#### 4.3 ONNX

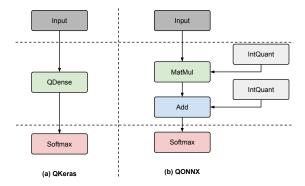

ONNX models are supported with direct object parsing. The converter ingests an ONNX object and parses its graph to determine the model inputs, outputs, and all operators present in the model. Because of the fine-grained representation of operators in ONNX models, hls4ml requires the model to be preprocessed, usually referred to as "cleaning", before conversion. Cleaning is performed using the QONNX [121] package, which performs constant folding, shape inference, renaming of the nodes into human-readable names, and conversion of the graph into the "channels-last" convention. Additionally, QONNX, as an extension of the ONNX library, introduces three new operators: QUANT, BIPOLARQUANT, and Trunc to enable flexible representation of quantized models. Hls4ml supports a subset of models representable by QONNX that are physically feasible for FPGA implementation. In the hls4ml IR, the precision is derived from the quantization operators and enforced. Additional scaling or unscaling is applied as needed. Figure 2 illustrates a QONNX representation of a simple one-layer MLP with a softmax output layer, compared to the representation in QKeras.

## 5 Internal representation and optimizer flows

#### 5.1 Internal Representation

The HLS4ML IR aims to provide a front- and back-end agnostic representation of models. By abstracting models from different frameworks into a uniform representation, HLS4ML can apply transformations and optimizations to a model independent of the framework used to create it. The IR is implemented as a ModelGraph object where each node corresponds to a layer or operator in the network. Each node contains all layer-specific information such as operation Manuscript submitted to ACM

Fig. 2. Comparison of the representation of an example model consisting of a one-layer MLP with a softmax output layer in QKERAS (left) and QONNX (right).

type, weights, quantization method, and connections to other nodes. During conversion, the IR is initialized with the layers from the original model by the front-end converter. Then, the IR undergoes a series of transformations performed by the *optimizer flows* to reach the final state used in the code generation of the target back end.

By default, HLS4ML creates a single HLS project for the entire model, which is then synthesized into a monolithic design. As of v1.2.0, HLS4ML supports a new feature that allows for the splitting of the model into multiple subgraphs. This is implemented by extending the ModelGraph with the MultiModelGraph object, which splits the model at user-defined layers, and creates independent HLS projects that can be synthesized independently. This allows for parallel synthesis to reduce synthesis time, or potentially distributing large models over multiple chips or devices in the future. HLS4ML currently supports automatic stitching of the synthesized IP cores from subgraphs into a single design for the Vivado/Vitis back ends. By running the individual synthesis in parallel, the HLS synthesis time for a quantized ResNet for CIFAR-10 classification decreases from 7 h to 3 h on average.

## 5.2 Optimizer flows

Inspired by modern compilers, HLS4ML implements a series of transformations, called *optimizer flows*, that iteratively transform the IR for the target back ends, where each flow represents a distinct optimization stage. Optimizer flows can either be generally applicable to all models or specific to a target back end. A single flow implements multiple *optimizers*, each performing a specific transformation on the model, such as precision propagation, template instantiation, or removing redundant operations. For instance, an optimizer may fuse batch normalizations that immediately follow an affine projection (fully connected or convolutional layers) operation into a single node with equivalent, fused weights when both nodes are not quantized.

## 5.3 User directives

In addition to the graph representation of the model itself, the ModelGraph object also holds directives regarding the model conversion and optimization process in the form of an HLSConfig object. The HLSConfig object contains information that cannot be derived directly from the model, such as the target back end, implementation strategy, I/O type, and, in some cases, quantization precision and resource reuse preferences. Users provide these configurations as

a Python dictionary. Some of the hardware-oriented configurations (e.g., I/O type, strategy) are further discussed in Section 6.1, in conjunction with the hardware implementation of neural network kernels.

Quantization parameters are a crucial part of the model conversion process. Improperly configured quantization parameters may introduce extra errors that accumulate throughout the model, which can lead to significant performance degradation. Currently, HLS4ML supports fixed-point, exponential (power-of-two), ternary, and binary data types. When the front-end framework quantizes the model properly, the quantization parameters will be stored directly in the nodes. However, some precision information may not always be available depending on the front end used. For instance, the accumulator<sup>3</sup> precision is rarely available from the front-end libraries. Since v1.0.0, HLS4ML is able to automatically determine it through conservative estimation to avoid unwanted overflows when the user specifies "auto" for the accumulator precision in the configuration. Other precision types, such as the weight, bias, and result precision, can also be inferred automatically, depending on the layer type and the metadata it contains when "auto" is specified. Since v1.2.0, HLS4ML includes a dedicated optimizer pass that propagates precision at the model level for bit-exactness when the model is fully quantized, which relies only on explicitly defined quantizers and the weights provided through interval arithmetic. User-supplied precision configurations are ignored when this optimizer pass is enabled.

## 6 Back ends and hardware implementations

HLS4ML generates HLS code through a set of manually optimized templates for different layers and operations, which are combined to represent a complete model to be synthesized. Each back end includes a set of dedicated templates and optimizers. Some back ends, such as those for VIVADO HLS and VITIS HLS, may share some templates and optimizers because of their similarity. The optimizers will register the back-end specific templates and apply them to the IR. They also perform back-end specific optimizations, such as pragma insertion, precision propagation, constant folding, and others. When creating an HLS project, the back ends will also generate the necessary utility files such as TCL scripts for synthesizing the project, test benches, and bridge code for calling the generated libraries directly from high-level Python functions. After synthesizing the generated HLS code, the back ends can parse the synthesis reports and display a concise summary of the resource usage and latency.

## 6.1 Hardware implementations

In the following, we provide a brief overview of hardware implementations in HLS4ML, with an emphasis on constant matrix-vector multipliers (CMVM) and activations, with are core building blocks of neural networks. Further details on specific layer implementations can be found in the corresponding publications for MLPs [41], CNNs [2, 48] and RNNs [1, 75]. In addition, we discuss the various strategies and data flow options supported in HLS4ML, each of which provides a trade-off between the resources used and inference latency.

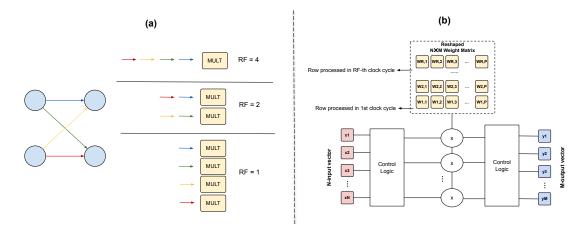

Constant matrix-vector multiplication, strategies, and parallelism: The CMVM operation is a fundamental building block of neural networks. HLS4ML places significant emphasis on its efficient implementations, with three supported strategies: Latency, Resource, and Distributed Arithmetic. To control the degree of parallelism, HLS4ML allows users to set the Reuse Factor (RF). Given a weight matrix of size  $M \times N$  and a reuse factor RF, HLS4ML implementations of CMVM are such that there are no more than  $N_{-}MULT = \frac{M \cdot N}{RF}$  multiplications per clock cycle (e.g., Fig. 3a). Different strategies will differently impact latency and resource consumption of a layer, and users are advised to choose based on their design goals. The availability of a particular strategy for a layer varies across back ends.

$<sup>^3{\</sup>rm The}$  accumulator holds the intermediate results in a layer for the MAC operations.

The *Latency* strategy implements fully unrolled CMVM with weights directly embedded into multiplier circuits, allowing the HLS compiler to perform intensive optimizations, such as removing multiplications with zeros, replacing multiplications with specific constants with shift-and-add operations, or reordering the multiplications to improve timing. The RF is implemented as a compiler directive that limits the number of parallel multiplications and determines the initiation interval of the CMVM operation. The HLS compiler determines the exact ordering and hardware primitive for the MAC operations, based on the data type, precision, and other conditions (e.g. target hardware and frequency). In cases where DSP blocks or other hardened multipliers are used for the MAC operations, a larger RF will usually result in reusing those blocks and lower resource consumption. However, when MAC operations are implemented in fabric, such as LUTs and fast carriers with shift-and-addition operations, a higher RF will not necessarily result in resource reduction, but will still increase the II. Depending on the underlying compiler and hardware mappings, the resource usage may even increase. Therefore, the Latency strategy is suitable for small models, targeting very low inference latencies. Additionally, the RF should be tuned carefully as it may not yield resource savings and may increase II.

In the *Resource* strategy, the CMVM implementation stores the weights in BRAM and explicitly controls the degree of parallelism in by specifying the number of MAC operations performed in parallel per clock cycle (Fig. 3a). Weights stored in BRAM are partitioned into *RF* blocks, each of size *N\_MULT* (Fig. 3b). Each clock cycle, a slice of *N\_MULT* weights is accessed and processed together with the inputs by a MAC unit, leading to an II of *RF* clock cycles. Depending on the chunk size *N\_MULT*, the weights may be stored in multiple BRAMs to increase the number of ports for parallel read. The exact implementation of the MAC unit will depend on the bit-width of the weights and inputs, as well as compiler heuristics. In the case of DSP-based MAC units, it can be implemented as cascaded DSP tiles, whereas for LUT-based MAC units, the exact implementation differs heavily depending on the precisions, target frequency and other factors. However, for specific operand types, HLS4ML can overwrite compiler primitives; for e.g. multiplications with power-of-two weights can be implemented using shifters explicitly, while multiplications with binary and ternary weights can be realized with AND and XOR gates. Increasing the RF in the Resource strategy directly reduces the number of MAC units used, thus reducing resource consumption. The Resource strategy is better suited for large models, since the Latency strategy can fail to compile in these cases due to full loop unrolling. However, due to the overhead in data movement and the use of general MAC units, the end-to-end latency for the Resource strategy is typically higher than for the Latency strategy with the same RF.

The Distributed Arithmetic (DA) strategy implements the CMVM operation by explicitly decomposing it into an adder graph with only shift-and-add (or subtract) operations, where any bit-wise sparsity in the weights will be explicitly exploited. This strategy relies on an external library, DA4ML [113], for generating and optimizing the adder graph corresponding to the specific CMVM problems. Compared to the Latency strategy with an RF of one, the DA strategy usually has lower fabric resource utilization and latency. DSPs or other hardened multipliers will not be used due to the lack of explicit multiplications. However, the DA strategy in general does not support RFs greater than one since the generated adder graph effectively unrolls the entire CMVM operation. Hence, in case of moderately large CMVM problems consuming significant amount of hardened multipliers (e.g., DSPs), the user is encouraged to try the Latency or Resource strategy with a higher RF instead of the DA strategy.

Some layers, e.g., convolutional layers lowered to CMVM through the im2col [21] transformation, may perform identical CMVM operations multiple times on different inputs in one forward pass. In this case, the parallelism between CMVM operations is controlled by the *Parallelization Factor* (PF). The PF controls the number of CMVM operations that are performed in parallel, and it is independent of the strategy and RF used for the CMVM operation. A higher PF reduces the II of one layer at the expense of higher resource usage. Like RF in the Resource strategy, the PF chosen Manuscript submitted to ACM

Fig. 3. (a) Illustration of the effect of different RF values for the outer product of two two-vectors. (b) Example CMVM in HLS4ML with the Resource strategy. Given a linear layer with N inputs, M outputs and reuse factor RF, there will be  $P = \frac{M \cdot N}{RF}$  multipliers operating in parallel. In each clock cycle, the control logic selects P out of the N inputs and feeds them to the multipliers, with wrap around if P > N. The  $N \times M$  kernel is reshaped and mapped to on-chip memories such that P elements can be accessed in parallel in each clock cycle. The products are accumulated accordingly at the precision specified to form the output.

must fully divide the number of CMVM operations needed in one forward pass for the layer to avoid any remainder. The total II of one layer is determined by the PF (if available), RF, and strategy together.

Activations: Piecewise linear activations (e.g., ReLU, Leaky ReLU) are implemented using multiplexers. Other activations (e.g., tanh, sigmoid) are implemented as lookup tables<sup>4</sup>, which are populated at compile-time. The use of look-up tables guarantees constant and efficient calculation of the activation, regardless of its complexity. Given the precision of the layer input, hls4ml will generate a look-up table storing all possible output values of the activation function for each possible input value. In case the user-specified table size is smaller than the generated table, HLS4mL will drop the least significant bits from the input to fit the table size. Depending on the table size and the precision, look-up tables can be implemented as BRAM or LUTRAM, which is determined by the HLS compiler. For example, on AMD FPGAs, BRAM can be implemented as 18 bit wide by 1024 bit deep true dual-port RAM. Since the variable precision rarely exceeds 18 bits, one BRAM is used for each table of 1,024 elements. In the case of parallel accesses, the HLS compiler may duplicate the BRAM to ensure single-clock-cycle access. Empirically, we determine that activation look-up tables consume a small amount of resources and that most activations can be sufficiently approximated with a modest look-up table of ~2048 entries; though heavily quantized models may use even smaller look up tables.

Data flow, scheduling and I/O types: Models deployed with HLS4ML target dataflow architectures, in which each operation is mapped to a dedicated hardware function synthesized into a separate region of the FPGA fabric. This approach enables pipeline parallelism across the computation graph allowing for low latency and high throughput. In general, dataflow is achieved through directives such as the #pragma HLS dataflow in VITIS HLS or tasks in ONEAPI. The exact scheduling of layers and data movement between them is, however, determined by the HLS compiler and depends on a number of factors, including the target FPGA platform, clock frequency/uncertainty, and model size. For

<sup>&</sup>lt;sup>4</sup>Not to be confused with the LUT primitive on FPGAs.

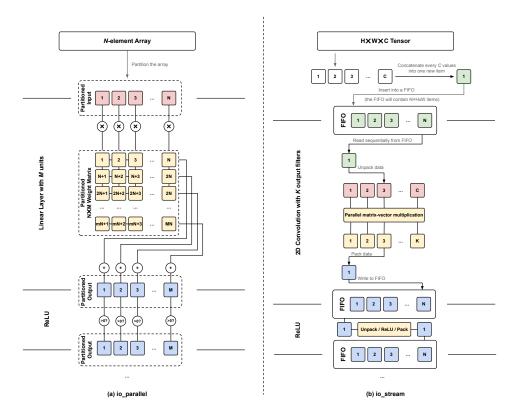

Fig. 4. Schematics of the computation of an MLP model implemented using parallel data transfer (left) and a CNN model implemented using streaming data transfer (right). In the Resource strategy, the number of parallel MAC operations executed in each cycle is determined by the RF and PF. In the case of the MLP,  $\frac{M \cdot N}{RF}$  multiplications are executed in parallel each clock cycle.

example, increasing the clock frequency will often lead to higher latency, since the HLS compiler automatically inserts more pipeline stages to better achieve timing closure during place and route.

The data flow between layers is a crucial part of the design. HLS4ML supports two types of data transfer between layers: io\_parallel and io\_stream (example in Figure 4). The io\_parallel setting directly wires the output of one layer to the input of the next layer, allowing for maximum throughput and minimum latency. This is the default data transfer type for HLS4ML, which is suitable for small models with moderate resource usage. On the other hand, io\_stream uses FIFO buffers between layers. This is typically used with larger models where some layer requires a significant II, and the data processed by the previous layer need to be buffered before being consumed by the next layer. Depending on the buffer depth, the HLS compiler may elect to use shift registers or BRAM to implement the FIFOs. By default, HLS4ML uses a conservative depth for these buffers, which can result in unnecessary resource overheads. In the Vivado and Vitis back ends, a special optimizer is implemented to optimize the depth of these FIFOs by performing an RTL co-simulation of the model and recording the maximum occupation of each FIFO buffer [17]. The optimizer then sets the final depth for each FIFO to the maximum occupation plus one.

#### 6.2 IP Core back ends

Currently, HLS4ML provides five back ends supporting HLS compilers from AMD/Xilinx, Intel/Altera, and Siemens EDA. There are two back ends for AMD/Xilinx FPGAs: the Vivado back end, targeting the discontinued VIVADO HLS, and the Vitis back end, targeting VITIS HLS 2022.2 or newer. These two back ends are best supported with the most complete feature set. They support the most layer types, including fully connected (dense), convolutional, recurrent, many activations, and Einstein summation layers. Both io\_parallel and io\_stream are supported. All strategies for the CMVM operation are supported, including Latency, Resource, and Distributed Arithmetic. Due to their popularity, many optimized layers exist for special configurations, such as pointwise, depthwise, and separable convolutions.

Similarly, there are two related back ends for Intel/Altera FPGAs: the Quartus back end, targeting the discontinued Intel HLS, and the oneAPI back end, targeting oneAPI 2025.0<sup>5</sup>. Both io\_parallel and io\_stream are supported in these back ends. In the streaming implementations, the oneAPI back end follows the data flow architecture more closely than the Quartus back end, where individual layers run independently as separate tasks, with handshaking and data transfers between tasks done through the streams implemented as pipes. Unlike Vivado/Vitis back ends, the Quartus and oneAPI back ends do not provide distinct strategy implementations for the CMVM operations and generally use a resource-optimized approach.

HLS4ML also provides a back end for CATAPULT HLS, developed in collaboration with Siemens EDA and guided by evolving industry requirements for edge ML applications. CATAPULT HLS is widely used for the development of ASICs, while also supporting FPGA designs, making it a versatile solution for synthesizing C++/SystemC specifications across various hardware targets. Both Latency and Resource strategies are supported, and the io\_type can be configured as either io\_parallel or io\_stream. For streaming implementations, the Catapult back end supports bottom-up synthesis, leveraging Catapult's Bottom-Up (BUP) flow to enable hierarchical and scalable hardware generation. This methodology enables individual model layers to be synthesized independently without requiring the entire model to be available. Each layer is synthesized into a separate RTL implementation and reusable Catapult library component. This divide-and-conquer approach simplifies design management, supports incremental synthesis (e.g., eliminating the need to re-synthesize the whole model when modifying a single layer), and enhances scalability by reducing memory requirements on the synthesis servers.

#### 6.3 Accelerator back ends

The accelerator back ends are extensions of the IP core back ends, which enable end-to-end design-to-deployment flows for specific FPGA/SoC platforms. The accelerator extensions are available for the Vivado and Vitis back ends, with oneAPI currently under development. The Vivado accelerator back end embeds the generated IP core into a larger design containing an DMA core and other necessary utilities for host communication. Beyond IP integration, the back end also facilitates communication between the IP core and a system's memory controller unit (MCU) or the host CPU via a custom device driver. Two different Vitis accelerator back ends are currently being integrated into HLS4ML. The first uses the *Vitis IP flow*, which closely resembles the Vivado accelerator back end in functionality, primarily targeting the AMD/Xilinx Zynq boards. The second one utilizes the *Vitis System Design Flow*, which enables the creation of complete applications targeting datacenter AMD/Xilinx Alveo accelerators. In this case, the accelerator back end generates a Vitis IP kernel along with a wrapper to facilitate data transfers between the accelerator and the host CPU. This approach allows compiling one or multiple instances of the resulting IP into a binary file that can be directly loaded

$<sup>^5</sup>$ Support for Altera FPGAs was dropped from ONEAPI version 2025.1, to be replaced by dedicated Altera software. Manuscript submitted to ACM

onto the accelerator card from the host. Additionally, the back end produces multi-threaded host code to manage kernel execution and optimize data movement. This setup enables overlapping PCIe data transfers with kernel computation, effectively multiplexing communication and processing. In practice, this approach has achieved core occupancy levels of up to 96 % of the theoretical throughput, as estimated from the II and the kernel's operating frequency. Multi-kernel and multi-accelerator configurations have demonstrated throughput exceeding 1.4 million inferences per second. HLS4ML's generic design and interfaces are showcased by its integration with other FPGA shells, such as Coyote v2 [97], which also allows seamless deployment of applications on Alveo boards.

## 7 Community tools for model optimization and co-design

With the growing need for higher performance and accuracy, machine learning has shifted towards techniques such as quantization and pruning to efficiently deploy models on a variety of hardware. Such techniques can also be *hardware-aware*, in which the quantization precision or sparsity pattern is determined by the specific computation or memory model of the target device. Model-hardware co-design often yields the best performance with the lowest drop in accuracy. Following this trend, the community has proposed a growing number of co-design tools. We introduce some tools proposed by the community that are supported by HLS4ML.

## 7.1 QKeras

QKERAS is a widely used QAT library built on top of KERAS 2, developed by Google in collaboration with some of the HLS4ML authors [30]. QKERAS was the first QAT framework to be natively supported in HLS4ML. The library supports three quantization types: fixed-point integer, binary, and power-of-two quantization, and provides drop-in replacements for many KERAS 2 layers with the corresponding quantized version. To define a quantized model with QKERAS, one needs to replace the corresponding Keras layer with the corresponding QKERAS counterpart (e.g., Conv2D—QConv2D, Dense—QDense), and specify the target quantization type and precision. AutoQKeras, a hyperparameter tuning tool, may be used to automatically search for the best quantization precision for each layer in the model given a set of constraints on the model size, latency, and accuracy [30]. QKERAS has been adopted by various applications, including image classification with quantized CNNs [2], ternary neural networks for network traffic filtering [61], low-precision models for jet tagging at the Large Hadron Collider (LHC) [30, 86], and muon tracking [111].

## 7.2 High-granularity quantization

High-granularity quantization (HGQ) [20] is a QAT library built on top of Keras that applies differentiable quantization to weights and activations at a sub-layer granularity. For models with unrolled CMVM operations, quantization granularity down to the per-parameter level can be used to exploit the FPGA's fine-grained parallelism. HGQ supports only fixed-point integer quantization, treating both binary and power-of-two quantization as special cases of the 1-bit quantization. Allowing learnable bit-widths to reach 0 bits automatically includes pruning as a special case of quantization. HGQ provides an accurate and differentiable resource usage estimation for the quantized model in the form of effective bit operations (EBOPs), a proxy for computational effort. This metric is used as a regularization term in the loss function, controlled by a hyperparameter  $\beta$ , which allows the user to control the trade-off between accuracy and resource usage during training. On models with unrolled CMVM operations, HGQ demonstrates significant advantages over other model compression techniques, with an on-chip LUT usage reduction of 50% to 95%, DSP usage reduction of 50% to 100%, and a latency reduction up to 80% with no inference performance degradation [20, 112]. There are two

versions of HGQ: HGQ 1 based on Keras 2, and HGQ 2 based on Keras 3. Both libraries are tightly integrated with HLS4ML, and no user intervention is required to generate bit-exact HLS designs from the quantized models.

#### 7.3 Distributed arithmetic

Distributed arithmetic is a technique for implementing fixed-point multipliers in hardware via shift-and-add operations. DA4ML [113] is a library that implements CMVM operations with an adder graph structure. The adder graph in DA4ML is optimized by a set of heuristics to minimize the number of adders weighted by their bit-width, including common sub-expression elimination (CSE). DA4ML targets unrolled CMVM operations, which constitute the dominant on-chip resource consumption for latency-critical models generated by HLS4ML. In contrast to other optimization techniques, DA4ML is an algorithm transformation at implementation time, usually taking only a few seconds, which does not change the model's output by a single bit relative to the corresponding fixed-point implementation. When applied to models trained with HGQ, DA4ML can achieve further LUT usage reduction of up to ~ 1/3 depending on the specific model, while completely eliminating the DSP usage [20, 113].

For some models that require the unrolling of large loops, especially of those contain many multiplication by zero, the HLS code generated directly with HLS4ML may be unsynthesizable, depending on the HLS compiler. They may, however, be synthesized with DA4ML [95, 112] due to its explicit loop unrolling and resource reduction. For each CMVM operation implemented with DA4ML, an accurate estimate of LUT usage is also provided. The DA4ML library is tightly integrated with HLS4ML, and setting the layer strategy to "distributed\_arithmetic" in the HLS4ML configuration will enable the distributed arithmetic implementation for the corresponding layers.

## 7.4 DSP- and BRAM-aware pruning

Model pruning is an effective way to reduce the resource utilization of a model. However, the benefit of unstructured pruning is limited for designs where the multipliers are reused, and it is necessary to prune the weights in an organized manner aligned to the specific on-chip primitives used. The DSP- and BRAM-aware pruning algorithm [98] is implemented in a submodule of HLS4ML based on QKERAS with objectives constructed directly corresponding to reductions in on-chip primitive usage. In each case, the algorithm solves a Knapsack problem where weights in the model are assigned an importance value and a hardware cost. Given a certain resource capacity, the algorithm identifies which weights to prune. As a basic objective, the model can be optimized for sparsity itself in an unstructured approach. However, for a more structured approach, hardware-specific metrics are available. For FPGAs, these can be registers, DSPs, BRAM, or all of them simultaneously. For instance, all weights processed by a single DSP can be grouped and pruned together, and hence a DSP block can be removed from the design once a group of weights is pruned. Depending on the specific application, reductions in DSP usage by factors ranging from 2.2× to 12.2× and BRAM usage reductions by factors ranging from 1.4× to 5.2× with minimal accuracy degradation have been demonstrated [98].

## 7.5 Symbolic expression

HLS4ML includes a symbolic regression (SR) interface for creating HLS designs based on analytic expressions. SR aims to find a closed-form mathematical expression, containing operators such as  $\exp(\cdot)$ ,  $\sin(\cdot)$ ,  $\cos(\cdot)$ , that describe the mapping between given input and output data. These expressions can be efficiently implemented in hardware, especially if the functions are approximated with look-up tables, making them suitable for low-latency applications. Support for building efficient IPs implementing SR models is included in HLS4ML on top of the Vivado/Vitis back ends, leveraging the built-in code generation functionality. Specifically, the SR back end supports the translation of expressions represented Manuscript submitted to ACM

as strings or SymPy objects, obtained through tools like PYSR [34] or SymbolNet [118]. The functions within expressions can be implemented either using the native Xilinx HLS math library or approximated via LUTs, giving users an option to find the desired balance between accuracy, resource usage, and latency.

## 7.6 Surrogate models

The rapid generation of HLS designs for various models with different hardware configurations opens up the possibility of systematic studies of the design space. However, waiting for HLS synthesis results is often impractical and lengthy. An alternative is to use surrogate models, which can accurately predict the model resource utilization and latency. This can assist in making design choices by providing fast and accurate hardware resource estimates for different model parameter choices. One example is RULE4ML [96], an open-source tool that uses an MLP surrogate model to predict the resource usage of MLPs generated with HLS4ML. Trained on over 15,000 HLS synthesis results covering a wide range of MLP parameter space and HLS4ML design configurations, it achieves predictions within 10% of the true synthesis results in ~80% of test cases. In a related approach, wa-hls4ML, over 100,000 models were generated, and a graph neural network, lui-GNN, was trained as the surrogate model [58].

## 7.7 Automated neural architecture and hardware co-design

Neural architecture co-design (NAC) [134] is a pipeline for neural architecture search and network compression in a two-stage approach based on the "Once-for-All" paradigm [19] to discover hardware efficient models. This approach consists of a global search stage that explores a wide range of architectures while considering hardware constraints, followed by a local search stage that fine-tunes and compresses the most promising candidates through QAT and pruning. Currently, the hardware cost is quantified using bit operations (BOPs), but integration of HLS4ML resource and latency estimates is underway. NAC has been demonstrated with Bragg peak finding in materials science and jet classification in HEP, achieving models with improved accuracy, smaller latencies, or reduced resource utilization.

A recent advancement in this direction is MetaML-Pro [93], a co-optimization framework that automates design space exploration across neural network and hardware abstraction levels. It supports reusable optimization tasks, such as pruning, quantization, and scaling, and enables top-down and bottom-up information flow between software and hardware stages. By integrating tools like HLS4ML and leveraging Bayesian optimization, MetaML-Pro efficiently balances latency, accuracy, and resource usage, and has been demonstrated on jet tagging models for HEP. Complementary to MetaML-Pro, another recent framework extends co-design principles to incorporate trustworthiness by optimizing not only for accuracy and efficiency but also for uncertainty estimation [94]. It introduces Bayesian CNNs with Monte Carlo Dropout and automates trade-offs among predictive accuracy, computational cost, and model calibration, supporting use cases such as safety-critical inference on FPGAs.

## 7.8 SoC integration

The Embedded Scalable Platform (ESP) is an open-source research framework for designing and prototyping heterogeneous system-on-chip (SoC) architectures using a modular, tile-based approach [78]. It supports the automated integration of hardware accelerators, processors, memory tiles, and I/O components into an RTL SoC design. ESP integrates with HLS4ML to enable end-to-end deployment of machine learning models as hardware accelerators [51]. After HLS4ML generates a synthesizable hardware block from a neural network, ESP wraps it with standard interfaces and connects it to the rest of the SoC, automatically generating testbenches, drivers, and software applications for

verification and experimentation. This combined workflow enables the design from a high-level ML model to complete system-level ASIC implementation. FPGA-based emulation and validation are also supported.

#### 8 User-defined functionality

While HLS4ML supports a wide range of neural networks from a variety of libraries, users may wish to include custom operations in their designs. For layers that are not natively supported by HLS4ML, users need to provide their own HLS implementation. If these are of wider interest to the community, they can be fully integrated into and contributed to the tool. However, when full integration is not desired, HLS4ML can be extended via the Extension API, available for both the Keras 2 and PyTorch front ends, and all supported back ends. The Extension API allows users to leverage most of HLS4ML's rich infrastructure for other layers, optimizers, and HLS templates, while enabling them to implement the missing operators for their target applications. For this, the front end, IR, and back end must all be extended to support the new layer. On the front end side, this requires a custom layer handler function to parse the properties of the new layer. A class inheriting from the base layer class in the HLS4ML IR must also be defined. Finally, the back end requires Python templates for the configuration, function calls, as well as the custom HLS code of the new layer. These components are then registered with HLS4ML through the Extension API. Optionally, optimizers for the new layer can also be registered. A complete example can be found in the HLS4ML documentation online<sup>6</sup>. A practical example can be found in Reference [86], where within the context of an interaction network for jet tagging at CERN, the Extension API has been used to implement a custom Keras 2 projection layer, consisting of left- and right-multiplication by graph adjacency matrices. In addition to extending HLS4ML to support new layers, this mechanism could also be used to provide custom HLS implementations for existing layers, to e.g. optimize the design for a specific application or use different design techniques.

#### 9 Evaluation

Given the breadth of possible applications for HLS4ML, only a fraction of its capabilities can be demonstrated here. The initial performance studies for the different types of networks supported by HLS4ML can be found in the respective publications [1, 2, 41, 48, 70, 71, 75]. Additionally, prior works have shown acceleration of larger CNNs (ResNet- and UNet-like architectures) [17, 42] as well as large-scale, distributed models over a cluster of FPGAs [77, 115] with HLS4ML. Here, we instead present quantitative results obtained with the HLS4ML framework for a variety of benchmark models as new baselines for future works, with the aim of highlighting more recently added capabilities, such as the oneAPI and Catapult HLS back ends. As a community driven project, we also highlight the benefits of the evolving HLS4ML ecosystem. Therefore, results obtained using the HGQ quantization library and the new DA strategy are presented. These are post-route results of designs generated by HLS4ML targeting AMD Xilinx UltraScale+ FPGAs (XCVU9P and XCVU13P), or an Altera Agilex7 FPGA. We further highlight the wide range of applications enabled by HLS4ML by discussing models implemented on ASICs using the Catapult back end, and studies evaluating the performance of the HLS code generated by HLS4ML.

## 9.1 High-level feature jet tagger

The high-level jet tagger is a commonly used benchmark for low-latency neural networks on FPGAs [90]. The task is to classify jets (collimated particle showers at collider physics experiments), into five classes based on their originating

<sup>&</sup>lt;sup>6</sup>https://fastmachinelearning.org/hls4ml/advanced/extension.html

particle. The inputs for each jet are 16 scalar values representing physics-motivated high-level features. The model architecture employed is an MLP from [41]. The results targeting an AMD XCVU9P FPGA are shown in Table 3.

All models use the <code>io\_parallel</code> data transfer strategy. The models are quantized with HGQ and deployed with both the built-in Latency strategy and the DA strategy provided by <code>DA4ML</code>. For HGQ trained models, the results shown in different rows are quantized to different bit-widths, regularized by different  $\beta$  values. The results show major improvements when using HGQ over the previous baseline presented in [31], shown in the table labeled as QKeras. The new DA strategy further reduces the resource usage and latency of the designs.

In addition, we add the maximum achieved clock frequency  $F_{max}$  for the models when targeting a 1 GHz clock period in Table 4 obtained for these designs with the default settings in Vivado and Vitis 2023.2 as a reference. The results show that the DA strategy may achieve lower latency and comparable or higher  $F_{max}$  compared to the Latency strategy. We further show results on a more resource-constrained AMD XC7A35T FPGA in Table 5. In the Latency strategy, the most accurate model failed to place due to insufficient resources, while the DA strategy successfully placed all models, with the most accurate model utilizing more than 90% of LUTs on the device. This demonstrates that HLS4ML also enables deployment of models on low-end, resource-constrained FPGAs. Compared to the larger FPGAs, the main difference is reflected in the latency and the clock frequency. Since the AMD XC7A35T is an FPGA of a lower speed grade, the HLS compiler inserts additional register stages to meet timing, leading to higher latency and resource consumption. Additionally, the absolute increase in resources, compared to the larger FPGA, can be attributed to logic duplication during place-and-route, again in order to achieve timing closure.

Table 3. Accuracy, resource consumption, latency, and initiation intervals (IIs) of the jet tagging models. Resources are reported after out of context place-and-route with an AMD XCVU9P FPGA. The clock period used is 5 ns for all designs shown, except for the design marked with \*, which used 7 ns. All designs use no BRAM. The results for QKeras trained models are cited from [31] and for HGQ cited from [113].

| Trainer      | Strategy | Accuracy | Latency (cc) | DSP       | LUT           | FF           | II |

|--------------|----------|----------|--------------|-----------|---------------|--------------|----|

| QKeras [98]* | Latency  | 76.3%    | 15 [105 ns]  | 5,504     | 175           | 3,036        | 2  |

| QKeras [93]  | Latency  | 76.1%    | 10 [50 ns]   | 13,042    | 70            | N/A          | 1  |

| HGQ          | Latency  | 76.9%    | 5 (23.6 ns)  | 55 [0.8%] | 13,303 [1.1%] | 2,374 [0.1%] | 1  |

| HGQ          | Latency  | 76.5%    | 5 (23.1 ns)  | 30 [0.4%] | 6,715 [0.6%]  | 1,348 [0.1%] | 1  |

| HGQ          | Latency  | 75.9%    | 3 (12.7 ns)  | 15 [0.2%] | 3,044 [0.3%]  | 641 [0.0%]   | 1  |

| HGQ          | DA       | 76.9%    | 5 (23.4 ns)  | 0         | 11,978 [1.0%] | 2,117 [0.1%] | 1  |

| HGQ          | DA       | 76.5%    | 4 (18.0 ns)  | 0         | 6,067 [0.5%]  | 1,178 [0.0%] | 1  |

| HGQ          | DA       | 75.9%    | 3 (12.1 ns)  | 0         | 2,891 [0.2%]  | 651 [0.0%]   | 1  |

Table 4. Accuracy, resource consumption, latency, and  $F_{max}$  of the jet tagging models trained in HGQ [20] when targeting 1 GHz clock. Resource reported are after out of context place-and-route with an AMD XCVU9P FPGA (part number: xcvu9p-f1ga2104-2L-e). All designs use no BRAM and have an II of one cycle.

| Trainer | Strategy | F <sub>max</sub> | Accuracy | Latency (cc) | DSP       | LUT           | FF            |

|---------|----------|------------------|----------|--------------|-----------|---------------|---------------|

| HGQ     | Latency  | 739 MHz          | 76.9%    | 37 (50.1 ns) | 57 [0.8%] | 14,624 [1.2%] | 21,365 [0.9%] |

| HGQ     | Latency  | 705 MHz          | 76.5%    | 31 (44.0 ns) | 30 [0.4%] | 7,656 [0.6%]  | 11,513 [0.5%] |

| HGQ     | Latency  | 694 MHz          | 75.9%    | 30 (43.2 ns) | 17 [0.2%] | 3,765 [0.3%]  | 5,845 [0.2%]  |

| HGQ     | DA       | 713 MHz          | 76.9%    | 28 (39.3 ns) | 0         | 12,465 [1.1%] | 18,004 [0.8%] |

| HGQ     | DA       | 719 MHz          | 76.5%    | 23 (32.0 ns) | 0         | 6,297 [0.5%]  | 9,524 [0.4%]  |

| HGQ     | DA       | 756 MHz          | 75.9%    | 21 (27.8 ns) | 0         | 2,886 [0.2%]  | 4,667 [0.2%]  |

Table 5. Accuracy, resource consumption, latency, and  $F_{max}$  of the jet tagging models trained in HGQ [20]. Resource reported are after out of context place-and-route with an AMD XC7A35T FPGA (part number: xc7a35t1csg325-2L). All designs use no BRAM and have an II of one cycle.

| Trainer | Strategy | F <sub>max</sub> | Accuracy | Latency (cc)  | DSP        | LUT            | FF             |

|---------|----------|------------------|----------|---------------|------------|----------------|----------------|

| HGQ     | Latency  | -                | 76.9%    |               | Pla        | ice failed     |                |

| HGQ     | Latency  | 187 MHz          | 76.5%    | 53 (284.0 ns) | 30 [33.3%] | 11,091 [53.3%] | 24,649 [59.3%] |

| HGQ     | Latency  | 182 MHz          | 76.0%    | 45 (246.7 ns) | 17 [18.9%] | 5,565 [26.8%]  | 11,330 [27.2%] |

| HGQ     | DA       | 172 MHz          | 76.9%    | 58 (337.4 ns) | 0          | 19,467 [93.6%] | 36,995 [88.9%] |

| HGQ     | DA       | 185 MHz          | 76.5%    | 50 (270.1 ns) | 0          | 10,692 [51.4%] | 20,407 [49.1%] |

| HGQ     | DA       | 176 MHz          | 75.9%    | 46 (261.1 ns) | 0          | 5,455 [26.2%]  | 9,952 [23.9%]  |

On the same task, we also processed a QKERAS trained model with 76.9% accuracy using the oneAPI back end, and evaluated its performance using ONEAPI 2025.0 and QUARTUS 23.1. The results are given in Table 6. Given the model's small size, we continue using io\_parallel for data transfer between the layers, and we fully unroll the layers. For this compiler, we use different compiler flags for different optimization targets. We found that the lowest latency can be obtained when requesting the lowest target frequency simultaneously with the latency optimization target. As this model has an II of one under this configuration, its throughput is proportional to the clock frequency given a continuous data stream. Therefore, it is possible to trade off between latency and throughput by adjusting the target frequency.

Table 6. Resource consumption, latency, and  $F_{max}$  of the jet tagging QKeras models using oneAPI. All designs have an accuracy of 76.9%. Resources reported are after out of context place-and-route, as reported by Quartus, with an Altera Agilex7 FPGA (part number: AGFB014R24A2E2V). The latency is measured first input to first output, reported both in clock cycles and in nanoseconds if running at  $F_{max}$ . The optimization target is an option given to the icpx compiler, unrelated to the HLS4ML strategy. The default option, obtained by not explicitly specifying an optimization target, optimizes for maximum frequency, and turns on hyper-optimized handshaking. All designs shown have negligible MLAB, RAM, and DSP usage (less than 0.01%) and an II of one.

| Opt. Target | Target F <sub>max</sub> | F <sub>max</sub> | Latency (cc) | ALM           | ALUT          | FF            |

|-------------|-------------------------|------------------|--------------|---------------|---------------|---------------|

| Latency     | 200 MHz                 | 341 MHz          | 21 [62 ns]   | 11,434 [2.3%] | 21,471 [2.2%] | 8,864 [0.45%] |

| Latency     | 480 MHz                 | 614 MHz          | 50 [81 ns]   | 12,085 [2.5%] | 22,551 [2.3%] | 31,243 [1.6%] |

| Default     | 480 MHz                 | 782 MHz          | 90 [115 ns]  | 13,576 [2.8%] | 24,319 [2.5%] | 40,051 [2.1%] |

## 9.2 Street View House Numbers classifier

Classification of the house numbers in images from the Street View House Numbers (SVHN) dataset [84] is a common benchmark for computer vision tasks. We show the results from [20] and [2], where both used the same model architecture as in [2]: a CNN with 3 convolutional layers, 3 max pooling layers, and 2 fully connected layers. The detailed description of the architecture can be found in both works. For HGQ trained models, the results shown in different rows are quantized to different bit-widths, regularized by different  $\beta$  values. The results are shown in Table 7. All designs shown are using PF = 1 (each convolution kernel is applied once per clock cycle) and io\_stream. Compared to the previous results obtained in [2] with HLS4ML, the new results use significantly fewer on-chip resources while retaining the same accuracy. As in the previous section, we find that the DA strategy offers improved performance compared to the Latency one, most notably by eliminating all DSP usage, while reductions in LUTs, FFs, and latency are less pronounced. However, this advantage might not transfer to cases where high variable precision is required, and all cases with an RF larger than one, which are not supported in the DA strategy.

Table 7. Accuracy, resource usage, and latency of the SVHN classifier models. Reported resource usage after out of context place-and-route with an AMD XCVU9P FPGA. The clock period used is 5 ns. The results for QKERAS trained models are cited from [2], and the HGQ trained models are cited from [20].

| Trainer | Strategy | Accuracy | Latency (cc)          | DSP         | LUT (k)    | FF (k)     | BRAM        | II (cc) |

|---------|----------|----------|-----------------------|-------------|------------|------------|-------------|---------|

| QKeras  | Latency  | 94.%     | 1,035 [5.2 μs]        | 174 [2.54%] | 111 [9.4%] | 33 [1.4%]  | 67.0 [3.1%] | 1,030   |

| QKeras  | Latency  | 88.%     | $1,059 [5.3 \mu s]$   | 72 [1.05%]  | 48 [4.1%]  | 15 [0.63%] | 32.5 [1.5%] | 1,029   |

| HGQ     | Latency  | 93.9%    | 1,050 [5.3 μs]        | 58 [0.85%]  | 69 [5.8%]  | 28 [1.2%]  | 32.0 [1.5%] | 1,029   |

| HGQ     | Latency  | 93.1%    | $1,061 [5.3 \mu s]$   | 30 [0.44%]  | 47 [4.0%]  | 21 [0.89%] | 28.0 [1.3%] | 1,029   |

| HGQ     | Latency  | 91.9%    | $1,058 [5.3 \ \mu s]$ | 15 [0.22%]  | 40 [3.4%]  | 18 [0.76%] | 23.5 [1.1%] | 1,029   |

| HGQ     | DA       | 93.9%    | 1,045 [5.2 μs]        | 0           | 53 [4.5%]  | 20 [0.85%] | 32.0 [1.5%] | 1,029   |

| HGQ     | DA       | 93.1%    | $1,045 [5.2 \ \mu s]$ | 0           | 37 [3.1%]  | 15 [0.63%] | 28.0 [1.3%] | 1,029   |

| HGQ     | DA       | 91.9%    | $1,045 [5.2 \mu s]$   | 0           | 31 [2.6%]  | 14 [0.59%] | 23.5 [1.1%] | 1,029   |

## 9.3 Particle-based jet tagger