# An Analytical and Empirical Investigation of Tag Partitioning for Energy-Efficient Reliable Cache

Elham Cheshmikhani and Hamed Farbeh Member, IEEE

Abstract—Associative cache memory plays a decisive role in enhancing the performance and energy consumption of modern processors. Meanwhile, by occupying more than half of the processor chip area, cache memory is susceptible to transient and permanent faults, threatening the system's dependability. As the only hardware-managed memory module in the system, the tag array of the caches is the most critical and active component contributing a large fraction of energy consumption and error occurrence. Tag partitioning is a widespread approach for both tag energy consumption reduction and reliability enhancement. This approach splits the tag comparison operation into two steps, and only the tags whose k lower order bits are matched with that of the input address in the first step are activated for comparing their remaining higher order bits in the second step. The key decision parameter for tag partitioning is properly adjusting the tag-splitting point (k) to achieve the maximum reduction in the number of reads. This parameter has been intuitively, randomly, or experimentally selected in the existing studies without any justification. Even for an appropriate selection of this parameter via extensive experiments, its sensitivity to various cache configuration parameters makes it ad-hoc and not extendable to other scenarios. In this paper, we analytically illustrate that selecting an inappropriately large or small value for the tag-splitting point significantly downgrades the efficiency of tag partitioning and then formulate this parameter to determine its optimum value. As a function of cache configuration parameters, the proposed formulation is proven to be convex and differentiable for determining the optimum splitting point, besides its ability to accurately report the degree of the tag partitioning efficiency for any splitting point and configuration parameters. To approve the correctness and accuracy of the proposed formulation, we experimentally investigate the tag partitioning efficiency and optimum splitting point for a wide range of cache configurations and demonstrate a very close matching between the two. The proposed formulation is a guarantee for the designers and researchers to instantaneously determine the optimum tag-splitting point and calculate the read reduction of tag partitioning.

*Index Terms*—Cache Memory, Energy Consumption, Error Rate, Tag Array, Tag Partitioning.

#### I. INTRODUCTION

On-chip caches have a crucial role in improving system performance in modern processors that support further requirements such as Artificial Intelligence (AI) and Neural Networks (NNs) in today's life [1]–[3]. Besides its benefit in performance and total energy consumption, on-chip caches are the most power-hungry and error-prone chip components [4]. Among different cache structures, associative caches are preferred, while the parallel accesses to the entries in a set

Manuscript received August 04, 2024; revised June 07, 2025.

for tag comparisons exacerbate the cache energy consumption and error rate [5]–[8]. The cache energy consumption further increases due to the necessity of employing Error Correction Codes (ECCs) for reliability enhancement [9]–[13]. According to recent industrial and research reports, cache hierarchy accounts for 12-45% of energy consumption in a system [5].

In a conventional set-associative cache, all the target set entries in the tag arrays are simultaneously accessed to achieve better performance, but doing so causes a large amount of energy consumption [8], [14], [15]. Among all steps of the caching procedure, tag comparison in highly-associative caches consumes a significant portion of energy dissipation. Previous attempts, such as way prediction and sequential tag access for energy reduction, are still associated with substantial energy consumption due to the tag reads [16]. Numerous new cache architectures, such as *phased*, *pseudo-set-associative*, way predicting, reactive-associative, way-halting, and way-concatenating caches are intended to reduce power and/or energy consumption [17]–[21].

On the other hand, the scalability challenge and high leakage power consumption of conventional SRAM-based caches in deep Nano-scale technology nodes resulted in extensive research on alternatives for SRAM technology in recent years [22]. Among various emerging memory technologies, *Spin-Transfer Torque Magnetic RAM* (STT-MRAM) is the most promising candidate for replacing the SRAM technology in on-chip caches [23]–[26]. The STT-MRAM technology benefits from high density, scalability, immunity to soft errors, and near-zero leakage power. However, it faces some reliability challenges such as *read disturbance*, *retention failure*, and *write failure* [15], [23], [27]. Among the various sources of STT-MRAM unreliability, read disturbance is the dominant threat in the read-intensive tag array.

Tag partitioning is known as an effective approach for reducing accesses to tag bits in associative caches for energy consumption and/or error rate reduction [5], [6], [20], [28]–[32]. In this approach, tag comparison is split into two steps. In the first step, k lower order tag bits of the target cache set are partially compared with the requested address, and the mismatched tags are eliminated from the second step comparison in which the remaining bits are compared. Several recent studies in both SRAM and STT-MRAM caches that targeted tag access reduction are based on this approach [5], [6], [14], [20], [28]–[32]. The efficiency of tag partitioning for read reduction depends on the tag-splitting point, where very small values for this point cause a majority of tags to be unfavorably matched in the first step, and very large values lead to a low effect of eliminating tags for the second step.

Despite its critical effect, there is no investigation on finding

E. Cheshmikhani (corresponding author) is with the Department of Computer Science and Engineering, Shahid Beheshti University, Tehran, Iran. E-mail address: e\_cheshmikhani@sbu.ac.ir.

H. Farbeh is with the Department of Computer Engineering, Amirkabir University of Technology, Tehran, Iran. E-mail: farbeh@aut.ac.ir.

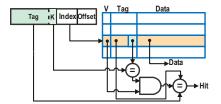

Fig. 1: Two-step tag comparison in tag partitioning method.

the proper tag-splitting point or a study on the sensitivity of both tag partitioning to this value and the proper selection of this value to the cache configuration. All the existing methods utilizing tag partitioning adjust tag-splitting points intuitively or experimentally for their specific system configuration. Its experimental adjustment requires time-consuming, exhaustive simulations to find a suitable value, and there is no guarantee of the suitability of this intuitive adjustment.

In this paper, we mathematically derive the optimum tagsplitting point for a partitioned tag structure by formulating the number of tag reads via a novel probabilistic model. The proposed formulation illustrates the dependency of tag reads on system configuration parameters, including cache associativity, cache size, and address length. It is also capable of deriving the total number of tag reads per access as well as the percentage of reduction for a given splitting point, besides calculating the optimum splitting point. As a multi-variable function, the proposed formulation is differentiable with a positive second-order derivative and is proven to be convex with a single minimum at the optimum splitting point.

We analytically and experimentally conduct a comprehensive design space exploration and demonstrate that the formulations agree with the experiments in all cache configuration scenarios. Taking advantage of the proposed formulation, the designers and researchers are able to not only determine the optimum tag-splitting point but also estimate the tag partitioning efficiency for energy consumption and error rate reduction. Therefore, instead of performing time-consuming exhaustive design space exploration to find an ad-hoc suitable tag-splitting point, the proposed formulation provides an early design stage investigation.

The rest of this paper is organized as follows. In Section II, we explore the related studies and present motivation for this work. In Section III, we propose different formulations to analyze the effective parameters on the optimal number of read bits in partial tag comparison. The analytical investigations and comprehensive empirical evaluations are presented in Section IV. We conclude the paper in Section V.

#### II. RELATED WORK AND MOTIVATION

Several methods have been proposed to manage the tag bits comparison in SRAM and STT-MRAM caches [5], [6], [14], [20], [28]–[33]. These methods are motivated by the observation that mismatches in tag comparisons typically take place in the low order bits due to the spatial locality. Therefore, a tag partitioning approach for partial tag comparison is proposed to reduce power consumption and decrease the number of read bits in the cache. Fig. 1 depicts an abstract schematic of tag partitioning and its two-step comparison operation.

The partial tag comparison was originally proposed for way-prediction [20], [29] to decrease the cache power consumption. The 2-way set-associative cache in these works played a direct-map cache role to gain power saving. The cache way is selected based on noticing that the two tags for a set must differ by at least one bit. These studies are the basis of all partial tag comparisons for power-saving goals.

2

Another study tries to predict cache misses using a Bloom filter [32]. In this work, each of the cache ways is fed to a Bloom filter. They use the *Most-Recently Used* (MRU) policy based on the *hot* lines to predict the cache hits, and if the numerical values for hot lines are small amounts, a Bloom filter is employed to predict the cache misses. An enhanced counting Bloom filter is also used in [6] to predict cache misses with high accuracy, as well as partial tags to decrease the overall cache size. This way, unnecessary tag comparisons can be prevented, and therefore, the cache energy consumption is considerably reduced.

The scheme proposed in [28] for tag comparison reduction is based on predicting either cache hits or cache misses. The authors presented a partial tag-enhanced Bloom filter to improve the accuracy of the cache miss prediction and hot/cold checks that control data liveness to reduce the tag comparisons of the cache hit prediction method. In this study, the number of lower order bits to be compared with the input tag address can be changed based on the blocks that are grouped between hot and cold blocks and the number of their accesses.

#### B. Tag Partitioning via Buffering Lower Order Bits

A partial tag comparison is proposed for SRAM-based caches in [34]. The authors added a very small array of tags beside the original tag array. These added tags are compared with the target address. If none of the ways' 3 least significant bits match the income address, a miss is reported. Only when there is a match, the sense amplifiers attached to the data array bit-lines will be enabled to read the corresponding data.

In [35], the authors extended the tag array with an additional register file, which consists of 2 lower order bits of each tag array way. The comparison procedure contains three steps. First, the 2 lower order bits in the register file are compared with the input tag address. If one or more matches occur by comparing those 2 bits in the first step, they have to compare the other bits, as well. If the remained bits are matched with the input tag address, the corresponding data block is read from the data array in the third step.

One of the most popular studies in SRAM-based caches to decrease power dissipation is the phased tag cache [17]. This method tries to partially compare the tags. The 7 least significant bits are compared in the first phase, and the remaining bits are compared in the second phase.

A new cache architecture, called *way-halting cache*, is developed in [21] to reduce the energy consumption. Way-halting cache is a four-way set-associative cache that stores the four lowest-order bits of all ways' tags into a fully associative memory, called a halt tag array. The halt tag array predetermines which tags cannot match due to their low order

4 bits mismatching. Further accesses to ways with known mismatching tags are then halted, thus saving energy.

Compressed tag architecture is introduced in [36]. To reduce the energy consumption in tag arrays, this tag-matching mechanism uses a locality buffer and tag compression. Small tag space matching is used instead of full tag matching in this work. Initially, the small tag space and then the remaining bits are compared to be matched.

## C. Tag Partitioning by Splitting Tag

In [5], a partial tag comparison method called *Segmented Tag Cache* (STC) is proposed to reduce the amount of energy consumption during the tag access. In this method, the tag array is segmented into two parts, and partial tag access only reads the low order part of the tag. The STC modifies the tag array to reduce its overhead same way as the way-halting cache.

Reduced One-Bit Tag Instruction Cache (ROBTIC) was proposed in [37] that enables the cache tag field to only contain the least significant bit of the full tag in the first step. As a result, the cache can only be mapped to one segment of memory, whereas it covers two regions. Next, the most significant bits of the memory addresses can be used to identify the mappable regions.

A new filter cache model using partial tag matching named *Data Filter Cache System with Partial Tag Cache* (DFPC) is proposed to reduce L1 cache access energy [38]. This model employed another small cache, called *partial tag cache*, to filter unnecessary accesses to the ways of cache. This work used 6 bits to compare the partial tag cache.

## D. Tag Partitioning in STT-MRAM Caches

In [39], the authors presented two techniques – sequential tag-data access for reads and partial line update for writes – that improve the energy efficiency of STT-MRAM caches. A cache architecture that performs partial cache line updates for cache writeback energy reduction was proposed. The technique does not incur any extra cache misses since it does not change the data flow between different cache levels.

Another study tried to increase the reliability of STT-MRAM caches using partial tag comparison [14], [33]. The authors split the tag comparison into two parts, first, they read the 4 bits of low order bits and in the next step, the remained bits are read and compared with the input address. They experimentally demonstrated that among different splitting points, 4 represents better reliability and energy saving for their dedicated cache configuration.

All the tag partitioning methods require a two-step operation for tag comparison. In the first step, a part of the tag bits are read and compared with the associated bits, and in the second step, the remained bits of a subset of tags are read and compared. All the methods dedicate a number of bits for the first step based on the reduction of false hits or increasing the number of hits. By the way, changing the cache size, the application running on the cache, the address length, or the cache associativity can affect this number. None of those studies provides an analytical reasoning for their selection,

while this value can have a significant effect on their efficiency for reducing energy consumption or error rate. In this paper, we open a new door to analyze the affecting factors of this selection. In this case, given the size of the cache, associativity, and other parameters of the cache, the optimal number of bits that should be read in the first step of partial tag comparison is determined to maximize the efficiency of the tag partitioning-based methods.

3

#### III. PROPOSED ANALYSIS AND FORMULATION

Partially comparing tags requires reading a few low order bits in the first step and the remaining part of the matched tags in the next step. In order to dedicate the proper number of reads in each step to minimize the number of reads for achieving the best reliability and energy saving, different parameters must be considered. In this paper, we formulate the number of tag reads to mathematically determine the tag-splitting point for maximum efficiency. It is important to note that tag partitioning does not influence cache access patterns, cache misses, interactions between cache levels, or operations related to coherency. The sole aspect impacted by tag partitioning is the frequency of reads from the tag cell, which is altered by modifying the tag comparison circuitry.

#### A. Formulating Number of Tag Reads

Considering an x-way set-associative cache, the number of reads from tag bits in conventional cache is according to (1).

Number of read bits in baseline =

$$n \times x$$

(1)

where, n is tag length, which depends on address length, cache size, associativity, and cache block size. In the partitioned tag, the number of reads in the first step is given in (2).

Number of read bits in first step =  $k \times x$  (2) where, k is the number of bits compared in the first step, i.e., the tag-splitting point. The number of bits *per tag* to be compared in the second step is as simple as (3).

Number of read bits in second step = n - k (3) where, n is the total tag length. However, calculating the total number of reads in the second step is more complicated, as it requires determining the number of tag ways matched in the first step. We model this value as a probability problem. Considering k bits in partial tag comparison of the first step, the probability of a match is according to (4).

Probability of a match in first step =

$$\frac{1}{2^k}$$

(4)

Equation (4) is equivalent to the probability of success in a single Bernoulli trial. Equivalently, the probability of a mismatch is according to (5).

Probability of a mismatch in first step =

$$1 - \frac{1}{2^k}$$

(5)

Consequently, the number of matched tags in the first step for an x-way set-associative cache can be calculated using (6).

$Number\ of\ matched\ tags\ in\ first\ step =$

$$\sum_{i=0}^{x} i \times {x \choose i} \times \left(\frac{1}{2^k}\right)^i \times \left(1 - \frac{1}{2^k}\right)^{x-i} \tag{6}$$

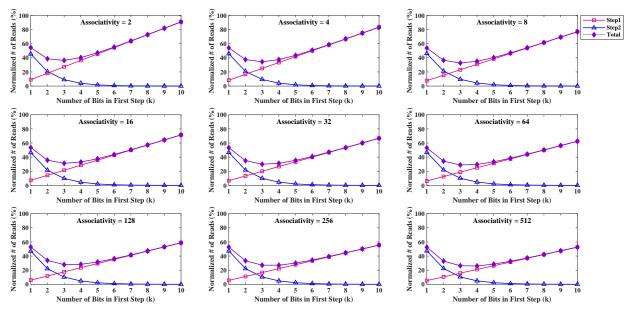

Fig. 2: Expected number of reads in the first (Eq. (2)) and second steps (Eq. (7)) besides their accumulation based on Eq. (8).

Combining (3) and (6) gives the number of reads in the second step, as shown in (7).

Number of read bits in second step =  $(n - k) \times$

$$\sum_{i=0}^{x} i \times {x \choose i} \times (\frac{1}{2^k})^i \times (1 - \frac{1}{2^k})^{x-i}$$

(7)

The summation of (2) and (7) results in the total number of reads for a cache access request as given in (8).

Total number of expected read bits =  $k \times x + (n - k) \times x$

$$\sum_{i=0}^{x} i \times {x \choose i} \times (\frac{1}{2^k})^i \times (1 - \frac{1}{2^k})^{x-i}$$

(8)

where, n is the number of tag address bits, k is the number of read bits in the first step, and i is the number of tag matches in the first step.

#### B. Analysing Tag Splitting Effect

As shown, this equation has two parts; the first part is  $k \times x$ , which is the number of read bits in the first step. It demonstrates that k bits, which is the tag-splitting point, are read in the first step from all the ways of the tag array. For the second step, the remaining (n-k) bits of the mismatched tags are discarded. The number of matched ways compared in the second step is calculated based on the given probability.

Considering the effect of the splitting point on the number of reads in each step, (2) shows that the number of reads in the first step linearly increases by larger k, whereas the number of reads in the second step super-linearly decease according to (7). In other words, the two terms in the total number of reads are adversely and differently affected by changing k.

Fig. 2 illustrates the effect of k on the number of reads in each step as well as the summation of the two. The results are for a wide range of cache associativities from 2 to 512 in a 1MB cache size and address length of 40 bits. The

horizontal axis is the tag-splitting point, and the vertical axis is the number of reads normalized to the baseline, i.e., non-partitioned tag. The curves related to the first and second steps show that their different ascending and descending trends lead to a minimum for the curve of total reads. The splitting point at which the minimum of total reads takes place is the optimum point we are looking for. Considering various associativities, the optimum splitting point increases from 2 in the 2-way cache to 4 in the 512-way cache, which indicates that the optimum value for k is directly but very slightly affected by the cache associativity. Besides the above observation derived from the formulation of the number of reads, we provide a formal calculation of the optimum splitting point in the following.

## C. Formulating Optimum Tag Splitting Point

So far, the total number of read bits in the tag part of the cache using partial tag comparison has been formulated, as observed in (8). The aim of this formulation is to calculate the optimal value of k, which is the one that minimizes the total number of read bits in both steps of partial tag comparison. To do so, we investigate the convexity of (8) and therefore, the second derivative of the function should be calculated. The second derivative of (8) is shown in (9).

$$\frac{\partial^{2}[k \times x + (n - k) \times \sum_{i=0}^{x} i \times {x \choose i} \times (\frac{1}{2^{k}})^{i} \times (1 - \frac{1}{2^{k}})^{x-i}]}{\partial k}$$

$$= \frac{x}{2^{k}} \times \log 2 \times (2 + (n - k) \times \log 2)$$

(9)

Since the value of k is between 0 and n, the second derivative of (8) is positive definite. Therefore, (8) is *convex* as shown in Fig. 3 and has a minimum, which is the optimal number of k.

| Cache | Address | Associativity = 4        |                  |                      | Associa                  | tivity =         | = 8                  | Associa                  | tivity =         | = 16                 | Associativity = 32       |                  |                      |  |

|-------|---------|--------------------------|------------------|----------------------|--------------------------|------------------|----------------------|--------------------------|------------------|----------------------|--------------------------|------------------|----------------------|--|

| Size  | Length  | Total # of read bits (%) | k <sub>min</sub> | k <sub>optimal</sub> | Total # of read bits (%) | $k_{\text{min}}$ | k <sub>optimal</sub> | Total # of read bits (%) | k <sub>min</sub> | k <sub>optimal</sub> | Total # of read bits (%) | $k_{\text{min}}$ | k <sub>optimal</sub> |  |

|       | 32      | 28.90                    | 3                | 3.20                 | 27.94                    | 3                | 3.29                 | 27.08                    | 3                | 3.38                 | 25.99                    | 3                | 3.47                 |  |

| 512VD | 40      | 21.87                    | 4                | 3.84                 | 21.25                    | 4                | 3.90                 | 20.67                    | 4                | 3.96                 | 20.14                    | 4                | 4.02                 |  |

| 512KB | 48      | 17.96                    | 4                | 4.29                 | 17.61                    | 4                | 4.33                 | 17.27                    | 4                | 4.38                 | 16.96                    | 4                | 4.43                 |  |

|       | 56      | 15.23                    | 5                | 4.63                 | 14.93                    | 5                | 4.67                 | 14.65                    | 5                | 4.71                 | 14.39                    | 5                | 4.75                 |  |

|       | 32      | 31.25                    | 3                | 3.38                 | 30.00                    | 3                | 3.29                 | 28.91                    | 3                | 3.20                 | 27.94                    | 3                | 3.29                 |  |

| 21/10 | 40      | 23.30                    | 4                | 3.96                 | 22.55                    | 4                | 3.90                 | 21.88                    | 4                | 3.84                 | 21.25                    | 4                | 3.90                 |  |

| 2MB   | 48      | 18.75                    | 4                | 4.38                 | 18.35                    | 4                | 4.33                 | 17.97                    | 4                | 4.29                 | 17.61                    | 4                | 4.33                 |  |

|       | 56      | 15.87                    | 5                | 4.71                 | 15.55                    | 5                | 4.67                 | 15.23                    | 5                | 4.63                 | 14.94                    | 5                | 4.67                 |  |

|       | 32      | 34.38                    | 3                | 2.79                 | 32.69                    | 3                | 2.87                 | 31.25                    | 3                | 2.99                 | 30.00                    | 3                | 3.10                 |  |

| 8MB   | 40      | 25.00                    | 4                | 3.55                 | 24.11                    | 4                | 3.63                 | 23.30                    | 4                | 3.70                 | 22.55                    | 4                | 3.77                 |  |

| SIVIB | 48      | 19.64                    | 4                | 4.08                 | 19.18                    | 4                | 4.13                 | 18.75                    | 4                | 4.19                 | 18.35                    | 4                | 4.24                 |  |

|       | 56      | 16.58                    | 5                | 4.47                 | 16.22                    | 5                | 4.51                 | 15.88                    | 5                | 4.55                 | 15.55                    | 5                | 4.59                 |  |

|       | 32      | 38.75                    | 3                | 2.51                 | 36.36                    | 3                | 2.61                 | 34.38                    | 3                | 2.75                 | 32.69                    | 3                | 2.87                 |  |

| 32MB  | 40      | 27.08                    | 3                | 3.38                 | 25.98                    | 4                | 3.47                 | 25.00                    | 4                | 3.55                 | 24.11                    | 4                | 3.63                 |  |

| 32MB  | 48      | 20.67                    | 4                | 3.96                 | 20.14                    | 4                | 4.02                 | 19.64                    | 4                | 4.08                 | 19.18                    | 4                | 4.13                 |  |

|       | 56      | 17.28                    | 4                | 4.38                 | 16.96                    | 4                | 4.43                 | 16.58                    | 5                | 4.47                 | 16.22                    | 5                | 4.51                 |  |

TABLE I: Number of reads using Eq. (8) for the optimal point ( $k_{optimal}$  and its rounded value  $k_{min}$ ) calculated by Eq. (11).

Fig. 3: Proving the convexity of Eq. (8), for 40-bit tag length and 16-way set-associative.

To calculate the minimum of (8), its first derivative should be calculated and equal to zero. We can see the first derivative of (8) in (10).

$$\frac{\partial[k \times x + (n - k) \times \sum_{i=0}^{x} i \times \binom{x}{i} \times (\frac{1}{2^k})^i \times (1 - \frac{1}{2^k})^{x-i}]}{\frac{\partial k}{2^k} \times (\log 2 \times (k - n) + 2^k - 1)}$$

(10)

The equality of (10) to zero results in (11), where ProductLog is the Lambert W function, also called the omega function or product logarithm. The multivalued function of product logarithm (ProductLog[z]) equals w, if  $z = we^w$ .

$$k = \frac{\log(ProductLog[2^n \times e])}{\log 2}$$

(11)

The final goal of the above analysis is to derive the formula of the optimum splitting point, which is given in (11). According to (11), it seems that k is, apparently, determined only by n. Since n is the tag length, both cache size and associativity directly affect it, in addition to the address length.

In this paper, we examine this dependency for different associativities and different cache sizes. By increasing the cache size, the tag address length is decreased. As illustrated in Table I, the total number of read bits is calculated based on (8). The result of the total number of read bits in comparison with the optimal number of bits to be read extracted from (11) shows that in an 8-way set-associative cache, reading 4 bits in

TABLE II: Details of system configuration.

| Processor    | Quad Core, out-of-order, 4-issue, 3.2 GHz         |

|--------------|---------------------------------------------------|

| L1 I/D-cache | 32KB/core, 4-way, 4-cycle latency, LRU            |

| L2-cache     | 256KB-1MB/shared, 4-64-way, 10-cycle latency, LRU |

| Main memory  | 4 GB, one 8-byte channel, 1600MT/s                |

the first step results in the minimum number of total read bits when the address length is 40 or 48. The optimum number of read bits in the first step for 16- and 32-way set-associative caches with the same address length remains 4. This value changes to 5 in very large associativities, very small caches, and/or very long addresses, and changes to 3 conversely. The above theoretical calculations depict that the optimum splitting point for the partial cache comparison is in the range of [3, 5] for conventional cache configurations.

### IV. EVALUATION METHODOLOGY AND RESULTS

## A. System Setup

This section experimentally evaluates and verifies the formulations and analysis presented in this work and investigates its various aspects. To this aim, a quad-core processor equipped with dedicated instruction/data L1 caches and a shared L2 cache is modeled in the gem5 full-system simulator [40]. Table II depicts the details of the system configuration. The workloads are 17 combinations of randomly-selected memory-bound and CPU-bound programs in the SPEC CPU2017 benchmark suite [41], as given in Table III, simulated for 4 billion instructions after fast-forwarding the initial 200 million instructions as the warm-up phase.

As mentioned in Section III, the key parameters affecting the efficiency of the tag partitioning approach are the degree of cache associativity, address length, and cache size. Cache partitioning can be utilized in different cache levels, and the goal of this study is to show that the optimum splitting point can be formulated and calculated in advance with no requirement for workload profiling. All the previous theoretical observations, i.e., Fig. 3, Fig.2, and Table I, are independent of cache level and are applicable to both L2 and L3 caches as well as L1 cache, considering their suitable configurations. To investigate

TABLE III: Combinations of benchmarks for generating workloads for a simulated quad-core processor.

| Workload | Benchmarks                                | CPU- (C) or Mem (M)  |

|----------|-------------------------------------------|----------------------|

|          |                                           | bound or mixture (X) |

| Mix0     | perlbench, exchange2, gcc, bwaves         | C, X, C, M (C)       |

| Mix1     | leela, exchange2, deepsjeng, xz           | C, X, C, M (C)       |

| Mix 2    | gcc, bwaves, mcf, leela                   | C, M, M, C (X)       |

| Mix 3    | bwaves, mcf, cactusADM, imageick          | M, M, X, M (M)       |

| Mix 4    | mcf, cactusADM, namd, x264                | M, X, C, C (X)       |

| Mix 5    | namd, parest, soplex, calculix            | C, C, C, X (C)       |

| Mix 6    | x264, namd, hmmer, 1bm                    | C, C, C, M (C)       |

| Mix 7    | cam4, nab, imageick, namd                 | X, C, M, C (X)       |

| Mix 8    | wrf, soplex, blender, parest              | M, C, X, C (X)       |

| Mix 9    | nab, cam4, x264, leela                    | C, X, C, C (C)       |

| Mix 10   | deepsjeng, hmmer, soplex, pelbench        | C, C, C, C (C)       |

| Mix 11   | blender, deepsjeng, libquantum, exchange2 | X, C, M, X (X)       |

| Mix 12   | parest, libquantum, exchange2, nab        | C, M, X, C (X)       |

| Mix 13   | lbm, omnetpp, astar, wrf                  | M, C, C, M (X)       |

| Mix 14   | omnetpp, namd, xalancbmk, cam4            | C, C, C, X (C)       |

| Mix 15   | roms, xalancbmk, bwaves, exchange2        | M, C, M, X (X)       |

| Mix 16   | xalancbmk, perlbench, cam4, blender       | C, C, X, X, (X)      |

the conformity of the formulations with the experiments, tag splitting is applied to the L2 cache in the following evaluations. Three cache sizes, i.e., 256KB, 512KB, and 1MB, have been considered in the experiments to correspond to the L2 cache size in real systems. In addition to regular cache associativities (8-way and 16-way), we also evaluated very small and very large associativities, e.g., 4-, 32-, and 64-way, in L2 cache to illustrate the matching between the experiments and formulation even in extreme configurations and corner cases.

We use CACTI to model the SRAM cache in various configurations within a 32nm technology node, and the energy parameters are detailed in Table IV for a 256KB L2 cache with 8- and 16-way associativity. For the sake of brevity, we are unable to report the energy details for all evaluated cache sizes and configurations. Since tag partitioning has no impact on the number of cache memory cells or cache performance, and the modifications to the cache control circuitry are negligible, the leakage power/energy in conventional and tag-partitioned caches is nearly identical. Targeting to reduce read operations from the tag array, tag partitioning primarily influences dynamic energy consumption. The three highlighted rows in Table IV represent the tag energy parameters impacted by tag partitioning. As shown, while certain cache components remain unchanged in tag partitioning, these three highlighted rows account for the majority of total tag energy consumption.

For a comprehensive design space exploration, a wide range of cache configurations is explored. The evaluations are for tag-splitting points from 1 to 10. Limiting the tag-splitting point to a maximum of 10 is because both formulations and experiments illustrate that the optimum point for all configurations is always significantly lower than 10. In the following, we first discuss the various workloads' behaviors and then illustrate the conformation of experiments and formulations. Then, the effect of the tag splitting point on energy consumption and error rate, and the proper selection of this value, is explored.

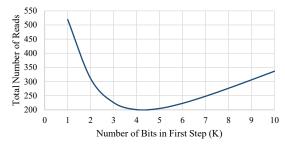

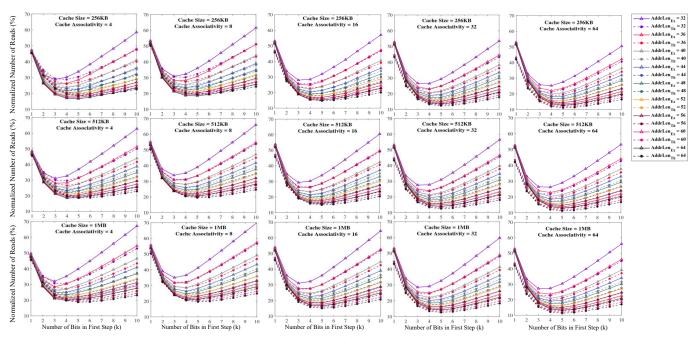

# B. Experimental Tag Read Evaluation

The number of tag bits reads per cache access request is the critical evaluation parameter that affects both the tag energy consumption and error rate. For each workload in a specific configuration, we normalize the tag bits read in each splitting point to the number of reads in the baseline, i.e., the cache configuration without partial tag read. Fig. 4 illustrates the number of reads in various tag-splitting points for all workloads considering cache associativity ranging from 4 to 64, cache size of 1MB, and 40-bit address length. It is noteworthy that a similar trend is observed in the other cache sizes/address lengths, and the deductions are extendable to other configurations.

In Fig. 4, five cache associativities (from 4 to 64) are separately plotted in independent subfigures, and the averages of all workloads in the five cache associativities are integrated into the sixth subfigure to better illustrate the effect of associativity on the optimum splitting point. Considering the trends in these associativities, three key observations are evident. First, by increasing the cache associativity, the variation and diversity in the workloads are reduced, and their behavior in the number of reads in various splitting points is smoother and closer to the average curve. This shows that although the reduction in the number of reads is workload-dependent, this dependency loosens in larger cache associativities due to a higher degree of randomness in low order tag bits in a set. Hence, the optimum splitting point is not meaningfully affected by the workload behavior, but by the cache configuration. Second, higher read reductions are observed in larger cache associativities. This is because a greater number of tags in a set are eliminated in larger associativities. Third, the optimum splitting point for all workloads in all associativities is almost the same and resonates between 3 and 5, which confirms our formulations.

The sixth subfigure in Fig. 4 is the integration of all average curves in different associativities. Three key observations on this subfigure are as follows. First, the larger the cache associativity, the greater reduction in tag reads is observed; the top curve is for the 4-way cache, and the bottom curve is for the 64-way cache. Second, the optimum splitting point is 4 for associativities 4, 8, 16, and 32, and it increases to 5 for associativity 64. These points are highlighted in the curves. This observation indicates that the optimum splitting point is directly affected by cache associativity, but a very large change in the latter slightly changes the former. Third, considering the optimum splitting points, the left side of the curves is semiexponentially descending, and the right side of the curves is semi-linearly ascending. This observation indicates that for small/large values of splitting point (smaller/larger than the optimum), the reads are dominated by the tags in the second/first comparison step.

The normalized number of reads in the first step linearly depends on the splitting point and is independent of the cache associativity. For large values of splitting points, the majority of tags are eliminated in the first step, which diminishes the contribution of the second step to the total reads. For very small values of the splitting point, a large fraction of tags contributes in the second step, which exponentially decreases by a slight increase in the value of the splitting point.

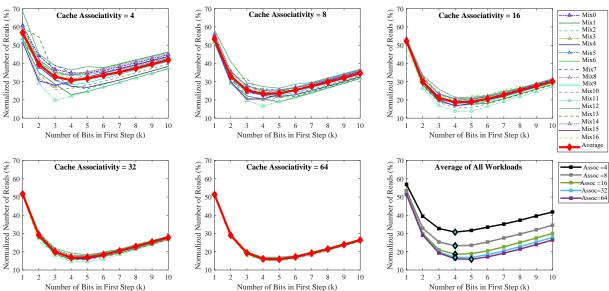

### C. Comparison of Experiments and Formulations

Fig. 5 provides a match between the experiments and formulations. Considering the average curve of all workloads

| 8-way                                                                             |       |                                                                 |      |       |          |           |       |       | 16-way                |       |         |           |          |       |       |                                                                      |       |      |

|-----------------------------------------------------------------------------------|-------|-----------------------------------------------------------------|------|-------|----------|-----------|-------|-------|-----------------------|-------|---------|-----------|----------|-------|-------|----------------------------------------------------------------------|-------|------|

| AddrLen                                                                           | 32    | 36                                                              | 40   | 44    | 48       | 52        | 56    | 60    | 64                    | 32    | 36      | 40        | 44       | 48    | 52    | 56                                                                   | 60    | 64   |

| Decoder                                                                           | 0.05  | 0.05                                                            | 0.05 | 0. 16 | 0.16     | 0.16      | 0. 16 | 0.16  | 0.16                  | 0.05  | 0.05    | 0.05      | 0. 16    | 0.16  | 0.16  | 0. 16                                                                | 0.16  | 0.16 |

| Wordline                                                                          | 0.11  | 0.13                                                            | 0.15 | 0.09  | 0.10     | 0.11      | 0.11  | 0.13  | 0. 14                 | 0. 11 | 0. 13   | 0.15      | 0.09     | 0. 11 | 0.12  | 0.13                                                                 | 0.14  | 0.15 |

| SA mux & drivers                                                                  | 0.05  | 0.07                                                            | 0.07 | 0.07  | 0.08     | 0.09      | 0.09  | 0.10  | 0.11                  | 0.08  | 0.10    | 0.11      | 0        | 0     | 0     | 0                                                                    | 0     | 0    |

| Bitlines precharge (pJ)                                                           | 0. 60 | 0.73                                                            | 0.86 | 0.52  | 0.59     | 0.65      | 0.65  | 0.78  | 0.84                  | 0.63  | 0.76    | 0.89      | 0.54     | 0.60  | 0.66  | 0.73                                                                 | 0.79  | 0.86 |

| Bitlines (pJ)                                                                     | 1.64  | 2.02                                                            | 2.41 | 2.70  | 3.07     | 3.44      | 3.44  | 4.19  | 4.56                  | 1.73  | 2.12    | 2.50      | 2.79     | 3.16  | 3.54  | 3.91                                                                 | 4.28  | 4.65 |

| SA (pJ)                                                                           | 0.49  | 0.61                                                            | 0.73 | 0.42  | 0.48     | 0.54      | 0.54  | 0.65  | 0.71                  | 0.52  | 0.64    | 0.76      | 0.44     | 0.49  | 0.55  | 0.61                                                                 | 0.67  | 0.73 |

| Sub-array output driver (pJ)                                                      | 0.08  | 0.09                                                            | 0.12 | 0.07  | 0.08     | 0.09      | 0.09  | 0.10  | 0.11                  | 0.17  | 0.20    | 0.23      | 0.14     | 0.16  | 0.18  | 0.19                                                                 | 0.21  | 0.22 |

| Total Dynamic                                                                     | 3.25  | 3.94                                                            | 4.64 | 4.30  | 4.84     | 5.38      | 5.38  | 6.45  | 6.99                  | 3.75  | 4.49    | 5.22      | 4.70     | 5.26  | 5.82  | 6.37                                                                 | 6.93  | 7.48 |

| Leakage(mW)                                                                       | 6.28  | 7.49                                                            | 8.68 | 10.30 | 11.51    | 12.71     | 12.71 | 15.11 | 16.30                 | 8.47  | 9.69    | 10.91     | 12.51    | 13.73 | 14.95 | 16.17                                                                | 17.38 | 18.5 |

| Cache Associativity = \$\frac{9}{8}\$ 60 8 9 50 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 |       | d Number of Reads (%)<br>00 00 00 00 00 00 00 00 00 00 00 00 00 |      | Cache | Associat | ivity = 8 |       |       | d Number of Reads (%) | \     | Cache A | ssociativ | ity = 16 |       |       | Mix0<br>Mix1<br>Mix2<br>Mix3<br>Mix4<br>Mix5<br>Mix6<br>Mix7<br>Mix8 |       |      |

TABLE IV: Details of energy parameters in the tag array for a 256 KB cache considering various address lengths.

Fig. 4: The number of tag reads as a function of splitting points for various cache associativity in all workloads.

in each configuration as the representative of the experiments, their conformity to the formulated values is illustrated. Three columns of subfigures in Fig. 5 depict the results for cache sizes of 256KB, 512KB, and 1MB, and five rows are related to cache associativities of 4 to 64. Nine solid/dotted lines in each subfigure are for experiments/formulations considering the address lengths from 32-bit to 64-bit in the stride of 4.

Considering each subfigure in Fig. 5, three main observations are evident. First, the tag reads that reduction is greater for larger address lengths. As an example, the normalized number of reads in the 256KB four-way cache (subfigure in upper-left corner) is about 30% for an address length of 32bit and is further decreased to 18% for a 64-bit address. The justification for this observation is that the tag partitioning approach reduces the number of reads by eliminating the tags from the second step of tag comparison and address length only affects the number of reads in the second step for a specific splitting point; address length has no effect on the number of bits reads in the first step of tag comparison, which is the common part of reads in the baseline and partitioned tag. With the same reasoning, the gaps between curves of different address lengths get wider for larger splitting points since the effect of eliminating a tag from the second step of the comparison is higher in longer addresses. Second, the optimum splitting point is almost the same in experimental

and formulated curves. Third, and more interestingly, better matching between experimental and formulated curves is observed around the optimum splitting point. By moving away from the optimum point, the pair of curves diverges.

Considering each column of subfigures in Fig. 5 depicting the results for different cache associativities in specific cache sizes, two key phenomena are observed. First, a higher matching between pairs of curves, i.e., experiments and formulations, is observed for smaller cache associativities. Note that even in the worst-case matching, the optimum splitting point is still the same in pairs of curves. Second, the reduction in the number of reads is larger in higher associativities for all cache sizes and all address lengths. This is in accordance with the observation already discussed in Fig. 4.

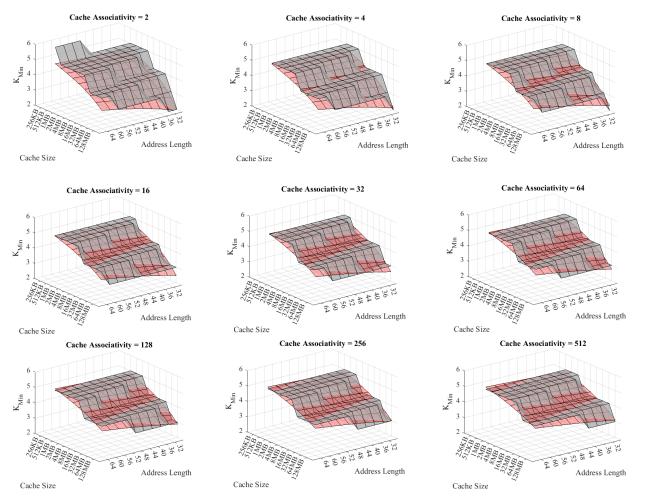

## D. Sensitivity of Optimum Point to Cache Configuration

After justifying the agreement of formulations with the experiments for different cache configurations, Fig. 6 is constructed to deeper investigate how the optimum splitting point is theoretically affected by the cache configuration parameters for a very wide range of configuration values. Considering each subfigure for specific cache associativity, there are two surfaces, a smooth one and a stairstep one. The stairstep surface represents optimum splitting points derived from Eq. (10) (calculates the number of reads for various splitting

Fig. 5: Number of tag reads as a function of splitting points for experiments and formulations in various address lengths and cache size and associativity.

Fig. 6: Optimum splitting point  $(K_{min})$  derived from Eq. (8), i.e., stairstep surfaces, and Eq. (11), i.e., smooth surfaces, for a wide range of cache sizes, associativities, and address lengths.

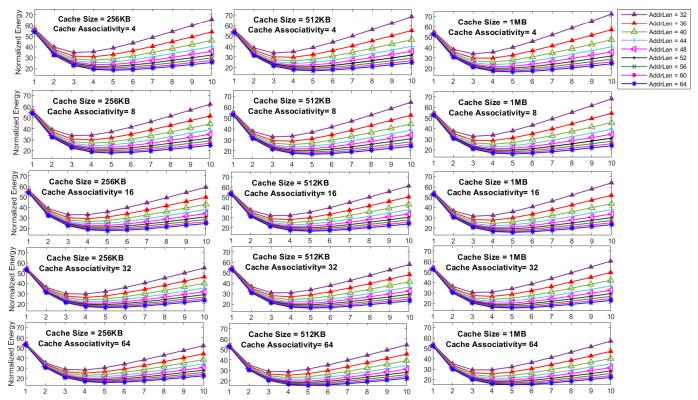

Fig. 7: The effect of tag splitting point on energy consumption in various cache sizes, associativities, and address lengths.

points). This is done by finding k with minimum output, which practically must be an integer value. The smooth surface represents the optimum splitting points calculated using Eq. (11), i.e., the point at which the derivative in Eq. (10) is zero. Theoretically, this point could have any real value. The x-axis in Fig. 6 is the cache size varying from 256KB to 128MB, and the y-axis is the address length ranging from 32-bit to 64-bit. The nine subfigures illustrate the results for cache associativities from 2 to 512.

Considering Fig. 6, the following observations are worthy of attention. First, it can be observed for each subfigure that the stairstep surface derived from Eq. (10) is equivalent to the round function of the smooth surface. Second, this is valid for all subfigures in that the optimum splitting point gets smaller by increasing the cache size and gets larger by increasing the address length. Considering Eq. (10), which is a function of splitting point, tag length, and associativity, both cache size and address length only affect the tag length. Tag length gets smaller by increasing the cache size and/or decreasing the address length. Both of these changes lead to an increase in the optimum splitting point, which can also be expected from Eq. (11). Third, the sensitivity of the optimum splitting point to cache size and address length diminishes in larger cache associativities. As is evident, the surfaces become flatter in higher-associative caches.

In summary, our evaluations demonstrate a very close match between the formulations and the experiments, which is a justification for the formulations. Considering a very wide range of cache configurations, the observations show that the optimum splitting point varies from 2 in a 2-way associative 256KB cache with an address length of 64-bit to 6 in a

2-way associative 128MB cache with an address length of 32-bit. Therefore, for today's realistic cache configurations, the optimum splitting point resides between 3 and 5. The interesting fact for this range is that, as observed in Fig. 5, the final reduction in the number of reads is very close to the optimum point and its neighboring values. Therefore, considering the safe range of [3, 5], it can be guaranteed that a very close to maximum read reduction is achieved.

# E. Energy Consumption

Fig. 7 depicts the effect of read reduction on the SRAMbased tag energy consumption for various cache configurations. While a small fraction of tag energy consumption is independent of the number of bits read, e.g., set indexing, its majority is affected by tag partitioning, and hence, by the proper selection of the splitting point. Compared to the baseline, the trend in energy reduction corresponds to that of the reduction in the number of reads. Again, a higher reduction is observed for longer address lengths and higher associativities. Considering the 4-way associative 256KB cache, the maximum energy consumption reduction (on the optimum splitting point) is 66% for 32-bit address length and gradually increases for longer addresses up to 82% for 64-bit address length. Energy consumption reduction in the 32-way associative cache with a size of 256KB is 71% and 84% in address lengths of 32- and 64-bit, respectively. On the other hand, if not properly selecting the tag splitting point, the tag energy consumption can increase as high as twice the optimum point in some configurations.

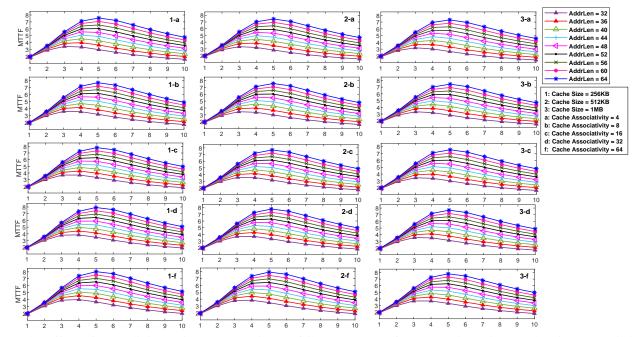

Fig. 8: The effect of tag splitting point on mean-time-to-failure (MTTF) of tag array in various cache sizes, associativities, address lengths.

TABLE V: Details of STT-MRAM cells parameters.

| Parameter                                  | Value  | Parameter                           | Value                               |

|--------------------------------------------|--------|-------------------------------------|-------------------------------------|

| $\overline{Write\; Current\; (I_{write})}$ | 2 mA   | Critical Current (I <sub>C0</sub> ) | 250 μΑ                              |

| Write Pulse (t <sub>write</sub> )          | 10 ns  | Bohr Magneton ( $\mu_B$ )           | $9.274 \times 10^{-24} \text{ J/T}$ |

| Read Pulse (twrite)                        | 1 ns   | Attempt Period $(\tau)$             | 1 ns                                |

| Read Current ( $I_{read}$ )                | 100 μΑ | Magnetic Momentum (m)               | $1.6 \times 10^{-16} \text{ J/T}$   |

| Euler Constant (c)                         | 0.5772 | Electron Charge (e)                 | $1.6021 \times 10^{-19} \mathrm{C}$ |

| Thermal Stability Factor $(\Delta)$        | 30     | Tunneling Spin<br>Polarization      | 50%                                 |

## F. Reliability Analysis

In addition to energy consumption reduction, tag partitioning reduces the error rate of STT-MRAM-based tag arrays. As the metric of tag reliability, we report the Mean-Time-To-Failure (MTTF) of the tag array using the framework presented in [27]. There are three sources of errors in STT-MRAM tag, i.e., read disturbance, retention failure, and write failure, all of them affected by process variation. Considering the 32nm technology node, device- and circuit-level parameters of STT-MRAM cache for MTJ thermal stability factor and read current, and Gaussian distribution of process variation, Table V reports the related cache parameters and per-cell error rates. Considering three sources of errors, read disturbance is the main source of unreliability in the tag array due to its frequent read accesses. On the other hand, tag partitioning mainly affects read disturbance rate by reducing the number of reads, which has a direct effect on error rate reduction. To calculate the MTTF, we take into account the total probability of error occurrence per tag cell during read operations. During the workload execution, all read accesses to the tag cell have been considered, and the cache reliability for a workload is defined as the probability of error-free data read for all tag accesses. Given the reliability and execution time, and

TABLE VI: Summary of the tag splitting point value and selection method in previous work.

|      |                 | T =           | T               |             |

|------|-----------------|---------------|-----------------|-------------|

| Ref. | Splitting Point | Cache Level   | Used Method     | Efficiency  |

| [5]  | 7               | L1 and L2     | Experimental    | 81.5        |

| [6]  | 6               | L1            | Experimental    | 89.2        |

| [14] | 4               | L2            | Experimental    | 96.9        |

| [17] | 3               | L1            | Experimental    | 100         |

| [20] | 4               | L1            | Randomize       | 93.7        |

| [21] | 4, 5, 7         | L1            | Randomize       | 96.8 (best) |

| [28] | 8               | L2            | Experimental    | 75.7        |

| [29] | 1               | L1            | Randomize       | 71.8        |

| [30] | 1, 2, 3, 4, 5   | BTB near L1-I | Experimental    | 100 (best)  |

| [31] | 0, 1, 2, 3      | L1-D          | Static analysis | 100 (best)  |

| [32] | 3               | L2            | Experimental    | 100         |

| [34] | 3               | L1            | Experimental    | 100         |

| [35] | 3, 4            | L1            | Experimental    | 100 (best)  |

| [36] | 5               | L1            | Experimental    | 94.4        |

| [37] | 1               | L1-I          | Static analysis | 72.4        |

| [38] | 6               | L1            | Experimental    | 89.7        |

| [39] | 4               | L2            | Randomize       | 97.6        |

assuming exponential distribution for reliability with error rate parameter  $\lambda$ , the MTTF for each workload is the inverse of  $\lambda$ .

Fig. 8 illustrates the MTTF of the tag array considering various cache configurations and tag splitting points, normalized to the baseline. The observations indicate that higher MTTF enhancement is achieved in the longer address lengths and higher cache associativities. MTTF is enhanced by 3.4x and 7.8x in a 4-way associative 256KB cache in address lengths of 32- and 64-bit on the optimum splitting point of 3 and 5, respectively. On the other hand, the proper selection of the tag splitting point has again a significant effect on the MTTF improvement by tag partitioning. Considering a single cache configuration, the blue curve in subfigure 2-d, for example, the MTTF enhancement is reduced from 7.9x to 5.6x when the splitting point is moved from the optimum point of 5 to an unsuitable point of 9.

In summary, the evaluations confirm the alignment of the formulations with the experiments, enabling a theoretical determination of the optimal tag splitting point with high accu-

| TABLE VII. Thining details of data and tag arrays for a 250KB cache in various address |                         |       |       |       |       |       |       |       |       |       | 1699   | icngt | 115.  |       |       |       |       |       |       |  |

|----------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--|

|                                                                                        |                         |       | 8-way |       |       |       |       |       |       |       | 16-way |       |       |       |       |       |       |       |       |  |

|                                                                                        | AddrLen                 | 32    | 36    | 40    | 44    | 48    | 52    | 56    | 60    | 64    | 32     | 36    | 40    | 44    | 48    | 52    | 56    | 60    | 64    |  |

|                                                                                        | Data array (ns)         | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076  | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 | 1.076 |  |

|                                                                                        | Tag array (ns)          | 0.213 | 0.220 | 0.227 | 0.279 | 0.282 | 0.286 | 0.286 | 0.293 | 0.297 | 0.213  | 0.220 | 0.228 | 0.279 | 0.282 | 0.286 | 0.289 | 0.293 | 0.297 |  |

| ا ج                                                                                    | Decoder + wordline (ns) | 0.129 | 0.131 | 0.134 | 0.154 | 0.156 | 0.157 | 0.157 | 0.160 | 0.161 | 0.130  | 0.132 | 0.135 | 0.155 | 0.156 | 0.157 | 0.159 | 0.160 | 0.162 |  |

| rray                                                                                   | Bitline (ns)            | 0.055 | 0.057 | 0.058 | 0.099 | 0.099 | 0.100 | 0.100 | 0.102 | 0.102 | 0.056  | 0.057 | 0.059 | 0.099 | 0.100 | 0.100 | 0.101 | 0.102 | 0.103 |  |

| ₹₹                                                                                     | Sense Amplifier (ns)    | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003  | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 | 0.003 |  |

$0.027 \ 0.029 \ 0.031 \ 0.033 \ 0.035 \ 0.037 \ 0.037 \ 0.041 \ 0.043 \ 0.027 \ 0.029 \ 0.031 \ 0.033 \ 0.035 \ 0.037 \ 0.039 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.041 \ 0.04$

$0.026 \ 0.029 \ 0.032 \ 0.023 \ 0.024 \ 0.026 \ 0.026 \ 0.029 \ 0.030 \ 0.026 \ 0.029 \ 0.032 \ 0.023 \ 0.024 \ 0.026 \ 0.027 \ 0.029 \ 0.030$

TABLE VII: Timing details of data and tag arrays for a 256KB cache in various address lengths.

racy during the early design stage. These formulations eliminate the need for exhaustive searches to find a suitable splitting point or for its random selection, which can compromise efficiency. Our observations indicate that the optimal splitting point is not significantly influenced by workload behavior due to the randomness in the combination of lower order bits of tags in a cache set, but rather by the cache configuration. Table VI presents details of prior work on tag partitioning, including their selected splitting point, cache level, and the method of acquisition. Due to the lack of a reliable formulation, some methods have identified the appropriate point by examining various cases, while others have considered a random point that was sometimes fortuitously close to the optimal point.

Comparator (ns)

H-tree output (ns)

Tag splitting necessitates minor modifications to the cache controller and tag wiring with negligible area and energy overheads to achieve significant energy savings. However, accessing the tag array in two steps does increase tag access latency. This increase in latency does not affect cache access time as long as the total tag operations conclude before the data array access operation is completed. As reported in [14], the latency of tag operations, in both conventional and splitting configurations, is lower than the data array latency across various cache sizes and associativities. Hence, the increase in tag splitting point has no impact on read cycles, overall cache latency, or the energy consumption of other cache components. Table VII illustrates the timing parameters of a 256KB L2 cache for 8- and 16-way associativities and different address lengths. Tag partitioning doubles the delays related to the two highlighted rows since the tag bits are accessed and compared in two phases. Because the access time of the data array is significantly greater than that of the tag array, this increase in tag array delay does not affect cache performance.

#### V. CONCLUSION

Tag array in set-associative on-chip cache memory contributes to a large fraction of energy consumption and vulnerability to errors because of very frequent and parallel read accesses. Tag partitioning as a well-known approach has been utilized in several studies to reduce the number of reads from the tag array by splitting the tag comparison operation into two steps, in which very few lower order tag bits of all cache ways in the target set are activated in the first step and only the partially matched ways are activated in the second comparison step. Although the value of the tag-splitting point is the key factor in the efficiency of the tag partitioning-based scheme, there is no investigation on the proper selection of this parameter and its effects in the existing studies. This paper formulated the tag partitioning efficiency to find the optimum

point of tag splitting and conducted comprehensive analysis and experiments for a wide range of system configurations to validate the accuracy of the proposed formulation. This formulation makes the designers and researchers capable of determining the optimum tag-splitting point at the early design stage and precisely estimating the tag partitioning efficiency for energy consumption and error rate reduction.

#### REFERENCES

- B. Peccerillo, E. Cheshmikhani, M. Mannino, A. Mondelli, and S. Bartolini, "Ixiam: Isa extension for integrated accelerator management," *IEEE Access*, vol. 11, pp. 33768–33791, 2023.

- [2] N. M. Barbhuiya, P. Das, and B. R. Roy, "Cache memory and on-chip cache architecture: A survey," in *International Conference on Advanced Computing, Machine Learning, Robotics and Internet Technologies*, pp. 126–138, Springer, 2023.

- [3] E. Cheshmikhani, B. Peccerillo, A. Mondelli, and S. Bartolini, "A general framework for accelerator management based on isa extension," *IEEE Access*, vol. 10, pp. 120702–120713, 2022.

- [4] M. Mavropoulos, G. Keramidas, and D. Nikolos, "Improving the performance predictability of faulty data caches," in *European Dependable Computing Conference (EDCC)*, pp. 123–130, 2024.

- [5] M. Kim, I.-J. Chang, and H.-J. Lee, "Segmented tag cache: A novel cache organization for reducing dynamic read energy," *IEEE Transac*tions on Computers, vol. 68, no. 10, pp. 1546–1552, 2019.

- [6] S. Rostami-Sani, M. Valinataj, and S. A. Chamazcoti, "Parloom: A new low-power set-associative instruction cache architecture utilizing enhanced counting bloom filter and partial tags," *Journal of Circuits, Systems and Computers*, vol. 28, no. 12, p. 1950203, 2019.

- [7] H. Farbeh, L. Delshadtehrani, H. Kim, and S. Kim, "Ecc-united cache: Maximizing efficiency of error detection/correction codes in associative cache memories," *IEEE Transactions on Computers*, vol. 70, no. 4, pp. 640–654, 2020.

- [8] L. Pons, J. Sahuquillo, V. Selfa, S. Petit, and J. Pons, "Phase-aware cache partitioning to target both turnaround time and system performance," *IEEE Transactions on Parallel and Distributed Systems*, vol. 31, no. 11, pp. 2556–2568, 2020.

- [9] M. Didehban, H. So, P. Gali, A. Shrivastava, and K. Lee, "Generic soft error data and control flow error detection by instruction duplication," *IEEE Transactions on Dependable and Secure Computing*, vol. 21, no. 1, pp. 78–92, 2024.

- [10] P. Papavramidou and M. Nicolaidis, "Reducing power dissipation in memory repair for high fault rates," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 31, no. 12, pp. 2112–2125, 2023.

- [11] S. G. Ghaemi, I. Ahmadpour, M. Ardebili, and H. Farbeh, "Smartag: Error correction in cache tag array by exploiting address locality," in Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 1658–1663, 2018.

- [12] X. Gao, N. Cui, J. Nian, Z. Liang, J. Gao, H. Liu, and M. Yang, "Rebec: A replacement-based energy-efficient fault-tolerance design for associative caches," *Future Generation Computer Systems*, vol. 155, pp. 39–52, 2024.

- [13] H. Farbeh, F. Mozafari, M. Zabihi, and S. G. Miremadi, "Raw-tag: Replicating in altered cache ways for correcting multiple-bit errors in tag array," *IEEE Transactions on Dependable and Secure Computing*, vol. 16, no. 4, pp. 651–664, 2017.

- [14] E. Cheshmikhani, H. Farbeh, and H. Asadi, "3rset: Read disturbance rate reduction in stt-mram caches by selective tag comparison," *IEEE Transactions on Computers*, vol. 71, no. 6, pp. 1305–1319, 2021.

- [15] E. Cheshmikhani, H. Farbeh, and H. Asadi, "Enhancing reliability of stt-mram caches by eliminating read disturbance accumulation," in *Design*, Automation & Test in Europe Conference & Exhibition (DATE), pp. 854–859, 2019.

- [16] M. D. Powell, A. Agarwal, T. Vijaykumar, B. Falsafi, and K. Roy, "Reducing set-associative cache energy via way-prediction and selective direct-mapping," in ACM/IEEE International Symposium on Microarchitecture (MICRO), pp. 54–65, IEEE, 2001.

- [17] R. Min, W. Jone, and Y. Hu, "Phased tag cache: An efficient low power cache system," in *IEEE International Symposium on Circuits and Systems (ISCAS)*, vol. 2, pp. II–805, 2004.

- [18] K. Inoue and H. Amano, "psas/c: Pseudo set associative and shared with competitive cache," *Electronics and Communications in Japan (Part II: Electronics)*, vol. 86, no. 9, pp. 76–84, 2003.

- [19] C. Zhang, F. Vahid, and W. Najjar, "A highly configurable cache architecture for embedded systems," in *Annual International Symposium* on *Computer Architecture (ISCA)*, pp. 136–146, 2003.

- [20] L. Liu, "Cache designs with partial address matching," in Annual international symposium on Microarchitecture, pp. 128–136, 1994.

- [21] C. Zhang, F. Vahid, J. Yang, and W. Najjar, "A way-halting cache for low-energy high-performance systems," ACM Transactions on Architecture and Code Optimization (TACO), vol. 2, no. 1, pp. 34–54, 2005.

- [22] K. A. Zubair, R. Abdullah, D. Mohaisen, and A. Awad, "Rc-nvm: Recovery-aware reliability-security co-design for non-volatile memories," *IEEE Transactions on Dependable and Secure Computing*, vol. 21, no. 4, pp. 1817–1830, 2024.

- [23] M. Hadizadeh, E. Cheshmikhani, M. Rahmanpour, O. Mutlu, and H. Asadi, "Copa: Cold page awakening to overcome retention failures in stt-mram based i/o buffers," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 10, pp. 2304–2317, 2021.

- [24] E. Cheshmikhani, H. Farbeh, and H. Asadi, "Robin: Incremental oblique interleaved ecc for reliability improvement in stt-mram caches," in Asia and South Pacific Design Automation Conference, pp. 173–178, 2019.

- [25] M. Hadizadeh, E. Cheshmikhani, and H. Asadi, "Stair: High reliable stt-mram aware multi-level i/o cache architecture by adaptive ecc allocation," in *Design, Automation & Test in Europe Conference & Exhibition* (DATE), pp. 1484–1489, 2020.

- [26] H. Asadi, E. Cheshmikhanikhanghah, and H. Farbeh, "Preventing read disturbance accumulation in a cache memory," Feb. 15 2022. US Patent 11.249.841.

- [27] E. Cheshmikhani, H. Farbeh, and H. Asadi, "A system-level framework for analytical and empirical reliability exploration of stt-mram caches," *IEEE Transactions on Reliability*, vol. 69, no. 2, pp. 594–610, 2019.

- [28] H. Park, S. Yoo, and S. Lee, "A novel tag access scheme for low power 12 cache," in *Design, Automation & Test in Europe*, pp. 1–6, 2011.

- [29] T. Juan, T. Lang, and J. J. Navarro, "The difference-bit cache," in Proceedings of the 23rd annual international symposium on Computer architecture, pp. 114–120, 1996.

- [30] B. Fagin, "Partial resolution in branch target buffers," *IEEE Transactions on Computers*, vol. 46, no. 10, pp. 1142–1145, 1997.

- [31] P. Petrov and A. Orailoglu, "Data cache energy minimizations through programmable tag size matching to the applications," in *International* symposium on Systems synthesis, pp. 113–117, 2001.

- [32] H. Park, S. Yoo, and S. Lee, "A multistep tag comparison method for a low-power 12 cache," *IEEE transactions on computer-aided design of integrated circuits and systems*, vol. 31, no. 4, pp. 559–572, 2012.

- [33] H. Asadi and E. Cheshmikhanikhanghah, "Reducing read disturbance error in tag array," Aug. 30 2022. US Patent 11,430,499.

- [34] R. Min, Z. Xu, Y. Hu, and W.-B. Jone, "Partial tag comparison: A new technology for power-efficient set-associative cache designs," in *International Conference on VLSI Design*, pp. 183–188, 2004.

- [35] J. Chen, R. Peng, and Y. Fu, "Low power set-associative cache with single-cycle partial tag comparison," in *International Conference on ASIC*, vol. 1, pp. 73–77, IEEE, 2005.

- [36] J. W. Kwak and Y. T. Jeon, "Compressed tag architecture for low-power embedded cache systems," *Journal of Systems Architecture*, vol. 56, no. 9, pp. 419–428, 2010.

- [37] J. Gu, H. Guo, and P. Li, "An on-chip instruction cache design with one-bit tag for low-power embedded systems," *Microprocessors and Microsystems*, vol. 35, no. 4, pp. 382–391, 2011.

- [38] J. H. Choi, J. W. Kwak, S. T. Jhang, and C. S. Jhon, "Data filter cache with partial tag matching for low power embedded processor," *IEICE Transactions on Information and Systems*, vol. 97, no. 4, pp. 972–975, 2014

- [39] S. P. Park, S. Gupta, N. Mojumder, A. Raghunathan, and K. Roy, "Future cache design using stt mrams for improved energy efficiency: Devices,

- circuits and architecture," in Annual Design Automation Conference (DAC), pp. 492–497, 2012.

- [40] J. Lowe-Power, A. M. Ahmad, A. Akram, M. Alian, R. Amslinger, M. Andreozzi, A. Armejach, N. Asmussen, B. Beckmann, S. Bharadwaj, et al., "The gem5 simulator: Version 20.0+," arXiv preprint arXiv:2007.03152, 2020.

- [41] J. Bucek, K.-D. Lange, and J. v. Kistowski, "Spec cpu2017: Next-generation compute benchmark," in *Companion of the ACM/SPEC International Conference on Performance Engineering*, pp. 41–42, 2018.

Elham Cheshmikhani is an assistant professor at the Department of Computer Science and Engineering at Shahid Beheshti University, Tehran, Iran. She also served as an assistant professor at the Department of Computer Engineering at Amirkabir University of Technology (Tehran Polytechnic), Tehran, Iran, from September 2022 to September 2023. Her educational background includes a B.Sc., M.Sc., and Ph.D. degrees in Computer Engineering from the Iran University of Science and Technology (IUST), Amirkabir University of Technology (Tehran Poly-

technic), and Sharif University of Technology (SUT) respectively, obtained in the years 2011, 2013, and 2020. From January 2021 to September 2022, she worked as a postdoctoral researcher at the Department of Information Engineering and Mathematics at the University of Siena, Siena, Italy. During her postdoctoral research, she collaborated with Huawei R&D (UK) Ltd. She was a member of the Design and Analysis of Dependable Systems (DADS) at Tehran Polytechnic from 2011 to 2015 and a member of the Dependable Systems Laboratory (DSL) at SUT from 2016 to 2018, and the Data Storage, Networks & Processing Laboratory (DSN) at SUT from 2018 to 2021. Her research interests encompass emerging nonvolatile memory technologies, processing-in-memory, RISC-V ISA design, hardware accelerators, SoC design, dependable systems design, and storage systems. Notably, she achieved the Best Paper Award at IEEE/ACM Design, Automation, and Test in Europe (DATE) in 2019.

Hamed Farbeh received the B.Sc., M.Sc., and Ph.D. degrees in computer engineering from Sharif University of Technology (SUT), Tehran, Iran, in 2009, 2011, and 2017, respectively. He was a member of the Dependable Systems Laboratory (DSL) at SUT from 2007 to 2017, was with the Embedded Computing Laboratory (ECL), KAIST, Daejeon, South Korea, as a Visiting Researcher from October 2014 to May 2015, and collaborated with the Institute of Research for Fundamental Sciences (IPM), Tehran, Iran, as Postdoc fellow from May 2017 to January

2018. He is currently a faculty member of the Department of Computer Engineering, Amirkabir University of Technology (Tehran Polytechnic-AUT), Tehran, Iran, where he established the Intelligent Computing and Communication Infrastructure Laboratory (ICCI) and is the director of Computer Systems Architecture and Networks (CSAN) group. He is also a member of the board of the Cyber-Physical Systems Society of Iran (CPSSI) since 2018. His current research interests include reliable memory hierarchy, emerging memory technologies, AI processors, and cyber-physical systems.