# LLaMCAT: Optimizing Large Language Model Inference with Cache Arbitration and Throttling

Zhongchun Zhou\*

zzhouch@connect.ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

Chengtao Lai\*

claiaf@connect.ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

Wei Zhang<sup>†</sup>

eeweiz@ust.hk

The Hong Kong University of Science

and Technology

Kowloon, Hong Kong

### **Abstract**

Large Language Models (LLMs) have achieved unprecedented success across various applications, but their substantial memory requirements pose significant challenges to current memory system designs, especially during inference. Our work targets last-level cache (LLC) based architectures, including GPUs (e.g., NVIDIA GPUs) and AI accelerators. We introduce LLaMCAT, a novel approach to optimize the LLC for LLM inference. LLaMCAT combines Miss Status Holding Register (MSHR)- and load balance-aware cache arbitration with thread throttling to address stringent bandwidth demands and minimize cache stalls in KV Cache access. We also propose a hybrid simulation framework integrating analytical models with cycle-level simulators via memory traces, balancing architecture detail and efficiency.

Experiments demonstrate that LLaMCAT achieves an average speedup of 1.26x when the system is mainly bottlenecked by miss handling throughput, while baselines mostly show negative improvements since they are not optimized for this scenario. When the cache size is also limited, our policy achieves a speedup of 1.58x over the unoptimized version, and a 1.26x improvement over the best baseline (dyncta). Overall, LLaMCAT is the first to target LLM decoding-specific MSHR contention, a gap in previous work. It presents a practical solution for accelerating LLM inference on future hardware platforms.

### **CCS** Concepts

• Computer systems organization  $\rightarrow$  Architectures; • Computing methodologies  $\rightarrow$  Machine learning; Modeling and simulation.

### **Keywords**

Cache, AI Accelerator, Large Language Model

# **ACM Reference Format:**

Zhongchun Zhou, Chengtao Lai, and Wei Zhang. 2025. LLaMCAT: Optimizing Large Language Model Inference with Cache Arbitration and Throttling. In *Proceedings of 54th International Conference on Parallel Processing (ICPP*

$<sup>^{\</sup>dagger}$ Corresponding author

This work is licensed under a Creative Commons Attribution 4.0 International License. ICPP '25, San Diego, CA, USA

© 2025 Copyright held by the owner/author(s). ACM ISBN 979-8-4007-2074-1/2025/09 https://doi.org/10.1145/3754598.3754671 '25). ACM, New York, NY, USA, 10 pages. https://doi.org/10.1145/3754598. 3754671

#### 1 Introduction

The advancement of large language models (LLMs) has prompted experts in electronic design automation and computer architecture to explore innovative methodologies and chip designs optimized for efficient LLM processing. Despite the diverse applications, LLMs share consistent computational characteristics. They typically adopt a decoder-only transformer architecture and use algorithmic techniques such as KV Cache and Group-Query Attention (GQA) [1]. This uniformity in their algorithmic patterns facilitates the development of domain-specific architectures (DSAs).

LLM inference is primarily bounded by memory bandwidth, making the performance of the memory system a critical factor. This challenge presents an opportunity to design domain-specific and sophisticated architectures that address the distinctive memory and bandwidth requirements of LLMs. However, both consumer- and server-grade chips need a certain degree of generality to adapt to the rapid change of workloads, which limits the utilization of domain-specific accelerators. Consequently, a more practical approach is to integrate the domain-specific design into the existing architecture and share a substantial portion of the system resources with the other components of the chip, such as the NVIDIA Tensor Core and the NPUs used in high-end consumer-grade chips [6, 22] recently. The last-level cache (LLC) is usually one of these shared system resources mentioned above with a significant impact on overall performance.

This paper thus focuses on optimizing the LLC for LLM inference, especially the memory-bound decoding stage. While traditional cache research has focused heavily on data reuse, LLM workloads exhibit structured data access patterns within dense GEMV or GEMM operators but impose stringent demands on memory-level parallelism and bandwidth. Therefore, our work shifts the focus to optimizing the Miss-Handling Architecture (MHA), which consists of Miss Status Handling Registers (MSHRs) and multiple queues. Efficient MHA utilization is critical, as resource depletion can lead to cache stalls. We address this by improving arbitration policies and introducing a novel throttling mechanism specifically designed for LLM workloads. This approach balances core and memory system interactions, reducing contention and improving overall performance.

Existing AI accelerator performance evaluation toolchains, typically classified into (1) analytical models or (2) cycle-accurate simulators, are often inadequate for LLM-specific research due to the large data sizes of LLMs and hardware architectural complexity. This work thus proposes a framework based on an existing

<sup>\*</sup>Both authors contributed equally to this research.

toolchain that combines the strengths of both types to facilitate LLM chip research.

In short, this work makes the following contributions:

- We look into the underlying mechanisms of "cache bandwidth" and identify the key factors that determine its utilization. We also show that MSHR can be more efficient in capturing temporal locality than cache storage;

- We design a 2-level dynamic multi-gear throttling policy to have a fine and accurate control over the throttling decisions, in order to relieve contention in the memory subsystem;

- To enhance the miss handling throughput of caches, we propose a method to predict the future behavior of memory requests in the arbiter, thereby improving MSHR utilization.

- We propose a hybrid framework that integrates an AI accelerator analytical model with a cycle-level simulator by generating memory traces, enabling more accurate performance statistics.

### 2 Background and Motivation

Four key factors drive our work:

- (1) LLCs are widely used in LLM inference devices, and they play a crucial role in adapting to algorithmic advances. Although scratchpad memories (SPMs) are generally considered more suitable for DNNs, GPUs and consumer-grade SoCs typically employ LLCs in their designs, due to the diversity of workloads. It is inevitable to optimize LLC for LLM inference in order to benefit from more application scenarios.

- (2) Previous cache-based research has focused primarily on data reuse, with limited attention to optimizing cache bandwidth utilization and ensuring load balance via arbitration. However, LLM inference is typically bandwidth-bound.

- (3) The Miss-Handling Architecture (MHA) holds significance in terms of cache bandwidth utilization, although it does not directly enhance the cache hit rate. Contention in the MHA can lead to cache stalls, which can adversely impact overall system performance.

- (4) Load balancing and appropriate throttling reduce contention and boost performance. Various methods can jointly improve temporal locality and reduce the chance of cache overflow by properly limiting the working set size - a mechanism we reveal in our experiments.

### 2.1 LLM Inference and KV Cache

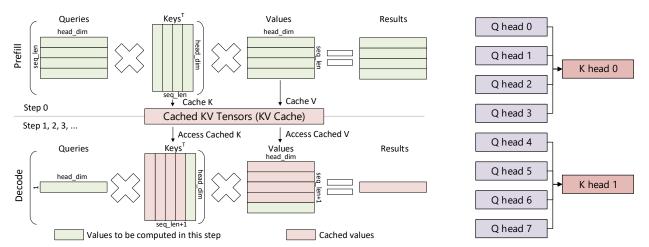

Recent advancements have aimed to improve the efficiency of LLM inference, which primarily relies on the auto-regressive, decoder-only transformer architecture. Inference computation can be divided into two stages: Prefill and Decode. The inference process begins with the Prefill stage, which computes the initial Key (K) and Value (V) tensors for the input prompt. In each step afterwards, the model takes in the result of the previous step and generates one token based on K and V tensors of all previous tokens, including the KV tensors of the input tokens computed in Prefill and any new ones computed until the current time step. To avoid repetitive computation, the KV tensors are stored in memory (so called KV Cache); In each time step, new KV tensors are concatenated to existing ones. This process is shown in Fig. 1.

The Decode stage is the most time-consuming and memory access-intensive phase of LLM inference. As demonstrated in [21], it dominates the execution time and is highly memory-bound due to frequent memory accesses to the KV Cache and an extremely low computation-memory access ratio (Utilization of GPU compute units can be lower than 1%). Given that the memory-boundness is primarily attributed to KV Cache access rather than the intermediate results, state-of-the-art operator fusion techniques such as FLAT [10] and FlashAttention [23] are not appropriate for this scenario. Efficiently managing these memory accesses is crucial to reducing the overall inference latency.

### 2.2 Group-Query Attention (GQA)

To alleviate the memory bottleneck associated with KV Cache, recent research has introduced Group-Query Attention (GQA), which optimizes memory usage by reducing the size of KV Cache. GQA allows multiple query heads to share a single head of KV tensors, effectively reducing the memory footprint without significantly impacting model accuracy, as illustrated in Fig. 2.

While GQA alleviates memory pressure, it cannot fundamentally resolve the memory bounding issue. The GQA operator employed during the decoding stage remains memory intensive, indicating that our research remains pertinent for such workloads.

Given the adoption of GQA in contemporary LLMs such as Llama3 [4], Gemma2 [24], and numerous state-of-the-art LLMs, we incorporate GQA-based workloads into our experiments to substantiate the efficacy of our proposed cache optimization techniques for LLM inference.

### 2.3 Optimizing Cache Bandwidth Utilization

For data-intensive workloads, bandwidth can be more critical than latency. Broadly speaking, cache bandwidth comprises two aspects: the bandwidth of SRAM itself and the capability of handling misses. During cache hits, SRAM bandwidth takes the lead. When cache misses occur, MHA is responsible for storing these outstanding requests and thus prevents the whole cache from being stalled (when cache misses are within a reasonable limit). Compared to optimizing for a higher cache hit rate, the improvement in MHA is much less explored in previous works. The two aspects are also orthogonal to each other: techniques for the latter can be applied together with those for the former.

As described in Intel® 64 and IA-32 Architectures Optimization Reference Manual [7], the cache system employs various queues to service various requests from processors and memory controllers, such as the Global Queue (GQ) in the Intel L3 cache system design. Previous research [2, 3] categorizes these queues into two types: request queues, which are responsible for servicing requests from the processor; and response queues, which are responsible for servicing data from the memory controller. These works optimize system performance by managing the request scheduling scheme and priority between the request queues and response queues in conjunction with request bypass to achieve higher system bandwidth. We optimize these arbitration techniques for LLM workloads and finally achieve better performance compared to the baselines.

Figure 1: KV Cache Mechanism

## 2.4 Impact of Miss-Handling Architecture

When MSHRs are exhausted, the cache pipeline will stall, preventing even cache hits from being processed. MSHRs have two key dimensions: numEntry, representing distinct outstanding cache misses, and numTarget, representing requests that can be merged. Cache stalls occur when either dimension is full. It is usually preferred to increase numEntry occupancy while preventing stalls, as numEntry directly influences DRAM bandwidth utilization.

## 2.5 Thread Throttling

Thread throttling is effective in mitigating memory system contention by limiting the processor's front-end throughput. The throttling decision involves three dimensions:

- (1) **Temporal**: The frequency at which the throttling decision should be modified during execution.

- (2) **Spatial**: The number of cores to which the throttling policy should be applied.

- (3) **Degree**: The extent to which cores should be throttled.

Varying any of these dimensions can have substantial effects on system performance. Previous research [11] proposes a dynamic throttling logic that applies throttling to all cores. Each core monitors its idle cycles ( $C_{idle}$ ) and memory contention-related stall cycles ( $C_{mem}$ ) independently using its own performance counters. If a core is excessively idle, it relaxes its throttling degree. Conversely, if memory contention is severe (which can be inferred from  $C_{mem}$ ), it increases its throttling degree. In their experiments, the best rate to adjust the throttling degree (i.e., the number of cycles between each throttling degree adjustment) is acquired through parameter sweeping. However, their method does not handle the spatial dimension, potentially losing an opportunity of finer control. In contrast, our throttling policy allows the number of throttled cores to be dynamically adjusted based on the system contention degree. In addition, the best parameters in their method are obtained by sweeping through a large set of general workloads. If the target workloads are known in advance, e.g., LLM inference in our scenario, the parameters can also be improved.

**Figure 2: Group-Query Attention**

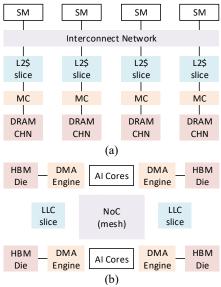

Figure 3: Example architectures applicable to this work. (a) GPGPU (b) Datacenter-level AI SoC from [16]. SM: Stream Multiprocessor; MC: Memory Controller; CHN: Channel.

# 3 System Architecture

### 3.1 Overall System Architecture

Fig. 3 (a) and (b) show the block diagrams of a typical datacenter-level GPU and an AI SoC with system-level caches. Since the dataflow and reuse pattern of NN operators are known at compilation time, both types leverage SPMs in their in-core datapaths. GPU stream multiprocessors (SMs) feature a shared memory that is configurable between SPM and L1 cache, while each DaVinci core of Ascend 910 [16] contains complex datapaths fully composed of SPMs. Despite these differences inside the cores, both include a hardware-managed shared L2 cache. As per FlashAttention-3 [23], "data from global memory gets transparently cached into an on-chip L2 cache". This makes the differences between these cores less critical for predominantly memory-bound LLM inference. To model the runtime scheduling mechanism in these cores, we adopt an

assumption commonly seen in both types. In each core, we model multiple instruction windows, each of which is assigned a set of instructions once at a time. To align with the terminologies in GPUs, we also call this set of instructions "thread block". During execution, to hide memory access latency, when an instruction window is full, the core will automatically switch to another to continue execution. Programmers only have control over the sizes and number of thread blocks, instead of the scheduling algorithms.

### 3.2 Baseline LLC Architecture

We adopt an LLC architecture commonly used in previous works [3, 9], as shown in Fig. 4. In datacenter-level chips mentioned in Section 3.1, LLC is usually sliced and physically distributed across the chip. In our setting, we slice the LLC across the cache set dimension, i.e., each slice contains several cache sets. An LLC slice works as follows: (1) a memory request travels through the interconnect and reaches the request queue. For illustrative purposes, we model the request queue as part of the arbiter. (2) The arbiter selects a proper request from the queue and performs cache lookup. If it is a hit, the result is immediately returned to the requesting core (return path not shown); (3) otherwise, it further checks MSHR whether the same address is already pending for DRAM response. If so, the request is merged into that entry. Otherwise, a new entry is opened, and a new memory request is sent to the DRAM. Note this MSHR reservation process will fail if there are not enough resources, and in that case the whole cache pipeline will stall. (4)&(4') When the request is returned by DRAM, MSHR will first be examined to get the requester(s), and a copy of the data will be directly forwarded to them, while another is pushed into the cache response queue. This ensures that the upstream cores will not wait for the request to travel through the response queue, which may delay their execution. The corresponding MSHR entry is also freed in this phase. (5) When a response dequeues, a bypass manager decides whether to keep the cache line. If not, the data will not be written into cache storage. Since this work is orthogonal to bypass logic design, we do not consider bypassing for fairness and clarity.

# 3.3 Request-response Arbitration

The architectural constraints of the system necessitate careful arbitration between requests and responses, particularly due to the shared nature of certain critical resources. Specifically, as illustrated in Fig. 4, both the request path (2) and the response path (5) contend for access to the same cache storage. To manage this contention, a request-response arbitration policy is required. An effective approach, as shown in [3], is to prioritize requests over responses, and only when the response queue is full, requests and responses are served in turn. Another approach is to prioritize responses over requests, whenever there is a response to be processed. Experiments reveal that our proposed architectural enhancements yield similar performance gains under both request-response arbitration policies. Without loss of generality, we demonstrate the result of using the latter (response-queue-first) in Section 6.

### 4 CAT: Cache Arbitration and Throttling

The main idea of our arbiter design is three-fold: (1) explicitly control MHA to serve the cores on an equivalent basis; (2) throttle

Figure 4: System assumption. Only 1 LLC slice and its corresponding arbiter is shown for simplicity. A slice comprises 1 or more cache sets. Items in red are our design, while others are the baseline. THRTL CTRL: throttling control unit; cnt: counter for the number of requests served for each core.

the cores whose requests are served more by MHA; (3) make full use of the limited resources in MHA, by using information from LLC and MSHR to guide request selection.

### 4.1 Arbiter: Serving Cores Fairly

By default, arbiters serve requests on a first-come, first-served basis. Requests served earlier may consume the limited memory resources, potentially causing imbalance between cores. We introduce progress counters to track requests served for each core. The counters are reset at the beginning of each operator execution. Under this mode, the arbiter always picks the request whose requester has the smallest counter value. This policy is named "B" (balanced).

### 4.2 Dynamic Thread Throttling

To effectively explore the three-dimensional throttling search space (Section 2.5) for our workload, we highly parameterize the throttling controller design. This design facilitates parameter sweeping across all dimensions and enables dynamic throttling decisions during execution. Besides, we implement a two-level throttling controller: A global multi-gear throttling and an in-core throttling controller, named "two-level dynamic multi-gear throttling" (dynmg).

The global dynamic multi-gear throttling controller, illustrated in Table 1, throttles the fastest cores (i.e., those with the largest progress counter values) for load balancing. The gear dynamically changes based on the current system contention degree. Table 3 shows the criteria for classifying contention degree, obtained through parameter sweeping. Algorithm 1 shows the multi-gear throttling control logic. High contention triggers a higher gear, while low contention drives the system to a lower gear.

The dynamic policy discussed in the previous paragraph addresses the spatial dimension of throttling decisions, while the **intra-core throttling decisions still need to be made**. Here we adopt an assumption of throttling the cores similar to the DYNCTA method [11]: If a core is throttled, its maximum running thread

Algorithm 1 Dynamic Multi-Gear Throttling for Cache Contention

```

qear: Current throttling gear

max qear: Maximum allowable gear

contention status: Current contention level

sampling_period: Duration of one sampling period

1: Initialize qear \leftarrow 0

2: while system is running do

Wait for next sampling_period

3:

Adjust Gear Based on Contention:

if contention_status == High_Contention then

5:

if gear < max_gear then

6:

gear \leftarrow gear + 1

7:

end if

8:

else if contention_status == Low_Contention then

9:

if gear > 0 then

10:

gear \leftarrow gear - 1

11:

12:

else if contention_status == Extreme_Contention then

13:

if gear \le max\_gear - 2 then

14:

gear \leftarrow gear + 2

15:

else

16:

gear \leftarrow max\_gear

17:

end if

18:

end if

19:

20: end while

```

blocks will be limited. But in our design, we divide each sampling period at the global level into several sub-periods, and decisions on the number of running thread blocks are made in each sub-period. During each sub-period, each core records the number of cycles where all thread blocks wait for memory access ( $C_{mem}$ ). If the cycle count exceeds a threshold, the core reduces the maximum number of running thread blocks ( $max\_tb$ ) by one. Conversely, if the cycle count falls below the threshold, the core increments  $max\_tb$  by one. It also records the number of idle cycles ( $C_{idle}$ ). If this cycle count is too high, the core increments  $max\_tb$  by one.

In summary, our in-core throttling controller incorporates two innovative features compared to the original DYNCTA design: (1) Using DYNCTA as a local logic to throttle individual cores, rather than all cores simultaneously. (2) Introducing two-level sampling periods, where the sampling period in DYNCTA corresponds to the sub-period. Through parameter sweeping, an optimal throttling configuration is identified (Table 2 and Table 4).

# 4.3 Arbiter: Select Requests Based on LLC and MSHR Information

The previous two policies aim to maintain balance and slow down the overly-issued cores, while this one opts for efficient utilization of MSHR resources. **Different from request-response arbitration** in Section 3.3, here we focus on determining the order of selecting requests from the request queue to send to LLC.

4.3.1 Motivation and Hardware Units Added. We notice two facts regarding LLC behavior: (1) cache hits will not lead to a cache stall;(2) cache and MSHR lookup latencies of MSHR hit requests can overlap with DRAM latency since this address is already pending

Table 1: Multi-gear throttling

| ge  | ar   | function                            |

|-----|------|-------------------------------------|

|     | ar 0 | No throttling                       |

| gea | ar 1 | throttle 1/8 of the processor cores |

|     | ar 2 | throttle 1/4 of the processor cores |

| gea | ar 3 | throttle 1/2 of the processor cores |

| gea | ar 4 | throttle 3/4 of the processor cores |

Table 2: Optimal throttling configuration

| Domain   | parameter                     | value       |

|----------|-------------------------------|-------------|

| Temporal | Sampling period               | 2000 cycles |

| Temporal | Sub-period                    | 400 cycles  |

| Spatial  | Maximum gear                  | gear 4      |

| Degree   | Maximum running thread blocks | dynamic     |

**Table 3: Cache contention classification**

| Contention degree | Criterion: $t_{cs}$ range |

|-------------------|---------------------------|

| Low               | [0, 0.1)                  |

| Normal            | [0.1, 0.2)                |

| High              | [0.2, 0.375)              |

| Extremely High    | [0.375, 1]                |

$t_{cs} := \text{proportion of cache stall cycles}$

Table 4: In-core throttling controller parameters

| Parameter             | Value (cycles) |

|-----------------------|----------------|

| Cidle upper bound     | 4              |

| $C_{mem}$ upper bound | 250            |

| $C_{mem}$ lower bound | 180            |

for DRAM response by definition. Suppose that the request arrives later and the previous one has been returned from DRAM, it will become a cache hit. A cache hit would require some extra cycles (hit-latency) before it can be returned to the core. So we conjecture that prioritizing cache hits and MSHR hits can benefit the system by allowing more requests to be sent to the cache before it stalls and reducing average memory access latency.

We propose a hardware solution to **identify these types of requests** before actual cache or MSHR lookup (i.e., prediction): adding a hit\_buffer (FIFO) to record recent cache hits and using MSHR information (MSHR\_snapshot+ sent\_reqs). The hit\_buffer is updated once a new cache hit is determined, while MSHR\_snapshot is passed to the arbiter through a direct wire connection, so it is a real-time summary of the MSHR.

Cache hits can be speculatively recognized by querying the hit\_buffer. For MSHR hits, recall that it takes several cycles (hitlatency) to perform cache lookup, and if a cache miss occurs, it will take some extra cycles (mshr-latency) to lookup the address in MSHR. Thus a newly-sent request causing cache & MSHR miss will only appear in MSHR and MSHR\_snapshot after hit-latency+mshrlatency. However, during this period, the information about this request is absent from MSHR\_snapshot, without which the arbiter will make suboptimal decisions based on outdated status. To this end, we propose sent\_reqs (FIFO) to keep track of these newly sent requests in aid of MSHR\_snapshot. A request is designed to be dequeued from sent\_regs after hit-latency+mshr-latency, since it will have been updated in MSHR at that time. When our arbiter queries for speculated MSHR information related to an address, these structures should offer a hint on whether the address is already in the MSHR to help identify MSHR hits.

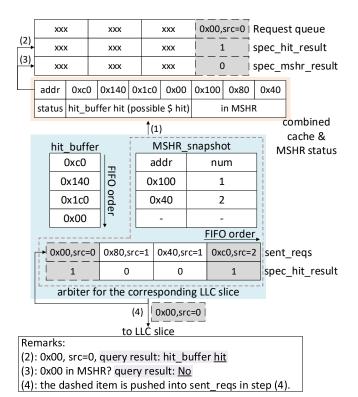

4.3.2 Overall Flow of Request Selection. Please refer to Fig. 5 for this process. When the arbiter begins to select a request from the request queue, it will first combine information from the hit\_buffer,

Figure 5: The process of selecting a request from the request queue and updating sent\_reqs. spec\_hit\_result: speculated hit result. In this example, 0x00 and 0xc0 are inferred as cache hits (colored in grey), so they are not counted when estimating MSHR entries used.

MSHR\_snapshot and sent\_reqs into a list (step 1), where each address is annotated with a status. The type of a request depends on whether it appears in this list. After that, for each element in the request queue, the arbiter looks up the hit\_buffer-related section in the list and generates a spec\_hit\_result bit (step 2). This result indicates the arbiter's speculation on the request being a cache hit. It also looks up the MSHR-related section and checks whether this address is already in MSHR (step 3). When a request is finally chosen (step 4), it is pushed back into sent\_reqs with the spec\_hit\_result bit. When combining MSHR\_snapshot and sent\_reqs, this bit acts as a mask: If it is 1, the corresponding request will not be counted, since MSHR is not involved in cache hits.

4.3.3 Arbitration Policy. Our policy can be described as rules to rank the priority of requests. It chooses the request with the highest rank to send to the cache:

- An inferred cache hit is assigned the highest priority;

- An inferred MSHR hit is assigned the second highest;

- If the above criteria produce a tie, use a tie-breaking mechanism, which could be either the default request arbitration method or the result of balanced request arbitration (both described in Section 4.1).

Later in the experiments, we call the policy with default request arbitration "MSHR-aware arbitration" (MA) and the one referring to the balanced result "Balanced MA" (BMA).

### 5 Simulation Framework

Simulation frameworks are crucial for designing and verifying novel hardware architectures. However, current open-source simulators face limitations when applied to LLM inference. Cycle-accurate simulators of accelerators like SMAUG [26] are slow and lack extensibility, especially for large-scale LLM workloads. While they provide detailed intra-core modeling, this level of detail is unnecessary for memory-bound LLM inference [10], where the focus should be on global memory performance. Furthermore, SMAUG lacks native support for transformers, requiring operator extensions for LLM simulation. Flexibility of the simulator is another concern when performing architecture exploration. Furthermore, simulators like Accel-Sim [12], built upon the GPGPU-Sim framework, present significant hurdles for our research since their design is tightly coupled with detailed replication of specific GPU microarchitectures. These simulators deeply embed GPU-specific assumptions, such as fixed warp sizes, complex warp scheduling logic, and memory coalescing mechanisms based on thread IDs, adding unnecessary complexity and rigidity to our study focused on optimizing shared LLC behavior. Critically, Accel-Sim relies on executing compiled GPU programs (e.g., PTX code), and this dependency on actual kernel code severely hinders efficient dataflow exploration; manually rewriting and compiling GPU kernels for each dataflow variant is far more time-consuming and error-prone compared to studying memory subsystem impacts using traces generated from analytical tools like Timeloop, and is constrained by the GPU programming model itself. Therefore, our hybrid simulation framework, driven by memory traces, more effectively decouples the study of LLC and memory system from the intricacies of specific core implementations, offering greater flexibility and efficiency for our purposes.

On the other hand, AI accelerator analytical models such as Timeloop [20] provide fast emulation, useful for early-stage design exploration, but they oversimplify memory behavior, often assuming a stall-free environment. Most of them also lack cache support, making them unsuitable for cache-related research. Although LCM [14] includes a cache model, it reduces cache behavior to mathematical formulas, limiting its ability to validate architectural innovations. To make matters worse, the presence of a cache may break apart contiguous memory accesses to DRAM, leading to crucial DRAM events like row buffer miss. This makes it inappropriate to compute average bandwidth simply with weighted harmonic mean of SRAM and DRAM bandwidth.

The analyses above point out that research on AI accelerators with caches calls for sufficient details of cache and DRAM components such as queues, write, allocation and replacement policies, as well as major DRAM events. It also has to be light-weight enough to simulate a whole LLM operator within reasonable time. These demands drive us to memory trace-driven, light-weight, cycleaccurate simulators like Ramulator2.0 [17]. We keep its DRAM modeling completely unchanged, while dramatically expanding its original Simple03 frontend, including the following major changes:

Dataflow: spatial & temporal mapping of each tiled loop dimension Trace: cycles of each non-memory operations, memory access addresses, R/W

### Figure 6: Flowchart of the simulation framework

- Modify each SimpleO3Core to a vector core with a width of 128 elements to align with the head dimension in popular transformer models. Since each thread in a vector group executes commands synchronously, their memory requests can be coalesced by default. This allows us to reduce memory requests by more than an order of magnitude.

- Enable a runtime scheduling mechanism that resembles a warp scheduler in GPUs. We model multiple instruction windows in a SimpleO3Core. During runtime, a "thread block" is first assigned to each instruction window. When one is full, the scheduler can switch to another to execute.

- Introduce a mechanism to send the thread blocks in the trace file of a slow core to a fast core. This is a compensation to the drawback of the original Ramulator2 modeling that each core can only run on its own trace file, which cannot model global scheduling policies that a thread block can be assigned to any cores. Without this feature, our baselines would be underestimated since fast cores have to wait a long time before the slowest core ends.

- Add cache policies like allocate-on-fill, write-no-allocate, writethrough, while originally Ramulator2 only supports allocate-onmiss, write-allocate, write back. L1&L2 caches usually have different design considerations.

- Split L2 into multiple slices, each of which consists of a number of cache sets.

- Model request and response queues and an arbiter that explicitly selects the transaction to feed to L2.

To get the memory traces to drive each simulated vector core, we first use Timeloop to generate a mapping of the operator for a given architecture. Since a mapping by definition is a hierarchy of nested loops mapped to either the spatial or temporal domain, it can be translated to memory traces simply by iterating through it. Since the mapping file produced by Timeloop is human-readable, our flow also accepts handwritten mapping dataflows, which is essentially equivalent to adding constraints to Timeloop mapper. We have written a script to seamlessly automate this flow (Fig. 6).

# 6 Experiments and Results

### 6.1 Hardware Cost Evaluation

We implement our design in Chisel HDL, and then synthesize the design with Synopsys design compiler and 15nm library[18]. The target frequency is 1.96 GHz. All other configurations are as in Table 5. Synthesis results show that our arbiter and hit buffer have an area of  $7312.93\mu m^2$  and  $3088.61\mu m^2$ , respectively. The design of the arbiter includes the request queue of the cache since they are logically an indivisible unit. The area of the arbiter should be significantly larger than the actual overhead for this reason.

**Table 5: Simulated System Configurations**

| Basics                  | frequency=1.96GHz, 16 cores, 16MB L2 cache, 8 L2 slices                                                                                                                       |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core                    | inst_window_depth=128, num_inst_windows=4                                                                                                                                     |

|                         | 1 core=1 vector unit + private L1 cache, vector-len=128B                                                                                                                      |

| L1 cache                | line-size=64B, associativity=8, 64KB, latency=1, alloc-on-fill,                                                                                                               |

|                         | streaming, write-no-allocate, write-through                                                                                                                                   |

| L2 slice                | associativity=8, hit-latency=3, data-latency=25, mshr-<br>num-entry=6 (per slice), num-target=8, mshr-latency=5,<br>alloc-on-fill, write-allocate, write-back, req_q_size=12, |

|                         | resp_q_size=64                                                                                                                                                                |

| L2 req-resp arbitration | response-queue-first                                                                                                                                                          |

| DRAM                    | DDR5_8Gb_x16, 4 ranks, DDR5-3200, 4 channels                                                                                                                                  |

# 6.2 Experiment Setup

6.2.1 Hardware configuration. A recent industrial trend is the increasing use of consumer-grade devices to run LLMs. Some vendors have announced that their state-of-the-art edge platforms can even run Llama3 70b at a decent generation speed. The simulated hardware setting is listed in Table 5, which is applicable to both high-end consumer-grade devices and cloud chips.

Since the policies of concern will display totally different characteristics when the system bottleneck changes, our discussion is divided mainly into two parts according to the sufficiency of L2 cache size (Section 6.3 and 6.4).

6.2.2 Benchmarks. Since our main focus is to alleviate the memory bottleneck related to KV cache access, we test our design against the Logit operator  $(QK^T)$ . Computation of this operator is executed across multiple head groups (H), head group sizes (G), sequence lengths (L), and dimensions per head (D). The operator sizes are set according to Llama3 70b (H=8,G=8,D=128) and Llama3 405b (H=8,G=16,D=128). Although Llama3 405b is too large for our current experimental setup, it can be deployed for inference across multiple cards in a pipeline-parallel fashion. Additionally, testing different operator shapes can validate the broad applicability of our improvements.

We add two constraints to the dataflow: (1) assign the fastest axis to each vector core, ensuring cache line access is complete; and (2) map at least 64B of elements in the L dimension to the innermost L1 cache temporal level to avoid false sharing of AttScore among cores. We divide each trace file into contiguous thread blocks for runtime scheduling. Each thread block covers at least 1 cache line of output to avoid false sharing, but larger blocks reduce locality and performance. Empirically, the best performance is achieved when each thread block covers 1-2 output cache lines. Satisfying these constraints results in a hardware-friendly workload that performs well on the unoptimized architecture.

6.2.3 Baselines. We employ baselines of both throttling (DYNCTA [11], LCS [15]) and cache arbitration (COBRRA [3]) to validate the efficacy of our policies. These baselines are introduced in Section 7. For those requiring parameter sweeping, we have also swept under our experiment settings for a fair comparison.

## 6.3 Efficacy of Throttling and Arbitration

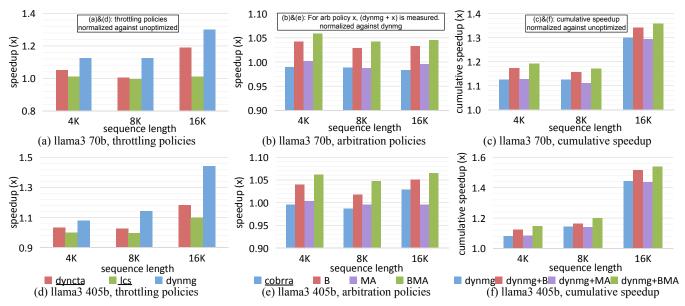

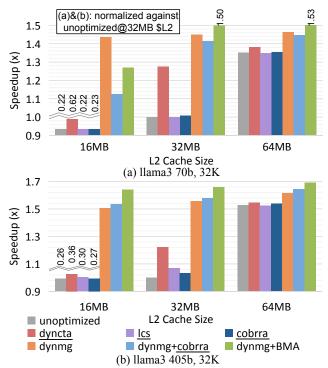

6.3.1 Throttling policies. Fig. 7(a)&(d) compare our policy (dynmg) with baseline throttling methods. Speedups are independently normalized against unoptimized versions. Our policy shows 1.08-1.44x speedups (geomean 1.19x), while under most circumstances baseline "lcs" does not show meaningful improvements, indicating it is not well-adapted to this scenario. This also applies to baseline

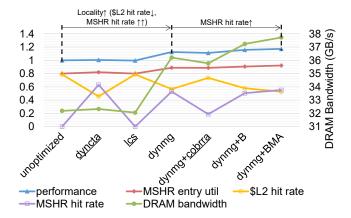

Figure 7: Speedups of the Logit operator. All baselines are underlined in the legend. B: balanced; MA: MSHR-aware arbitration. Each policy in (b)&(e) is aided with "dynmg".

"dyncta" under shorter sequence lengths. It turns out that these baselines are too conservative: Fig. 8 will show that their MSHR entry utilization remains almost unchanged compared with the unoptimized version. As Section 6.4 will show, these baselines perform better when cache size is also among the bottlenecks. In contrast, our policy can still excavate additional performance gains when workloads are mostly bounded by miss handling throughput.

6.3.2 Cache Arbitration Policies. Since arbitration policies are orthogonal to throttling in previous works, here we aid all arbitration policies with the best throttling method (dynmg), to better showcase their joint effect. Fig. 7(b)&(e) compare our versions with baseline "cobrra". Speedups are computed by dividing the performance of using each policy with dynmg by that of using dynmg only. We observe that the baseline still causes a performance degradation in most cases. It turns out that the baseline arbitration strategy maintains a stable performance when enabling or disabling throttling. This makes its speedup superseded by that of the throttling policy.

The results also reveal that "B" and "MA" need to work together to achieve more improvement. Employing only one of them can also lead to performance degradation. This is because the result of MA sometimes conflicts with the idea of making a fair arbitration among requesters. By returning the result of "B" when MA produces a tie, the unfairness is compensated to some extent. Over all cases, our BMA policy produces a speedup of 1.04-1.07x (geomean 1.05x).

6.3.3 Core Mechanism of Improvement. Here we discuss how our policies (unoptimized  $\rightarrow$  dynmg  $\rightarrow$  dynmg+BMA) produce a speedup in such a scenario. Fig. 8 lists some other key statistics for analysis. We first notice the number of DRAM accesses does not change dramatically across all policies, but MSHR hit rate keeps improving (annotated for unoptimized, dynmg and dynmg+BMA). In this circumstance, DRAM bandwidth and the throughput of miss handling

Figure 8: Detailed comparison among policies for llama3 70b 8K benchmark. MSHR entry util: numEntry occupancy throughout execution.

will take the lead, as shown by the strong correlation among performance, MSHR entry utilization, and average DRAM bandwidth.

Cache and MSHR hit rates, on the other hand, contribute to performance in a more complex mechanism. MSHR hit rate is defined as the number of requests merged to an existing entry divided by the number of cache misses. Cache hits and MSHR hits can convert to each other depending on the timing of requests. In our experiments, they are mostly a result of GQA, since non-GQA operators do not share activation across heads. By properly throttling the cores (unoptimized—dynmg), the locality of memory requests is enhanced, as shown by the reduced cache hit rate but dramatically increased MSHR hit rate. Hence what we have done at this stage is to properly throttle the cores to enhance temporal locality (and will reduce L2 cache overflow in Section 6.4), while still maintaining a reasonable pace to issue memory requests such that

Figure 9: Throttling and arbitration policies running with 32K sequence.

the cores themselves will not become the bottleneck. After that, by adopting cache arbitration policies (dynmg—dynmg+BMA), MSHR hit rate continues to increase, while cache hit rate keeps decreasing, both in a mild manner. The reason of optimizing towards this direction is that the MSHR lookup latency of an MSHR hit can be overlapped with DRAM latency, while cache lookup latency of a cache hit cannot. In other words, **MSHR can be more efficient in capturing temporal locality than cache storage**. As shown in Fig. 7(c)&(f), our final policy (dynmg+BMA) delivers a speedup of 1.15-1.54x (geomean 1.26x).

# 6.4 When Workloads Become Larger

Real-world applications may require a longer context length. Longer sequences induce larger working sets, thus imposing more pressure on the cache size. In this section, we will demonstrate that our policy is more resistant to performance degradation caused by limited L2 cache sizes. To achieve this goal, we set the cache size around the original while running 32K sequences for both benchmarks (only 16K in the previous section).

Fig. 9 shows the execution time of the operator using multiple throttling and arbitration policies. We notice as the cache size varies, performance of the unoptimized version changes dramatically, while that of our policy nearly saturates at 16MB. The unoptimized version's demand for larger caches stems from its runtime scheduling mechanism: Each instruction window is assigned a thread block, and a core will switch to another instruction window upon stalls. Since the assigned thread blocks may span a wide range, constraining instruction window switching is effective in reducing the working set.

Among baselines, dyncta achieves notable speedups over the unoptimized version at 16MB and 32MB but its superiority diminishes at 64MB, suggesting it is better suited for cache-constrained scenarios. Similarly, cobrra outperforms the unoptimized version at 32MB, but its gains diminish at 16MB and 64MB. The dynmg+cobrra combination also outperforms dynmg for the llama3 405b model. In contrast, our final policy, dynmg+BMA, delivers the highest speedup across all cases since it is also capable of efficiently utilizing MSHR resources to enhance miss handling throughput, with the only exception of llama3 70b @16MB. In summary, under the 32MB configuration, our final policy achieves a speedup of 1.50-1.66x (geomean 1.58x) over the unoptimized version, and a 1.18-1.35x (geomean 1.26x) improvement over the best baseline (dyncta).

### 7 Related Works

# 7.1 On-Chip Memory Optimization for AI Accelerators

Previous research on optimizing on-chip buffers for AI workloads focuses on either scratchpad memory (SPM) management or cache management. Software frameworks like Pin-or-Fuse [8] and On-SRAM [19] enhance SPM utilization, but cache-based systems cannot directly benefit from these. LCM [14] optimizes cache usage for LLM inference by improving data reuse within the cache but overlooks load balancing and bandwidth optimization. Additionally, it does not consider advanced LLM inference techniques such as Group-Query Attention and KV Cache optimization.

### 7.2 Last-Level Cache Arbitration

While cache replacement policies have been extensively studied to optimize data reuse, few works address bandwidth optimization and scheduling among cores in the LLC. COBRRA [3] demonstrates that maximizing cache hit rate does not guarantee optimal performance, highlighting limitations in previous research. REAL [25] schedules shared LLC bandwidth based on the LLC instruction density in each core's Reorder Buffer. COBRRA combines cache bypassing and arbitration to reduce cache contention and improve system performance. POEM [2] aggressively bypasses cache writeback to reduce cache contention and also optimizes the endurance of NVM cache. However, these works focus on traditional CPU applications and do not address cache stalls caused by MSHR reservation failures.

### 7.3 Miss Handling Architecture

Most prior works target the utilization of MSHR numEntry. For example, [13] dynamically adjusts GPU warp scheduling: employing higher thread parallelism when few MSHR entries are reserved and lower parallelism when occupancy is high. DL-MSHR [5] mitigates stalls from insufficient numTargets by redesigning MSHRs into a list structure, but this incurs significant architectural changes, hardware costs, and additional latency. MRPB [9] addresses numEntry insufficiency through request prioritization but does not tackle limitations related to numTarget.

### 7.4 Thread Throttling

Our experiments show that throttling alone does not fully optimize performance, but is more effective when combined with other

strategies. We focus on integrating throttling with an MSHR-aware cache arbitration policy, not discussed in previous works. DYNCTA [11] dynamically monitors runtime statistics to adjust the number of active thread blocks based on memory system contention and core busyness. In contrast, LCS [15] improves throttling by observing the execution of the first thread block to calculate the optimal number of thread blocks without dynamic tuning.

### 8 Conclusion

We introduce LLaMCAT, a comprehensive approach to optimizing the LLC for LLM inference. By synergistically combining MSHR-and load balance-aware cache arbitration with dynamic thread throttling, it effectively addresses the stringent bandwidth demands and improves overall performance. It achieves a geometric mean speedup of 1.26x when the system is mainly bottlenecked by miss handling throughput, while the baselines mostly cause a performance degradation since they do not optimize for this scenario. When cache size is also a bottleneck, it reaches a speedup of 1.58x, 1.26x over the best baseline. This proves that our enhancements are crucial for future hardware platforms aiming to efficiently handle the memory-bound nature of LLMs.

Moreover, we presented a hybrid simulation framework that bridges the gap between AI accelerator analytical models and cycle-level simulators. This framework, which generates memory traces from dataflow produced by analytical models, offers a flexible and efficient means to evaluate architectural innovations for LLMs, addressing the limitations of existing simulation tools.

### Acknowledgments

This work is partially funded by Hong Kong RGC GRF 16214123 and AI Chip Center for Emerging Smart Systems (ACCESS).

#### References

- Joshua Ainslie, James Lee-Thorp, Michiel de Jong, Yury Zemlyanskiy, Federico Lebrón, and Sumit Sanghai. 2023. GQA: Training Generalized Multi-Query Transformer Models from Multi-Head Checkpoints. arXiv:2305.13245 [cs.CL] https://arxiv.org/abs/2305.13245

- [2] Aritra Bagchi, Dharamjeet, Ohm Rishabh, Manan Suri, and Preeti Ranjan Panda. 2024. POEM: Performance Optimization and Endurance Management for Nonvolatile Caches. ACM Trans. Des. Autom. Electron. Syst. 29, 5, Article 79 (Sept. 2024), 36 pages. doi:10.1145/3653452

- [3] Aritra Bagchi, Dinesh Joshi, and Preeti Ranjan Panda. 2024. COBRRA: COntention-aware cache Bypass with Request-Response Arbitration. ACM Trans. Embed. Comput. Syst. 23, 1, Article 12 (jan 2024), 30 pages. doi:10.1145/3632748

- [4] Abhimanyu Dubey, Abhinav Jauhri, Abhinav Pandey, Abhishek Kadian, Ahmad Al-Dahle, Aiesha Letman, et al. 2024. The Llama 3 Herd of Models. arXiv:2407.21783 [cs.AI] https://arxiv.org/abs/2407.21783

- [5] Yongbin Gu and Lizhong Chen. 2019. Dynamically linked MSHRs for adaptive miss handling in GPUs. In Proceedings of the ACM International Conference on Supercomputing (Phoenix, Arizona) (ICS '19). Association for Computing Machinery, New York, NY, USA, 510–521. doi:10.1145/3330345.3330390

- [6] Intel. 2023. Intel Accelerator Engines. https://www.intel.com/content/www/us/en/products/docs/accelerator-engines/overview.html

- [7] Intel. 2024. Intel® 64 and IA-32 Architectures Optimization Reference Manual Volume 1. https://www.intel.com/content/www/us/en/content-details/671488/intel-64-and-ia-32-architectures-optimization-reference-manual-volume-1.html

- [8] Hyuk-Jin Jeong, JiHwan Yeo, Cheongyo Bahk, and JongHyun Park. 2023. Pin or Fuse? Exploiting Scratchpad Memory to Reduce Off-Chip Data Transfer in DNN Accelerators. In Proceedings of the 21st ACM/IEEE International Symposium on Code Generation and Optimization (Montréal, QC, Canada) (CGO 2023). Association for Computing Machinery, New York, NY, USA, 224–235. doi:10.1145/3579990.3580017

- [9] Wenhao Jia, Kelly A. Shaw, and Margaret Martonosi. 2014. MRPB: Memory request prioritization for massively parallel processors. In 2014 IEEE 20th International Symposium on High Performance Computer Architecture (HPCA). 272–283.

- doi:10.1109/HPCA.2014.6835938

- [10] Sheng-Chun Kao, Suvinay Subramanian, Gaurav Agrawal, Amir Yazdanbakhsh, and Tushar Krishna. 2023. FLAT: An Optimized Dataflow for Mitigating Attention Bottlenecks. In Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2 (Vancouver, BC, Canada) (ASPLOS 2023). Association for Computing Machinery, New York, NY, USA, 295–310. doi:10.1145/3575693.357547

- [11] Onur Kayıran, Adwait Jog, Mahmut Taylan Kandemir, and Chita Ranjan Das. 2013. Neither more nor less: optimizing thread-level parallelism for GPGPUs. In Proceedings of the 22nd International Conference on Parallel Architectures and Compilation Techniques (Edinburgh, Scotland, UK) (PACT '13). IEEE Press, 157–166.

- [12] Mahmoud Khairy, Zhesheng Shen, Tor M Aamodt, and Timothy G Rogers. 2020. Accel-Sim: An extensible simulation framework for validated GPU modeling. In 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA). IEEE, 473–486.

- [13] Gwang Bok Kim, Jong Myon Kim, and Cheol Hong Kim. 2019. Mshr-aware dynamic warp scheduler for high performance GPUS. KIPS Transactions on Computer and Communication Systems 8, 5 (2019), 111–118.

- [14] Chengtao Lai, Zhongchun Zhou, Akash Poptani, and Wei Zhang. 2024. LCM: LLM-focused Hybrid SPM-cache Architecture with Cache Management for Multi-Core AI Accelerators. In Proceedings of the 38th ACM International Conference on Supercomputing (Kyoto, Japan) (ICS '24). Association for Computing Machinery, New York, NY, USA, 62–73. doi:10.1145/3650200.3656592

- [15] Minseok Lee, Seokwoo Song, Joosik Moon, John Kim, Woong Seo, Yeongon Cho, and Soojung Ryu. 2014. Improving GPGPU resource utilization through alternative thread block scheduling. In 2014 IEEE 20th International Symposium on High Performance Computer Architecture (HPCA). 260–271. doi:10.1109/HPCA. 2014.6835937

- [16] Heng Liao, Jiajin Tu, Jing Xia, Hu Liu, Xiping Zhou, Honghui Yuan, and Yuxing Hu. 2021. Ascend: a Scalable and Unified Architecture for Ubiquitous Deep Neural Network Computing: Industry Track Paper. In 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA). 789–801. doi:10. 1109/HPCA51647.2021.00071

- [17] Haocong Luo, Yahya Can Tuğrul, F Nisa Bostancı, Ataberk Olgun, A Giray Yağlıkçı, and Onur Mutlu. 2023. Ramulator 2.0: A modern, modular, and extensible dram simulator. IEEE Computer Architecture Letters 23, 1 (2023), 112–116.

- [18] Mayler Martins, Jody Maick Matos, Renato P. Ribas, André Reis, Guilherme Schlinker, Lucio Rech, and Jens Michelsen. 2015. Open Cell Library in 15nm FreePDK Technology. In Proceedings of the 2015 Symposium on International Symposium on Physical Design (Monterey, California, USA) (ISPD '15). Association for Computing Machinery, New York, NY, USA, 171–178. doi:10.1145/2717764. 2717783.

- [19] Subhankar Pal, Swagath Venkataramani, Viji Srinivasan, and Kailash Gopalakrishnan. 2022. OnSRAM: Efficient Inter-Node On-Chip Scratchpad Management in Deep Learning Accelerators. ACM Trans. Embed. Comput. Syst. 21, 6, Article 86 (oct 2022), 29 pages. doi:10.1145/3530909

- [20] Angshuman Parashar, Priyanka Raina, Yakun Sophia Shao, Yu-Hsin Chen, Victor A. Ying, Anurag Mukkara, Rangharajan Venkatesan, Brucek Khailany, Stephen W. Keckler, and Joel Emer. 2019. Timeloop: A Systematic Approach to DNN Accelerator Evaluation. In 2019 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). 304–315. doi:10.1109/ISPASS. 2019.00042

- [21] Jaehyun Park, Jaewan Choi, Kwanhee Kyung, Michael Jaemin Kim, Yongsuk Kwon, Nam Sung Kim, and Jung Ho Ahn. 2024. AttAcc! Unleashing the Power of PIM for Batched Transformer-based Generative Model Inference. In Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2 (La Jolla, CA, USA) (ASPLOS '24). Association for Computing Machinery, New York, NY, USA, 103–119. doi:10.1145/3620665.3640422

- [22] Qualcomm. 2023. Snapdragon X Elite. https://www.qualcomm.com/snapdragon/laptops

- [23] Jay Shah, Ganesh Bikshandi, Ying Zhang, Vijay Thakkar, Pradeep Ramani, and Tri Dao. 2025. Flashattention-3: Fast and accurate attention with asynchrony and low-precision. Advances in Neural Information Processing Systems 37 (2025), 68658–68685.

- [24] Gemma Team, Morgane Riviere, Shreya Pathak, Pier Giuseppe Sessa, Cassidy Hardin, Surya Bhupatiraju, et al. 2024. Gemma 2: Improving Open Language Models at a Practical Size. arXiv:2408.00118 [cs.CL] https://arxiv.org/abs/2408. 00118

- [25] Sakshi Tiwari, Shreshth Tuli, Isaar Ahmad, Ayushi Agarwal, Preeti Ranjan Panda, and Sreenivas Subramoney. 2019. REAL: REquest Arbitration in Last Level Caches. ACM Trans. Embed. Comput. Syst. 18, 6, Article 115 (nov 2019), 24 pages. doi:10.1145/3362100

- [26] Sam Xi, Yuan Yao, Kshitij Bhardwaj, Paul Whatmough, Gu-Yeon Wei, and David Brooks. 2020. SMAUG: End-to-end full-stack simulation infrastructure for deep learning workloads. ACM Transactions on Architecture and Code Optimization (TACO) 17, 4 (2020), 1–26.