# Assessing Large Language Models in Generating RTL Design Specifications

Hung-Ming Huang $^{\star,1}$ , Yu-Hsin Yang $^{\star,1}$ , Fu-Chieh Chang $^1$ , Yun-Chia Hsu $^2$ , Yin-Yu Lin $^2$ , Ming-Fang Tsai $^2$ , Chun-Chih Yang $^2$ , Pei-Yuan Wu $^1$ .

\*Equal contribution

$^1$ Graduate Institute of Communication Engineering, National Taiwan University, Taipei, Taiwan  $^2$ MediaTek Inc, Hsinchu, Taiwan

#### **Abstract**

As IC design grows more complex, automating comprehension and documentation of RTL code has become increasingly important. Engineers currently should manually interpret existing RTL code and write specifications, a slow and error-prone process. Although LLMs have been studied for generating RTL from specifications, automated specification generation remains underexplored, largely due to the lack of reliable evaluation methods. To address this gap, we investigate how prompting strategies affect RTL-to-specification quality and introduce metrics for faithfully evaluating generated specs. We also benchmark open-source and commercial LLMs, providing a foundation for more automated and efficient specification workflows in IC design.

# **CCS** Concepts

• Hardware  $\rightarrow$  Software tools for EDA.

#### **Keywords**

Verilog, Large Language Models, Automation

#### **ACM Reference Format:**

#### 1 Introduction

The increasing scale and complexity of modern integrated circuit (IC) design have made Register–Transfer Level (RTL) codebases harder to document, validate, and maintain. In industrial workflows, engineers often spend considerable time manually interpreting existing RTL code to produce design specifications—documents that describe interface semantics, functional intent, timing assumptions, and control behavior. Unlike RTL, which can be simulated and verified with electronic design automation (EDA) toolchains, hardware specifications lack automated evaluation pipelines, making them

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

© 2018 Copyright held by the owner/author(s). Publication rights licensed to ACM. ACM ISBN 978-1-4503-XXXX-X/2026/07 https://doi.org/XXXXXXXXXXXXXXX

labor-intensive to create and difficult to benchmark for correctness and completeness.

Recent advances in large language models (LLMs) have sparked rapid progress in *Specification-to-RTL* generation (e.g.,[9–11, 14, 21, 29, 31]), with multiple benchmarks and model improvements demonstrating strong RTL synthesis capability. However, the inverse task—generating structured, faithful specifications from RTL [7]—remains largely under-explored, despite its critical importance in design understanding, verification hand-off, documentation, and AI-assisted hardware engineering workflows. This reverse task introduces unique challenges: unlike RTL generation, specification generation requires *semantic abstraction*, *temporal reasoning*, *interface precision*, and *preservation of design intent*, all of which are difficult to measure with traditional text- and semantic-based similarity metrics.

In this work, we present the first systematic and benchmarkdriven study of RTL-to-specification generation. We argue that a correct specification should not simply restate the RTL implementation, but instead provide sufficient detail about design intent, I/O interfaces, functional behavior, state transitions, and related semantics to enable reconstruction of functionally equivalent RTL. Motivated by this, we first propose a set of prompting strategies that progressively incorporate structural guidance and reasoning steps to improve abstraction quality and reduce specification errors. Next, we introduce two hardware-aware evaluation metrics-GPT-RTL Score and RTL Reconstruction (RR) Score—that assess specification fidelity through aspect-wise analysis and testbench-level functional validation. Finally, we evaluate both commercial and open-source LLMs across multiple model scales using these metrics, providing the first quantitative comparison of model performance on the RTLto-specification task and establishing practical recommendations for real-world deployment. In summary, we make the following contributions:

- We present the first systematic study on the task of translating RTL code into human-readable specifications.

- We study how prompting strategies influence specification quality and introduce prompts tailored for RTL-to-spec generation

- We propose two hardware-aware metrics that more sensitively and interpretably evaluate RTL-to-spec performance.

- Using these metrics, we benchmark open-source and commercial LLMs, offering guidance on model selection for practical workflows.

, ,

#### 2 Related Works

# 2.1 Specification-to-RTL Generation and Evaluation

RTL generation from specifications has been widely studied. Liu et al. [9] and Pinckney et al. [21] introduced <code>VerilogEval</code> and <code>VerilogEval-V2</code> for evaluating LLM-based RTL generation. Lu et al. [14] and Liu et al. [11] proposed <code>RTLLM</code> and <code>RTLLM-2.0</code>, benchmarks with more complex design. Beyond benchmarks, Pei et al. [29] improve RTL generation via data augmentation and discriminator-guided fine-tuning. Liu et al. [10] develop a small-size LLM fine-tuned by RTL synthetic data outperforming commercial models. Zhao et al. [31] introduce a multi-agent system with sampling and debugging for RTL refinement. Despite progress in spec-to-RTL, the reverse task—RTL-to-spec generation—remains underexplored.

# 2.2 RTL Code Understanding and Specification Generation

Similar to specification generation, RTL understanding takes RTL as input and outputs natural language descriptions. Pinckney et al. [22] proposed *CVDP*, a benchmark for RTL generation and comprehension. Liu et al. [12, 13] introduced *DeepRTL* and *DeepRTL2*, unified models for RTL understanding and generation evaluated via GPT Score. Although these datasets include high-level descriptions, their evaluation focuses on code comprehension rather than specification generation. Unlike RTL understanding, specification generation requires higher-level abstraction of design intent, constraints, and functional behavior. Pinckney et al. [22] also note that specification generation is a more challenging test of LLM reasoning than comprehension alone. To our knowledge, the only work targeting RTL-to-spec is SpecLLM [7], which provides a taxonomy for specifications but relies on qualitative analysis without quantitative evaluation metrics, a gap we address in our work.

# 2.3 Software Code to Document Generation and Evaluation

Research on hardware specification generation remains limited, while the software domain has advanced rapidly in LLM-based code documentation. Shi et al. [27] evaluated neural code summarization models across BLEU variants. Mastropaolo et al. [15] proposed contrastive metric learning. Sun et al. [28] analyzed LLM summarization pipelines. Diggs et al. [3] studied legacy code documentation and metric correlation. Sharma et al. [26] introduced a structure-aware Javadoc dataset, and Fang et al. [5] used a Struct-Agent for improved code interpretation. Despite progress in software documentation, applying these methods to RTL remains underexplored, as hardware specifications require modeling timing, hierarchy, and circuit behavior beyond software-style summarization.

# 3 Methodology

#### 3.1 Problem Formulation

In our problem formulation, the input to the LLM is an *RTL reference code* file (or repository), and the output is a *functional specification* describing the design. The generated specification should be human-readable and must clearly express design intent and key

hardware characteristics, including input/output interfaces, logical functionality, control flow, state transitions, and timing behaviors such as clocking and reset. Using only the generated specification, an experienced engineer should be able to reimplement RTL that is functionally equivalent to the original design. It is important to distinguish *RTL-to-specification generation* from *RTL code understanding*. The core difference lies in the level of abstraction. While prior work on RTL understanding [12, 13, 22] focuses on the interpretation of implementaion details, specification generation [7] requires inferring higher-level design intent and behavioral semantics. Because many functionally-equivalent RTL implementations can share the same specification, the goal of RTL-to-specification generation is not line-by-line explanation, but rather abstraction and summarization of essential logic, interfaces, and timing characteristics.

You are a helpful assistant. Describe what the given Verilog code does in a few sentences (should include module name)

Verilog Code: [verilog-code]

You are an expert hardware engineer. Given a Verilog RTL module, describe its functionality in natural language. Requirements:

- Do NOT output Verilog code.

- The description MUST explicitly include:

- Module name

- All input names with their bit-widths

- All output names with their bit-widths

- Provide a concise functional description of the module's purpose and behavior.

- The explanation should be precise and understandable by another RTL engineer.

Verilog Code: [verilog-code]

Figure 1: Minimal prompt (top) and specification-aware prompt (bottom).

### 3.2 Prompt Design

To generate high-quality specifications, and inspired by the prompt engineering strategies discussed in [25], we explore three prompt designs that provide progressively stronger structural guidance. The exact content of these three prompts are in Fig 1 and 2.

- Minimal Prompt: A minimal instruction that asks the model to describe the implementation of a given Verilog design in natural language. It imposes no structural or technical requirements, serving as a baseline for unconstrained specification generation.

- Specification-Aware Prompt: A more structured prompt that explicitly instructs the model to describe essential hardware attributes, such as module interfaces (port names and bit-widths) and functional behavior. The focus is on conveying design intent and interface semantics in a clear, engineer-readable format.

- Multi-Step Reasoning Prompt: A reasoning-enhanced prompt that enforces a staged generation process: (1) internal RTL analysis covering control logic, state behavior, and timing, (2) generation of a structured specification following a predefined template, and (3) internal self-checking to validate interface correctness and behavioral completeness. This design aims to improve consistency and reduce hallucinations.

You are a senior hardware design engineer specializing in RTL design analysis and documentation. Your task is to interpret a Verilog RTL module and produce a precise, human-readable functional specification

Stage 1 - Internal Analysis (Reasoning): Internally, analyze the RTL step by step. You may reason through:

- · Signal definitions and bit widths

- Data dependencies between inputs, outputs, and internal logic

- Sequential versus combinational behavior

- Control flow, counters, FSM transitions, and enable signals

- Clocking, reset conditions, and timing dependencies

Special or exceptional signal behaviors

Do NOT output this reasoning explicitly. Use this reasoning only to construct a correct and complete specification.

Stage 2 - Structured Specification Output: After reasoning, write only the final specification using the following format

- Module Name: [exact name from the RTL]

- Inputs: [signal\_name] [bit-width] : [concise purpose]

Outputs: [signal\_name] [bit-width] : [concise purpose]

- Functional Description: (1) Describe the module's overall purpose and how outputs are derived from inputs. (2) Explain internal logic, sequential behavior, and control mechanisms coherently. (3) Highlight any counters, state machines, arithmetic logic

- Clocking and Reset Behavior: Specify active clock edge, reset polarity, and initialization

- Notes (if applicable): Mention parameters, default values, pipeline latency, or exceptional conditions.

Stage 3 — Self-Reflection and Consistency Check: Before finalizing your answer:

- Internally verify that all input/output signals mentioned exist in the RTL.

- Ensure every output is explained in the Functional Description.

- Verify clock and reset behavior are correctly identified.

- If uncertainty remains, make reasonable inferences explicitly stated in the Notes

#### Output Rules:

- Output only the structured specification from Stage 2.

- Do not include or mention any reasoning steps, thought processes, or internal analysis

- Maintain a clear, formal, and technical tone appropriate for RTL design documentation.

Verilog Code: [verilog-code]

Figure 2: Multi-step reasoning prompt.

We evaluate the effectiveness of all three prompts in Sec. 4.2, providing a comparative analysis to identify the prompts for producing accurate and engineer-friendly specifications.

#### 3.3 Evaluation Metrics

Prior work [7] demonstrated RTL-to-spec generation via case studies. In contrast, we adopt a systematic, multi-metric evaluation framework inspired by software documentation research [15, 28]. We assess specification quality using various types of metrics, detailed below.

- 3.3.1 Textual and Semantic Similarity Metrics. Textual similarity metrics such as BLEU [20], and ROUGE-L [8] measure n-gram overlap between generated and reference specifications, producing normalized scores in [0, 1]. While widely used [3, 5, 15, 26, 28], these metrics are limited in capturing semantic equivalence due to their token-level matching. Hence, semantic-based similarity metrics are proposed, such as BERTScore-R [30], SentenceBERT Cosine Similarity (SBCS) [24]. These evaluate similarity in high-dimensional semantic space, better reflecting semantic alignment [6].

- 3.3.2 LLM-Based Evaluation. Following recent LLM-as-judge approaches [12, 28], we employ LLMs as evaluators, allowing them to serve as a surrogate for human assessment.

GPT Score. GPT Score [12] presents both golden and generated specifications to an LLM as a judge, which outputs a similarity

You are a professional Verilog designer that needs to evaluate the similarity between two textual functional specifications describing Verilog code. The first specification is the ground truth specification of the Verilog code, and the second specification is the generated specification of the Verilog code. Please read the following specifications and provide a similarity score between 0 and 1 based on how similar the two specifications are in terms of describing the functionality of the Verilog code, where 0 means completely dissimilar and 1 means identical. Note that you should strictly only output the score without any additional information

Specifications 1: [golden] Specifications 2: [model-output]

Figure 3: Prompt for GPT Score

score within [0,1] based on functional agreement in describing the Verilog design (0: no alignment, 1: identical functionality). The prompt for computing this metric is illustrated in Fig. 3. We use GPT-5 Chat [18] to execute this prompt, evaluating semantic and functional correctness of generated specifications.

GPT-RTL Score. Although GPT Score primarily measures the alignment between generated and reference specifications, our goal is to make evaluation more hardware-aware. To this end, we propose GPT-RTL Score, an LLM-based assessment tailored to digital design specifications. GPT-RTL Score emphasizes hardware fidelity by evaluating five key aspects: (1) design intent, (2) input/output ports, (3) logical functionality, (4) state transition and clock-cycle behavior, and (5) data flow and control flow. The detailed prompt for evaluation is provided in Fig. 4. For each aspect, LLMs compare consistency between golden specification and the generated specification, then assign a score between 0 and 1, where 1 indicates perfect alignment and 0 indicates no consistency. The five dimension scores are then averaged to produce a final score between 0 and 1. By explicitly scoring these hardware-critical dimensions, GPT-RTL Score offers a more domain-aligned measure of specification quality compared to generic semantic similarity metrics.

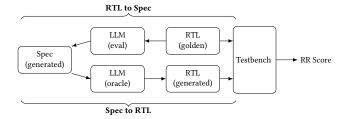

3.3.3 RTL-Reconstruction Score (RR Score). We propose the RTL-Reconstruction Score (RR Score), a behavior-grounded metric that evaluates whether a generated specification contains sufficient information-functional intent, interfaces, and timing-to reconstruct correct RTL. As shown in Fig. 5, the top represent the task of RTL-tospecification (i,e., a reference RTL is first converted into a specification by the LLM to be evaluated). We then use an oracle LLM (GPT-5 Codex in our experiments) to reconstruct RTL based solely on the generated specification. The reconstructed and golden RTL are validated on the same testbench; behavioral equivalence determines success. The RR Score is computed as the fraction of generated specifications that pass this testbench-based equivalence check. For each specification, we use pass@1, meaning only a single reconstructed design is generated. Because correctness is measured at the input-output level, structural differences of reconstructed RTL are allowed if functionality matches. RR Score therefore assesses functional corectness rather than semantic or textual similarity.

#### **Experiments**

# 4.1 Implementation Details

We use Python to implement our evaluation pipeline. For the LLMs being evaluated, we rely on the OpenRouter[19] API, which provides unified access to both commercial and open-source models

You should evaluate the consistency between the golden specification and the generated specification with respect to the following key aspects:

- design intent: Evaluates whether the generated specification accurately captures

the overall purpose and high-level functionality of the RTL design, including its

operational goal and design rationale.

- (2) input/output ports: Assesses the correctness and completeness of input/output signal definitions, including names, directions, bit widths, and interface semantics (e.g., handshaking, valid/ready protocols).

- (3) logical functionality: Measures the consistency of described logical operations (e.g., arithmetic, conditional, or sequential logic) with the intended RTL behavior, independent of implementation syntax.

- (4) state transition and clock-cycle behavior: Evaluates how well the specification represents sequential behavior, including finite-state transitions, timing relations, clocked events, and reset conditions.

- (5) data flow and control flow: Checks whether the specification correctly describes signal propagation, data dependencies, and control signal interactions between components or modules.

For each aspect, assign a consistency score between 0 and 1, where 1 indicates perfect alignment and 0 indicates no consistency. For example, if the generated specification is fully consistent with the golden specification in terms of design intent, mostly consistent in interface description, but only partially consistent in logical functionality and state-transition behavior, and inconsistent in data flow and control flow, the corresponding scores would be:

design intent = 1.0, input/output ports = 0.8, logical functionality = 0.2, state transition and clock-cycle behavior = 0.2, data flow and control flow = 0.0.

If a particular feature is not applicable in the golden specification (e.g., a combinational circuit with no state transitions), that aspect should be assigned a score of 1.0 to avoid penalizing the generated specification for the absence of such behavior. Note that you should strictly only output the JSON for mat of score without any additional information.

Golden Specification: [golden-specification]

Generated Specification:[generated-specification]

Figure 4: Prompt for GPT-RTL Score

Figure 5: RTL-Reconstruction (RR) score

through a single, standardized interface. This allows us to query multiple model families with consistent rate limits, formatting, and request handling. Details on the selected LLM candidates and evaluation benchmarks are provided below.

4.1.1 LLM Candidates. We evaluate GPT-5-Codex[17], Claude-Sonnet-4.5[1], Qwen3-Coder[23], LLaMA-3.1[16], and DeepSeek-3.1[2]. For Qwen3-Coder and LLaMA-3.1, we include multiple model sizes to enable cross-scale comparison. Our study includes both commercial and open-source LLMs covering large (>100B), medium (10–100B), and small (<10B) parameter ranges, providing insight into how specification quality correlates with model scale and weight accessibility.

4.1.2 Benchmarks. We use two standard spec-to-RTL benchmarks, VerilogEval-V2 [21] and RTLLM-2.0 [11], which provide golden specifications and testbenches. Golden specs serve as the reference for assessing how closely the generated specification matches the ground truth, while testbenches verify whether generated specs enable correct RTL reconstruction. Using these benchmarks in

Table 1: Evaluation of RTL-to-Spec. Here, RGL refers to ROUGE-L, BS denotes BertScore-R, GS represents GPT Score, GRS represents GPT-RTL Score, RRS denotes RTL-Reconstruction Score.

(a) Evaluation of prompts design. MINI denotes Minimal Prompt, SA denotes Specification-Aware Prompt and MSR denotes Multi-Step Reasoning Prompt. Gray-highlighted cells mark the best result among the three prompts for each model.

|                        | Metric | Text & Semantic Similarity |       |       |       | LLM-Based |       | RTL   |  |  |

|------------------------|--------|----------------------------|-------|-------|-------|-----------|-------|-------|--|--|

| Model                  | Prompt | BLEU                       | RGL   | BS    | SBCS  | GS        | GRS   | RRS   |  |  |

| Benchmark: VerilogEval |        |                            |       |       |       |           |       |       |  |  |

| GPT-5<br>Codex         | MINI   | 2.2%                       | 20.5% | 81.0% | 64.6% | 90.0%     | 94.3% | 76.3% |  |  |

|                        | SA     | 2.8%                       | 22.6% | 83.0% | 70.6% | 93.5%     | 94.2% | 89.1% |  |  |

|                        | MSR    | 2.1%                       | 29.6% | 83.8% | 70.5% | 92.4%     | 94.1% | 98.7% |  |  |

| Qwen3<br>Coder<br>480B | MINI   | 2.5%                       | 24.2% | 81.2% | 63.6% | 86.5%     | 91.4% | 56.4% |  |  |

|                        | SA     | 2.7%                       | 26.3% | 83.0% | 71.9% | 87.7%     | 90.5% | 73.1% |  |  |

|                        | MSR    | 2.4%                       | 23.7% | 83.9% | 72.2% | 89.3%     | 92.5% | 80.1% |  |  |

| Benchmark: RTLLM       |        |                            |       |       |       |           |       |       |  |  |

| GPT-5<br>Codex         | MINI   | 1.4%                       | 22.6% | 80.8% | 82.7% | 94.0%     | 95.8% | 42%   |  |  |

|                        | SA     | 3.3%                       | 24.3% | 84.1% | 85.5% | 93.8%     | 95.2% | 72%   |  |  |

|                        | MSR    | 4.2%                       | 25.8% | 86.9% | 87.8% | 93.6%     | 94.8% | 76%   |  |  |

| Qwen3<br>Coder<br>480B | MINI   | 4.4%                       | 28.2% | 81.7% | 81.4% | 93.4%     | 95.0% | 38%   |  |  |

|                        | SA     | 6.9%                       | 29.3% | 85.4% | 86.2% | 94.3%     | 95.9% | 64%   |  |  |

|                        | MSR    | 8.0%                       | 31.6% | 87.9% | 90.0% | 93.2%     | 95.9% | 66%   |  |  |

(b) Evaluation of LLM candidates using multi-step reasoning prompt. Bolded values indicate the top-3 scores for each metric, where black is 1st, dark gray is 2nd, and gray is 3rd.

| Metric                 | Text & Sematic Similarity |       |       |       | LLM-Based |       | RTL   |  |  |

|------------------------|---------------------------|-------|-------|-------|-----------|-------|-------|--|--|

| Model                  | BLEU                      | RGL   | BS    | SBCS  | GS        | GRS   | RRS   |  |  |

| Benchmark: VerilogEval |                           |       |       |       |           |       |       |  |  |

| GPT-5-Codex            | 2.1%                      | 29.6% | 83.8% | 70.5% | 92.4%     | 94.1% | 98.7% |  |  |

| Claude-Sonnet-4.5      | 1.6%                      | 27.3% | 82.6% | 72.2% | 92.3%     | 93.4% | 93.6% |  |  |

| Qwen3-Coder-480B       | 2.4%                      | 23.7% | 83.9% | 72.2% | 89.3%     | 92.5% | 80.1% |  |  |

| Qwen3-Coder-30B        | 2.3%                      | 22.9% | 83.7% | 70.9% | 85.4%     | 89.1% | 67.3% |  |  |

| Llama3.1-405B          | 2.7%                      | 25.2% | 81.7% | 69.1% | 84.9%     | 89.8% | 62.2% |  |  |

| Llama3.1-70B           | 2.3%                      | 24.9% | 83.2% | 67.7% | 84.4%     | 90.0% | 62.8% |  |  |

| Llama3.1-8B            | 2.3%                      | 24.2% | 81.6% | 68.3% | 77.2%     | 84.3% | 48.7% |  |  |

| Deepseek-V3.1          | 2.3%                      | 23.3% | 84.0% | 70.1% | 91.6%     | 92.8% | 92.9% |  |  |

| Benchmark: RTLLM       |                           |       |       |       |           |       |       |  |  |

| GPT-5-Codex            | 4.2%                      | 25.8% | 86.9% | 87.8% | 93.6%     | 94.8% | 76%   |  |  |

| Claude-Sonnet-4.5      | 5.5%                      | 25.1% | 85.9% | 83.7% | 92.7%     | 95.5% | 76%   |  |  |

| Qwen3-Coder-480B       | 8.0%                      | 31.6% | 87.9% | 90.0% | 93.2%     | 95.9% | 66%   |  |  |

| Qwen3-Coder-30B        | 8.1%                      | 31.3% | 87.8% | 89.7% | 91.8%     | 93.5% | 68%   |  |  |

| Llama3.1-405B          | 8.7%                      | 32.8% | 85.2% | 90.3% | 93.6%     | 93.9% | 58%   |  |  |

| Llama3.1-70B           | 9.3%                      | 33.2% | 87.4% | 90.6% | 91.7%     | 91.4% | 54%   |  |  |

| Llama3.1-8B            | 8.0%                      | 31.5% | 84.8% | 90.1% | 87.1%     | 87.3% | 46%   |  |  |

| Deepseek-V3.1          | 5.7%                      | 29.0% | 87.3% | 86.6% | 92.5%     | 94.9% | 70%   |  |  |

reverse (RTL-to-spec) offers reproducible, comparable bidirectional evaluation.

# 4.2 Prompt Design

We evaluate the prompts described in Sec. 3.2 using Qwen3-Coder-480B and GPT-5 Codex. The results, shown at Table 1a, highlight the best-performing prompt for each model using gray shading. Overall, the minimal prompt yields the weakest performance, while the specification-aware prompt achieves moderate improvements. The multi-step reasoning prompt produces the highest scores, demonstrating the importance of well-structured prompt design for high-quality RTL-to-specification generation. Sec. 4.4.1 provides an illustrative example of specifications generated using different prompts.

#### 4.3 Evaluation of LLM Candidates

The RTL2Spec evaluation results for LLM candidates are reported at Table 1b, and the correlation between evaluation metrics are shown in Fig 6. From these results, we make the following key observations:

- Overall, GPT-5-Codex delivers the best performance across most of the metrics, followed by Claude-Sonnet-4.5. Opensource models with large weights(>100B), such as DeepSeek-V3.1, Qwen-Coder-480B, and LLaMA-3.1-405B form the next tier with similar performance levels, although their relative rankings differ across datasets and evaluation metrics. For instance, under GPT Score, DeepSeek performs better on VerilogEval, while Qwen-Coder and LLaMA achieve stronger performance on RTLLM.

- The small-size model LLaMA-3.1-8B performs the worst across almost all metrics except SBCS, with a significant gap from larger models. Medium-size models such as LLaMA-3.1-70B and Qwen3-Coder-30B occasionally outperform larger models on specific metrics. This suggests that aggressively reducing parameter count can substantially degrade RTL-to-spec performance, whereas well-scaled medium-size models can still retain strong reasoning and abstraction capability, offering a more efficient trade-off between model size and performance.

- Consistent with prior findings in [12, 28], LLM-based metrics are more reliable than token or semantic similarity metrics. Specifically, GPT Score, GPT-RTL Score and RR Score better reflect expected model behavior—latest commercial models outperform earlier open-source ones—whereas text and semantic similarity metrics often underestimate the performance gap.

- Our proposed RTL-Reconstruction Score is strongly aligned with GPT Score [12], indicating that it is also a reliable indicator of specification quality. Notably, it exhibits higher variation (46%–98%) than GPT Score (77%–93%), making it more sensitive to specification errors and more discriminative in distinguishing quality differences. A detailed comparison is provided in Sec. 4.4.2.

- GPT-RTL Score is also highly correlated with GPT Score. However, unlike GPT Score, which outputs a single scalar without explanation, GPT-RTL Score evaluates five core design aspects independently before averaging them into a final score. This metric enables more interpretable assessment by identifying why a specification receives a given score. Further analysis is presented in Sec. 4.4.2.

- Although GPT-5-Codex receives a higher GPT Score than Claude-Sonnet-4.5, this result is influenced by the fact that GPT Score—and our improved variants—ultimately depend on the LLM judge in GPT series. This reliance may overestimate GPT-5-Codex's performance while underestimating Claude-Sonnet-4.5. We discuss this limitation in Sec. 5.1, and future work will aim to mitigate this evaluation bias.

# 4.4 Qualitative Analysis

4.4.1 Comparison Between Different Prompts. Figure 7 compares outputs generated by the minimal and specification-aware prompts.

|                   | (1)   | (2)   | (3)  | (4)   | (5)  | (6)  | (7)   |

|-------------------|-------|-------|------|-------|------|------|-------|

| BLEU (1)          | 1.00  | 0.67  | 0.31 | 0.54  | 0.05 | 0.02 | -0.17 |

| ROUGE-L (2)       | 0.67  | 1.00  | 0.30 | 0.56  | 0.08 | 0.06 | -0.18 |

| BERTScore-R (3)   | 0.31  | 0.30  | 1.00 | 0.50  | 0.33 | 0.31 | 0.14  |

| SBCS (4)          | 0.54  | 0.56  | 0.50 | 1.00  | 0.21 | 0.18 | -0.08 |

| GPT-Score (5)     | 0.05  | 0.08  | 0.33 | 0.21  | 1.00 | 0.87 | 0.29  |

| GPT-RTL-Score (6) | 0.02  | 0.06  | 0.31 | 0.18  | 0.87 | 1.00 | 0.28  |

| RR-Score (7)      | -0.17 | -0.18 | 0.14 | -0.08 | 0.29 | 0.28 | 1.00  |

Figure 6: Pairwise correlation matrix between metrics, computed using results from the Multi-step reasoning prompt across all models and datasets, where each generated specification score from a given metric is treated as an independent data point.

VerilogEval Prob024\_hadd

assign {cout. sum} = a+b:

```

GPT Score of Spec from Minimal Prompt: 0.6

GPT Score of Spec from Specification-Aware Prompt: 0.7

Generated Specification from Minimal Prompt, OWen3-Coder-480B

The Verilog code defines a module named "TopModule" that implements a simple 1-bit full adder.

It takes two 1-bit inputs (a and b) and produces a 1-bit sum output and a 1-bit carry output

(cout). The module uses a continuous assignment to calculate the sum and carry by adding the

two input bits together, where the result is automatically extended to 2 bits and assigned to the

concatenated output wires (cout, sum).

Generated Specification from Specification-Aware Prompt, QWen3-Coder-

Module Name: TopModule

Input Names and Bit-Widths:

a: 1-bit input (a single-bit signal)

b: 1-bit input (a single-bit signal)

Output Names and Bit-Widths

sum: 2-bit output (a 2-bit result)

cout: 1-bit output (a single-bit carry-out)

Functional Description: The TopModule is a simple arithmetic logic unit (ALU) that performs

a single-bit addition operation. It takes two 1-bit inputs, a and b, and produces a 2-bit result, sum, and a single-bit carry-out, cout. The result is calculated using the basic arithmetic operation

n, where the carry-out (cout) is set to 1 if the sum of a and b requires a carry bit. In

essence, the TopModule is a basic adder module that can be used as a building block for more

complex arithmetic circuits.

Golden Specification

Module Name: TopModule

input a

input b

output sum

output cout

The module should implement a half adder. A half adder adds two bits (with no carry-in) and

produces a sum and carry-out.

Golden Verilog Code

module RefModule (

input a,

input b,

output sum.

output cout

```

Figure 7: An example from VerilogEval to show the comparison of results from different prompts. Certain text segments are highlighted in red for clarity, and some line breaks have been removed to meet page-length requirements.

The minimal prompt produces low-level, code-centric descriptions (e.g., "uses a continuous assignment to calculate the sum and carry") and even misidentifies the module's functionality (e.g., "1-bit full adder"), yielding a GPT Score of 0.6. In contrast, the specification-aware prompt guides the model toward higher-level functional intent (e.g., "calculated using basic arithmetic operation of addition")

, ,

and produces clearer, more human-readable I/O descriptions, resulting in a higher score of 0.7. This example demonstrates that prompt design has a substantial impact on specification quality: minimal prompts tend to produce superficial code descriptions, whereas specification-aware prompts better capture functional behavior, improve readability, and align more closely with the golden specification.

4.4.2 Comparison between Different Metrics. Fig. 8 shows that RTL-Reconstruction and GPT-RTL Score offer more sensitive and diagnostic evaluation than GPT Score. In this VerilogEval example, despite the golden specification requiring an asynchronous reset, the generated specification incorrectly claims that the reset is synchronized with the clock, but immediately sets q to 0 upon reset activation. This statement contradicts both itself and the golden specification, leading the model to reconstruct an incorrect synchronous-reset design, causing a functional mismatch. Consequently, the RTL-Reconstruction Score falls to 0.0. GPT-RTL Score also detects the error, reporting a score of 0.7 for state transition and clock-cycle behavior and consequently revealing where the inconsistency occurs. In contrast, GPT Score assigns a high score of 0.9 without explicitly indicating the mistake. This example demonstrates that our metrics better identify subtle semantic errors and provide interpretable, aspect-level feedback.

#### 5 Limitations

#### 5.1 Evaluation Metric

A key limitation of our work lies in the evaluation methodology. GPT Score, GPT-RTL Score, and RR Score rely on judge or oracle LLMs (GPT-5-Chat or GPT-5-Codex) to inspect specification quality or reconstruct RTL, implicitly assuming that the judge or oracle are always reliable. In practice, however, LLMs may misinterpret specifications or introduce RTL errors. For instance, GPT Score [12] uses GPT as the sole judge, which may overlook its own mistakes while more readily detecting errors produced by other models (e.g., Claude-Sonnet-4.5), potentially inflating GPT-5-Codex's score and unfairly penalizing competing models. Human evaluation [28] can mitigate some of these issues but remains susceptible to bias and inconsistency [4]. A more promising direction is to use a panel of diverse LLMs as evaluators to reduce single-model bias, or to combine multiple LLM judges with human review. Future work should investigate such hybrid multi-LLM-human evaluation frameworks to improve robustness and trustworthiness.

# 5.2 Scope of the Problems

Our study is also limited in scope. We evaluate only single-file RTL designs from VerilogEval and RTLLM, whereas real-world designs contain multiple interacting modules. Besides, for improving RTL-to-specification generation, we focus solely on prompting and do not examine other techniques such as RAG, test-time search, or fine-tuning. Additionally, our evaluation targets functional correctness, while real specifications must express broader design objectives (e.g., PPA) and multimodal formats such as waveforms or diagrams. Extending the framework to these richer, practical settings is an important direction for future work.

```

VerilogEval Prob047_dff8ar

GPT Score: 0.9

GPT-RTL Score: 0.92 (design intent: 1.0, input/output ports: 1.0, logical functionality: 0.9, state

transition and clock-cycle behavior: 0.7, data flow and control flow: 1.0)

Generated Specification, Using Llama3.1-8B

Module Name: TopModule

Inputs:

clk: Clock input signal

d [7:0]: 8-bit data input

areset: Active-high reset signal

Outputs:

a [7:0]: 8-bit output

Functional Description The TopModule is a simple synchronous register. It takes an 8-bit data

input d and an active-high reset signal areset. When the clock edge occurs, if the reset signal is high, the output q is immediately set to 0. Otherwise, the output q is updated to the value of

the input data d. The module's primary function is to store the input data in a synchronized

manner, using the clock edge to determine when to update the output. Clocking and Reset Behavior

Clocking: Active clock edge on clk (posedge).

Reset: Active-high reset on areset. Reset is synchronized with the clock and immediately sets q

to 0 upon reset activation

Golden Specification

Module Name: TopModule

input clk

input areset

input d (8 bits)

output q (8 bits)

The module should include 8 D flip-flops with active high asynchronous reset. The output should

be reset to 0. All DFFs should be triggered by the positive edge of clk.

Snippet of the Reconstructed Design

always @(posedge clk) begin

if (areset) begin

q <= 8'd0:

end else begin

q <= d;

end

```

Figure 8: An example from VerilogEval to show the comparison of score from different metrics. Selected text segments are highlighted in red for clarity, and some line breaks have been omitted to satisfy page-length requirements.

#### 6 Conclusion

This work presents the first systematic study of RTL-to-specification generation, addressing a critical but previously underexplored procedure of hardware design automation. We evaluate how prompting strategies influence abstraction quality, benchmark both commercial and open-source LLMs, and introduce two hardware-aware metrics-GPT-RTL Score and RTL-Reconstruction Score-that more reliably capture specification fidelity than existing measures. Our experiments on VerilogEval-V2 and RTLLM-2.0 show that structured prompting, especially the multi-step reasoning prompt, substantially improves specification correctness, while LLM-based and reconstruction-based metrics provide more sensitive and interpretable feedback on design intent, timing behavior, and interface accuracy. The evaluation further highlights clear performance differences across commercial and open-source models, with mediumand large-scale models demonstrating strong capability in generating engineer-ready specifications. We hope this study provides a foundation for future research in automated documentation and AI-assisted hardware design, enabling more accurate, scalable, and trustworthy RTL-to-specification frameworks.

#### References

- Anthropic. [n. d.]. Claude Sonnet. https://www.anthropic.com/claude/sonnet. Accessed: 2025-02-10.

- [2] DeepSeek AI. 2025. DeepSeek Open AI Model Platform. https://www.deepseek.com/en. Accessed: 2025-11-14.

- [3] Colin Diggs, Michael Doyle, Amit Madan, Siggy Scott, Emily Escamilla, Jacob Zimmer, Naveed Nekoo, Paul Ursino, Michael Bartholf, Zachary Robin, et al. 2024. Leveraging LLMs for legacy code modernization: Challenges and opportunities for LLM-generated documentation. arXiv preprint arXiv:2411.14971 (2024).

- [4] Aparna Elangovan, Ling Liu, Lei Xu, Sravan Babu Bodapati, and Dan Roth. 2024. ConSiDERS-The-Human Evaluation Framework: Rethinking Human Evaluation for Generative Large Language Models. In Proceedings of the 62nd Annual Meeting of the Association for Computational Linguistics (Volume 1: Long Papers), Lun-Wei Ku, Andre Martins, and Vivek Srikumar (Eds.). Association for Computational Linguistics, Bangkok, Thailand, 1137–1160. doi:10.18653/v1/2024.acl-long.63

- [5] Minying Fang, Xing Yuan, Yuying Li, Haojie Li, Chunrong Fang, and Junwei Du. 2025. Enhanced Prompting Framework for Code Summarization with Large Language Models. Proceedings of the ACM on Software Engineering 2, ISSTA (2025), 1630–1653.

- [6] Sakib Haque, Zachary Eberhart, Aakash Bansal, and Collin McMillan. 2022. Semantic similarity metrics for evaluating source code summarization. In Proceedings of the 30th IEEE/ACM International Conference on Program Comprehension. 36–47.

- [7] Mengming Li, Wenji Fang, Qijun Zhang, and Zhiyao Xie. 2025. Specllm: Exploring generation and review of vlsi design specification with large language model. In 2025 International Symposium of Electronics Design Automation (ISEDA). IEEE, 749–755.

- [8] Chin-Yew Lin. 2004. Rouge: A package for automatic evaluation of summaries. In Text summarization branches out. 74–81.

- [9] Mingjie Liu, Nathaniel Pinckney, Brucek Khailany, and Haoxing Ren. 2023. Verilogeval: Evaluating large language models for verilog code generation. In 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD). IEEE, 1–8.

- [10] Shang Liu, Wenji Fang, Yao Lu, Jing Wang, Qijun Zhang, Hongce Zhang, and Zhiyao Xie. 2025. RTLCoder: Fully Open-Source and Efficient LLM-Assisted RTL Code Generation Technique. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 44, 4 (2025), 1448–1461. doi:10.1109/TCAD.2024. 3483089

- [11] Shang Liu, Yao Lu, Wenji Fang, Mengming Li, and Zhiyao Xie. 2024. Openllm-rtl: Open dataset and benchmark for llm-aided design rtl generation. In Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design. 1–9.

- [12] Yi Liu, Changran Xu, Yunhao Zhou, Zeju Li, and Qiang Xu. 2025. Deeprtl: Bridging verilog understanding and generation with a unified representation model. arXiv preprint arXiv:2502.15832 (2025).

- [13] Yi Liu, Hongji Zhang, Yunhao Zhou, Zhengyuan Shi, Changran Xu, and Qiang Xu. 2025. DeepRTL2: A Versatile Model for RTL-Related Tasks. arXiv preprint arXiv:2506.15697 (2025).

- [14] Yao Lu, Shang Liu, Qijun Zhang, and Zhiyao Xie. 2024. Rtllm: An open-source benchmark for design rtl generation with large language model. In 2024 29th Asia and South Pacific Design Automation Conference (ASP-DAC). IEEE, 722–727.

- [15] Antonio Mastropaolo, Matteo Ciniselli, Massimiliano Di Penta, and Gabriele Bavota. 2024. Evaluating code summarization techniques: A new metric and an empirical characterization. In Proceedings of the IEEE/ACM 46th International Conference on Software Engineering. 1–13.

- [16] Meta AI. 2024. Introducing Llama 3.1: Our most capable models to date. https://ai.meta.com/blog/meta-llama-3-1/. Accessed: 2025-11-14.

- [17] OpenAI. 2025. Codex A powerful coding agent in ChatGPT. https://chatgpt.com/en-TW/features/codex. Accessed: 2025-11-14.

- [18] OpenAI. 2025. Introducing GPT-5. https://openai.com/index/introducing-gpt-5/. Accessed: 2025-11-09.

- [19] OpenRouter, Inc. 2025. OpenRouter The unified API for LLMs. https://openrouter.ai/. Accessed: 2025-11-15.

- [20] Kishore Papineni, Salim Roukos, Todd Ward, and Wei-Jing Zhu. 2002. Bleu: a method for automatic evaluation of machine translation. In Proceedings of the 40th annual meeting of the Association for Computational Linguistics. 311–318.

- [21] Nathaniel Pinckney, Christopher Batten, Mingjie Liu, Haoxing Ren, and Brucek Khailany. 2025. Revisiting verilogeval: A year of improvements in large-language models for hardware code generation. ACM Transactions on Design Automation of Electronic Systems (2025).

- [22] Nathaniel Pinckney, Chenhui Deng, Chia-Tung Ho, Yun-Da Tsai, Mingjie Liu, Wenfei Zhou, Brucek Khailany, and Haoxing Ren. 2025. Comprehensive Verilog Design Problems: A Next-Generation Benchmark Dataset for Evaluating Large Language Models and Agents on RTL Design and Verification. arXiv preprint arXiv:2506.14074 (2025).

- [23] Qwen Team. 2025. Qwen3-Coder. https://www.qwen3coder.com/. Accessed: 2025-11-14.

- [24] Nils Reimers and Iryna Gurevych. 2019. Sentence-bert: Sentence embeddings using siamese bert-networks. arXiv preprint arXiv:1908.10084 (2019).

- [25] Pranab Sahoo, Ayush Kumar Singh, Sriparna Saha, Vinija Jain, Samrat Mondal, and Aman Chadha. 2025. A Systematic Survey of Prompt Engineering in Large Language Models: Techniques and Applications. arXiv:2402.07927 [cs.AI] https://arxiv.org/abs/2402.07927

- [26] Swapnil Sharma Sarker and Tanzina Taher Ifty. 2025. Automated and Context-Aware Code Documentation Leveraging Advanced LLMs. arXiv e-prints (2025), arXiv-2509.

- [27] Ensheng Shi, Yanlin Wang, Lun Du, Junjie Chen, Shi Han, Hongyu Zhang, Dongmei Zhang, and Hongbin Sun. 2022. On the evaluation of neural code summarization. In Proceedings of the 44th international conference on software engineering. 1597–1608.

- [28] Weisong Sun, Yun Miao, Yuekang Li, Hongyu Zhang, Chunrong Fang, Yi Liu, Gelei Deng, Yang Liu, and Zhenyu Chen. 2024. Source code summarization in the era of large language models. arXiv preprint arXiv:2407.07959 (2024).

- [29] PEI Zehua, Huiling Zhen, Mingxuan Yuan, Yu Huang, and Bei Yu. 2024. Betterv: Controlled verilog generation with discriminative guidance. In Forty-first International Conference on Machine Learning.

- [30] Tianyi Zhang, Varsha Kishore, Felix Wu, Kilian Q Weinberger, and Yoav Artzi. 2019. Bertscore: Evaluating text generation with bert. arXiv preprint arXiv:1904.09675 (2019).

- [31] Yujie Zhao, Hejia Zhang, Hanxian Huang, Zhongming Yu, and Jishen Zhao. 2025. MAGE: A Multi-Agent Engine for Automated RTL Code Generation. In 2025 62nd ACM/IEEE Design Automation Conference (DAC). 1–7. doi:10.1109/DAC63849. 2025.11133191