# Critical Path Aware Timing-Driven Global Placement for Large-Scale Heterogeneous FPGAs

He Jiang\*, Yi Guo, Shikai Guo\*, Huijiang Liu, Xiaochen Li, Ning Wang, Zhixiong Di

Abstract—Timing optimization during global placement is critical for achieving optimal circuit performance and remains a key challenge in modern Field Programmable Gate Array (FPGA) design. As FPGA designs scale and heterogeneous resources increase, dense interconnects introduce significant resistive and capacitive effects, making timing closure increasingly difficult. Existing methods face challenges in constructing accurate timing models due to multi-factor nonlinear constraints as well as load and crosstalk coupling effects arising in multi-pin driving scenarios. To address these challenges, we propose TD-Placer, a critical path aware, timing-driven global placement framework. It leverages graph-based representations to capture global net interactions and employs a nonlinear model to integrate diverse timing-related features for precise delay prediction, thereby improving the overall placement quality for FPGAs. TD-Placer adopts a quadratic placement objective that minimizes wirelength while incorporating a timing term constructed by a lightweight algorithm, enabling efficient and high-quality timing optimization. Regarding net-level timing contention, it also employs a finer-grained weighting scheme to facilitate smooth reduction of the Critical Path Delay (CPD). Extensive experiments were carried out on seven real-world open-source FPGA projects with LUT counts ranging from 60K to 400K. The results demonstrate that TD-Placer achieves an average ~10% improvement in Worst Negative Slack (WNS) and a  $\sim$ 5% reduction in CPD compared to the state-of-the-art method, with an average CPD comparable  $(\times 1.01)$  to the commercial AMD Vivado across five versions (2020.2–2024.2). Its code and dataset are publicly available<sup>1</sup>.

Index Terms-FPGA, Timing Driven, Analytical Placement

## I. Introduction

Field Programmable Gate Array (FPGA) is a programmable platform for flexible user customization, featuring short development cycles and zero non-recurring engineering costs [1]. As user demands diversify, FPGAs grow in capacity and heterogeneity to support more complex designs, placing

H Jiang, Y Guo, H. Liu, and X. Li are with the School of Software, Dalian University of Technology, Dalian, China. E-mail: jianghe@dlut.edu.cn, gy2220212088@dlmu.edu.cn, liuhuijiang@mail.dlut.edu.cn, xiaochen.li@dlut.edu.cn.

S. Guo is with the School of Information Science and Technology, Dalian Maritime University, Dalian, China. E-mail: shikai.guo@dlmu.edu.cn.

N Wang is with Chengdu Sino Microelectronics System Co.Ltd., Chengdu 610031, China. E-mail: wangning@csmsc.com.

Z. Di is with the School of Information Science and Technology, Southwest Jiaotong University, Chengdu 610031, China. E-mail: zxdi@home.swjtu.edu.cn.

\* Corresponding author (He Jiang and Shikai Guo)

greater demands on placement tools in both runtime and solution quality [10]. Specifically, placement, which maps logic blocks to physical locations on the FPGA, directly determines routability in the subsequent routing stage and significantly affects circuit wirelength and timing quality [2], [12], [13].

To deliver high-quality placement solutions across diverse application scenarios, two placement methods are widely adopted in academia and industry: simulated annealing [22] and analytical placement [26]. Simulated annealing iteratively swaps block positions to optimize wirelength under legalization constraints. When targeting larger netlists, analytical placement methods provide a better trade-off between placement quality and runtime, and demonstrate stronger scalability [23]. A typical analytical placement flow consists of three phases: global placement, legalization, and detailed placement [29]. Global placement, which roughly positions elements under resource constraints, plays a crucial role in shaping instance distribution and greatly impacts final placement quality.

Traditional analytical placers minimize total wirelength while ensuring routability of the solution in the global placement stage, indirectly addressing timing constraints by approximating net delay using wirelength metrics [3], [16], [20], [21]. However, as modern FPGA designs continue to scale in complexity and heterogeneous resource integration, the relationship between FPGA interconnect delays and wirelength has become highly nonlinear [1]. Consequently, Wirelengthdriven techniques increasingly fail to achieve optimal timing quality, or even ensure timing closure [12]. To address this challenge, timing-driven global placement has been extensively studied. It integrates the timing model into the global placement loop, dynamically estimates post-routing timing, and models the interplay between wirelength, routability, and timing to improve circuit performance. Lin et al. [1] developed an timing model based on FPGA routing architecture and net delay mapping, incorporating clock and density costs during global placement to ensure clock resource legality. Liang et al. [13] proposed a hard-coded piecewise polynomial model for critical path identification, and applied a series of pseudo-net strategies during placement iterations to optimize the timing. Xiong et al. [2] proposed a lightweight data-driven linear timing model with routing congestion estimates, integrated into an electrostatic global placement scheme to optimize timing.

However, as design scales increase and the complexity of heterogeneous resources and architectures in modern FPGAs persists, the resistive and capacitive effects introduced by dense heterogeneous interconnects make net delays more sensitive to a wider range of timing-related features and the global

<sup>&</sup>lt;sup>1</sup>https://github.com/yyiloe/TD-Placer

context of the net. Therefore, to enhance the quality of timingdriven placement, it is essential to address two fundamental challenges in current methods.

Challenge 1: Lacking awareness of load and crosstalk coupling effects in multi-pin driving scenarios. Each FPGA interconnect net consists of one driver pin and multiple load pins, which share a portion of the routing path. The delay between any driver-load pin pair can vary significantly due to load and crosstalk coupling effects from other instances on the net, which limits the accuracy of existing single-pin pair models. Therefore, a key challenge is how to incorporate the full net topology for accurate timing analysis.

Challenge 2: Lacking nonlinear modeling of diverse timing features affecting net delays. In modern FPGA architectures, net delays arise from nonlinear interactions among factors such as programmable switches, segmented routing, heterogeneous instance cascades, geometric distance, parasitic resistance, capacitance, and inductance. These factors make accurate net delay prediction difficult, and inaccurate estimates can misguide placement, significantly degrading post-routing timing quality. Therefore, developing a model that comprehensively captures these nonlinear timing factors is one of the core challenges in timing-driven placement optimization.

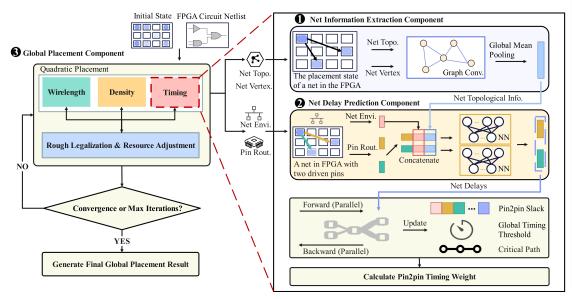

To address these challenges, we propose TD-Placer, a critical path aware, timing-driven global placement framework to effectively optimize post-routing circuit timing. TD-Placer consists of three main components: (1) the net information extraction component, (2) the net delay prediction component and (3) the global placement component. First, the net information extraction component addresses crosstalk and coupling effects under multi-pin driving scenarios by employing a specially designed graph-based method to capture net topology, providing critical support for accurate delay prediction. Then, the net delay prediction component leverages this topology, integrates various timing-related features, and adopts a nonlinear model to estimate precise end-to-end net delays. Finally, the global placement component introduces an end-to-end timing metric via fast slack estimation, which is integrated with a wirelength term into a unified quadratic objective to jointly optimize timing and wirelength. Within the global placement component, a fine-grained weighting scheme, guided by logic depth and global timing thresholds, is specifically applied along critical timing paths to enable smooth delay reduction during iterative optimization. In addition, TD-Placer employs a lightweight net delay prediction algorithm to ensure efficient deep learning model inference.

We conduct extensive experiments on seven open-source FPGA designs with LUT counts ranging from 60K to 400K (as listed in Table II). The state-of-the-art methods we compare against include: (1) AMF-placer [13], the state-of-the-art open-source timing-driven placer supporting mixed-size macros for Ultrascale devices, (2) five versions (2020.2-2024.2) of the commercial AMD Xilinx Vivado [4]. Compared to AMF-Placer, TD-Placer reduces average Critical Path Delay (CPD) by 4% and 5% and improves Worst Negative Slack (WNS) by 7% and 12% on designs routed with Vivado 2020.2 and 2021.2, respectively. Compared to Vivado, it achieves comparable average CPD (×1.01) across five versions.

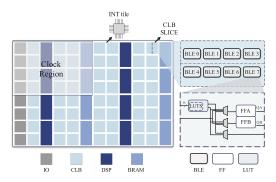

Fig. 1: Example of a simplified FPGA architecture depiction for Xilinx UltraScale.

The main contributions of this paper are as follows:

- We propose an accurate timing model for global placement, which comprehensively modeling multi-pin load, crosstalk coupling effects, and multiple timing-related factors to enable precise net delay prediction.

- We design a lightweight algorithm to ensure efficient timing analysis during global placement. In addition, we introduce a fine grained timing weighting scheme with awareness of global timing thresholds and logic depth, enabling smooth optimization along critical paths.

- We conduct extensive experiments to validate TD-Placer. Compared to the state-of-the-art method, it achieves a ~5% reduction in CPD, a ~10% improvement in WNS, and a 23% increase in timing prediction accuracy. We also open-source the code and dataset, including scripts for feature extraction and dataset construction, which can be easily adapted to other devices<sup>2</sup>.

# II. BACKGROUND AND MOTIVATION

#### A. FPGA Architecture

We adopt the Xilinx UltraScale architecture VU095 [44] as our target FPGA device. As illustrated in Fig 1, the architecture consists of a 2D array of configurable sites. Each Configurable Logic Block (CLB) contains two slices, each with 8 Basic Logic Elements (BLEs), and each BLE comprises two Look-Up Tables (LUTs) and two Flip-Flops (FFs). The device also incorporates heterogeneous resources including Digital Signal Processors (DSPs), Block RAMs (BRAMs), and Input/Output (IO) blocks. It comprises a 5×8 array of clock regions, with Fig 1 showing a partial representation. Each clock region accommodates up to 24 distinct clock nets.

FPGA routing typically comprises both intra-site routing and inter-site routing. Inter-site routing is achieved through the nearest interconnect (INT) tiles (represented by the white area with black arrows), where the built-in switch box enables switching between wiring segments in all four directions (up, down, left, right) as well as wire branching for multiple fanouts, connecting to different instances respectively. Intra-site routing handles communication between instances within

<sup>&</sup>lt;sup>2</sup>https://github.com/yyiloe/TD-Placer

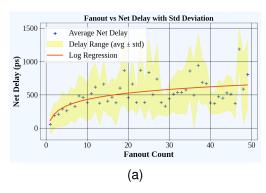

Fig. 2: (a) shows a scatter plot illustrating the relationship between net delay and **net fanout**. (b) presents a box plot of net delay categorized by **load type**.

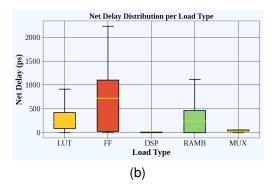

Fig. 3: The pins in the FPGA drive the RC path of two other pins through the switch box

the same site. The routing delay between any two different sites generally consists of both the intra-site delay and the delay through segmented wires in the INT tiles.

# B. Traditional Global Placement

The wirelength-driven quadratic placement process determines approximate locations for all cell instances under resource constraints [15]–[17]. To approximate the non-differentiable HPWL (Half-Perimeter Wirelength) function, the Bound2Bound [18] net model is employed to weight the quadratic objective function:

$$W_m = \sum_{i,j \in m} \left[ w_{x,ij}^{B2B} (x_i - x_j)^2 + w_{y,ij}^{B2B} (y_i - y_j)^2 \right]$$

(1)

where m represents a net, i,j denote the instances connected by the net,  $w_{x,ij}^{B2B}$  and  $w_{y,ij}^{B2B}$  are the weighting coefficients assigned according to the Bound2Bound net model.

To transform the constrained problem into an unconstrained optimization problem, virtual anchors are added to restrict illegal movement of instances [3], [15], [21]. Virtual anchors are connected to their associated instances through two-pin pseudo nets:

$$\min_{x,y} \sum_{m \in Q} W_m + \sum_{m_p \in Q_p} w_{m_p} W_{m_p}(x,y) \tag{2}$$

where  $W_m$  and  $W_{m_p}$  represent the HPWL approximations for regular nets and pseudo nets respectively, Q and  $Q_p$  denote the sets of regular nets and pseudo nets (for legalization and density control),  $w_{m_p}$  indicates the weighting coefficients applied to pseudo nets.

#### C. Motivation

Net delay is a major contributor to path delay and plays a critical role in circuit timing performance. Accurate prediction during placement is essential, as timing analysis relies on repeated delay estimation to guide instance adjustments. Since net delay is influenced by multiple factors, predicting delay solely based on geometric distance or simple congestion metrics is insufficient. As illustrated in Figure 3, a driver pin in an FPGA net fans out via a switch box to multiple load pins. Each programmable switch in the switch box introduces resistance, forming parallel Resistive-Capacitive paths. This increases delay, especially with added input capacitance from load types. We analyzed 160,162 nets with driver-load distances shorter than 4% of the longer dimension of the target layout, as shown in Figure 2a, that average net delay increases significantly from  $\sim 200$  ps to a peak of  $\sim 1200$  ps as fanout grows from 1 to 50. Figure 2b further shows that load types also cause noticeable variations in delay. These results highlight that net delay is sensitive to crosstalk, coupling effects, and various timing features, making accurate delay prediction difficult and significantly affecting timing convergence in placement.

## D. Related Works

Simulated Annealing (SA), exemplified by the widely used VPR placer [22], [36], effectively handles architectural constraints and non-smooth objectives in FPGA placement, but its convergence efficiency remains limited for large solution spaces despite numerous enhancements [10], [27], [31], [32].

To balance placement quality and runtime, wirelength-driven analytical placers have been widely studied. Chen et al. proposed a bin-packing-based algorithm for large-scale heterogeneous FPGAs, achieving nearly 200× bin-packing acceleration, 3× placement speedup, and 50% wirelength reduction over VPR 7.0 [38]. Analytical placers from ISPD 2016/2017 contests showed strong results in mitigating routing congestion and clock resource overflow [16], [21], [37]. Electrostatic placement, modeling device density as charged particles to control congestion, is another key method [39], [42], while OpenParf provides an open-source, GPU-accelerated framework for full physical design flows [23], [40], [41].

With the increasing scale of modern FPGA designs, wirelength-driven placement is insufficient to ensure optimal

Fig. 4: The TD-Placer framework.

timing and convergence [12]. Timing-driven placers address this by optimizing WNS and TNS through integrated timing models and metrics [1], [2], [43]. Yet, as applications grow more complex, delivering precise timing guidance for densely interconnected devices remains critical and challenging, requiring more advanced algorithms for large-scale heterogeneous circuits.

## III. TD-PLACER FRAMEWORK

## A. Overview

To address the above challenges, we present TD-Placer, a critical path aware, timing-driven global placement framework as illustrated in Figure 4. TD-Placer comprises three components: 1 the net information extraction component, 2 the net delay prediction component and 3 the global placement component, which collaboratively enable efficient timing optimization and placement convergence. Firstly, the net information extraction component performs holistic net modeling to provide topology information that capture load and crosstalk coupling effects, enabling more accurate delay prediction. Then, the extracted net topology information is fed into the net delay prediction component, which integrates other multi-dimensional timing-related features to achieve accurate end-to-end net delay prediction. Within the global placement component, the hierarchical netlist is converted into a directed acyclic timing graph, with vertex weights set via a logic delay lookup table. The design's nets are analyzed to extract topological information for net delay prediction, updating timing arc weights accordingly to prepare for timing analysis. Hierarchical parallel forward and backward traversals of the timing graph are performed to compute arc-level slacks. These slacks, together with the identified critical path and a threshold estimation of global slack, enable the construction of arcbased fine-grained timing metrics to ensure as smooth timing optimization as possible. Next, these metrics are integrated with wirelength and density terms to improve Worst Negative

Slack (WNS), Critical Path Delay (CPD) and Total Negative Slack (TNS). Finally, TD-Placer employs rough legalization and resource adjustment algorithms to enhance placement quality and support subsequent global placement iterations.

#### B. Data Preparation for Timing Analysis

1) Timing-Related Features Preprocessing: The continuous expansion of FPGA design scales has led to interconnect delays being influenced by multiple nonlinear factors [12]. To achieve accurate net delay prediction, TD-Placer constructs 25 key timing features based on circuit knowledge and parameter pruning experiments. As presented in Table I, these features are systematically categorized into (a) net vertex features (characterizing pin locations and instance attributes), (b) net environment features (describing the operational context of pin nets), and (c) pin routing features (representing the routing environment between driver and load pin pairs). Notably, all net-intrinsic features except congestion metrics are directly extracted from the current placement state and original circuit design, ensuring the efficiency of TD-Placer.

The limited routing resources in FPGAs often force routing wires in congested areas to detour through non-congested regions, significantly impacting net delays [2]. To address this, TD-Placer adapts the congestion estimation method from RippleFPGA [3] by developing an average routing density metric to quantify localized congestion levels. Furthermore, we introduce an average pin density metric specifically between driver and load pins to more accurately characterize how routing congestion affects net delays.

**Average Routing Density.** The average routing density reflects the congestion level in the region traversed by a given net. In TD-Placer, the placement-target area is partitioned into uniform square grids, where the grid size is a constant determined experimentally. Each grid is treated as a global routing cell (g-cell), and the routing density of the *i*-th g-cell is computed as follows:

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 3 if LUT Whether the instance is a lookup table 4 if FF Whether the instance is a flip-flop 5 if DSP Whether the instance is a DSP module 6 if RAMB Whether the instance is a block RAM Net Vertex 7 if MUX Whether the instance is a multiplexer 8 if IO Whether the instance is a multiplexer 9 if ClockBuffer Whether the instance is a clock buffer 10 if CARRY8 Whether the instance is a carry chain 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a LUT-based RAM 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net |               |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| Net Vertex  5 if DSP Whether the instance is a DSP module 6 if RAMB Whether the instance is a block RAM 7 if MUX Whether the instance is a multiplexer 8 if IO Whether the instance is a multiplexer 9 if ClockBuffer Whether the instance is a clock buffer 10 if CARRY8 Whether the instance is a carry chain 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a shifter 13 if IN Direction of signal propagation in the net relative to 14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                   |               |

| Net Vertex  6 if RAMB Whether the instance is a block RAM  Net Vertex  7 if MUX Whether the instance is a multiplexer  8 if IO Whether the instance is an I/O buffer  9 if ClockBuffer Whether the instance is a clock buffer  10 if CARRY8 Whether the instance is a carry chain  11 if Shifter Whether the instance is a shifter  12 if LUTRAM Whether the instance is a LUT-based RAM  13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net  15 Width Vertical width of the net  Net Environment  16 Length Horizontal length of the net  17 Fanout Fanout count of the net                                                                                                   |               |

| Net Vertex 7 if MUX Whether the instance is a multiplexer 8 if IO Whether the instance is an I/O buffer 9 if ClockBuffer Whether the instance is a clock buffer 10 if CARRY8 Whether the instance is a carry chain 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a shifter 13 if IN Direction of signal propagation in the net relative to 14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                |               |

| 8 if IO Whether the instance is an I/O buffer 9 if ClockBuffer Whether the instance is a clock buffer 10 if CARRY8 Whether the instance is a carry chain 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a LUT-based RAM 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                   |               |

| 9 if ClockBuffer Whether the instance is a clock buffer 10 if CARRY8 Whether the instance is a carry chain 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a LUT-based RAM 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                                                                 |               |

| 10 if CARRY8 Whether the instance is a carry chain 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a LUT-based RAM 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                                                                                                                         |               |

| 11 if Shifter Whether the instance is a shifter 12 if LUTRAM Whether the instance is a LUT-based RAM 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| 12 if LUTRAM Whether the instance is a LUT-based RAM 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| 13 if IN Direction of signal propagation in the net relative to  14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

| 14 HPWL Half-Perimeter Wire Length of the net 15 Width Vertical width of the net Net Environment 16 Length Horizontal length of the net 17 Fanout Fanout count of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| Net Environment 16 Length Horizontal length of the net Fanout count of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | this instance |

| Net Environment 16 Length Horizontal length of the net Fanout count of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| Fanout Fanout ount of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| Ave Routing Density Average routing congestion of the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| 19 PinPairXDist The x-direction distance between driver and load pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pairs         |

| 20 PinPairYDist The y-direction distance between driver and load pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pairs         |

| 21 Net Index Index of the load pin in the net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| 22 I/O Crossing Whether the connection crosses an I/O module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| Pin Routing 23 DSP Crossing Whether the connection crosses a DSP module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| 24 BRAM Crossing Whether the connection crosses a BRAM module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |

| 25 Ave Pin Density Average pin congestion between the driver and the lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

TABLE I: TIMING-RELATED FEATURES USED IN TD-PLACER

TABLE II: RESOURCE UTILIZATION OF BENCHMARKS ON VU095 DEVICE

| Benchmark | BLSTM [50] | DigitRecog [45] | FaceDetect [45] | SpooNN [46] | MemN2N [49] | MiniMap2 [47] | OpenPiton [48] | VU095   |

|-----------|------------|-----------------|-----------------|-------------|-------------|---------------|----------------|---------|

| #LUT      | 118,967    | 151,636         | 68,945          | 63,095      | 184,997     | 407,586       | 180,388        | 537,600 |

| #FF       | 54,690     | 105,580         | 56,987          | 70,987      | 84,694      | 252,624       | 111,966        | 537,600 |

| #CARRY    | 2,762      | 1,970           | 4,978           | 2,091       | 11,528      | 19,826        | 1,712          | 33,600  |

| #MUX      | 36,210     | 4,662           | 2,177           | 217         | 4,466       | 180           | 13,696         | 201,600 |

| #LUTRAM   | 1,147      | 251             | 255             | 251         | 3,500       | 251           | 752            | 19,200  |

| #DSP      | 258        | 1               | 101             | 165         | 312         | 528           | 58             | 768     |

| #BRAM     | 812        | 379             | 141             | 208         | 148         | 283           | 147            | 1,728   |

| #Cell     | 215,101    | 265,775         | 134,450         | 137,937     | 289,721     | 681,889       | 309,145        | -       |

$$cong_i = \sum_{m \in M_i} \frac{NW(m) \cdot HPWL(m)}{A_m}$$

(3)

where  $M_i$  denotes the set of nets intersecting with the i-th g-cell,  $A_m$  represents the total area of all g-cell covered by the net m, NW is the weighting coefficients associated with pin count, and HPWL corresponds to the HPWL estimation of the net m.

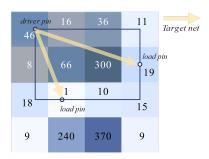

The average routing density of a net is defined as the mean density of all g-cells it traverses. As illustrated in Figure 5, the net connecting the driver and load pins has an average routing density equal to the mean value of the density within the the black shaded region, calculated as  $(46 + 16 + 36 + 8 + 66 + 300)/6 \approx 78.67$ .

Average Pin Density. The average pin density reflects congestion between driver and load pins, providing a more refined and direct congestion metric for net delay. For any pin pair, their average pin density is defined as the number of utilized pins within their enclosing rectangular region.

Fig. 5: The Average Routing Density of a net.

2) Data Collection: The ISPD 2016/2017 benchmarks [24], [25] have certain limitations: their randomly-generated netlists may produce unrealistic interconnects and unnecessary register duplication. Additionally, the absence of design hierarchy in these netlists results in an overly uniform distribution of critical timing paths, making them less representative of realworld scenarios [15]. To address this, we adopted seven opensource projects (Table II) as benchmarks to construct a dataset

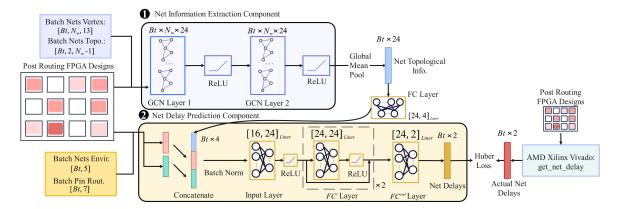

Fig. 6: Interaction and Architecture of Net Information Extraction and Net Delay Prediction Components.

The figure illustrates the batch training process of the network information extraction and delay prediction components, where Bt denotes the batch size and  $N_m$  represents the number of vertices in net m.

providing more realistic training and testing samples.

We extracted net vertex features from post-routing benchmarks using the commercial tool Vivado [4]. For each driverload pin pair within a net, we further extracted net environment features and pin routing features. All labels (net delays) were obtained using Vivado's built-in command get\_net\_delay. By comprehensively traversing all nets across the seven benchmarks, we treated each pin pair as an independent sample in the dataset. However, the full sample size was prohibitively large. To ensure efficient timing analysis, we needed to build a lightweight deep learning model. Therefore, we adopted a balanced sampling strategy based on both the proportion of benchmark instances and the geometric distance between sample components to select representative samples. We divided the number of nets in the dataset into training, validation, and testing sets in a ratio of 7:1.5:1.5 and obtained 197178 training samples (44082 nets), along with 41734 validation samples (9447 nets) and 44737 test samples (9446 nets).

## C. Net Information Extraction Component

During FPGA routing, pins of the same net are interconnected through wires, forming a tree topology with the driver pin as the root and load pins as leaves. The net delay from the root to any leaf node is intrinsically linked to this tree's overall structure. To capture topological information, TD-Placer employs graph convolution mechanisms [9] to model load and crosstalk coupling effects in multi-driver scenarios. This method enables each vertex to aggregate feature information from its neighboring vertices during message passing.

**Graph Construction for Nets:** For any given net m composed of N instance vertices and their driver-load relationships, TD-Placer constructs a corresponding directed graph G(m) = V, E, T, where V denotes the vertex set, E the set of directed edges, and T the edge types.

**Vertex Set** V: For any given net, its instances vertices are represented by vertices v belonging to the directed graph G's vertex set V. Each vertex is initialized using the net vertex features defined in III-B1, and its embedding vector is iteratively updated during graph convolution.

**Edge Set** E: The edge set is constructed based on interconnects within the net. The existence of edge  $u_{ij} \in E$  indicates a direct connection between instance vertices  $v_i$  and  $v_j$ .

**Edge Type Set** T: For each edge  $u_{ij}$ , its type  $t_{ij} \in T$  is defined by the driver-load relationship between instances. Four primary edge types  $p \to p, p \to d, d \to d$  are established, where p denotes the driver vertex, d represents the driven vertex. To prevent vertex self-attributes from being disregarded during graph convolution, TD-Placer enforces self-loop connections for both driver and load vertices.

Hierarchical Graph Convolution: TD-Placer employ multi-layer graph convolution to jointly learn attributes of instance vertices and their interconnect topology. Through driver-load relationships, graph convolution aggregates and transforms features from adjacent instance vertices, which are then propagated to subsequent layers via the following implementation:

$$v_i^{l+1} = \sigma \left( \left( \sum_{j \in P(*,i)} w_{ji} v_j^l \right) w^l \right)$$

(4)

where  $P\left(*,i\right)$  denotes the set of vertices pointing to vertex  $v_i, \ v_j^l$  represents the feature vector of the vertex after being updated at layer  $l, \ v_i^{l+1}$  indicates the feature vector after layer l+1's update,  $\sigma$  is the nonlinear activation function,  $w^l$  corresponds to the trainable parameter matrix at layer l, with  $w_{ji}$  defined as:

$$w_{ji} = \frac{1}{\sqrt{(|N_{in}(i)|(|N_{out}(j)|))}}$$

(5)

where  $N_{in}(i)$  denotes the in-degree of vertex i,  $N_{out}(j)$  represents the out-degree of vertex j.

After multi-layer graph convolution, each vertex embedding now encodes multi-hop neighborhood information. A global pooling operation is then applied to these vertex features to derive a unified graph-level representation capturing the complete topological information:

$$y = \frac{1}{N} \sum_{i=1}^{N} v_i \tag{6}$$

where y is the feature vector embedding net topology information, N is the number of component vertices in the current net,  $v_i$  is the feature vector of the i-th vertex.

## D. Net Delay Prediction Component

After processing by net information extraction component, TD-Placer obtains net topology information. It then fuses this with net environment and pin routing features via a multi-layer perceptron (feature vector construction detailed in III-B1), enabling nonlinear modeling of net delay through multi-factor interactions. Figure 6 shows the interaction between extraction and prediction components, along with internal model details.

Firstly, due to net topology dimensionality far exceeding that of the other two feature groups, this imbalance may hinder net prediction. TD-Placer addresses this by passing topology features through a Fully Connected neural network for dimensionality reduction:

$$y' = FC(y) \tag{7}$$

where y' denotes the dimensionality-reduced global feature vector of the net.

Next, TD-Placer concatenates the newly generated global net feature vector y' with the other two feature groups:

$$y_{cat} = [y', y_{net}, y_p] \tag{8}$$

where  $y_{cat}$  represents the concatenated global feature vector,  $y_{net}$  denotes the feature vector of the net environment,  $y_p$  indicates the feature vector of the driver-load pin pair.

Following Batch Normalization, the feature vectors are then fed into a multi-layer feedforward neural network for feature fusion, with residual blocks incorporated to prevent gradient vanishing during training. Finally, a linear layer processes the fused features to get the final net delay netDelay:

$$\hat{y}^{l+1} = \operatorname{Re}Lu(FC^{l}(\hat{y}^{l})) + \hat{y}^{l}$$

(9)

$$netDelay = FC^{end}(\hat{y}^{end})$$

(10)

where  $\hat{y}^{l+1}$  represents the composite feature vector at layer l+1,  $FC^l$  denotes the weight matrix of the feedforward neural network at layer l,  $FC^{end}$  indicates the weight matrix of the linear layer,  $\hat{y}^{end}$  corresponds to the feature vector after feedforward neural network processing.

TD-Placer employs the Smooth Mean Absolute Error loss function [11] for loss minimization. Since net delays are influenced by complex factors (e.g., FPGA architecture, temperature), extreme delay values (outliers) inevitably occur. These outliers may distort the model's judgment and trap it in local optima. Huber Loss is adopted to mitigate the impact of extreme values, ensuring robust model performance.

$$L_{\delta}(\overline{y}, netDelay) = \begin{cases} \frac{1}{2}(\overline{y} - netDelay)^{2}, & \text{if } |\overline{y} - netDelay| \leq \delta \\ \delta |\overline{y} - netDelay| - \frac{1}{2}\delta^{2}, & \text{if } |\overline{y} - netDelay| > \delta \end{cases}$$

(11)

where  $\bar{y}$  denotes the ground truth net delay,  $\delta$  represents the tunable threshold parameter controlling outlier boundaries.

# **Algorithm 1: The Process of Static Timing Analysis**

```

Require: timing graph G, logic delay lookup table T_l,

weight of graph convolution W_t, weight of

mlp W_m, batch size bt

Output: timing graph G', critical path P

1 Initialize i \leftarrow 0:

2 Initialize Net vertex Set A, Net Environment Array B,

Pin Routing Array C, Net Delays D;

g' \leftarrow updateVertexWeights(G, T_l)

4 parallel for i = 1 to qetEdgesSize(G) do

net \leftarrow getNetFromGraph(G, i);

setFeatures(net, i, A, B, C);

7 \mathcal{A}' \leftarrow batchGetNetTopologyInfo(\mathcal{A}, W_t, bt);

8 \mathcal{D} \leftarrow batchGetNetDelay(\mathcal{A}', W_m, bt);

9 parallel for i = 1 to getEdgesSize(G) do

updateGraphArcWeights(G', \mathcal{D}, i);

11 P \leftarrow forwardPropagation(G')

12 backwardPropagation(G')

13 return G', P

```

## E. Global Placement Component

This section outlines the full global placement workflow, highlighting TD-Placer's lightweight integration of the precise timing model introduced in Sections III-C and III-D for static timing analysis, as well as its fine-grained timing-aware weighting method to effectively optimize circuit timing.

- 1) Static Timing Analysis: To reduce the computational complexity of deep learning, TD-Placer employs a lightweight net delay prediction algorithm. Simultaneously, it adopts a hierarchical parallelization strategy to efficiently compute pinlevel timing slack through forward and backward propagation.

- a) Proposed Lightweight Algorithm: During the initial global placement phase, the hierarchical topology of the design netlist is abstracted into a directed acyclic timing graph. The vertex weights in this graph are initialized using a preconstructed logic delay lookup table. As the physical locations of instances are dynamically adjusted throughout the iterative placement process, net delays are recomputed to update the edge weights in the timing graph.

To handle the one-to-many driver-load pin pairs within each net and avoid redundant computations in end-to-end net delay prediction, TD-Placer employs a weight-decoupled architecture that separates graph convolution (for topology extraction) and MLP (for delay regression), with an optimized inference flow (Algorithm 1, lines 1–10). Specifically, the method begins by traversing all timing arcs in the timing graph to update net vertex features, pin routing features, and net environment features on a per-net basis (Lines 4-6 in Algorithm 1). Subsequently, the net information extraction component performs batched processing using GPU acceleration and conducts convolutional inference to efficiently acquire topological information of the nets (Line 7 in Algorithm 1). The net delay prediction component then concatenates the obtained topology information with corresponding pin routing features

| Benchmark                       | BLSTM | DigitRecog | g FaceDetec | t SpooNN | MemN2N | MiniMap2 | OpenPiton | Average |

|---------------------------------|-------|------------|-------------|----------|--------|----------|-----------|---------|

| AMF-Placer [13]                 | 272   | 366        | 159         | 142      | 366    | 543      | 346       | 0.92    |

| TD-Placer (no lightweight alg.) | 408   | 512        | 170         | 182      | 387    | 876      | 547       | 1.29    |

| TD-Placer                       | 284   | 408        | 162         | 160      | 372    | 617      | 384       | 1       |

TABLE III: COMPARISON OF PLACEMENT RUNTIME (S)

and net environment features. These samples are packaged into small batches and fed into the GPU for inference, ultimately yielding net delay predictions (Line 8 in Algorithm 1). Finally, the method performs another parallel traversal of all arcs in the timing graph to update their timing weights (Lines 9-10 in Algorithm 1). This algorithm demonstrates significant reduction in computational overhead for timing analysis, particularly when handling large-scale netlists. Furthermore, TD-Placer parallelizes the feature migration process from CPU to GPU, thereby achieving additional improvements in overall computational efficiency.

We compare the runtime of TD-Placer with and without the lightweight algorithm integrated into placement. As shown in Table III, placement time is reduced by an average of 29% with the lightweight algorithm. TD-Placer incurs 8% more runtime than AMF-Placer due to deep learning overhead. Incorporating more features increases inference parameters, which may be mitigated by larger batch sizes and greater GPU memory.

b) Parallelized Propagation: A path delay typically comprises both logic and net delays. Upon completing net delay prediction, both are stored in the directed acyclic timing graph as vertex and arc weights, respectively. TD-Placer then performs forward and backward propagation on the graph following OpenTimer's [14] timing analysis methodology (Algorithm 1, lines 11–12) to determine slack for each arc. Since vertices at the same timing level are mutually independent, TD-Placer parallelizes the process to reduce runtime. Starting from the first level (outputs of source registers), TD-Placer conducts levelized forward propagation to determine the latest arrival time for each instance:

$$T_{arr}(v_i) = \max_{\forall v_j \in fanin(v_i)} \left( T_{arr}(v_j) + logic(v_j) + netD(u_{ji}) \right)$$

(12)

where  $T_{arr}(v_i)$  denotes the latest signal arrival time at the *i*-th instance,  $logic(v_j)$  is the logic delay of the *j*-th instance,  $netD(u_{ji})$  is the net delay of edge  $u_{ji}$ , and  $fanin(v_i)$  specifies the set of fan-in instances for the *i*-th instance.

Subsequently, TD-Placer performs backward propagation starting from the final level in a levelized manner to determine the earliest required arrival time for each instance:

$$T_{req}(v_i) = \max_{\forall v_j \in fanout(v_i)} (T_{req}(v_j) - logic(v_j) - netD(u_{ij}))$$

(13)

where  $T_{req}(v_i)$  denotes the latest required arrival time at the *i*-th instance, fanout represents the set of fan-out instances for instance *i*.

Finally, TD-Placer obtains the timing slack  $Slack_{ij}$  between driver instance i and load instance j, calculated as:

$$Slack_{ij} = T_{req}(j) - T_{arr}(i) - netD(u_{ij})$$

(14)

While our accurate timing model is time-consuming, the lightweight algorithm mitigates computational costs, and the resulting precise slack offers effective guidance for subsequent timing optimization.

2) Timing-Driven Quadratic Placement: As noted in Section II-B, wirelength-driven placer minimizes weighted wirelength [15], [17], while timing-driven placement adds timing terms to optimize TNS and WNS. TD-Placer introduces a pinto-pin weighting scheme and proposes a global timing and logic-depth-aware strategy to optimize high-risk timing arcs.

a) Timing-arc Based Quadratic Placement Formulation: For high-fanout FPGA designs, applying a uniform worst-case slack-based weight to an entire net can leave timing arcs with positive slack unconstrained, significantly degrading overall TNS [2]. To address this, TD-Placer directly constructs fine-grained pin-to-pin timing loss. In addition, following the original implementation in [13], for long timing paths that span a single FPGA clock region, TD-Placer aims to place all instances on the path within the same clock region. To achieve this, it generates pseudo nets at the horizontal center of the clock region containing more than 50% of the instances on the path, and connect them to the corresponding instances. This guides instances toward the target clock region during optimization and enables vertical placement alignment to alleviate congestion. Based on these considerations, the quadratic cost function for placement is formulated as:

$$\min_{x,y} (1 - \lambda)(WL + WD) + \lambda WT$$

(15a)

with:

$$WL = \sum_{m \in Q} W_m$$

(15b)

$$WD = \sum_{m_p \in Q_p} w_{m_p} W_{m_p}(x, y)$$

(15c)

$$WT = \sum_{u_t \in Q_t} w_{u_t} W_{u_t}(x, y) + \sum_{u_b \in Q_b} w_{u_b} W_{u_b}(x, y)$$

(15d)

where:

- $\lambda$  balances the wirelength and timing optimization terms during global placement.

- $Q_b$  denotes the clock-region-aware pseudo nets set,  $W_{u_b}$  represents their HPWL-based approximations, and  $w_{u_b}$  is the corresponding weight applied to the pseudo nets [13].

- $Q_t$  is the set of timing arcs, and  $w_{u_t}$  is the timing slack-related weight. The slack is defined in Equation 14. And  $W_{u_t}$  is the HPWL approximation of timing arcs.

- b) Depth and Global Timing-Aware Weighting Scheme: In prior timing-driven placer [2],  $w_{u_t}$  is defined as:

$$w_{u_t} = \begin{cases} 0 & slack(u_t) \ge 0\\ \left(1 - \frac{slack(u_t)}{Cl_{require}}\right)^{\alpha} & slack(u_t) < 0 \end{cases}$$

(16)

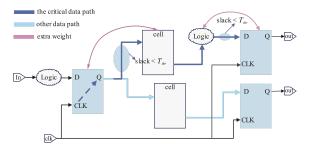

Fig. 7: The illustration of optimizations for the critical path.

where  $Cl_{require}$  is the target delay value, and  $\alpha$  is a constant determined empirically.

While inspired by [13], our method differs in that TD-Placer directly applies additional slack-related weighting coefficients to timing arcs with slack below a predefined threshold, thereby enhancing their optimization strength. Furthermore, as show in Figure 7, if the arc lies on a critical timing path, a small incremental weight is applied to ensure that, within similar slack ranges, the critical path receive higher optimization priority, thereby enabling the delay of the critical path to decrease more steadily. To further refine the optimization strategy for the critical path, TD-Placer introduces an internal prioritization mechanism among timing arcs on the path: arcs farther from the endpoint register are assigned higher weights. This design is based on the observation that optimizing earlystage arcs not only improves local timing but also has a significant cascading effect on the timing of downstream instances, thereby maximizing overall timing improvement.

Therefore, in TD-Placer, the final weighting coefficient  $w_{u_t}$  for each timing arc is defined as follows:

$$w_{u_t} = \left(1 - \frac{slack(u_t)}{Cl_{require}}\right)^{\alpha + \frac{\beta slack(u_t)}{T_{thr}} + \varsigma}$$

(17)

where  $\beta$  is a constant,  $T_{thr}$  is the percentile value used to evaluate the current global timing quality, and  $\varsigma$  is the additional weight assigned to identified critical timing paths, defined as follows:

$$\varsigma = \begin{cases}

0 & u_t \notin path_{critical} \\

\gamma \frac{c_{forward}}{c_{\max}} & u_t \in path_{critical}

\end{cases}$$

(18)

where  $c_{forward}$  is the distance from the current load pin to the endpoint of the critical timing path,  $c_{\max}$  is the total length of the critical path,  $path_{critical}$  denotes the critical timing path, and  $\gamma$  is a small constant determined experimentally.

- 3) Rough Legalization: In FPGAs, resources are location-constrained, requiring instance spreading after each placement iteration. TD-Placer adopts the method from [15], dividing the area into grids, detecting overflows, and redistributing instances to nearby grids until resolved. After spreading, virtual pseudo nets are created based on new instance positions and used as legalization terms during quadratic placement (as shown in Equation 15c) to control instance density.

- 4) Resource Demand/Supply Adjustment: After each rough legalization step, to allow direct legalization and avoid routing congestion, it is necessary to adjust instance resource

demand and available grid resources. TD-Placer adopts the method from [17], dynamically adjusting the resource demand of corresponding instance types when LUT or FF positions change. This method is extended to handle clock constraints by checking for clock overflow: if a half-column clock net in a region exceeds 80% capacity, the FF resource demand for that clock net increases. To further ensure routability, TD-Placer applies the congestion estimation approach from [30], dynamically adjusting available grid resources based on congestion levels and increasing cell spacing in congested regions during later iterations.

#### IV. EVALUATION

## A. Experimental Setup

**Implementation details.** TD-Placer is implemented in C++ and Python. Net extraction and delay prediction components are trained synchronously in Python and integrated into the C++ placement flow via model tracing.

TD-Placer targets the Xilinx UltraScale VU095 FPGA device, but the related techniques can be easily adapted to other devices using general data preprocessing scripts provided by us. The benchmark tests used in the experiments (as shown in Table II) are all applicable to the VU095 device.

**Baselines.** Existing state-of-the-art timing-driven placers include methods proposed by Xiong [2], Mai et al. [23], and AMF-Placer. We adopt AMF-Placer as our primary open-source baseline, as Xiong's method does not support key FPGA primitives widely used in practical designs (e.g., MUX and CARRY8), and Mai et al.'s open-source library lacks essential timing analysis modules. For comprehensive evaluation, we also include five versions of the commercial placer AMD Xilinx Vivado, spanning from 2020.2 to 2024.2.

**Running Platform.** The experimental environment is an Ubuntu 22.04 server, with hardware configurations including an NVIDIA A6000 GPU, a 10-core 4.8GHz CPU (with Turbo Boost support), and 192GB of RAM.

## B. Comparisons to state-of-the-art placers

**Motivation:** In this section, we evaluate the placement performance of TD-Placer on seven benchmarks (as shown in Table II) to verify its effectiveness in real-world scenarios. We integrate TD-Placer into the infrastructure of AMF-Placer [13]. Placement results on seven benchmarks are routed in Vivado, where post-routing CPD and WNS are extracted using the built-in report timing summary for evaluation.

**Results:** The performance of TD-Placer on seven benchmark test sets is shown in Tables IV and V, where "V" represents Vivado, "AMF" represents AMF-placer, and "-" indicates a combination. For example, AMF-V2020 denotes the result of using AMF-placer for placement and Vivado 2020 for routing. Overall, TD-Placer shows a significant advantage over AMF-placer across all three metrics. On the seven benchmark tests with five corresponding Vivado routing versions, the CPD metric improved by an average of 4%, 5%, 4%, 4%, and 4%, respectively. WNS metric improved by 7%, 12%, 6%, 10%, and 4%. Additionally, TNS shows notable improvements in most scenarios. Specifically, in the Vivado 2020,

| EVA | Place-Route        | BLSTM                    | DigitRecog               | FaceDetect             | SpooNN                   | MemN2N           | MiniMap2 | OpenPiton                 | Average |

|-----|--------------------|--------------------------|--------------------------|------------------------|--------------------------|------------------|----------|---------------------------|---------|

|     | V2020 [5]          | -0.562                   | -2.564                   | -0.243                 | -0.779                   | -0.669           | 0.037    | -2.159                    | 0.85    |

|     | AMF-V2020 [13]     | -0.389                   | -3.595                   | -0.384                 | -0.491                   | -1.601           | 0.049    | -2.310                    | 1.07    |

| WNS | TD-Placer-V2020    | -0.33                    | -3.486                   | 0.126                  | -0.489                   | -1.581           | 0.068    | -2.49                     | 1       |

|     | V2021 [6]          | -0.668                   | -3.249                   | -0.264                 | -0.836                   | -0.732           | 0.07     | -2.436                    | 0.88    |

|     | AMF-V2021 [13]     | -0.508                   | - <b>3.249</b><br>-4.373 | -0.264<br>-0.445       | -0.830                   | -0.732<br>-1.665 | 0.07     | -2.430<br>-2.556          | 1.12    |

|     | TD-Placer-V2021    | -0.308<br>- <b>0.356</b> | -4.575<br>-3.98          | -0.443<br><b>0.012</b> | -0.337<br>- <b>0.517</b> | -1.763           | 0.001    | -2.536<br>-2.517          | 1.12    |

|     | 15 1 11001 12021   |                          | 2.70                     |                        |                          | 1.700            | 0.017    | 2.017                     |         |

|     | V2020 [5]          | -18                      | -39689                   | -1.865                 | -17                      | -485             | 0        | -13493                    | _       |

|     | AMF-V2020 [13]     | -18                      | -54278                   | -0.413                 | -9                       | -1269            | 0        | -27189                    | -       |

| TNS | TD-Placer-V2020    | -10                      | -53714                   | 0                      | -14                      | -1214            | 0        | -21595                    | -       |

|     | V2021 [6]          | -54                      | -46804                   | -0.273                 | -18                      | -352             | 0        | -9343                     | _       |

|     | AMF-V2021 [13]     | -21                      | -64569                   | -0.574                 | -18                      | -1676            | ő        |                           | _       |

|     | TD-Placer-V2021    | -14                      | -61372                   | 0                      | -14                      | -1624            | 0        | -9343<br>-28630<br>-19775 | -       |

|     | V2020 [5]          | 0.56                     | 10.61                    | 15.24                  | 8.79                     | 10.67            | 7.96     | 12.17                     |         |

|     | V2020 [5]<br>Rnorm | 8.56<br>1.1              | 0.95                     | 1.02                   | 1.08                     | 0.95             | 1.02     | 12.17                     | 1.02    |

|     | AMF-V2020 [13]     | 8.40                     | 11.64                    | 15.39                  | 8.50                     | 11.60            | 7.96     | 12.38                     | 1.02    |

|     | Rnorm              | 1.08                     | 1.05                     | 1.03                   | 1.05                     | 1.03             | 1.02     | 1.02                      | 1.04    |

|     | TD-Placer-V2020    | 7.79                     | 11.11                    | 1.03<br>14.96          | 8.144                    | 11.24            | 7.782    | 12.14                     | 1.04    |

|     | Rnorm              | 1                        | 11.11                    | 1                      | 1                        | 11.24            | 1        | 1                         | 1       |

| CPD | Kiloriii           |                          | 1                        | •                      |                          | 1                | •        | -                         | •       |

|     | V2021 [6]          | 8.67                     | 11.29                    | 15.27                  | 8.85                     | 10.73            | 7.94     | 12.44                     | _       |

|     | Rnorm              | 1.15                     | 0.93                     | 1.02                   | 1.1                      | 0.93             | 1.08     | 1.01                      | 1.03    |

|     | AMF-V2021 [13]     | 8.51                     | 12.41                    | 15.45                  | 8.55                     | 11.66            | 8.01     | 12.56                     | -       |

|     | Rnorm              | 1.13                     | 1.03                     | 1.03                   | 1.06                     | 1.01             | 1.1      | 1.02                      | 1.05    |

|     | TD-Placer-V2021    | 7.56                     | 12.1                     | 14.98                  | 8.05                     | 11.55            | 7.34     | 12.31                     | -       |

|     | Rnorm              | 1                        | 1                        | 1                      | 1                        | 1                | 1        | 1                         | 1       |

TABLE IV: COMPARISON OF PLACEMENT WNS, TNS, AND POST-ROUTE CPD (NS) USING VIVADO 2020 AND 2021

2021, and 2022 routing versions, FaceDetect transitioned from negative slack to positive slack. BLSTM, DigitRecognition, and Minimap2 demonstrated significant improvements across all Vivado routing versions, while MemN2N, SpooNN, and OpenPiton outperformed AMF-placer in most Vivado routing versions. Compared to the commercial tool Vivado, TD-Placer improved the CPD metric by an average of 2% and 3% for the 2020 and 2021 versions. For the 2022, 2023, and 2024 versions, the average degradation was only 1%, 1%, and 4%, respectively, highlighting the excellent performance of our placer in timing optimization.

Compared to the baseline method, AMF-placer, TD-Placer demonstrates significant improvements in performance. Its advantages primarily stem from two key aspects:

- Equipped with a precise timing model: FPGA net delay is influenced by multiple nonlinear factors, and load and crosstalk coupling effects in multi-pin driving scenarios can significantly impact delay. TD-Placer's timing model considers diverse features and leverages global net representations, learning from large-scale samples to achieve accurate and generalizable delay prediction.

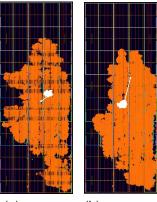

- Considering global timing and fine-grained critical paths weighting: TD-Placer dynamically assesses global timing by assigning extra weights to high-risk arcs, promoting optimization in critical regions. It further prioritizes critical paths based on logic depth to ensure stable delay reduction during iteration. As shown in Figure 8, our placement on digitRecognition benchmark achieves a significantly shorter critical path than AMF-Placer.

#### C. The accuracy of the end-to-end delay prediction

**Motivation:** We evaluate TD-Placer's end-to-end delay prediction (referred to as the TD-Placer-DP) accuracy on the

(a) TD-Placer (b) AMF-Placer

Fig. 8: Comparison between TD-Placer and AMF-Placer placement results on digitRecognition [45].

dataset from Section III-B2, comparing it with Random Forest (RF), Gradient Boosting Regression (GBR), and AMF-Placer's piecewise polynomial model [13]. Hyperparameters are tuned via grid search on the validation set for optimal comparison.

**Results:** The performance comparison of different regression models on the same test set is presented in VI. Specifically, TD-Placer-DP achieves the best generalization performance, with a Mean Absolute Error (MAE), Root Mean Square Error (RMSE), and R<sup>2</sup> of 0.097, 0.171, and 0.80, respectively. The piecewise linear regression model adopted in AMF-placer ranks second, with MAE, RMSE, and R<sup>2</sup> values of 0.119, 0.186, and 0.71. In contrast, Random Forest and Gradient Boosting Regression show inferior generalization ability, with their respective metrics being 0.178, 0.279, 0.63 and 0.198, 0.314, 0.60. The limited generalization of models like RF and GBR arises from their reliance on single-feature

TABLE V: COMPARISON OF PLACEMENT WNS, TNS, AND POST-ROUTE CPD (NS) USING VIVADO 2022-2024

| EVA | Place-Route              | BLSTM               | DigitRecog    | FaceDetect           | SpooNN       | MemN2N        | MiniMap2            | OpenPiton     | Averag |

|-----|--------------------------|---------------------|---------------|----------------------|--------------|---------------|---------------------|---------------|--------|

|     | V2022 [4]                | -0.627              | -4.516        | 0.252                | -0.349       | -0.842        | 0.009               | -2.054        | 0.91   |

|     | AMF-V2022 [13]           | -0.5                | -4.62         | 0.37                 | -0.481       | -1.876        | -0.001              | -2.385        | 1.06   |

|     | TD-Placer-V2022          | -0.462              | -3.927        | 0.407                | -0.681       | -1.922        | 0.024               | -2.376        | 1      |

| WNS | V2023 [7]                | -0.972              | -3.642        | 0.12                 | -0.391       | -0.698        | 0.048               | -1.946        | 0.82   |

|     | AMF-V2023 [13]           | -0.489              | -4.862        | 0.085                | -0.643       | -1.862        | -0.001              | -2.345        | 1.1    |

|     | TD-Placer-V2023          | -0.435              | -4.216        | 0.216                | -0.703       | -1.812        | 0.067               | -2.297        | 1      |

|     | V2024 [8]                | -0.546              | -2.917        | 0.086                | -0.396       | -0.648        | 0.046               | -2.182        | 0.74   |

|     | AMF-V2024 [13]           | -0.387              | -4.275        | 0.296                | -0.672       | -1.684        | 0.024               | -2.47         | 1.04   |

|     | TD-Placer-V2024          | -0.345              | -3.957        | 0.356                | -0.652       | -1.923        | 0.029               | -2.38         | 1      |

|     | V2022 [4]                | -11                 | -69667        | 0                    | -6           | -501          | 0                   | -6807         | -      |

|     | AMF-V2022 [13]           | -27                 | -66195        | 0                    | -20          | -1610         | 0                   | -26799        | -      |

|     | TD-Placer-V2022          | -9                  | -62801        | 0                    | -14          | -1712         | 0                   | -20922        | -      |

| TNS | V2023 [7]                | -44                 | -50880        | 0                    | -6           | -309          | 0                   | -11251        | -      |

|     | AMF-V2023 [13]           | -23                 | -64726        | 0                    | -18          | -1527         | -0.001              | -26994        | -      |

|     | TD-Placer-V2023          | -17                 | -61251        | 0                    | -12          | -1745         | 0                   | -19690        | -      |

|     | V2024 [8]                | -13                 | -44019        | 0                    | -7           | -271          | 0                   | -9680         | -      |

|     | AMF-V2024 [13]           | -19                 | -58803        | 0                    | -19          | -1649         | 0                   | -27530        | -      |

|     | TD-Placer-V2024          | -8                  | -61307        | 0                    | -12          | -1522         | 0                   | -21363        | -      |

|     | V2022 [4]                | 8.07                | 12.38         | 17.4                 | 7.51         | 10.3          | 7.98                | 11.72         | -      |

|     | Rnorm                    | 1.02                | 1.08          | 1.04                 | 0.96         | 0.85          | 1.05                | 0.96          | 0.99   |

|     | AMF-V2022 [13]           | 8.16                | 11.97         | 17.92                | 8.32         | 12.43         | 7.92                | 12.5          | -      |

|     | Rnorm                    | 1.03                | 1.05          | 1.07                 | 1.07         | 1.03          | 1.04                | 1.01          | 1.04   |

|     | TD-Placer-V2022          | 7.92                | 11.42         | 16.68                | 7.81         | 12.1          | 7.59                | 12.41         | -      |

|     | Rnorm                    | 1                   | 1             | 1                    | 1            | 1             | 1                   | 1             | 1      |

|     | V2023 [7]                | 7.86                | 11.29         | 17.78                | 7.77         | 10.91         | 8.26                | 11.76         | -      |

| CPD | Rnorm                    | 1.0                 | 0.96          | 1.05                 | 0.97         | 0.91          | 1.06                | 0.95          | 0.99   |

|     | AMF-V2023 [13]           | 8.14                | 12.14         | 18.24                | 8.34         | 12.38         | 8.17                | 12.43         | 1.04   |

|     | Rnorm<br>TD-Placer-V2023 | 1.04<br><b>7.83</b> | 1.04<br>11.71 | 1.08<br><b>16.91</b> | 1.05<br>7.97 | 1.03<br>12.04 | 1.05<br><b>7.78</b> | 1.01<br>12.34 | 1.04   |