TOPICAL WORKSHOP ON ELECTRONICS FOR PARTICLE PHYSICS - TWEPP2025 6-10 October 2025 Rethymno, Crete, Greece

# Analysis of Single Event Induced Bit Faults in a Deep Neural Network Accelerator Pipeline

Naïn Jonckers, $^{a,1}$  Toon Vinck, $^{a,b}$  Peter Karsmakers $^a$  and Jeffrey Prinzie $^a$

<sup>a</sup>KU Leuven, Kleinhoefstraat 4, Geel, Belgium <sup>b</sup>Magics Technologies, Cipalstraat 3, Geel, Belgium

E-mail: nain.jonckers@kuleuven.be

ABSTRACT: In recent years, the increased interest and the growth in application domains of Artificial Intelligence (AI), and more specifically Deep Neural Networks (DNNs), has led to an extensive usage of domain specific DNN accelerator processors to improve the computational efficiency of DNN inference. However, like any digital circuit, these processors are prone to faults induced by radiation particles such as heavy ions, protons, etc., making their use in harsh radiation environments a challenge.

This work presents an in-depth analysis of the impact of such faults on the computational pipeline of a Systolic Array based Deep Neural Network accelerator (SA-DNN accelerator) by means of a Register Transfer Level (RTL) Fault Injection (FI) simulation in order to improve the observability of each hardware block. From this analysis, we present the sensitivity to single bit faults of register groups in the pipeline for three different DNN workloads utilising two datasets, namely MNIST and CIFAR-10. These sensitivity figures are presented in terms of Fault Propagation Probability ( $P(f_{non-crit})$ ) and False Classification Probability ( $P(f_{crit})$ ) which respectively show the probability that an injected fault causes a non-critical error (numerical offset) or a critical error (classification fault). From these results, we devise a fault mitigation strategy to harden the SA-DNN accelerator in an efficient way, both in terms of area and power overhead.

Keywords: Computing, Data processing methods, Digital electronic circuits, Simulation methods and programs

<sup>&</sup>lt;sup>1</sup>Corresponding author.

#### 1 Introduction

Recent advancements in Artificial Intelligence (AI), and specifically Deep Neural Networks (DNNs), have led to machine implementations that often outperform human cognitive abilities. This has caused an increased interest in the usage of DNNs in applications such as space satellite imagery [1] for, among others, bandwidth reduction and also particle physics [2]. These applications have challenging requirements due to bit faults induced by radiation and require either a form of physical hardening or circuit based hardening [1].

Additionally, DNN inference has high computational demands, requiring domain specific processors to compute these workloads with a good power efficiency, which is especially important in edge applications [3]. However, previous work has shown that commercial DNN accelerators such as Intel's Movidius Myriad X VPU and Google's Edge TPU are only suited for short duration low earth orbit missions [4], making their usage in high energy physics applications not feasible. To improve the reliability of such accelerators, techniques such as software-based mitigation or multiple redundant hardware processors are typically used [5], however, these techniques negatively impact the overall power efficiency [6]. More efficient techniques usually focus on (1) efficient hardware mitigation using techniques such as razor flip-flops, error correcting codes, etc. or (2) fault-aware training of DNNs [5]. The latter approach leverages the inherent redundancy that neural networks can have when trained properly. However, due to the complex nature of DNN models, propagation of faults on a hardware or DNN accelerator level is often not well understood [7, 8].

To fill this knowledge gap, this work will perform a case study on a, often used, 8-bit quantised Systolic Array based Deep Neural Network accelerator (SA-DNN accelerator) to analyse the fault propagation behaviour of DNN workloads on a hardware level. This analysis can be achieved by either performing physical beam tests or by utilising a Fault Injection (FI) simulation. While beam tests offer a more accurate representation of real-world conditions [8], they provide limited insights into fault propagation within the accelerator logic due to physically limited on-chip signal observation. Although essential for evaluating reliability and fault tolerance, beam testing alone may not yield sufficient information for strategic fault mitigation. Therefore, in this work, we conduct a FI injection simulation using a digital Register Transfer Level (RTL) simulation environment utilising standard SystemVerilog force and release statements to inject faults on critical Flip-Flop (FF) nodes in the accelerator pipeline, allowing for a much better observability of fault propagation.

This paper is organized as follows: Section 2 describes the hardware architecture of the SA-DNN accelerator and explains the data flow through this pipelined architecture. In section 3, we present our FI methodology and simulation. The results are presented and discussed in section 4 and finally, a conclusion together with potential future work is presented in section 5.

## 2 Accelerator architecture

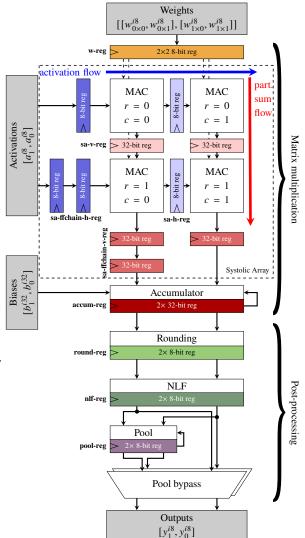

This work evaluates a SA-DNN accelerator which includes, as the name implies, a Systolic Array (SA). SAs were already described in 1979 [9], but have only recently been widely used in DNN accelerators such as the Google TPU [10], due to their efficient computation of matrix and tensor products [11], which are an essential part of DNNs. The employed SA in this work's SA-DNN accelerator is shown at the top of Figure 1 for a 2×2 parametrisation (2 rows and 2 columns).

Aside from matrix multiplications, which are used heavily in DNN Fully-Connected (FC) or "dense" layers, 2D Convolution (Conv2D) layers can also be computed by the SA. This is accomplished by converting Conv2D operations into a matrix multiplication by means of convolution unrolling [12].

When computing these layers, activation inputs and layer weights are first loaded into the SA. Since the employed SA is weight-stationary, weights are kept statically for each (partial) matrix multiplication whilst activations are slanted and flow from left to right through Multiply Accumulate (MAC) units. These perform one multiply accumulate calculation of the form  $u_{r\times c}^{i32} = a_r^{i8} w_{r\times c}^{i8}$  into a 32-bit register to account for overflow, with  $a_r^{i8}$  a signed 8-bit activation input for row r,  $w_{r \times c}^{i8}$  a stationary signed 8-bit weight for row r and column c and  $u_{r \times c}^{i32}$  a signed 32-bit partial result for row r and column c. Thus partial results flow from the top to the bottom of the SA. Often the parametrisation of the SA  $(2\times2)$ in Figure 1) will be smaller than the actual matrix multiplication. To handle this, a column-wide 32bit accumulator is foreseen which can also add an additional bias  $b_c^{i32}$  to the final layer result. Thus, for each column c, Equation 2.1 is computed, where R is the total number of rows, resulting in a total vector-matrix multiplication over each column c:

$$y_c^{i32} = b_c^{i32} + \sum_{r=0}^{R-1} \left( a_r^{i8} w_{r \times c}^{i8} \right)$$

(2.1)

**Figure 1**: Block diagram of the SA-DNN accelerator pipeline for a 2×2 parametrisation

After accumulating the 32-bit partial sums from the

SA in the accumulators for each column, the result is rescaled to an 8-bit resolution in the "rounding" block. This is required since all memories in the SA-DNN accelerator are 8-bit quantised (except for the bias) as mentioned before. Hence the final result should also be rescaled to this resolution.

To accomplish this, the rounding block applies a scale factor s to the 32-bit accumulator result. This scale factor is constrained to a power of two so that the usual division by this scale factor, becomes a simple right shift  $S = \log_2(1/s)$  in hardware [13, 14]. Furthermore, the shifted result is rounded and clipped to the 8-bit signed integer range. This operation can thus contribute positively to fault masking by discarding least significant bits of the 32-bit accumulated result (shift operation) as well as discarding some most significant bits of this result (clipping). This leads to Equation 2.2 where the matrix multiplication result is re-quantised to 8-bit using this rounding operation.

$$y_c^{i8} = \text{clip}\left(\text{round}\left(b_c^{i32} + \sum_{r=0}^{R-1} \left(a_r^{i8} w_{r \times c}^{i8}\right)\right)\right) >> S$$

(2.2)

Finally, after the rounding stage, a Non-Linear Function (NLF) block is implemented which can compute any non-linear function by utilizing a Lookup Table (LUT) structure. After this NLF stage, a final pooling stage is foreseen which can compute max-pool layers, commonly employed by many DNNs, and specifically Convolutional Neural Networks (CNNs). This unit can be bypassed since pooling is not required after each DNN layer.

# 3 Test methodology

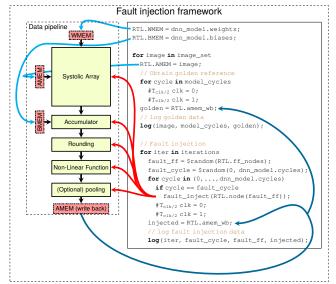

In order to improve the observability of fault propagation in data pipeline registers, this work performs several FI experiments using RTL simulations. The constructed framework for these experiments is highlighted in Figure 2. The right-hand side of this figure shows a pseudo-algorithm of the FI framework and the left-hand side shows the simplified accelerator data pipeline from Figure 1, where AMEM, WMEM and BMEM respectively hold the model's input/output activations  $(a_r^{i8}, y_c^{i8})$ , weights  $(w_{r\times c}^{i8})$  and biases  $(b_c^{i32})$ .

For each selected DNN model, we first load the model's weights and biases into their respective memories. Then, for

Figure 2: Simulation FI framework

several input images we perform multiple inferences, where each first inference computes the golden reference (i.e. no fault injected) for that specific input image. Consecutive inferences for the same image will then inject a fault at (1) a random cycle and (2) a random register FF. The DNN output after each of these FI inferences is then compared to the golden reference to assess fault propagation for that specific register FF. The following DNNs were used based on a trade-off between the time needed for statistically relevant FI simulations and representativeness to typical DNN and DNN layer usage:

- **3L-FC** + **MNIST**: 3-Layer FC network with intermediate ReLU activation function, trained on MNIST (post-quantisation accuracy: 96.9%)

- LeNET + MNIST: LeNET with ReLU and max-pooling, trained on MNIST (post-quantisation accuracy: 98.6%)

- LeNET + CIFAR-10: Modified (increased to 3 input channels) LeNET with ReLU and max-pooling, trained on CIFAR-10 (post-quantisation accuracy: 70.8%)

When comparing the classification result of an inference to the golden reference, three situations can occur: (i) No difference is observed due to the model's redundancy or fault masking by the post-processing stages such as rounding and NLF activation (e.g. ReLU). (ii) An injected fault may cause a numerical difference on the DNN model's output logits but not cause any classification corruption. In this case, we classify the fault in the Fault Propagation Probability ( $P(f_{non-crit})$ ) category, which is the likelihood that an injected fault for a specific register, causes a non-critical

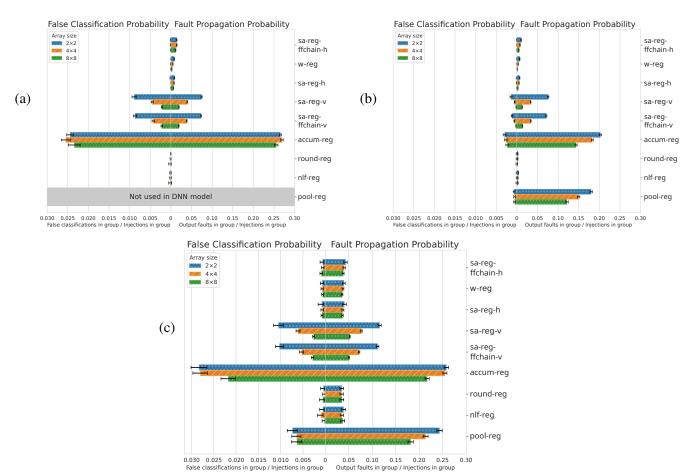

**Figure 3**: DNN test results for: (a) 3-Layer FC network with MNIST, (b) LeNET with MNIST and (c) LeNET with CIFAR-10

DNN output fault. (iii) An injected fault causes a classification corruption in which case we classify it in the False Classification Probability ( $P(f_{crit})$ ) category, which is the likelihood that an injected register fault causes a critical DNN output fault.

### 4 Results

Figure 3 shows the FI results for the three DNNs. The right-hand side of each figure shows  $P(f_{non-crit})$  for each register whereas the left-hand side shows  $P(f_{crit})$ . Across all DNNs, the impact of faults appears to be similar across four groups of registers. To simplify the discussion of the results, we propose four groups: (i) 8-bit SA registers (w-reg, sa-ffchain-h-reg, sa-h-reg), (ii) 32-bit SA registers (sa-ffchain-v-reg, sa-v-reg), (iii) 32-bit accumulator registers (accum-reg) and (iv) post-processing registers (round-reg, nlf-reg, pool-reg).

For the first **3L-FC** network, trained on MNIST, DNN in Figure 3 (a), the first observation is that neither the 8-bit SA nor the post-processing registers contribute significantly to  $P(f_{non-crit})$  and  $P(f_{crit})$  (note that pooling is not used in this model). This is due to their small (8-bit) Dynamic Range (DR) and the fact that the post-processing registers can mask faults by shifting (round-reg) and NLF activation (such as ReLU). In contrast, the 32-bit SA registers have much higher fault probabilities up to about 25%  $P(f_{crit})$  for the 32-bit accumulator. This can be attributed to their

high DR, which increases the probability that a single-bit fault, during inference, causes an output difference large enough to cause a DNN misclassification. The accumulator register has an even higher  $P(f_{non-crit})$  and  $P(f_{crit})$ , which can be explained by the fact that it has a large Temporal Vulnerability  $(t_v)$  when accumulating many partial matrix multiplication results over a longer period of time. Finally, it is clear that the 32-bit SA register sensitivity decreases as the SA size is scaled up. Fortunately, a larger array is also more efficient for calculating large matrix multiplications which are prevalent in modern DNN models.

When looking at **LeNET with MNIST**, a CNN model with pooling layers, in Figure 3 (b), we observe a large decrease in  $P(f_{crit})$  from around 25% in the 3L-FC network to a maximum of about 2.5% in this network even though the values for  $P(f_{non-crit})$  are in the same order of magnitude, albeit slightly lower. This can be attributed to an increased model redundancy of LeNET compared to a simple 3L-FC network. Furthermore, we now also observe a large  $P(f_{non-crit})$  of almost 18% for a 2×2 SA in the pooling registers. This can be attributed to a larger  $t_v$  of this register since it is also a form of accumulator register. However due to its small DR of 8-bit and the fact that pooling layers are used only as the first LeNET layers, the impact on  $P(f_{crit})$  is again negligible like the rest of the post-processing registers.

Finally, **LeNET with CIFAR-10**, highlighted in Figure 3 (c), exhibits increased fault probabilities compared to LeNET with MNIST, where the worst-case  $P(f_{crit})$  reaches up to 30% for the accumulator register. Rather than being the cause of the switch to a different dataset (CIFAR-10), it is more probable that this increased  $P(f_{crit})$  is due to a reduced training accuracy compared to LeNET with MNIST (70.8% v.s. 98.6%). CIFAR-10 exhibits a more complex classification task and thus increases the uncertainty of the model, leading to al lower accuracy and a reduced margin for error [15]. As such, smaller numerical errors are more likely lead to misclassifications. This highlights that the training process also strongly impacts fault propagation during DNN inference.

## 5 Conclusions

In this work, we performed RTL FI simulations on a SA-DNN accelerator to increase observability of fault propagation in internal pipeline registers. We observed that, on a **hardware level**, the main contributor to an increased fault propagation probability, both in terms of  $P(f_{non-crit})$  and  $P(f_{crit})$ , was (1) the DR and (2)  $t_v$  of a register. Hence, the 32-bit SA and the 32-bit accumulator registers are the most vulnerable. Furthermore, on a **model level**, it was observed that from the 3L-FC model to LeNET (both trained on MNIST) a factor 10 decrease in  $P(f_{crit})$  occurred, highlighting that the DNN model's inherent redundancy also plays an important role in fault propagation. Finally between LeNET trained on MNIST and LeNET trained on CIFAR-10, an increase of more than 10 times is observed due to the latter model's lower training accuracy (70.8% v.s. 98.6%), highlighting that the model's training phase is also very important to the overall fault propagation.

From these results it is clear that, in order to obtain a power and area efficient fault tolerant DNN accelerator, one needs to take both hardware and the software DNN model into account. By leveraging proper DNN model training fault propagation can already be reduced significantly in software. Further faults can efficiently be detected in hardware using for instance a low-overhead fault check mechanism [16] and then optionally recomputed. By leveraging this hardware-software co-design a very efficient, fault tolerant AI accelerator can be designed.

## References

- [1] Vivek Kothari, Edgar Liberis, and Nicholas D. Lane. The Final Frontier: Deep Learning in Space, 2020. URL https://arxiv.org/abs/2001.10362.

- [2] Dan Guest, Kyle Cranmer, and Daniel Whiteson. Deep Learning and Its Application to LHC Physics. *Annual Review of Nuclear and Particle Science*, 68(1):161–181, October 2018. ISSN 1545-4134. doi: 10.1146/annurev-nucl-101917-021019. URL http://dx.doi.org/10.1146/annurev-nucl-101917-021019.

- [3] Md Shahanur Alam, Chris Yakopcic, Qing Wu, Mark Barnell, Simon Khan, and Tarek Taha. Survey of Deep Learning Accelerators for Edge and Emerging Computing. *Electronics*, 13:2988, 07 2024. doi: 10.3390/electronics13152988.

- [4] Devin P. Ramaswami, David M. Hiemstra, Zhi Wu Yang, Shuting Shi, and Li Chen. Single Event Upset Characterization of the Intel Movidius Myriad X VPU and Google Edge TPU Accelerators Using Proton Irradiation. In 2022 IEEE Radiation Effects Data Workshop (REDW) (in conjunction with 2022 NSREC), pages 1–3, 2022. doi: 10.1109/REDW56037.2022.9921608.

- [5] Sparsh Mittal. A survey on modeling and improving reliability of DNN algorithms and accelerators. *Journal of Systems Architecture*, 104:101689, 2020.

- [6] Younis Ibrahim, Haibin Wang, Junyang Liu, Jinghe Wei, Li Chen, Paolo Rech, Khalid Adam, and Gang Guo. Soft errors in DNN accelerators: A comprehensive review. *Microelectronics Reliability*, 115:113969, 2020.

- [7] Guanpeng Li, Siva Kumar Sastry Hari, Michael Sullivan, Timothy Tsai, Karthik Pattabiraman, Joel Emer, and Stephen W Keckler. Understanding Error Propagation in Deep Learning Neural Network (DNN) Accelerators and Applications. In *Proceedings of the international conference for high performance computing, networking, storage and analysis*, pages 1–12, 2017.

- [8] Paolo Rech. Artificial Neural Networks for Space and Safety-Critical Applications: Reliability Issues and Potential Solutions. *IEEE Transactions on Nuclear Science*, 71(4):377–404, 2024.

- [9] Hsiang-Tsung Kung. *Why systolic architecture?* Design Research Center, Carnegie-Mellon University Pittsburgh, PA, USA, 1982.

- [10] Shamik Kundu, Suvadeep Banerjee, Arnab Raha, Suriyaprakash Natarajan, and Kanad Basu. Toward Functional Safety of Systolic Array-Based Deep Learning Hardware Accelerators. *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, 29(3):485–498, 2021.

- [11] Rui Xu, Sheng Ma, Yang Guo, and Dongsheng Li. A Survey of Design and Optimization for Systolic Array-based DNN Accelerators. *ACM Computing Surveys*, 56(1):1–37, 2023.

- [12] Kumar Chellapilla, Sidd Puri, and Patrice Simard. High Performance Convolutional Neural Networks for Document Processing. In *Tenth international workshop on frontiers in handwriting recognition*. Suvisoft, 2006.

- [13] Benoit Jacob, Skirmantas Kligys, Bo Chen, Menglong Zhu, Matthew Tang, Andrew Howard, Hartwig Adam, and Dmitry Kalenichenko. Quantization and Training of Neural Networks for Efficient Integer-Arithmetic-Only Inference, 2017. URL https://arxiv.org/abs/1712.05877.

- [14] Markus Nagel, Marios Fournarakis, Rana Ali Amjad, Yelysei Bondarenko, Mart van Baalen, and Tijmen Blankevoort. A White Paper on Neural Network Quantization, 2021. URL https://arxiv.org/abs/2106.08295.

- [15] Lucas Roquet, Fernando Fernandes dos Santos, Maria Kastriotou, and Angeliki Kritikakou. Strategic Input Selection For Deep Neural Networks Reliability Evaluation. In NSREC 2025-IEEE Nuclear & Space Radiation Effects Conference, 2025.

- [16] Elbruz Ozen and Alex Orailoglu. Low-Cost Error Detection in Deep Neural Network Accelerators with Linear Algorithmic Checksums. *Journal of Electronic Testing*, 36(6):703–718, 2020.