# Architect in the Loop Agentic Hardware Design and Verification

Mubarek Mohammed Western Washington University Bellingham, WA USA mohammm6@wwu.edu

Abstract—The ever increasing complexity of the hardware design process demands improved hardware design and verification methodologies. With the advent of generative AI various attempts have been made to automate parts of the design and verification process. Large language models (LLMs) as well as specialized models generate hdl and testbenches for small components, having a few leaf level components. However, there are only a few attempts to automate the entire processor design process. Hardware design demands hierarchical and modular design processes. We utilized this best practice systematically and effectively. We propose agentic automated processor design and verification with engineers in the loop. The agent with optional specification tries to break down the design into sub-components, generate HDL and cocotb tests, and verifies the components involving engineer guidance, especially during debugging and synthesis. We designed various digital systems using this approach. However, we selected two simple processors for demonstration purposes in this work. The first one is a LEGv8 like a simple processor verified, synthesized and programmed for the DE-10 Lite FPGA. The second one is a RISC-V like 32bit processor designed and verified in similar manner and synthesized. However, it is not programmed into the DE-10 Lite. This process is accomplished usually using around a million inference tokens per processor, using a combination of reasoning (e.g gemini-pro) and nonreasoning models (eg. gpt-5-mini) based on the complexity of the task. This indicates that hardware design and verification experimentation can be done cost effectively without using any specialized hardware. The approach is scalable, we even attempted system-on-chip, which we want to experiment in our future work.

Index Terms—Agentic Design, Hardware Description Language, Architecture, RISC-V, SystemVerilog, LLM, FPGA, Design Automation

#### I. Introduction

The domain of digital systems design, traditionally characterized by long development cycles, extensive manual effort, and a high barrier to entry, is poised for transformation by advances in Artificial Intelligence [1]. Large Language Model (LLM) based AI agents now possess the capability to understand natural language specifications and generate hardware description languages (HDLs) like SystemVerilog and VHDL. This promises to automate tedious coding tasks, lower the

barrier to entry for hardware design, and accelerate the critical design verification loop.

However, moving from single file code generation to agentic, system-level design introduces significant challenges related to maintaining architectural integrity, managing complex dependencies, and ensuring semantic consistency across dozens of files. Recent work such as AutoChip [2] and other end-to-end synthesis frameworks [3] have made significant strides, particularly in high-level synthesis (HLS) and domain-specific accelerator design. Yet, a gap remains in understanding the practical capabilities and limitations of agentic systems for general-purpose, register-transfer level (RTL) CPU design, a domain that demands attention to detail, from instruction set architecture (ISA) to microarchitectural data paths.

This case study investigates a practical application of this emerging technology through a framework we term the "Blueprint-Driven Agent". We tasked an AI agent with several complete design challenges of increasing complexity: a simple single-cycle LEGv8-style processor, a synthesizable 32-bit RISC-V core, a pipelined LEGv8 processor, and others(not reported in this work). The methodology was rooted in a blueprint-driven approach, where the AI first generates a high-level JSON specification, defining the system's architecture, which it then uses to create, verify, and self-correct the necessary HDL components by using cocotb testing.

The objective was to rigorously assess the AI's efficacy not just in localized code generation, but in its ability to compose a complex, functional, and synthesizable system. While initial results in component generation and verification were impressive, system-level verification invariably revealed critical failures. This paper documents the collaborative human-AI debugging journey, providing a granular analysis of the agent's limitations, and offers a refined "Architect-in-the-Loop" workflow as a powerful and economically viable paradigm for future hardware design.

#### II. RELATED WORKS

In this section we discuss the major works in this area.

# A. Verilog Generation and Evaluation

There are several attempts to fine tune LLMs to better generate Verilog hdl code. Some of them are BetterV [4], VerilogEval [6], and RTL coder [5]. The focus of these works is to evaluate the models capability for small modules. This is close to the leaf level components or components with few subcomponents. Even though we use LLMs to generate SystemVerilog code components, the strength of our work comes from how we hierarchically build complex digital systems including processors.

In our work, we mainly use LLMs with a combination of reasoning models (for planning, debugging/fix, and integration) and non-reasoning models (for code and testbench generation).

# B. AI Assisted Digital Systems Design

The work very close to ours conceptually is Chip-Chat [1]. They tried to build a small processor from scratch by chatting with LLMs. An experienced engineer (the author) prompted the LLM to give the required modules, debugged it, and iteratively improved it to generate a working processor. Chip-Chat purely involves the engineer and chat bot, with parts of the code being broken up into separate chats. They even continued to the tiny-tapeout process for manufacturing. In our case, we automate the hierarchical and modular design process. Another work, AutoChip [2] used LLMs to build small digital circuits by incorporating self-feedback loop, very similar to ours at the component level. However, AutoChip does not create more complicated components and hierarchical components.

Our work partially or completely automates the process through agentic digital systems design. The experiment in this work is done considering the human engineer playing a critical role in the digital systems design process such as a simple processor development process. The engineer/architect can provide specification in terms of JSON blueprint as well as a text prompt. Once the agent starts, if a component fails the agent initiates a self-correction loop. However, it waits for the engineer to provide feedback and approves the fix. The engineer at this stage can edit the failed hdl or test files and let the agent continue. In a separate work of ours for experimental purposes, not published, we even let the agent run end-to-end without human intervention just starting from blueprint or prompt specification. However, even in this case the engineer has the option to edit code especially if the agent is struggling to fix some issues.

#### III. THE AI-DRIVEN DESIGN METHODOLOGY

Our framework is designed to emulate and enhance a modern, specification-driven workflow. It leverages an AI agent for code generation, verification, and selfcorrection, all under the strategic supervision of a human architect. The core components of this methodology are outlined below.

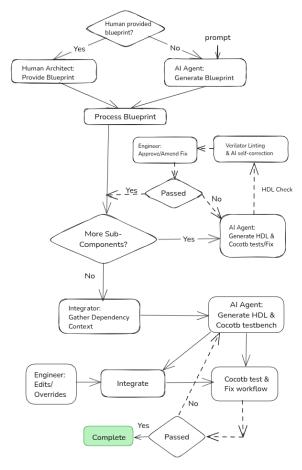

Fig. 1: Agentic Digital Design Flow with Human-in-the-Loop Feedback and Approval at Each Stage

For sample code look at the appendix. The details are also hosted on github. <sup>1</sup>

# A. Phase 1: The Blueprint as a Formal Specification

The foundation of each project is a JSON blueprint, which can either be provided by a human architect or generated by the agent from a high-level natural language prompt. This document serves as the formal, machine-readable specification, defining:

- Global project parameters (e.g., data widths, memory depths).

- An optional SystemVerilog package for defining a shared Instruction Set Architecture (ISA).

<sup>&</sup>lt;sup>1</sup>https://github.com/mmubarek/eda/tree/main/paper1

A hierarchical list of all required system components, their individual interfaces (ports and parameters), and their inter-dependencies.

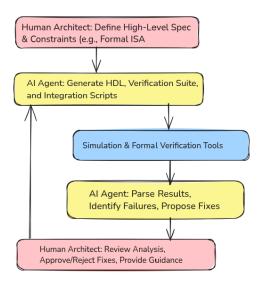

A key observation, which became central to later debugging efforts, was that initial agent-generated blueprints often omitted a formal ISA definition or created contradictory parameterizations. Our refined methodology (Figure 2) now employs a highly structured prompt that explicitly guides the agent to produce a complete and non-contradictory blueprint as the first step.

TABLE I: Key Parameters Defined in an Example AI-Generated Blueprint

#### Parameter

DATA\_WIDTH

ADDRESS\_WIDTH

INSTRUCTION\_WIDTH

OPCODE\_WIDTH

REG\_ADDR\_WIDTH

In addition to these parameters, ISA related parameters are defined in the blueprint.

B. Phase 2: Component Generation, Integration, and Self-Correction

Using the blueprint, the agent's orchestrator processes each component according to its dependency graph. For each sub-module, the following workflow is applied:

- 1) **HDL and Testbench Generation:** The agent generates a synthesizable SystemVerilog module and a corresponding cocotb testbench.

- Pre-Flight Linting (Verilator): A lightweight compilation check using Verilator in linting mode is performed first to efficiently detect syntax and structural errors.

- If the linting passes, the workflow proceeds to functional verification.

- If the linting fails, the agent analyzes the error log, proposes a fix, and submits it for human approval. Upon approval, the design is retried.

- 3) Functional Verification (cocotb): If linting succeeds, the sub-module is tested against its cocotb unit testbench. Failures here typically expose behavioral or semantic errors.

- As with linting, testbench failures trigger a selfcorrection loop: error analysis → candidate fix → human approval → re-verification.

- The number of retry attempts is bounded by a configurable limit (e.g., three attempts per component). If the limit is reached, the human engineer may step in directly to provide manual edits.

- 4) **Human Overrides:** At any stage, the engineer can manually modify the HDL or testbench. The

agent then re-verifies the edited design to ensure correctness before allowing it to proceed.

This iterative, human-in-the-loop process ensures that every component is both structurally correct and functionally validated before integration.

Once all sub-modules pass their unit tests, the orchestrator enters the integration phase, generating a top-level module that instantiates and interconnects the verified components. This step is itself subject to the same linting, verification, and human approval loops, since interface mismatches or wiring errors commonly arise during integration.

# C. Phase 3: System-Level Verification

With all components integrated, the agent generates a cycle-accurate top-level cocotb testbench. The verification strategy follows a *golden model* approach: a Python implementation of the ISA maintains an internal model of the processor's architectural state (registers and memory). For each executed instruction, the golden model predicts the expected state updates, which are then compared against the DUT's debug outputs at every cycle.

This strategy uncovers subtle, cross-module issues such as pipeline hazards, bus arbitration errors, or timing mismatches that are not visible at the unit-test level. Failures again trigger the same AI self-correction loop with mandatory human approval, ensuring both automation and accountability.

Only after passing system-level verification is the design returned to the engineer for FPGA synthesis, hardware debugging, and physical validation. This final step ensures that ultimate responsibility and fine-grained optimization remain in human hands, even as the agent automates the majority of the design flow.

# IV. DEBUGGING AND ROOT CAUSE ANALYSIS

Debugging and analysis continues for the top level module if there is failure. This initiates an iterative debugging process that reveals a pattern of agent failure modes. This process was repeated across other designs, confirming our analysis. Table II provides a detailed log of representative bugs discovered, their root cause, and the corresponding solution, which often involved refining the agent's underlying prompting strategies.

# V. ANALYSIS OF AGENTIC CAPABILITIES AND LIMITATIONS

This case study, in our view, provides a snapshot of the current capabilities and, more importantly, the systemic limitations of LLM agents in digital design.

TABLE II: Summary of observed errors, root causes, and applied solutions in LLM-assisted hardware design.

| Error                                              | Cause                                                                     | Solution                                                                                                                                                |

|----------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inconsistent ISA implementations                   | LLM generated<br>mismatched<br>instruction<br>encodings across<br>modules | Refined prompting<br>with explicit ISA<br>tables; enforced<br>consistency via<br>shared JSON<br>blueprint                                               |

| Parameter<br>propagation errors                    | Uncoordinated<br>parameter<br>definitions across<br>modules               | Centralized<br>parameter file and<br>enforced<br>inheritance through<br>JSON schema                                                                     |

| Incorrect handling<br>of SystemVerilog<br>packages | Agent omitted or<br>mismatched<br>imports in<br>integrated designs        | Prompted agent to<br>generate package<br>stubs first, then<br>ensured imports<br>during integration.<br>Later, used only<br>centeralized<br>parameters. |

| Misaligned memory interfaces                       | Agent-generated load/store modules had width mismatches                   | Human-in-the loop<br>debugging and<br>prompt<br>improvement                                                                                             |

| Clock related errors                               | Agent failed to<br>insert<br>synchronization<br>logic for signals         | Human-in-the-loop<br>correction                                                                                                                         |

# A. Strengths

- Syntactic Correctness and Boilerplate Generation: The agent excelled at generating syntactically correct SystemVerilog and Python. It handled the boilerplate of module definitions, port lists, and testbench structure well, saving significant manual effort.

- Blueprint Adherence: It correctly parsed the JSON blueprint to define module names, parameters, and port widths, demonstrating a strong grasp of structured input and the ability to follow a formal specification. In some cases, the blueprint (JSON) is more than 1300 lines of code.

- Modular Decomposition and Localized Reasoning: The initial design breakdown into standard, single-responsibility components was excellent engineering practice. Within the context of a single module, the agent demonstrated a strong ability to implement the required logic based on its description.

# B. Limitations: The Semantic Cohesion Gap

The core failures of the agent, across all tested designs, stemmed from a single, profound limitation: a lack of **holistic semantic cohesion**. While capable of reasoning about a task in isolation (e.g., "write an ALU"), the agent struggles to maintain a consistent, system-wide

understanding of how components must interact. This "semantic gap" is a known challenge in AI-driven code generation and is particularly acute in hardware design due to the tight, bit-level coupling between modules. This manifested in several critical ways, summarized in Table III.

TABLE III: Critical Errors Encountered in Final Phases

| Error Category                     | Description of Is-<br>sue                                                                                                | Resolution / Fix                                                                                                                 |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Missing Initialization File        | Instruction memory lacked a proper . hex file, leading to failed instruction fetch.                                      | Created and integrated a correctly formatted . hex file, then re-ran verification.                                               |

| Cascading Data<br>Width Mismatches | Fixing the missing hex file exposed hidden inconsistencies in data widths across modules.                                | Performed<br>systematic width<br>alignment across<br>modules, updated<br>bus connections,<br>and extended<br>testbench coverage. |

| Inconsistent ISA<br>Encoding       | ISA instruction en-<br>codings were in-<br>consistently imple-<br>mented across de-<br>coder and execu-<br>tion modules. | Standardized<br>instruction<br>encodings using<br>a single JSON<br>ISA specification,<br>regenerated RTL<br>and testbenches.     |

#### VI. ECONOMIC AND FUTURE IMPLICATIONS

# A. A Highly Cost-Effective Collaboration

A remarkable aspect of this project was its economic efficiency. The whole design, verification, and the debugging process for multiple complex processors was completed by utilizing reasoning models for planning and integration, and non-reasoning model for test code generation at component level, a simple processor can be completed in less than a million tokens. For context, this stands in stark contrast to the significant engineering man-hours and associated costs typically required for such tasks. In this framework, the AI agent plays the role of a junior engineer, automating more than 80% of the repetitive coding and first-pass verification. Meanwhile, the human architect remains central-providing highlevel guidance, validating decisions, and ensuring that the design intent is faithfully captured. The result is not only cost-effective but also aligned with democratizing access to sophisticated hardware design workflows.

#### B. The Path Forward: The Architect-in-the-Loop

This work strongly suggests that the most promising near-term trajectory for AI in hardware design is not complete autonomy, but a sophisticated *Architect-in-the-Loop* model. In this paradigm, the human engineer is not simply a reviewer of the AI's output but an active collaborator from the earliest stages of design.

Fig. 2: Refined Agentic Digital Design Flow with Human-in-the- Loop

Crucially, human oversight begins at the **specification level**: ambiguous or incomplete ISAs, architectural parameters, or high-level constraints must be clarified by the architect before the agent proceeds. This ensures that the agent operates with a complete and unambiguous blueprint. The human architect also provides strategic debugging insight, approves or rejects AI-generated fixes, and may directly modify RTL when necessary, with the agent handling re-verification.

Looking ahead, realizing this vision requires nextgeneration agents to evolve in three key directions:

- Demand Complete Specifications: Agents must be trained to detect missing or contradictory elements in high-level specifications and formally request clarification, rather than making assumptions that can cascade into architectural flaws.

- 2) Perform Cross-Module Semantic Analysis: Agents should employ lightweight static and semantic checks to ensure interface compatibility, parameter consistency, and adherence to design rules across the codebase before running expensive simulations.

- 3) **Integrate with Formal Methods**: Beyond simulation, agents should be capable of generating SystemVerilog Assertions (SVA) or formal properties to express inferred design intent, enabling exhaustive verification with formal tools.

Taken together, these directions position the human architect as the source of design intent, while empowering the AI agent to act as a capable, efficient, and verifiable collaborator. This balance preserves accountability, reduces cost barriers, and opens a path toward broader participation in advanced hardware design.

#### VII. CONCLUSION

The experiment of designing multiple complex processors using a blueprint-driven AI agent was a qualified success. It demonstrated the immense potential of this approach to dramatically accelerate hardware development by automating the most labor-intensive aspects of RTL and testbench generation. The agent proved capable of creating complex, synthesizable designs that successfully targetted FPGA hardware.

However, it also starkly highlighted the "semantic cohesion gap" that prevents current models from reliably composing complex systems without human oversight. The agent, while proficient at localized tasks, lacks the holistic, system-wide reasoning that is the hallmark of an experienced engineer.

The most valuable takeaway is the demonstrated viability and economic efficiency of the human-AI collaborative model. The AI acts as a tireless, fast, and exceptionally low-cost junior engineer, while the human provides the architectural wisdom and strategic debugging insight that is currently irreplaceable. The future of AI in digital design is not about replacing the architect, but about providing them with the most powerful copilot, turning weeks of work into days, and days into hours.

#### REFERENCES

- [1] H. Fu, H. G. Gerez, et al. (2024). Chip-Chat: A Large Language Model for Conversational Hardware Design. arXiv:2402.13324.

- [2] Z. Liu, H. G. Gerez, et al. (2023). AutoChip: A LLaMA-based Agent for Chip Design. arXiv:2311.09228.

- [3] B. Li, Y. G. Gerez, et al. (2024). Towards Automatic and Agile AI/ML Accelerator Design with End-to-End Synthesis. In Proceedings of the 2024 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays.

- [4] Z. Pei, et al., "BetterV: Controlled Verilog Generation with Discriminative Guidance," arXiv preprint arXiv:2402.03375, 2024.

- [5] S. Liu, et al., "RTLCoder: Outperforming GPT-3.5 in Design RTL Generation with Our Open-Source Dataset and Lightweight Solution," arXiv preprint arXiv:2312.08617, 2023.

- [6] M. Liu, N. Pinckney, B. Khailany, and H. Ren, "VerilogEval: Evaluating Large Language Models for Verilog Code Generation," arXiv preprint arXiv:2309.07544, 2023.

- [7] Cocotb Contributors, cocotb documentation, [Online]. Available: https://docs.cocotb.org/. (Accessed: Aug. 26, 2025).

- [8] W. Snyder, Verilator, [Online]. Available: https://github.com/verilator/verilator, 2023 (Accessed: August 26, 2025)

#### APPENDIX

#### COMPLETE SUPPORTING DATA

You will find the complete blueprint, hdl files, cocotb test, scripts to simulate the digital system at https://github.com/mmubarek/eda/tree/main/paper1. Sample code is provided in the next appendices.

#### APPENDIX: TOOLS AND DEBUGGING PROCESS

20

#### A. Tools

For simulation, we utilized cocotb together with 22 verilator. We developed both component-level and 23 top-level cocotb tests to ensure functionality and correctness across the design hierarchy.

# B. Debugging Process: Synthesis and Experimentation

One of the major issues encountered was the absence 30 of a hex file for the instruction memory. To resolve this, 31 we created the required hex file, integrated it into the 33 design, and retested the code.

When compiling for the FPGA, we also needed to <sup>35</sup> provide a dedicated top-level module that wired the <sup>36</sup> design components to the FPGA peripherals. This modi- <sup>38</sup> fication introduced cascading issues, primarily related to <sup>39</sup> mismatched data widths across modules, which required <sup>40</sup> significant debugging. After carefully resolving these <sup>42</sup> mismatches, both verification and synthesis completed <sup>43</sup> successfully.

The updated design was then iteratively tested using 46 cocotb: each modification was rerun, verified, and 47 debugged through simulation until stable results were 49 achieved.

# C. Processor Development Notes

Using our HDL generation tool, we created a 32-51 bit RISC-V processor. During early debugging stages, 52 we noticed recurring issues. Both the RISC-V and 53 LEGv8 implementations successfully passed cocotb 55 tests; however, neither included a preloaded hex file 56 in their instruction memory. Instead, cocotb injected 57 instructions directly at the top-level testbench.

To enable standalone execution, we manually added an  $_{60}$  instruction.hex file for the RISC-V design. With  $^{61}$  this addition, the RISC-V processor ran without errors,  $^{62}_{63}$  though the synthesis tool still reported minor warnings.  $^{64}$

#### BLUEPRINT

```

67

68

"projectName": "Legv8SingleCycleProcessor",

"parameters": {

70

"DATA_WIDTH": 8,

"ADDRESS_WIDTH": 8,

"INSTRUCTION WIDTH": 16,

"REG_ADDR_WIDTH": 3,

74

"OPCODE_WIDTH": 4,

75

"ALU_OP_WIDTH": 3,

"IMMEDIATE_WIDTH": 6,

10

"JUMP_ADDR_WIDTH": 12,

78

"PC_INCREMENT_VAL": 2

80

14

"components": [

81

15

82

"name": "ProgramCounter",

16

"file": "program_counter.sv",

17

"description": "Holds the address of the _{85}

current instruction and updates it based on _{86}\,

control signals.",

```

```

"dependencies": [],

"status": "Validating".

"interface": [

"name": "clk",

"direction": "input",

"width": 1

"name": "rst",

"direction": "input",

"width": 1

"name": "pc_next_addr",

"direction": "input",

"width": "ADDRESS_WIDTH"

"name": "pc_out",

"direction": "output",

"width": "ADDRESS_WIDTH"

]

},

"name": "Legv8SingleCycleProcessor",

"file": "legv8_single_cycle_processor.sv"

"description": "Top-level module for the

simple single-cycle Legv8 processor,

integrating all sub-components.",

"dependencies": [

"ProgramCounter",

"InstructionMemory",

"ControlUnit",

"RegisterFile",

"ALU",

"DataMemory",

"SignExtender",

"Mux2to1",

"Mux3to1",

"Adder"

"status": "Pending",

"interface": [

"name": "clk",

"direction": "input",

"width": 1

"name": "rst",

"direction": "input",

"width": 1

"name": "debug_pc_out",

"direction": "output",

"width": "ADDRESS_WIDTH"

"name": "debug_instruction_out",

"direction": "output",

"width": "INSTRUCTION_WIDTH"

"name": "debug_alu_result",

```

```

"direction": "output",

"width": "DATA_WIDTH"

88

89

90

"name": "debug_reg_write_data",

91

92

"direction": "output",

"width": "DATA_WIDTH"

93

94

95

1

96

}

97

]

98 }

```

Listing 1: Simple Legv8 Like Blueprint

14

16

17 18

19

27

30

31

43

44

49

51

53

54

# D. RegisterFile.sv

```

module RegisterFile (

input logic clk,

input logic rst,

input logic [2:0] read_addr1,

input logic [2:0] read_addr2,

input logic [2:0] write_addr,

22

input logic [7:0] write_data,

input logic write_en,

output logic [7:0] read_data1,

24

output logic [7:0] read_data2

25

11 );

26

localparam DATA_WIDTH = 8;

13

localparam REG_ADDR_WIDTH = 3;

14

28

localparam NUM_REGISTERS = (1 <<</pre>

15

29

REG_ADDR_WIDTH);

16

logic [DATA_WIDTH-1:0] registers [

NUM_REGISTERS-1:0];

// Synchronous write, preventing writes to R0 ^{\rm 34}

19

always_ff @(posedge clk or posedge rst) begin

20

if (rst) begin

21

for (int i = 0; i < NUM_REGISTERS; i++)</pre>

begin

registers[i] <= {DATA_WIDTH{1'b0}};</pre>

24

end

25

end else begin

// Only write if write_en is high AND the

26

destination is not RO

if (write_en && (write_addr != 0)) begin

28

registers[write_addr] <= write_data;</pre>

29

end

30

end

end

31

33

// Asynchronous read, forcing R0 to be 0

// If reading address 0, output 0, otherwise

output the register value.

assign read_data1 = (read_addr1 == 0) ? {

DATA_WIDTH{1'b0}} : registers[read_addr1];

assign read_data2 = (read_addr2 == 0) ? {

DATA_WIDTH{1'b0}} : registers[read_addr2];

37

38 endmodule

```

Listing 2: Corrected RegisterFile

#### E. test\_RegisterFile.sv

```

import cocotb

2 from cocotb.clock import Clock

55

3 from cocotb.triggers import RisingEdge,

FallingEdge, Timer, ClockCycles

```

```

4 import random

6 @cocotb.test()

7 async def register_file_test(dut):

"""Test the RegisterFile module thoroughly.

# Parameters derived from the HDL module

DATA_WIDTH = 8

REG\_ADDR\_WIDTH = 3

NUM_REGISTERS = 1 << REG_ADDR_WIDTH # 2^3 =</pre>

8 registers

# Create a clock instance and start it

clock = Clock(dut.clk, 10, units="ns") # 10

ns period = 100MHz clock

cocotb.start_soon(clock.start())

# Keep a shadow model of the register file

for verification

# Initialize all shadow registers to 0,

matching the reset behavior

shadow_registers = [0] * NUM_REGISTERS

cocotb.log.info("Starting RegisterFile test

# 1. Reset the DUT

cocotb.log.info("Applying reset and

verifying initial state.")

dut.rst.value = 1

dut.write en.value = 0

dut.write_addr.value = 0

dut.write_data.value = 0

dut.read_addr1.value = 0

dut.read_addr2.value = 0

await ClockCycles(dut.clk, 5) # Hold reset

for a few clock cycles

dut.rst.value = 0

await RisingEdge(dut.clk) # Wait for reset

to de-assert and first clock edge

# Verify all registers are 0 after reset

for i in range(NUM_REGISTERS):

dut.read_addr1.value = i

dut.read_addr2.value = i # Check both

read ports

await Timer(1, units="ns") # Allow

combinatorial logic to settle

assert dut.read_data1.value == 0, \

f"ERROR: Register {i} (read_data1)

not 0 after reset. Got {dut.read_data1.

value}"

assert dut.read data2.value == 0, \

f"ERROR: Register {i} (read_data2)

not 0 after reset. Got {dut.read_data2.

value}"

shadow_registers[i] = 0 # Ensure shadow

model is also reset to 0

cocotb.log.info("Initial state verified:

All registers are 0.")

# 2. Basic Write and Read Test

cocotb.log.info("Performing basic write and

read test.")

test addr = 1

test_data = 0xAA

```

```

dut.write_en.value = 1

.read_data1.value) } "

dut.write_addr.value = test_addr

dut.write_data.value = test_data

assert dut.read_data2.value == write_data2,

58

59

await RisingEdge (dut.clk) # Write occurs on 107

f"ERROR: Concurrent read data2 mismatch

60

. Expected {hex(write_data2)}, got {hex(dut

this rising edge

shadow_registers[test_addr] = test_data #

.read_data2.value)}"

cocotb.log.info(f"Concurrent writes to R{

Shadow model updated *after* the clock edge 108

62

write_addr1} ({hex(write_data1)}) and R{

# Read immediately after write (within the

write_addr2} ({hex(write_data2)}) and reads

63

same clock cycle)

verified.")

dut.read_addr1.value = test_addr

dut.read_addr2.value = test_addr

# 4. Overwriting a Register

110

65

await Timer(1, units="ns") # Allow

66

cocotb.log.info("Testing overwriting a

combinatorial read outputs to settle

register.")

assert dut.read_data1.value == test_data, \ 112

overwrite\_addr = 2

67

f"ERROR: Read data1 mismatch after

overwrite\_data = 0xCC

68

write. Expected {hex(test_data)}, got {hex(114

dut.write_en.value = 1

dut.read_data1.value) } "

115

dut.write_addr.value = overwrite_addr

assert dut.read_data2.value == test_data, \ 116

dut.write_data.value = overwrite_data

69

f"ERROR: Read data2 mismatch after

await RisingEdge(dut.clk)

70

write. Expected {hex(test_data)}, got {hex(118

shadow_registers[overwrite_addr] =

dut.read_data2.value) } "

overwrite_data

71

# Read from an unwritten address (should

dut.read_addr1.value = overwrite_addr

120

await Timer(1, units="ns")

still be 0)

121

unwritten_addr = (test_addr + 1) %

assert dut.read_data1.value ==

NUM REGISTERS

overwrite_data, \

7.4

dut.read_addr1.value = unwritten_addr

f"ERROR: Overwrite failed for R{

75

await Timer(1, units="ns")

overwrite_addr}. Expected {hex(

assert dut.read_data1.value ==

overwrite_data)}, got {hex(dut.read_data1.

76

shadow_registers[unwritten_addr], \

value) } "

f"ERROR: Read data from unwritten

cocotb.log.info(f"Overwrite of R{

124

register {unwritten_addr} mismatch.

overwrite_addr} with {hex(overwrite_data)}

Expected {hex(shadow_registers[

verified.")

unwritten_addr])}, got {hex(dut.read_data1.125

# 5. No Write when write_en is low

126

cocotb.log.info(f"Basic write to R{

cocotb.log.info("Testing no write when

write_en is low.")

test_addr} ({hex(test_data)}) and read

verified.")

128

no\_write\_addr = 3

# 3. Concurrent Writes and Reads (

no\_write\_data = 0xFF

79

129

different addresses)

original_value = shadow_registers[

cocotb.log.info("Testing concurrent writes

no_write_addr] # Should be 0 from reset

80

dut.write_en.value = 0 # Crucial: write_en

and reads.")

write_addr1 = 1

81

is low

write_data1 = 0x11

dut.write_addr.value = no_write_addr

82

132

dut.write_data.value = no_write_data

write_addr2 = 2

83

write_data2 = 0x22

await RisingEdge(dut.clk) # Clock edge, but

84

134

85

no write should occur

86

# Write to addr1

135

dut.write en.value = 1

dut.read_addr1.value = no_write_addr

87

136

await Timer(1, units="ns")

dut.write_addr.value = write_addr1

dut.write_data.value = write_data1

assert dut.read_data1.value ==

89

138

90

await RisingEdge(dut.clk)

original_value, \

f"ERROR: Write occurred when write_en

91

shadow_registers[write_addr1] = write_data1 139

was low for R{no_write_addr}. Expected {hex

92

93

# Write to addr2

(original_value) }, got {hex(dut.read_datal.

dut.write_en.value = 1

value) } "

94

assert dut.read_data1.value !=

95

dut.write_addr.value = write_addr2

96

dut.write_data.value = write_data2

no_write_data, \

await RisingEdge(dut.clk)

"ERROR: Data was written despite

97

shadow_registers[write_addr2] = write_data2

write_en being low!"

99

cocotb.log.info(f"No write to R{

# Read both concurrently using different

no_write_addr} when write_en is low

100

read ports

verified.")

dut.read_addr1.value = write_addr1

101

143

dut.read_addr2.value = write_addr2

# 6. Fill all registers and verify

102

144

await Timer(1, units="ns")

103

145

cocotb.log.info("Filling all registers and

assert dut.read_data1.value == write_data1,

verifying their contents.")

104

dut.write_en.value = 1

f"ERROR: Concurrent read data1 mismatch 147

for i in range(NUM_REGISTERS):

```

```

DATA_WIDTH) - 1)

dut.write_addr.value = i

149

dut.write_data.value = data_to_write

150

dut.write_en.value = 1 if i != 0 else 0

# Don't write to R0

await RisingEdge(dut.clk)

154

# Update shadow model only if not R0

155

if i != 0:

156

157

shadow_registers[i] = data_to_write

else:

158

159

shadow_registers[i] = 0 # R0

always stays 0

198

160

100

# Verify all registers by reading them back 200

161

for i in range(NUM_REGISTERS):

162

dut.read_addr1.value = i

163

dut.read_addr2.value = (i + 1) %

202

164

NUM_REGISTERS # Read another one

203

concurrently

await Timer(1, units="ns")

165

assert dut.read_data1.value ==

205

shadow_registers[i], \

f"ERROR: Verification failed for R{

167

i) (read_data1). Expected {hex(

shadow_registers[i])}, got {hex(dut.

208

read_data1.value) } "

assert dut.read_data2.value ==

168

shadow_registers[(i + 1) % NUM_REGISTERS], 210

f"ERROR: Verification failed for R 212

169

{(i + 1) % NUM_REGISTERS} (read_data2).

Expected {hex(shadow_registers[(i + 1) %

NUM_REGISTERS]) }, got {hex(dut.read_data2.

cocotb.log.debug(f"Verified R{i} ({hex(215

170

shadow_registers[i])}) and R{(i + 1) %

NUM_REGISTERS) ({hex(shadow_registers[(i + 217

1) % NUM_REGISTERS]) }) ")

cocotb.log.info("All registers filled and 218

verified successfully.")

# 7. Randomized Test

cocotb.log.info("Starting randomized test

174

(100 cycles).")

for cycle in range(100):

176

# 1. Determine write operation for the

*upcoming* clock edge

write_this_cycle = False

178

write_addr_val = 1

179

180

write_data_val = 0

181

if random.random() < 0.6: # 60% chance 222

182

to write

write_this_cycle = True

183

write_addr_val = random.randint(1, 223

184

NUM_REGISTERS - 1)

write_data_val = random.randint(1,

185

(1 << DATA_WIDTH) - 1)

dut.write_en.value = 1

186

dut.write_addr.value =

187

write_addr_val

dut.write_data.value =

188

write_data_val

cocotb.log.debug(f"Cycle {cycle}:

Setting inputs for write: addr={

write_addr_val}, data={hex(write_data_val)}

")

else:

```

```

dut.write_en.value = 0 # No write

this cycle

cocotb.log.debug(f"Cycle {cycle}:

No write this cycle.")

\# 2. Set read addresses for the *

current* cycle's verification.

\# These reads will reflect the state *

after* the upcoming clock edge.

read_addr1 = random.randint(0,

NUM_REGISTERS - 1)

read_addr2 = random.randint(0,

NUM_REGISTERS - 1)

dut.read_addr1.value = read_addr1

dut.read_addr2.value = read_addr2

# 3. Wait for the clock edge. This is

when the DUT's write (if enabled) happens.

await RisingEdge(dut.clk)

# 4. Update shadow model *after* the

clock edge if a write was enabled

if write_this_cycle:

shadow_registers[write_addr_val] =

write_data_val

# 5. Allow combinatorial logic for

reads to settle *after* the clock edge

await Timer(1, units="ns")

# 6. Now verify the reads

expected_data1 = shadow_registers[

read_addr1]

expected_data2 = shadow_registers[

read_addr2]

actual_data1 = dut.read_data1.value

actual data2 = dut.read data2.value

assert actual_data1 == expected_data1,

f"ERROR: Cycle {cycle}: Random

Read1 mismatch at addr {read_addr1}.

Expected {hex(expected_data1)}, got {hex(

actual_data1) } "

assert actual_data2 == expected_data2,

f"ERROR: Cycle {cycle}: Random

Read2 mismatch at addr {read_addr2}.

Expected {hex(expected_data2)}, got {hex(

actual data2) } "

cocotb.log.debug(f"Cycle {cycle}:

Random Read: addr1={read_addr1}, data1={hex

(actual_data1) } (expected {hex(

expected_data1) }) | "

f"addr2={read_addr2},

data2={hex(actual_data2)} (expected {hex(

expected_data2) }) ")

cocotb.log.info("Randomized test completed.

cocotb.log.info("RegisterFile test finished

successfully!")

```

Listing 3: Corrected test\_RegisterFile