# VeriPy - A New Python-Based Approach for SDR Pipelined/Unrolled Hardware Accelerator Generation

Yuqin Zhao, Linghui Ye, Haihang Xia, Luke Seed, Tiantai Deng Electronic and Electrical Engineering, the University of Sheffield, Mappin Building, Sheffield, UK, S1 3JD Corresponding author: Tiantai Deng (email: t.deng@sheffield.ac.uk). This work is supported by EPSRC Early Career Researcher Studentship

Abstract—Software-defined radio (SDR) plays an important role in the communication field by providing a flexible and custimized communication system for different purposes according to the needs. To enhance the performance of SDR applications, hardware accelerators have been widely deployed in recent years. In facing this obstacle, a necessity arises for a high-level synthesis (HLS) tool specifically designed for communication engineers without detailed hardware knowledge. To lower the barrier between SDR engineers and hardware development, this work proposed a Python-based HLS tool, VeriPy, which can generate both mainstream architecture for hardware accelerators in Verilog specifically for SDR designs including unrolled design and pipelined design, requiring no detailed digital hardware knowledge or Hardware Description Languages (HDL). Furthermore, VeriPy supports automatic testbench generation with random input stimulus, an extensible hardware library, performance and resource estimation, and offers strong optimisation potential at both the algorithmic and digital hardware levels.

The generated hardware design by VeriPy can achieve up to 70% faster operating frequency compared to pragma-optimised Vivado HLS designs with a reasonably higher resource consumption while delivering comparable performance and resource consumption to hand-coded implementations. Regarding code complexity, VeriPy requires no pragmas, completely eliminating the need for low-level hardware knowledge. For straightforward algorithms, the input code length remains comparable to that of Vivado HLS.

Index Terms—High-Level Synthesis, Software-Defined Radio, Design Tool, Design Automation, FPGA, Communication, Hardware Acceleration.

## I. INTRODUCTION

OFTWARE-DEFINED radio (SDR) is a communication platform where the signals are processed in the software approach based on a hardware platform with flexible configurations of frequency, bandwidth, etc [1]. Conventional SDR applications are operated on a General-Purpose Processor (GPP) like a central processing unit (CPU) [2], from which the SDR design can benefit from high reprogrammability and short redesign time [3]. It demonstrates lower performance-to-power efficiency compared to other platforms, such as Field Programmable Gate Arrays (FPGAs), when applied to an SDR application. This is primarily due to the delay incurred during the execution of software layers and the fetch decoding

This paper was produced by the IEEE Publication Technology Group. They are in Piscataway, NJ.

Manuscript received April 19, 2021; revised August 16, 2021.

execution process [4] [5]. Currently, software-defined radio (SDR) plays an important role in the state-of-the-art 4G and 5G communication systems [6], [7]. Thanks to its extraordinary flexibility, SDR is projected to have significant potential for development and implementation in future SDR applications experimentally and practically, reflecting the increasing interest in enhancing SDR performance to meet the heavier computational demands of 6G data processing by deploying it on alternative hardware platforms, such as FPGAs, instead of general-purpose processors (GPPs), achieving higher efficiency and lower level of flexibility [6]-[9]. For example, future SDR applications in 6G data processing are expected to be computationally intensive on general-purpose processors (GPPs); however, their performance can be significantly enhanced through hardware architectures such as systolic arrays implemented on FPGAs [10].

To improve the SDR performance-to-power efficiency, FPGA emerges as a more suitable alternative hardware platform to replace the current GPP platform, attributed to its remarkable performance-to-power efficiency [9] [11]. However, FPGA implementations usually requires extensible hardware knowledge and using the low-level Hardware Description Languages (HDLs), necessitating extensive knowledge and experience in digital hardware, which requires a different skill set from SDR engineers. While general-purpose tools like Vivado HLS have been suggested for SDR hardware development, they still demand considerable hardware expertise [12] as HLS only allows coding using a higher level syntax but does not truly bring the design level higher, achieving such optimisations typically requires additional settings and efforts, such as using directives or pragmas alongside the code. Alternatively, users may need to manually modify the HDL code, which often results in poor readability. Both approaches still present a substantial barrier to entry for individuals without extensive hardware knowledge. Alternatively, Vivado can also combine MATLAB Simulink, HDL Coder, lowering the entry barrier for SDR design at the system level design. However, similar to Vivado HLS, it still presents challenges in performing low-level hardware optimisations. Tools such as UHD (USRP Hardware Driver) using GNU Radio for the USRP, which are specifically designed for SDR communication applications. rely on vendors to update corresponding hardware libraries to support software applications and achieve higher-performance functionalities. This dependence imposes a risk for users, as the availability and updates of these customised libraries [13]. Developing an SDR application using HLS tools like Vivado HLS or Intel Quartus HLS Compiler offers the advantage of directly generating both Verilog and VHDL designs from C/C++ code, supported by comprehensive libraries [14], [15]. However, this approach also presents several challenges, including the limited generalisability of tool chain (e.g. the output hardware desgin of HLS can be implemented in any FPGA, however, but when it comes to IP in a certain tool chain, the usage of the IP will be limited within the tool chain itself), lack of readability of the generated HDL file, a steep learning curve, and the need for significant hardware expertise. Additionally, hardware-specific pragmas, such as Unrolled/Pipeline and AXI protocol settings (used in HLS C/C++ for coding simplification), introduce barriers for SDR engineers. The choice of different AXI protocols and optimisation pragmas/directives can significantly impact the performance, power, and area of the resulting hardware design. The choice between unrolled and pipelined implementations can lead to different hardware architectures, ultimately affecting performance in terms of timing and resource utilisation. Similarly, selecting different AXI protocols influences the data transfer speed and size in the hardware design. Besides, the optimisation in the vendor's tool, like Intel Quartus HLS and Vivado HLS, relies on the correct placement of directives such as pipeline and unroll pragmas, which increases code complexity and steepens the learning curve [16], [17]. Moreover, effective use of these pragmas requires users to possess a solid understanding of hardware design concepts [12]. Furthermore, the limited optimisation capabilities are exacerbated by the poor readability of the hardware designs generated by HLS tools, restricting users to optimisation at the HLS pragma/directive level and limiting flexibility for modifications at the HDL level.

GNU Radio, an SDR-specific hardware design tool, accepts Graphical, Python, and C/C++ as input [13]. It also benefits from compatibility with various platforms such as GPPs, GPUs, DSP chips, and FPGAs [12]. However, the functions supported in GNU Radio are provided by default, with no capability for hardware-level reprogrammability, which limits both the performance and design flexibility of SDR applications [18]. Additionally, the transfer speed in a GNU Radio hardware design is limited to USB 2.0 because of the out of date and non-customised library, which falls significantly below the state-of-the-art communication data rates. [19].

The existing approaches for SDR development on FPGAs typically present one of two limitations: either a steep learning curve and the need for extensive hardware knowledge, or a limited capacity to improve performance for future communication systems. To address these problems and enable SDR engineers to develop FPGA-based applications with a lower hardware entry barrier while achieving an improved trade-off among performance, power, and area (PPA), this paper introduces VeriPy—a novel Python-based, SDR-specific HDL generation tool designed for users without extensible hardware design experience.

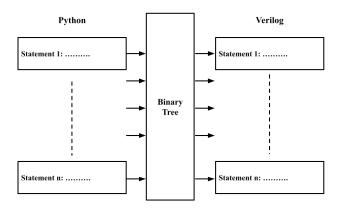

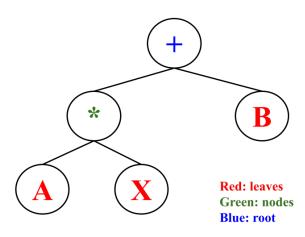

The proposed tool supports the generation of both unrolled and pipelined Verilog hardware to meet different performance, power, and area (PPA) requirements, based on a one-to-one function mapping concept. The Python-based software design is decomposed into smaller functions and transformed into a binary tree that captures data dependencies and timing information. This intermediate representation is then used to construct the corresponding hardware architecture. Additionally, the tool supports automatic testbench generation with random data for input stimulus, an extensible hardware library, performance and resource estimation, and offers strong optimisation potential at both the software and hardware levels.

To evaluate the effectiveness of VeriPy HLS tool, several benchmarking and commonly-used algorithms from SDR applications [21]–[23] were extracted and implemented using VeriPy, Vivado HLS 2024, and hand-coded Verilog approaches. Based on the results, VeriPy achieves a maximum operating frequency and throughput (they have the same data type) up to 1.7× compared to the pragma-optimised designs generated by Vivado HLS 2024, while delivering performance comparable to hand-coded Verilog implementations. For the trade off, the hardware generated by VeriPy consumes more resources than the HLS version but remains comparable to the hand-coded Verilog implementation.

The main contributions of this SDR hardware generation tool can be summarised below:

- VeriPy accepts Python as its input design language, which is the most widely used programming language, eliminating the need for extensible hardware knowledge for SDR engineers.

- The generated Verilog code includes clear, structured comments for each code block, significantly improving readability and facilitating further hardware-level optimisation.

- 3) VeriPy supports automatic testbench generation with random input stimulus, an extensible hardware library, and performance and resource estimation—all of which contribute to a faster and more user-friendly design process.

- 4) The generated hardware achieves up to 1.7× higher operating frequency and throughput in the unrolled FFT design compared to optimised Vivado HLS implementations and performs comparably to hand-coded Verilog, while consuming more resources than the HLS version as trade off but remaining similar to the hand-coded Verilog design.

# II. TOOL STRUCTURE AND ANALYSIS

In this section, the VeriPy tool is introduced and analysed from the highest level down to its implementation details. The discussion covers its overall structure and workflow, the data types and fundamental functions it provides, and the detailed internal processing mechanisms. By combining these perspectives, this section aims to provide a comprehensive and clear understanding of VeriPy's design and functionality.

# A. Overview of the VeriPy and Working Flow

The proposed VeriPy is a Python-based high-level synthesis (HLS) tool designed to automatically generate unrolled and pipelined hardware architectures for software-defined radio

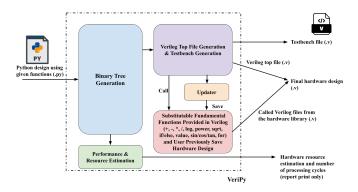

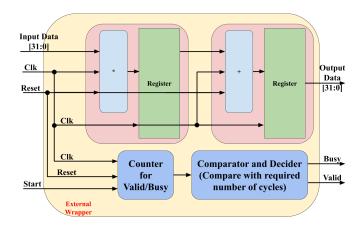

Fig. 1. Tool structure.

(SDR) applications without requiring extensive hardware design expertise. The generation environments for both unrolled and pipelined hardware share a common structural framework, as illustrated in Figure 1. VeriPy accepts Python-based SDR algorithm code as input, utilising a set of predefined fundamental functions. Based on this input, a binary tree array is constructed during the Binary Tree Generation block, which encapsulates all the essential information needed for hardware synthesis, including operands, operators, delay cycles, and address references. In the Verilog Top File and Testbench Generation block, the necessary information from the binary tree array is extracted to produce a top-level Verilog file that instantiates all required submodules, along with the corresponding testbench file. All data types in the generated files are set as 32-bit fixed-point format, comprising 16 bits for the integer part and 16 bits for the fractional part. The generated top-level Verilog file also includes comments that explain the functionality of each code block, enhancing readability and facilitating hardware-level optimisations. Simultaneously, the Performance & Resource Estimation block analyses the expected resource usage and processing cycles and generates a report (the performance report is generated for unrolled designs only). Additionally, users can choose to update the hardware library with newly synthesised modules for future reuse.

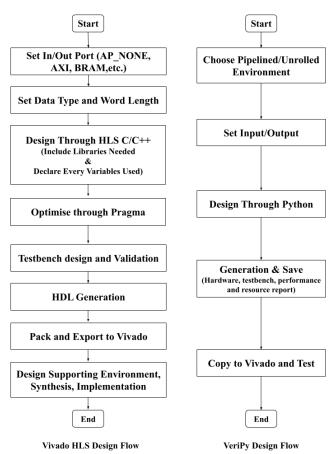

A comparison of the design flows of Vivado HLS and VeriPy is presented in Figure 2. Vivado HLS requires a more complex workflow, demanding greater adherence to design rules and a deeper understanding of hardware concepts. In contrast, VeriPy simplifies the process by allowing users to develop hardware designs using only the provided fundamental functions, along with straightforward input and output declarations.

To design an FPGA-based SDR accelerator using Vivado HLS, users must follow several critical steps. First, it is necessary to configure the input/output port types (e.g., AP\_NONE, AXI, BRAM) according to the specific design requirements, which demands a clear understanding of the differences between hardware communication protocols. Careful selection of data types, word lengths, and appropriate libraries is essential, as these choices directly affect the accuracy and performance of the final implementation. Since C/C++ is used as the input language, all variables must be explicitly declared to prevent

Fig. 2. The Design Flow Comparison between Vivado HLS and VeriPy.

compilation errors and warnings. In addition, optimisation pragmas must be inserted, which also requires familiarity with hardware design principles. A testbench must be developed to validate the design through C/RTL co-simulation in Vivado, and the verified hardware must then be packaged and exported. Finally, users may need to configure a port-protocol-specific environment within Vivado to complete the synthesis and implementation stages.

VeriPy, on the other hand, offers a significantly streamlined design flow, particularly when compared to Vivado HLS. Users begin by selecting either the pipelined or unrolled environment, depending on their specific requirements. During the Python algorithm development stage, users will define inputs and outputs and construct the desired algorithm exclusively with the provided function set. Once the design is complete, VeriPy automatically generates the corresponding hardware description and its testbench in Verilog, with all data defined using a 32-bit fixed-point data type (16 bits for the integer part and 16 bits for the fractional part), along with a detailed performance and resource utilisation report. Additionally, the generated hardware modules are automatically stored in the hardware library for future reuse. Finally, users can import both the hardware design and testbench into Vivado to perform functional validation, synthesis, and implementation.

Figure 3 illustrates a comparison of manually written input code for both approaches. VeriPy significantly reduces the

```

4

```

```

#include <ap_fixed.h>

#include <ap_int.h>

#include <cmath>

#include <cmath>

#include <cing>

#include <cing>

#include <ap_axi_sdata.h>

void MAC_5 (ap_fixed<32,16> results[5]) {

#pragma HLS INTERFACE s_axilite port=return bundle=CTRL

#pragma HLS INTERFACE bram port=results

ap_fixed<32,16> a[5] = {1, 2, 3, 4, 5};

ap_fixed<32,16> b[5] = {7, 8, 9, 10, 11};

for(int i = 0; i < 5; i++) {

results[i] = a[i] * b[i];

}

}</pre>

```

## **HLS Input Code**

```

input_define("c")

array_define_content("a", a)

array_define_content("b", b)

output_define("array_x_wire_4")

output_define("array_x_wire_2")

output_define("array_x_wire_1")

output_define("array_x_wire_1")

output_define("array_x_wire_0")

for i in range(0, 5):

wire_a = "array_a_wire_" + str(i)

wire_b = "array_b_wire_" + str(i)

wire_x = "array_x_wire_" + str(i)

```

## VeriPy Input Code

Fig. 3. Comparison of the Input Code between HLS and VeriPy.

complexity associated with variable declarations and library inclusions required by Vivado HLS, thereby eliminating potential confusion for SDR engineers and streamlining the design process.

Compared with Vivado HLS, the design stages in VeriPy are significantly simplified and streamlined. Variable declarations and explicit data type specifications are not required, and hardware-specific pragmas for optimisation are unnecessary, as VeriPy directly provides dedicated Python-based unrolled and pipelined generation environments. Additionally, a corresponding testbench is automatically generated, further reducing the time required for testbench development. In summary, VeriPy offers clear advantages in terms of shorter design time, ease of use, minimal hardware expertise requirements, and reduced coding effort.

# B. Datatypes and Fundamental Functions

As mentioned previously, to lower the barrier for users with limited hardware expertise, VeriPy does not require explicit data type declarations, as all data is by default defined as 32-bit fixed-point numbers, with 16 bits for the integer part and 16 bits for the fractional part in the generated hardware. Since SDR systems typically receive input from an ADC with a resolution of 4 to 14 bits [24], the 32-bit fixed-point representation adopted in this work is expected to be sufficient. This

TABLE I

FUNDAMENTAL FUNCTIONS AND THEIR EXPRESSION

| Functions                        | Expression                            |

|----------------------------------|---------------------------------------|

| Addition_V(c,a,b)                | c = a + b                             |

| Subtraction_V(c,a,b)             | c = a - b                             |

| Multiplication_V(c,a,b)          | c = a * b                             |

| Division_V(c,a,b)                | c = a / b                             |

| Power_V(c,a,d)                   | $c = a^d$                             |

| Logarithm_V(c,a,b)               | c = log(a)b                           |

| Sqrt_V(c, a)                     | c = sqrt(a)                           |

| SinCosTan_V(sin_r, cos_r, tan_r, | $\sin_r = \sin(a), \cos_r = \cos(a),$ |

| a)                               | $tan_r = tan(a)$                      |

| Value_V(c, a)                    | c = a                                 |

| If_V(comp1, comp2, condition) *  | if(comp1 (condition) comp2)           |

| If_V(comp1, comp2, condition,    | if( comp1 (condition) comp2 )         |

| input_array, output_array) **    |                                       |

| # TC/ 1 ' 11 1 '                 | TC/ 1 ' 1' 1 ' 1                      |

<sup>\*</sup> If/else in unrolled environment \*\* If/else in pipelined environment. input\_array and output\_array are for input/output declaration in the if/else block, they are not used in the calculation.

TABLE II

INPUT AND OUTPUT PRECISION OF PROVIDED FUNDAMENTAL

FUNCTIONS.

| F .:                    | T . D           | D                |

|-------------------------|-----------------|------------------|

| Functions               | Input Precision | Output Precision |

| Addition_V(c,a,b)       | fixed(32,16)    | fixed(32,16)     |

| Subtraction_V(c,a,b)    | fixed(32,16)    | fixed(32,16)     |

| Multiplication_V(c,a,b) | fixed(32,16)    | fixed(32,16)     |

| Division_V(c,a,b)       | fixed(32,16)    | fixed(32,16)     |

| Power_V(c,a,d)          | fixed(32,16)    | fixed(32,16)     |

|                         | int(8)*         |                  |

| Logarithm_V(c,a,b)      | fixed(32,16)    | fixed(32,16)     |

| Sqrt_V(c, a)            | fixed(32,16)    | fixed(32,16)     |

| SinCosTan_V(sin_r,      | fixed(32,16)    | fixed(32,16)     |

| cos_r, tan_r, a)        |                 |                  |

| Value_V(c, a)           | fixed(32,16)    | fixed(32,16)     |

| If_V(comp1, comp2,      | fixed(32,16)    | bool(1)***       |

| condition)**            |                 |                  |

| If_V(comp1, comp2,      | fixed(32,16)    | bool(1)          |

| condition, input_array, |                 |                  |

| output_array)****       |                 |                  |

<sup>\*</sup> Only support power(a,b) when b is an integer from -128 to 127.

\*\* Unrolled if/else. \*\*\* If/else only gives true/false as output. \*\*\*\*

Pipelined if/else.

is implemented through the provided fundamental functions, as all corresponding hardware modules for these functions are designed using the 32-bit fixed-point format.

Table I, Table II, and Table III present the provided fundamental functions, their input/output precision, and their internal calculation precision, respectively. The available fundamental functions include addition, subtraction, multiplication, division, exponentiation, logarithm, square root, sine, cosine,

TABLE III

FUNDAMENTAL FUNCTIONS INTERNAL PRECISION

| Functions                           | Internal Precision |

|-------------------------------------|--------------------|

| Addition_V(c,a,b)                   | fixed(32,16)       |

| Subtraction_V(c,a,b)                | fixed(32,16)       |

| Multiplication_V(c,a,b)             | fixed(64,32)       |

| Division_V(c,a,b)                   | fixed(64,32)       |

| Power_V(c,a,d)                      | fixed(64,32)       |

| Logarithm_V(c,a,b)                  | fixed(128,64)      |

| Sqrt_V(c, a)                        | fixed(16,8)        |

| SinCosTan_V(sin_r, cos_r, tan_r, a) | fixed(32,29)       |

| Value_V(c, a)                       | fixed(32,16)       |

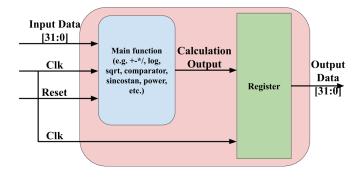

Fig. 4. Hardware Architecture of the Provided Fundamental Functions.

tangent, value assignment, and conditional branching (if/else). Loop structures can be implemented directly using Python's native for loop syntax. All provided functions support 32-bit fixed-point input and output precision, except for the power function and the if/else block. Currently, the power function supports only an exponent specified as a signed 8-bit integer, since fractional exponents can cause excessive power and resource consumption, and large exponents can easily lead to overflow. For the if/else block, the output is limited to a boolean value, as it performs comparison operations only. Regarding internal precision, addition, subtraction, and value assignment use fixed(32,16), while power, multiplication, division, logarithm, and trigonometric functions (sine, cosine, tangent) use a higher-precision data type to improve numerical accuracy. The square root function, on the other hand, employs an internal precision of fixed(16,8) due to its specific mathematical calculation method. The set of fundamental functions is sufficient for typical SDR algorithm design, and the hardware library will continue to expand as users and developers contribute additional modules over time. This ensures that future designs become increasingly straightforward and convenient, with a wider range of functions available, thanks to VeriPy's built-in updater and extensible hardware library.

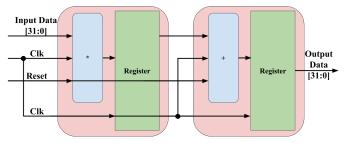

All provided functions share a similar hardware architecture, with signals including input, clock (clk), and reset, and each ending with a register to store the result for the next computation stage, as illustrated in Figure 4. Within this architecture, all fundamental functions are synchronised by the clock signal and support reset functionality. Since both the unrolled and pipelined hardware designs generated by VeriPy are composed of these fundamental functions, the resulting architecture is naturally divided into stages, with registers placed between each function to store intermediate results, as shown in Figure 5. The pipelined design, in contrast, is wrapped with control signals such as start, busy, and valid, enabling control flow management through a counter and comparator based on the defined number of processing cycles, as illustrated in Figure 6.

It is important to note that the default fundamental functions provided by VeriPy can be directly substituted to meet different design considerations, such as performance or power optimisation. This flexibility enables a potential optimisation approach within VeriPy, as the generated top-level file serves

Fig. 5. Generated Unrolled Hardware Architecture Composed of Provided Fundamental Functions.

Fig. 6. Generated Pipelined Hardware Architecture Composed of Provided Fundamental Functions.

as a framework that instantiates all required submodules. To replace a fundamental function, users simply need to maintain the same module name and port definitions in their custom implementation. Further details on this substitution mechanism will be presented in the next section.

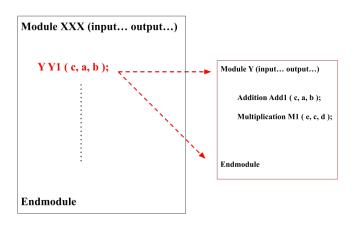

# C. Updater and Hardware Library

The updater function saves the number and order of inputs and outputs for each hardware design, along with the required processing cycles and resource usage, into the hardware library, assigning a unique label to each design. Simultaneously, three Python files corresponding to the If, Else, and Normal statements are automatically generated. When the function is invoked in the user's Python design, the algorithm first searches the hardware library using the label, ensuring that variable names follow the same order as the declared inputs and outputs. This information is then stored in a binary tree, which is subsequently used during the generation of the Verilog hardware design. The generation process follows the detailed procedure described in the next section. The output maintains a nested structure, where the top-level Verilog file generated by VeriPy directly calls the submodules containing the corresponding hardware designs, as illustrated in Figure 7.

Through the Updater and Hardware Library, users can design and reuse hardware modules without the need for redesign. This not only saves redevelopment time but also gradually enriches the library, making it more comprehensive and versatile.

Fig. 7. Nested Structure of the Output Hardware Design.

Fig. 8. One-to-one correspondence concept.

## III. PROCESS OF GENERATION

As illustrated in Figure 8, the core principle of VeriPy is built upon a one-to-one correspondence between software functions and their hardware counterparts. The functions available in Python are exactly matched to equivalent modules in the hardware library, ensuring a direct mapping. The Python input for VeriPy is composed using these provided functions, each of which is extracted along with its data dependencies and stored in a binary tree structure. Subsequently, the generated Verilog hardware invokes the same corresponding modules from the hardware library and establishes the appropriate wire connections to ensure correct functionality.

The entire code generation process in VeriPy consists of two main stages: Binary Tree Generation and Hardware Generation. While both the unrolled and pipelined environments share the same Hardware Generation stage, they differ in the Binary Tree Generation stage. This is because pipelined hardware requires more intricate dataflow control and precise ordering of operations, making its binary tree structure more complex than that of the unrolled design. To accommodate these additional requirements, the Binary Tree Generation process is further divided into two phases: Initial Binary Tree Generation, which produces a tree structure sufficient for unrolled hardware,

Fig. 9. Binary tree for a simple equation.

and Binary Tree Processing, which augments the tree with the additional information necessary for pipelined hardware generation.

### A. Binary Tree Generation

The binary tree concept is employed in VeriPy to provide a clear representation of calculation order and data dependencies. As illustrated in Figure 9, the binary tree for a simple equation Y=A\*X+B demonstrates the roles of leaves, nodes, and the root: leaves represent operands, nodes denote operators, and the root corresponds to the final operation of the expression. The original equation can be reconstructed by traversing the binary tree from the leaves to the root. In practice, the binary tree serves as an intermediate representation (IR) between the input and output languages. The design specified in the input language is first transformed into a binary tree, which is then traversed and interpreted in reverse to generate the corresponding hardware design in the output language.

# 1) Initial Binary Tree Generation:

# 1) Binary Tree Structure in Python

Owing to its structure and functionality, the binary tree also serves as a crucial intermediate representation (IR) of the input Python-based SDR application in VeriPy. The binary tree is internally constructed using an object-oriented programming approach (not exposed to the user). This internal structure consists of eight object fields that store the following information: operand names, number of operands, operator type, result names, number of results, previous addresses, number of previous addresses, and delay cycles.

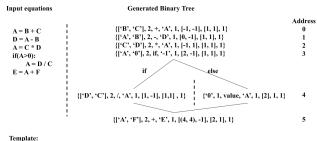

# 2) Binary Tree Generation Example

One of the examples is shown in Figure 10, which contains some fundamental functions and if/else. Information at addresses 2, 4, and 5 in the binary tree will be explained.

For address 2, according to the equation A=C\*D, ['C',

(operands names, the number of operands, operator, results names, the number or results, previous addresses, the number of previous addresses, delay cycle)

Fig. 10. Binary tree structure and a binary tree generation example.

Fig. 11. Unrolled and Pipelined Binary Tree (# represents delay).

'D'] indicates the operands, 2 indicates there are 2 operands, 'A', and '1' mean the only result name 'A'. Besides, [-1,1] specifies there is no previous address for 'C', and 'D' has a previous address at address 1 while [1,1] represents both 'C' and 'D' have only 1 previous address. The final 1 indicates this multiplication will have a 1-cycle delay for calculation.

Turning to address 4, the equation of A=0 is added to the else part to simplify the search previous address process. It also eliminates the complexity of the binary tree.

Address 5, however, stores a [(4,4),-1] in the object of "previous addresses" as A shows up both in the if and else statement, which also gives a [2,1] in the object of "the number of previous addresses".

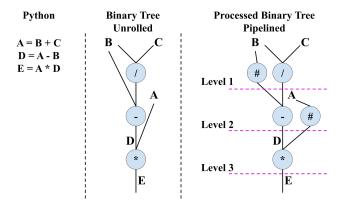

2) Processed Binary Tree Generation: As shown in Figure 11, the initially generated binary tree in VeriPy contains only data dependency and operator/operand/result information, which is sufficient for unrolled hardware generation. However, additional processing is required to adapt the binary tree for pipelined hardware generation, as pipelining demands precise control of dataflow and execution order across processing stages. This adaptation involves inserting delay modules between stages to align data correctly and ensure proper timing for data propagation.

Based on the initial binary tree, the complete processing sequence can be extracted and organised into hierarchical levels, representing the operations to be performed at each pipeline stage. To enable pipelined hardware generation, delay modules

Fig. 12. Different rules in Python and Verilog.

are inserted between result outputs and their corresponding input ports whenever a level gap exists between dependent operations.

As illustrated in Figure 11, the initial binary tree (centre) displays data dependencies, connections, and required modules—information sufficient only for unrolled hardware generation. To adapt this for pipelined hardware, the dataflow must be explicitly structured and stage boundaries clearly defined. In the example, operations are divided into three levels based on their calculation order. For instance, variable B is required in both Level 1 and Level 2, while variable A, computed as the result of B + C at the end of Level 1, is also needed as input to a multiplication operation in Level 3. Consequently, delay modules are inserted: one between B and the subtraction input in Level 2, and another between the result A from Level 1 and the multiplication input in Level 3. These inserted delays ensure correct data alignment and synchronisation across pipeline stages.

# B. Verilog Hardware Generation

The unrolled or pipelined Verilog hardware design is generated by VeriPy based on the initial or processed binary tree, respectively. The binary tree structure stores essential information such as input names, output names, number of inputs and outputs, previous addresses, number of previous addresses, and the number of processing cycles. For the processed binary tree used in pipelined hardware generation, additional delay modules are inserted where necessary; however, no new types of information are introduced—only timing alignment is modified.

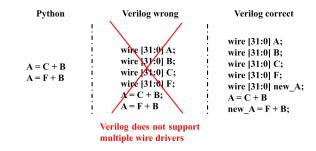

As is well known, hardware description languages (HDLs) like Verilog differ fundamentally from high-level programming languages such as Python. Verilog explicitly describes hardware structures, including the creation of wires and registers for data transmission and storage, whereas in Python, variable declarations merely allocate memory without hardware semantics. For example, as shown in Figure 12, a variable reassignment in Python is interpreted as a new memory allocation, but in Verilog, it could result in multiple drivers assigned to the same wire, leading to synthesis warnings or functional errors. To address this, VeriPy ensures that a new wire is defined for each reassigned signal, thereby avoiding multi-driver conflicts in the generated hardware.

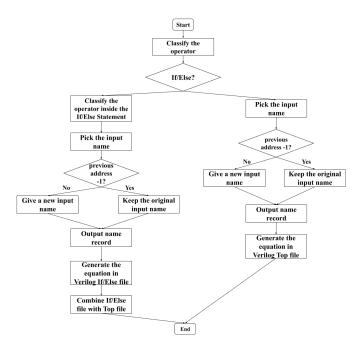

Fig. 13. Flow chart of Verilog generation through binary tree.

To generate a synthesisable Verilog hardware design, the process of binary tree analysis and code generation must be executed with care. The workflow for Verilog generation is illustrated in Figure 13.

This process will occur sequentially based on the binary tree generated from the Python design. Since If/else statements will increase the number of branches of the binary tree, the equation in the If/else statement will be processed separately from the ordinary equations. Ordinary equations will be generated directly into the Verilog Top file while equations in the If/else statement will be generated into an If/Else Verilog file. When processing each element, the operator will initially be classified to determine whether it represents an If/Else or a non-If/Else statement. If the current element is a non-If/Else statement, the input name will be selected, and its iteration in the previous occurrences will be checked. A new input name will be assigned if the same name has been used before, while the name will remain unchanged if it hasn't. This process helps avoid errors and warnings in the Verilog design, as mentioned in Figure 12. The output name will also be recorded for future processes, and the equation with new/original input names (depending on iteration) will be written in the Verilog Top file. If the current element is an If/Else statement, the process will traverse the If/Else binary tree, following the same operations as in the non-If/Else scenario. However, the final equation will be generated in the If/Else file in Verilog. Ultimately, the If/Else file will be combined with the Verilog file to complete the synthesis process.

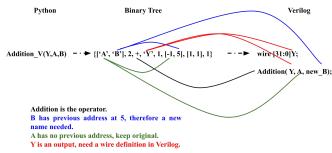

An example is illustrated in Figure 14. A newly declared variable Y is computed as the sum of A and B. Upon transformation into a binary tree, it is revealed that A does not have a previous address, whereas B has a previous address at 5. Consequently, A can retain its original name, while B must be assigned a new name to prevent the occurrence of the multi-

Fig. 14. Example of the process from Python to Verilog design.

driver problem in Verilog. After declaring the new output Y and rewriting the Verilog equation with A and new\_B, the final Verilog design is shown on the right side of Figure 14.

# IV. FUNCTIONS AND RULES OF VERIPY

## A. Functions and Advantages of VeriPy

The key functions and advantages of VeriPy over Vivado HLS are summarised below:

# 1) Python Input Without Pragmas or Data Type Declarations

As illustrated in Figure 3, VeriPy eliminates the need to declare variables, specify data types, define ports, or insert pragmas for optimisation—unlike Vivado HLS. This significantly reduces the learning curve and lowers the barrier between SDR software engineers and hardware design.

# 2) Unrolled and Pipelined Hardware Generation

VeriPy provides two independent environments for unrolled and pipelined hardware generation, catering to different performance, power, and area (PPA) requirements. Unlike Vivado HLS, which relies on pragma directives, VeriPy separates the two modes explicitly to minimise design confusion.

# 3) Enhanced Readability

In the generated hardware file, each block of Verilog code is followed by comments explaining its functionality, significantly improving readability—especially in comparison with the Vivado HLS-generated Verilog, as shown in Figures 15 and 16.

# 4) Support for Both High-Level and Low-Level Optimization

VeriPy supports optimisation at both the high-level (Python code) and low-level (Verilog structure). The advanced readability of the generated hardware—enhanced by informative comments and a clear structural hierarchy in the top-level Verilog file—enables users to substitute individual fundamental functions or adjust the hardware structure manually with ease.

# 5) Automatic Testbench Generation

VeriPy automatically generates a corresponding testbench for each hardware design. This reduces the manual effort required for testbench development and allows users to directly import both the design and testbench into hardware design tools for simulation and validation.

```

wire [31:0]temp;

//Proceed with temp = array_a_wire_0 * array_b_wire_0

wire start_mul_HDL_0;

wire valid_mul_HDL_0;

wire busy_mul_HDL_0;

mul_always mul_HDL_0 (array_a_wire_0, array_b_wire_0, temp,

assign start_mul_HDL_0 = start;

wire [31:0]array_x_wire_0;

//Proceed with array_x_wire_0 = temp + 0

wire start_addition_HDL_0;

wire valid_addition_HDL_0;

wire busy_addition_HDL_0;

addition_always addition_HDL_0 (temp, 0, array_x_wire_0, cl

assign start_addition_HDL_0 = start;

```

Fig. 15. VeriPy Generated Verilog File.

```

always @ (*) begin

if ((icmp_ln22_fu_108_p2 == 1'dl)) begin

ap_condition_pp0_exit_iter0_state2 = 1'b1;

end else begin

ap_condition_pp0_exit_iter0_state2 = 1'b0;

end

end

always @ (*) begin

if ((1'b1 == ap_CS_fsm_state6)) begin

ap_done = 1'b1;

end else begin

ap_done = 1'b0;

end

end

always @ (*) begin

if (((ap_start == 1'b0) & (1'b1 == ap_CS_fsm_state1))) begin

ap_idle = 1'b1;

end else begin

ap_idle = 1'b0;

end

end

```

Fig. 16. Vivado HLS Generated Verilog File.

#### 6) Performance and Resource Estimation

VeriPy provides resource utilisation estimates—including LUTs, flip-flops (FFs), DSPs, and BRAMs—for both unrolled and pipelined designs. Additionally, it offers performance estimation (in terms of required processing cycles) for pipelined designs.

#### 7) Extensible Hardware Library

VeriPy supports an extensible hardware library where users can store custom hardware modules for future reuse. This promotes design reuse and reduces both development time and input code length.

#### B. Rules

To generate synthesizable Verilog output, the VeriPy tool requires users to follow several specific rules, as outlined below (for details rules: https://github.com/RainChinChao/PythonToVerilogTool):

# 1) In/Out Define

To ensure the hardware design is synthesizable, input and output names must be defined using the input\_define() and output\_define() functions. Currently, the number of input and output names is limited to a maximum of 20 each.

#### 2) Number to Fixed Type

Since this tool supports a default 32-bit data type (16-bit

integer, 16-bit fraction) for inputs and outputs, any pure number must be converted to a 32-bit fixed-point format using number\_to\_hex().

# 3) Function Output Names and Accumulation

In this tool, input and output names must be unique within a single function. For accumulation designs, use a new name for each accumulation step. (Examples are available in the instructions on GitHub.)

#### 4) Nested If/Else

Currently, nested if/else structures can be implemented up to 2 levels. For designs requiring additional levels of nesting, please use the updater instead.

# 5) Array

In this tool, arrays can be declared but will follow a specific naming convention. For instance, if an array A is declared, each element in A will be named array\_A\_wire\_i, where i represents the index of the element.

Detailed rules, examples, function instructions, and example videos can be found on the following GitHub Repo (https://github.com/RainChinChao/PythonToVerilogTool).

#### V. CASE STUDY AND EVALUATION

In this section, 5 major SDR examples are chosen for hardware developments of VeriPy, Vivado HLS 2024.1, and handcoded Verilog based on the FPGA platform of RFSoC. Both tools have an intentionally unoptimised SDR algorithm as input to emulate the unfamiliarity between SDR engineers and hardware development. The comparisons are made under the scopes of **performance & area, readability & substitutability**, and **length of code (LoC)**. In Vivado HLS, all the inputs and outputs are in 32-bit fixed format and are assigned as AP\_NONE. The output Verilog Top file of VeriPy will be tested and simulated in Vivado 2024.1 to obtain performance and resource consumption data.

In addition to the five major SDR examples, several other simple designs have been developed and tested using different versions of Vivado HLS and various FPGA boards. All Python source files of VeriPy, generated Verilog top-level designs, comparison tables, and tool usage instructions have been uploaded to GitHub for public access. (https://github.com/RainChinChao/PythonToVerilogTool).

$$MAC16(A,B) = \sum_{i=0}^{15} A(i) * B(i)$$

(1)

$$T = -\frac{2 * pi * k * i}{n} \tag{2}$$

$$FFT32\_real(k) = \sum_{i=0}^{31} Xreal(i)*cos(T) - Ximag(i)*sin(T) \tag{3}$$

$$FFT32\_imag(k) = \sum_{i=0}^{31} Xreal(i)*sin(T) + Ximag(i)*cos(T)$$

(4)

# Algorithm 1 BPSK\_Demodulation

```

\begin{split} \mathbf{BPSK\_DEMODULATION}(\mathbf{input\_sig}[\mathbf{10}]) \\ \mathbf{for} \quad i = 1, ..., 10 \\ \quad t[i] \leftarrow i/Sample\_rate \\ \quad carrier[i] \leftarrow cos(2*pi*carrier\_freq*t[i]) \\ \quad temp \leftarrow temp + carrier[i]*input\_sig[i] \\ \mathbf{if} \quad (\mathbf{temp} >= 0) \\ \quad output \leftarrow 1 \\ \mathbf{else} \\ \quad output \leftarrow 0 \end{split}

```

# **Algorithm 2** BPSK\_Modulation

```

\begin{aligned} & \textbf{BPSK\_MODULATION}(\textbf{input\_bit}) \\ & \textbf{for} \quad i = 1, ..., 10 \\ & \quad t[i] \leftarrow i/Sample\_rate \\ & \quad carrier[i] \leftarrow cos(2*pi*carrier\_freq*t[i]) \\ & \quad carrier\_m[i] \leftarrow -cos(2*pi*carrier\_freq*t[i]) \\ & \textbf{if} \quad (\textbf{input\_bit} == 1) \\ & \quad bpsk\_s[i] \leftarrow carrier[i] \\ & \textbf{else} \\ & \quad bpsk\_s[i] \leftarrow carrier\_m[i] \end{aligned}

```

# Algorithm 3 Back\_Propagation

```

\begin{aligned} & \textbf{BACK\_PROPAGATION}(\mathbf{X[8], Y[4]}) \\ & \textbf{for} \quad i = 1, ..., 4 \\ & net\_input[i] \leftarrow \mathbf{X[2*i]*weight[1]} + \mathbf{X[2*i+1]*} \\ & weight[2] \\ & output[i] \quad \leftarrow \quad 1/2 \, + \, net\_input[i]/2( \quad \textbf{originally} \\ & 1/(1 + exp(net\_input[i])) \\ & error[i] \leftarrow \mathbf{Y[i]} - output[i] \\ & sig\_deri\_out[i] \leftarrow (1 - output[i]) * output[i] \\ & delta[i] \leftarrow error[i] * sig\_deri\_out[i] \end{aligned}

```

The five tested examples are illustrated in Equations 1, 3, 4 (Equation 2 is part of Equation 3), and Algorithms 1, 2, and 3. Equation 1 represents a multiply-accumulate (MAC) operation, which is commonly extracted from SDR designs such as Automatic Modulation Classification (AMC), as well as CNN-based AMC implementations [21]–[23]. Equations 3 and 4 describe components of a 32-point Fast Fourier Transform (FFT), a fundamental operation widely used in SDR applications. Algorithms 1 and 2 demonstrate the Binary Phase-Shift Keying (BPSK) modulation and demodulation algorithms, both of which have been designed and implemented using VeriPy and Vivado HLS. Algorithm 3 presents the backpropagation function, which is commonly used in convolutional neural networks (CNNs), a technique increasingly applied in modern SDR systems.

# A. Perforamance and Resource Consumption

Table IV, Table V, and Table VI present the maximum operating frequency and resource utilisation of selected designs generated by VeriPy, Vivado HLS 2024, and hand-coded Verilog, respectively. Both the VeriPy-generated and

TABLE IV

ALGORITHM PERFORMANCE AND RESOURCE RESULTS FROM VERIPY

RUN BY VIVADO 2024.1.

| VeriPy             | Max Freq | LUT   | FF   | DSP | BRAM |

|--------------------|----------|-------|------|-----|------|

|                    | (MHz)    |       |      |     |      |

| MAC 16 P           | 181      | 5079  | 2930 | 64  | 0    |

| MAC 16 U           | 895      | 4320  | 1024 | 64  | 0    |

| FFT 32 imag P      | 182      | 21388 | 9635 | 240 | 0    |

| FFT 32 real P      | 182      | 19539 | 9699 | 240 | 0    |

| FFT 32 U           | 180      | 32620 | 7796 | 464 | 0    |

| Demodulation P     | 119      | 3013  | 1453 | 40  | 0    |

| Demodulation U     | 181      | 2631  | 962  | 40  | 0    |

| Modulation P       | 211      | 108   | 51   | 0   | 0    |

| Modulation U       | inf      | 9     | 1    | 0   | 0    |

| Back Propagation P | 108      | 1389  | 516  | 16  | 0    |

| Back Propagation   | 132      | 4639  | 1018 | 64  | 0    |

| U                  |          |       |      |     |      |

TABLE V ALGORITHM PERFORMANCE AND RESOURCE RESULTS FROM VIVADO HLS 2024.1.

| HLS                   | Max Freq<br>(MHz) | LUT  | FF  | DSP | BRAM |

|-----------------------|-------------------|------|-----|-----|------|

| MAC 16                | 776               | 108  | 77  | 4   | 0    |

| MAC 16 U              | 776               | 108  | 77  | 4   | 0    |

| MAC 16 P              | 362               | 198  | 234 | 8   | 0    |

| FFT 32                | 259               | 122  | 142 | 8   | 0    |

| FFT 32 U              | 259               | 122  | 142 | 8   | 0    |

| FFT 32 P              | 109               | 9720 | 977 | 12  | 0    |

| Demodulation          | 195               | 705  | 279 | 15  | 0    |

| Demodulation U        | 205               | 184  | 139 | 4   | 0    |

| Demodulation P        | 504               | 201  | 166 | 0   | 0    |

| Modulation            | 178               | 677  | 323 | 7   | 0    |

| Modulation U          | 307               | 249  | 194 | 0   | 0    |

| Modulation P          | 1818              | 16   | 6   | 0   | 0    |

| Back Propagation      | 149               | 647  | 604 | 8   | 0    |

| Back Propagation<br>U | 149               | 647  | 604 | 8   | 0    |

| Back Propagation P    | 174               | 498  | 155 | 8   | 0    |

hand-coded designs were synthesised and implemented using Vivado 2024.1 to ensure a consistent evaluation environment. P means pipelined design while U means unrolled design.

As shown in Table IV, Table V, and Table VI, VeriPy demonstrates superior performance in terms of maximum operating frequency compared to Vivado HLS 2024.1 for the unrolled designs of MAC16, FFT32, and modulation, achieving up to 1.7× higher frequency. When compared with

TABLE VI

ALGORITHM PERFORMANCE AND RESOURCE RESULTS FROM

HAND-CODED VERIOG RUN BY VIVADO 2024.1.

| Verilog            | Max Freq | LUT   | FF   | DSP | BRAM |

|--------------------|----------|-------|------|-----|------|

|                    | (MHz)    |       |      |     |      |

| MAC 16 P           | 119      | 4848  | 2413 | 64  | 0    |

| MAC 16 U           | 895      | 4320  | 1024 | 64  | 0    |

| FFT 32 P           | 181      | 15379 | 7758 | 192 | 0    |

| FFT 32 U           | 181      | 13024 | 3136 | 192 | 0    |

| Demodulation P     | 181      | 2969  | 1416 | 40  | 0    |

| Demodulation U     | 181      | 2607  | 609  | 40  | 0    |

| Modulation U       | 205      | 7     | 2    | 0   | 0    |

| Modulation P       | inf      | 7     | 2    | 0   | 0    |

| Back Propagation P | 200      | 127   | 319  | 8   | 0    |

| Back Propagation   | 471      | 51    | 1    | 4   | 0    |

| U                  |          |       |      |     |      |

TABLE VII

PERFORMANCE AND RESOURCE CONSUMPTION COMPARISON BETWEEN

OPTIMISED AND UNOPTIMISED MAC16.

|                   | Max Freq | LUT  | FF   | DSP | BRAM |

|-------------------|----------|------|------|-----|------|

| Unoptimised       | 181      | 5079 | 2930 | 64  | 0    |

| MAC16             |          |      |      |     |      |

| Python Optimised  | 119      | 4325 | 995  | 64  | 0    |

| MAC16             |          |      |      |     |      |

| Verilog Optimised | 218      | 2789 | 2418 | 0   | 0    |

| MAC16             |          |      |      |     |      |

| Python+Verilog    | 186      | 2245 | 995  | 0   | 0    |

| Optimised MAC16   |          |      |      |     |      |

hand-coded Verilog, VeriPy achieves comparable maximum frequencies. Regarding resource utilisation, VeriPy adopts a modular architecture with a top-level file structure, resulting in resource usage similar to that of hand-coded Verilog, though slightly higher than that of the Vivado HLS version.

#### B. Readability and Optimisation

Figure 15 and Figure 16 display the Verilog code generated separately by the Vivado HLS and VeriPy approach. In the Vivado HLS version, the code is scarcely readable, even for a hardware engineer. However, according to the Verilog code generated by VeriPy, with the aid of automatic comment generation highlighting each step, readability is greatly enhanced compared to HLS. This ensures the feasibility of further improving the performance or power of the SDR application at the hardware level, if necessary.

Furthermore, the hardware design produced by this study consists of a package containing a generated Verilog Top file along with the provided Verilog files for fundamental functions. These fundamental function Verilog files can be easily substituted for performance or power optimisation purposes. VeriPy supports flexible optimisation at both the Python (high-level) and Verilog (low-level) stages. Users can either substitute the hardware implementation of fundamental functions or modify the overall hardware structure to optimise for performance, power, and area (PPA).

As shown in Table VII, Equation 1 is selected to demonstrate high-level, low-level, and combined optimisations. High-level optimisation refers to reducing computation within the design—for example, by minimising the number of operations inside a loop. Low-level optimisation involves replacing a fundamental hardware function with a more efficient custom implementation. Combined optimisation applies both high-level and low-level techniques to achieve improved overall design efficiency.

The results in Table VII demonstrate a frequency improvement of 1.2× and 1.03× when Verilog-level and combined Python+Verilog optimisations are applied, respectively. The table also highlights notable reductions in resource utilisation: Python-level optimisation yields a 15% reduction in LUT usage and a 67% reduction in flip-flop (FF) usage; Verilog-level optimisation results in a 45% reduction in LUTs, 17% in FFs, and complete elimination (100% reduction) of DSP usage. When both Python and Verilog optimisations are applied, the design achieves a 56% reduction in LUTs, 67% in FFs, and

TABLE VIII

LENGTH OF INPUT CODE COMPARISON BETWEEN VERIPY AND VIVADO

HLS.

|                 | VeriPy | VeriPy<br>Pragma | Vivado<br>HLS | Vivado<br>HLS |

|-----------------|--------|------------------|---------------|---------------|

|                 |        |                  |               | pragma        |

| MAC16           | 15     | 0                | 13            | 4             |

| FFT32           | 67     | 0                | 24            | 7             |

| Modulation      | 41     | 0                | 32            | 7             |

| Demodulation    | 50     | 0                | 34            | 6             |

| BackPropagation | 43     | 0                | 35            | 9             |

100% in DSPs. These results confirm the effectiveness and flexibility of VeriPy in supporting both high-level and low-level design optimisations.

# C. Length of Code (LoC)

The length of the input code is considered one of the comparison aspects of design effort in a code generation tool, like in [25]. Pragmas, which are commonly used in Vivado HLS for input/output port definitions and optimisation directives, represent another important factor when evaluating the ease of use of an HLS tool. Therefore, in this section, the lengths of the input code and the number of pragmas for the previous four examples are compared between VeriPy and HLS, as shown in Table tab:lengthofCode.

The data in Table VIII shows that the VeriPy tool requires a comparable number of input code lines to Vivado HLS when the design is simple. This is primarily due to VeriPy's one-to-one correspondence concept and its use of a limited set of fundamental functions, whereas Vivado HLS allows multiple operations to be expressed within a single statement and has more already-designed complicated functions that can be directly used. However, as VeriPy continues to evolve and its function library expands, the overall input code length is expected to decrease. Notably, VeriPy requires no pragma directives during design, further simplifying the development process.

## D. Performance and Resource Estimation

VeriPy also supports performance estimation of the number of processing cycles in pipelined designs, as well as resource estimation for both unrolled and pipelined designs.

As shown in Table IX, the performance estimation for processing cycles is 100% accurate. The resource estimation, while not exact, closely approximates the actual resource utilisation observed during the implementation stage.

# VI. CONCLUSTION

In this paper, VeriPy, a Python-based tool for SDR hardware accelerator development, has been proposed. The tool enables automatic generation of unrolled and pipelined hardware designs in Verilog based on high-level Python SDR algorithms, requiring no prior hardware design experience. VeriPy also supports automatic testbench generation, an extensible hardware library, performance and resource estimation, and enhanced readability of the generated Verilog code. Additionally, the tool offers strong potential for both high-level

| 77 'D          | D       | TITE  | - PP | DCD | DDAM |

|----------------|---------|-------|------|-----|------|

| VeriPy         | Process | LUT   | FF   | DSP | BRAM |

|                | Cycle   |       |      |     |      |

| MAC 16 P       | 17      | 5744  | 2930 | 64  | 0    |

| MAC 16 U       | NA      | 4320  | 1024 | 64  | 0    |

| FFT 32 P       | 34      | 47968 | 8192 | 512 | 0    |

| FFT 32 U       | NA      | 47968 | 8192 | 512 | 0    |

| Demodulation P | 13      | 3752  | 673  | 40  | 0    |

| Demodulation U | NA      | 3800  | 705  | 40  | 0    |

| Modulation P   | 2       | 1140  | 10   | 0   | 0    |

| Modulation U   | inf     | 820   | 10   | 0   | 0    |

| Back           | 7       | 1921  | 320  | 20  | 0    |

| Propagation P  |         |       |      |     |      |

| Back           | NA      | 7492  | 1152 | 80  | 0    |

| Propagation U  |         |       |      |     |      |

TABLE IX

ESTIMATED RESOURCE BY VERIPY.

and low-level design optimisation. These features not only accelerate the design process but also lower the learning curve and bridge the gap between SDR software developers and hardware engineers.

Performance and resource evaluation of VeriPy-generated designs—tested using identical SDR algorithms—shows that VeriPy can achieve up to 1.7× higher operating frequency than designs generated by Vivado HLS with optimisation pragmas, with only a minimal increase in resource usage. This improvement can be attributed to VeriPy's one-to-one module mapping approach, which contrasts with the more abstract generation strategy used in Vivado HLS. Moreover, VeriPy's strong optimisation potential allows for further PPA improvements when enhanced fundamental function modules or optimised architectural structures are integrated. Compared to hand-coded Verilog designs, VeriPy demonstrates comparable performance and resource efficiency, highlighting the quality of its hardware generation.

One limitation to be addressed in future work is the need for users to follow a VeriPy-compatible coding style in the Python input. Although no hardware knowledge is required, the current syntax and structure rules may still slow down the design process. Future development should focus on relaxing these input constraints to further streamline design and enhance usability.

In conclusion, the proposed Python-based VeriPy tool offers a compelling solution for SDR hardware accelerator generation. It excels in design speed, code readability, optimisation flexibility, and ease of use—thanks to features such as automatic testbench generation and accurate performance/resource estimation. While it may exhibit slightly higher resource usage than Vivado HLS, it delivers hardware quality comparable to hand-coded Verilog and remains accessible to users without hardware expertise, making it a practical and efficient tool for modern SDR hardware development.

# VII. REFERENCES SECTION

#### REFERENCES

Markus Dillinger, Kambiz Madani, Nancy Alonistioti (2003)., Software Defined Radio: Architectures, Systems and Functions. Wiley and Sons. p. xxxiii. ISBN 0-470-85164-3.

- [2] Schiphorst, Roel & Hoeksema, F.W. & Slump, C.H.. (2005). A Real-Time GPP Software-Defined Radio Testbed for the Physical Layer of Wireless Standards. EURASIP Journal on Advances in Signal Processing. 2005. 10.1155/ASP.2005.2664.

- [3] G. Sklivanitis, A. Gannon, S. N. Batalama and D. A. Pados, "Addressing next-generation wireless challenges with commercial software-defined radio platforms," in *IEEE Communications Magazine*, vol. 54, no. 1, pp. 59-67, January 2016, DOI. 10.1109/ MCOM.2016.7378427.

- [4] D. F. Macedo, D. Guedes, L. F. M. Vieira, M. A. M. Vieira and M. Nogueira, "Programmable Networks—From Software-Defined Radio to Software-Defined Networking," in *IEEE Communications Surveys & Tutorials*, vol. 17, no. 2, pp. 1102-1125, Secondquarter 2015, DOI. 10.1109/ COMST.2015.2402617.

- [5] V. Rosenfeld, S. Breß, and V. Markl, "Query Processing on Heterogeneous CPU/GPU Systems," in ACM Comput. Surv., vol. 55, no. 1, Jan. 2022, DOI. 10.1145/3485126.

- [6] P. R. Kshirsagar, D. H. Reddy, M. Dhingra, D. Dhabliya and A. Gupta, "A Review on Comparative study of 4G, 5G and 6G Networks," 2022 5th International Conference on Contemporary Computing and Informatics (IC3I), Uttar Pradesh, India, 2022, pp. 1830-1833, doi: 10.1109/IC3156241.2022.10073385.

- [7] I. Palamà et al., "From Experiments to Insights: A Journey in 5G New Radio Localization," 2023 21st Mediterranean Communication and Computer Networking Conference (MedComNet), Island of Ponza, Italy, 2023, pp. 74-82, doi: 10.1109/MedComNet58619.2023.10168856.

- [8] C. Karle, M. Kreutzer, J. Pfau, and J. Becker, "A hardware/software co-design approach to prototype 6G mobile applications inside the GNU Radio SDR Ecosystem using FPGA hardware accelerators," in Proceedings of the 12th International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies,, Jun. 2022, pp. 33–41 DOI. 10.1145/3535044.3535049.

- [9] E. J. Khatib, C. S. Álvarez-Merino, H. Q. Luo-Chen and R. B. Moreno, "Designing a 6G Testbed for Location: Use Cases, Challenges, Enablers and Requirements," in *IEEE Access*, vol. 11, pp. 10053-10091, 2023, DOI. 10.1109/ ACCESS.2023.3240775.

- [10] K. Yang, L. Liu, H. Liu, and T. Deng, "A novel parallel processing element architecture for accelerating ODE and AI," Tsinghua Science and Technology, vol. 30, no. 5, pp. 1954–1964, 2025.

- [11] S. Pinjerla, S. Rao S and C. Reddy P, "Sampling Rate Conversion Techniques- A Review," in 2021 4th International Conference on Recent Trends in Computer Science and Technology (ICRTCST), Jamshedpur, India, 2022, pp. 278-282, DOI. 10.1109/ ICRTCST54752.2022.9781914.

- [12] R. Akeela and B. Dezfouli, "Software-defined Radios: Architecture, state-of-the-art, and challenges," in *Computer Communications*, vol. 128, pp. 106–125, 2018, DOI. 10.1016/j.comcom.2018.07.012.

- [13] Truong, Nguyen & Suh, Young-Joo & Yu, Chansu. (2013). Latency analysis in GNU radio/USRP-based software radio platforms. Proceedings - IEEE Military Communications Conference MILCOM. 305-310. 10.1109/MILCOM.2013.60.

- [14] https://www.altera.com/products/development-tools/quartus-prime/hlscompiler

- [15] https://www.amd.com/en/products/software/adaptive-socs-and-fpgas/vivado/high-level-design.html

- [16] https://www.intel.com/content/www/us/en/docs/programmable/683680/21-4/high-level-synthesis-hls-design-examples.html

- [17] https://docs.amd.com/r/en-US/ug1399-vitis-hls/HLS-Pragmas

- [18] V. R. Gannapathy, T. Ibrahim, A. Fayeez, Z. Zakaria, A. R. Othman, and N. Q. Jalaudin, "A review on various types of software defined radios (sdrs) in radio communication," in *International Journal of Research in Engineering and Technology*, vol. 3, no. 12, pp. 203–209, 2014.

- [19] O. Gustafsson et al., "Architectures for cognitive radio testbeds and demonstrators — An overview," in 2010 Proceedings of the Fifth International Conference on Cognitive Radio Oriented Wireless Networks and Communications,, Cannes, France, 2010, pp. 1-6, DOI. 10.4108/ICST.CROWNCOM2010.9290..

- [20] S. Zhang, O. Wallscheid and M. Porrmann, "Machine Learning for the Control and Monitoring of Electric Machine Drives: Advances and Trends," in *IEEE Open Journal of Industry Applications*, vol. 4, pp. 188-214, 2023, DOI. 10.1109/OJIA.2023.3284717.

- [21] Y. Sun and E. A. Ball, "Automatic modulation classification using techniques from image classification," in *IET Commun*, vol. 16, no. 11, pp. 1303–1314, Jul. 2022, DOI. 10.1049/cmu2.12335.

- [22] Y. Zhao, T. Deng, B. Gavin, E. A. Ball and L. Seed, "An Ultralow Cost and Accurate AMC Algorithm and its Hardware Implementation," in *IEEE Open Journal of the Computer Society*, doi: 10.1109/OJCS.2024.3381827.

- [23] Y. Zhao, W. C. J. Gavin, T. Deng, E. A. Ball and L. Seed, "A Scalable and Accurate Chessboard-Based AMC Algorithm With Low Computing Demands," in *IEEE Access*, vol. 11, pp. 120955-120962, 2023, doi: 10.1109/ACCESS.2023.3328205.

- [24] Hemlata Dalmia, Sanjeet K. Sinha, "Analog to Digital Converters (ADC): A Literature Review," in 2nd International Conference on Design and Manufacturing Aspects for Sustainable Energy (ICMED),, 2020, DOI. 10.1051/202018401025.

- [25] Jason Lau, et al, "RapidStream IR: Infrastructure for FPGA High-Level Physical Synthesis," in *EEE/ACM International Conference on Computer-Aided Design (2024)*, New York, NY, USA, 2024, DOI. arXiv:2410.13079.

- [26] S. Singh and D. J. Greaves, "Kiwi: Synthesis of FPGA Circuits from Parallel Programs," in 2008 16th International Symposium on Field-Programmable Custom Computing Machines,, Stanford, CA, USA, 2008, pp. 3-12, DOI. 10.1109/FCCM.2008.46.

- [27] Guo, L., Chi, Y., Wang, J., Lau, J., Qiao, W., Ustun, E., Zhang, Z., & Cong, J. "AutoBridge: Coupling Coarse-Grained Floorplanning and Pipelining for High-Frequency HLS Design on Multi-Die FPGAs," in *The 2021 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays*,, pp. 81–92., DOI. 10.1145/3431920.3439289.

- [28] E. Mäkinen, "A Survey on Binary Tree Codings," in *The Computer Journal*, Volume 34, Issue 5, 1991, Pages 438–443, DOI. 10.1093/comjnl/34.5.438.

- [29] A. Canis et al., "LegUp: high-level synthesis for FPGA-based processor/accelerator systems," in *Proceedings of the 19th ACM/SIGDA International Symposium on Field Programmable Gate Arrays*,, 2011, pp. 33–36., DOI. 10.1145/1950413.1950423.

- [30] J. Villarreal, A. Park, W. Najjar and R. Halstead, "Designing Modular Hardware Accelerators in C with ROCCC 2.0," in 2010 18th IEEE Annual International Symposium on Field-Programmable Custom Computing Machines,, Charlotte, NC, USA, 2010, pp. 127-134, DOI. 10.1109/FCCM.2010.28.

on FPGAs.

YUQIN ZHAO, received the B.E. degree in electrical and computer engineering from Tamkang University, New Taipei City, Taiwan, in 2021 and the MSc. degree in electronics from Nanyang Technological University, Singapore, in 2022. He is currently pursuing a Ph.D. degree in electronic and electrical engineering at the University of Sheffield, Sheffield, UK. His research interest includes the development of an FPGA accelerator for AI and SDR, SDR implementation of SDR application, and high-level synthesis environment for SDR and AI applications

YE LINGHUI received the B.Eng. degree in Electronics and Computer Engineering from the University of Sheffield, UK, in 2025. She has been admitted to the Master of Computer Science at the University of Sydney, Australia.

Haihang Xia received the MSc degree in Electronic and Electrical Engineering from University of Glasgow, Glasgow, United Kingdom, in 2023. He is currently pursuing the PhD degree in Electronic and Electrical Engineering with the School of Electronic and Electrical Engineering, University of Sheffield, Sheffield, United Kingdom. His research interests include Spiking Neural Networks, Neuromorphic computing, AI acceleration, and digital systems design.

**Dr Tiantai Deng,** received his PhD from Queen's University Belfast in 2019, and BEng from Harbin Institute of Technologies in 2015. He is currently a lecturer at the University of Sheffield. Prior to his career as an academic, he was a senior engineer at HiSilicon, Huawei. His main research focus is on hardware acceleration for image processing, deep learning, and high-level design environments.

**Luke Seed,** is a Senior Lecturer in the Department of Electronic and Electrical Engineering at the University of Sheffield. His research interests extend from chip design through to holographic lithography.