## A 3D-integrated BiCMOS-silicon photonics high-speed receiver realized using micro-transfer printing

Ye Gu<sup>1\*†</sup>, He Li<sup>2\*†</sup>, Tinus Pannier<sup>1†</sup>, Shengpu Niu<sup>1</sup>, Patrick Heise<sup>3,4</sup>, Christian Mai<sup>3</sup>, Prasanna Ramaswamy<sup>5</sup>, Alex Farrel<sup>5</sup>, Alin Fecioru<sup>5</sup>, Antonio Jose Trindade<sup>5</sup>, Ruggero Loi<sup>5</sup>, Nishant Singh<sup>1</sup>, Senbiao Qin<sup>2</sup>, Biwei Pan<sup>2</sup>, Jing Zhang<sup>2</sup>, Johanna Rimböck<sup>6</sup>, Kristof Dhaenens<sup>7</sup>, Toon De Baere<sup>7</sup>, Geert Van Steenberge<sup>7</sup>, Dieter Bode<sup>8</sup>, Dimitrios Velenis<sup>8</sup>, Guy Lepage<sup>8</sup>, Neha Singh<sup>8</sup>, Joris Van Campenhout<sup>8</sup>, Xin Yin<sup>1</sup>, Günther Roelkens<sup>2\*</sup>, Peter Ossieur<sup>1\*</sup>

<sup>1</sup>IDLab, INTEC, Ghent University – imec, Ghent, 9052, Belgium. <sup>2</sup>Photonics Research Group, INTEC, Ghent University – imec, Ghent, 9052, Belgium.

<sup>3</sup>IHP- Leibniz-Institut für innovative Mikroelektronik, Frankfurt (Oder), Germany.

<sup>4</sup>Technical University of Applied Sciences Mittelhessen, Gießen, 35390, Germany.

<sup>5</sup> X-Celeprint Ltd., Lee Maltings, Dyke Parade, Cork, Ireland.

<sup>6</sup> EV Group, E. Thallner GmbH, St. Florian am Inn, Austria.

<sup>7</sup>Center for Microsystems Technology (CMST), INTEC, imec – Ghent University, Ghent, 9052, Belgium.

<sup>8</sup>imec, Kapeldreef 75, Leuven, 3001, Belgium.

\*Corresponding author(s). E-mail(s): Ye.Gu@ugent.be; He.Li@ugent.be; Gunther.Roelkens@UGent.be; Peter.Ossieur@imec.be; Contributing authors: Tinus.Pannier@ugent.be;

†These authors contributed equally to this work.

#### Abstract

Meeting the escalating demands of data transmission and computing, driven by artificial intelligence (AI), requires not only faster optical transceivers but also advanced integration technologies that can seamlessly combine photonic and electronic components. Traditional approaches struggle to overcome the parasitic limitations arising from fabricating those components using different processes. Here, we report a novel 3D heterogeneously integrated optical receiver based on micro-transfer printing  $(\mu TP)$ , enabling the co-integration of a compact bipolar CMOS (BiCMOS) electronic chiplet  $(0.06 \ mm^2)$  directly onto a silicon photonic integrated circuit (SiPIC). While previous  $\mu$ TP demonstrations have focused primarily on photonic integration, our work pioneers the direct integration of electronics and photonics, significantly enhancing performance and scalability. The resulting optical receiver achieves 224 Gb/s four-level pulse amplitude modulation (PAM-4) operation, delivering -5.2 dBm optical modulation amplitude (OMA) sensitivity at a bit-error rate (BER) of  $2.4 \times 10^{-4}$ , a record-small footprint, and an excellent power efficiency of 0.51 pJ/b. This demonstration not only showcases the potential of  $\mu$ TP for high-density, cost-efficient integration but also represents a critical step toward next-generation optical interconnects in the AI era.

**Keywords:** Heterogeneous integration, micro-transfer printing, silicon photonics, SiGe BiCMOS, optical receivers

#### 1 Introduction

The unprecedented acceleration in AI development is driven by remarkable advances in fields such as large language models and deep neural networks. As AI tasks continue to increase in both scale and complexity, the corresponding computational requirements have escalated dramatically. The implementation of optical interconnect technology enables high-bandwidth and energy-efficient communications between graphics processing units (GPUs) or central processing units (CPUs), supporting the development of scalable computing infrastructures for modern AI systems[1–4]. Optical transceivers serve as the interface between electrical and optical signals, and determine the performance and power efficiency of optical links. Those transceivers are typically composed of photonic integrated circuits (PICs) and electronic integrated circuits (EICs) from different processes and nodes, and heterogeneous integration is needed[5–11]. Monolithic integration, which integrates photonics and electronics into a single electronic-photonic integrated circuit (EPIC) [12–14], is associated with obstacles such as fabrication complexity, material constraints, high cost and limited design flexibility.

Heterogeneous integration of PICs and EICs allows largely independent selection and optimization of the processes with which both are fabricated, leading to superior performance as long as the interconnect parasitics can be kept small. Conventional 2-dimensional (2D) integration, such as wire-bonding integration, suffers from high parasitics [5, 15–18]. 3D integration, leveraging flip-chip, through-silicon vias and

backside redistribution layer, can reduce parasitics with shorter connections, improve integration density, and improve energy efficiency [6, 19–21].

Micro-transfer printing ( $\mu$ TP) technology has emerged as a promising approach for 3D heterogeneous integration [22, 23]. Compared with the traditional flip-chip assembly,  $\mu$ TP offers the advantages of high throughput and low cost[24].  $\mu$ TP allows for parallel assembly of many chiplets in a single operation, unlike flip-chip which is serial in nature. The heterogeneous integration of PICs using  $\mu$ TP technology has been demonstrated; for example, the heterogeneous integration of InAs/GaAs quantum dot semiconductor optical amplifiers (SOAs) in SiPICs [25], lithium niobate modulators in silicon nitride PICs[26], and photodiodes on silicon nitride PICs[27] have been successfully implemented. However, to date, no heterogeneous integration of PICs and high-speed EICs has been demonstrated to realize an optical receiver using  $\mu$ TP.

The sub-micron alignment accuracy of  $\mu$ TP [28] allows the EICs to occupy a small area as the X&Y dimensions of its bondpads can be shrunk accordingly, reducing the associated electrical parasitics (capacitance) and enabling density scaling. The small footprint optical engines are also required for co-packaged optical transceivers (CPO) with high shoreline density, so they can fit around the host application specific integrated circuits (ASICs). High-throughput integration is possible through massively parallel micro-transfer printing. Ref. [29] demonstrated the  $\mu$ TP of an EIC on a blank silicon wafer and metallization. Here, we demonstrate a further developed  $\mu$ TP process to integrate a silicon–germanium (SiGe) BiCMOS chiplet onto an advanced SiPIC, including metallization for the interconnection of both, to realize a high-speed optical receiver.

In this paper, we report the first  $\mu$ TP-based 3D integrated optical receiver integrating a SiGe BiCMOS chiplet on a SiPIC. The SiGe BiCMOS chiplet and the SiPIC are connected with lithographically defined metal traces. The SiGe BiCMOS chiplet contains a transimpedance amplifier (TIA) with a small footprint of 200  $\times$  300  $\mu m^2$ . 224 Gb/s PAM-4 operation is demonstrated, achieving -5.2 dBm OMA sensitivity at a BER of  $2.4 \times 10^{-4}$  (KP4-FEC) with a 6-tap feed-forward equalizer (FFE). The optical receiver achieves a low power consumption of 0.51 pJ/b and a small EIC footprint of 0.06  $mm^2$ .

#### 2 Concept

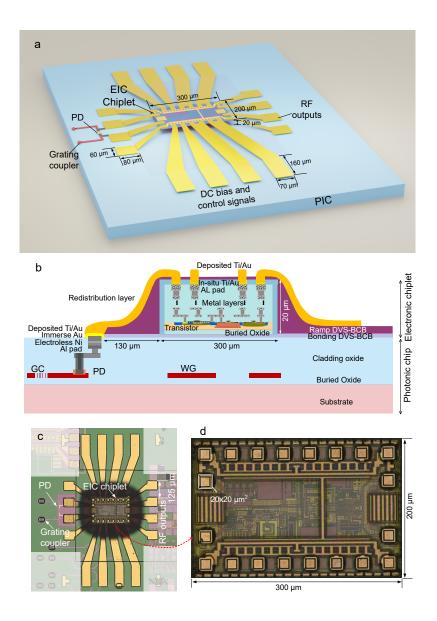

The 3-D and cross-section diagrams of the  $\mu$ TP-based optical receiver are shown in Fig. 1(a) and Fig. 1(b), respectively. The optical receiver consists of an EIC chiplet micro-transfer printed on a SiPIC. Fig. 1(c) shows a micrograph of the realized optical receiver, and Fig. 1(d) shows the EIC chiplet before  $\mu$ TP.

The PIC consists of a grating coupler to interface with an optical fiber and a waveguide-coupled O-band Germanium photodiode (PD), which is manufactured in imec's 300 mm silicon photonics platform (iSiPP300)[30]. Silicon photonics combines compatibility with mature CMOS fabrication technology and the ability to integrate diverse optical components, enabling the realization of compact, low-cost, and high-performance optical transceivers[31]. The PD features >50 GHz bandwidth and

Fig. 1 (a) 3D diagram of the optical receiver consisting of an EIC chiplet micro-transfer printed on a SiPIC and metal traces (b) Cross-section diagram of the optical receiver (c) Micrograph of the optical receiver (d) Micrograph of the EIC chiplet.

$0.9~\mathrm{A/W}$  responsivity at 1310 nm (O-band), supporting high band rate and good sensitivity optical receivers.

The EIC chiplet consists of a single-ended input TIA, which is used to convert the current signal from the PD into a voltage signal and to provide a buffer with

50 Ohm output impedance for measurements. The EIC is manufactured using an IHP 130 nm SiGe BiCMOS process. SiGe BiCMOS technology employs the high-speed bipolar junction transistors alongside the low-power characteristics of CMOS transistors, making it ideal for high-frequency applications[32]. In this work, the SiGe BiCMOS EIC is processed on silicon-on-insulator (SOI) wafers with <100> crystal orientation, to enable the release etch. The EIC chiplet is designed to have a compact footprint of 300  $\mu$ m in length, 200  $\mu$ m in width, and 20  $\mu$ m in height, enabling high-density integration. The high alignment accuracy of  $\mu$ TP technique allows the use of small pads with dimensions of 20  $\mu$ m × 20  $\mu$ m, reducing the parasitic capacitance.

The anode of the PD is connected to the input of the TIA, and the cathode of the PD is connected to a bias voltage on the TIA chiplet. As the pads of the TIA chiplet are too small to be probed or wire-bonded, the outputs of the TIA chiplet are fanned out on a divinylsiloxane-bis-benzocyclobutene (DVS-BCB) interlayer to larger pads  $(70 \ \mu m \times 80 \ \mu m)$  with a 125- $\mu m$  pitch, which can be measured with an electrical GSSG RF probe. The pads for the power, ground, and control signals are also redistributed to larger pads (70  $\mu$ m × 160  $\mu$ m) with Au traces for electrical interconnection in the measurement. The EIC chiplet is micro-transfer printed about 130  $\mu$ m away from the pads of the PD. It should be noted that, in order to further reduce interconnect parasitics, this distance could be shortened by further process optimizations. The pad of the PD on the PIC is  $60 \ \mu m \times 80 \ \mu m$ , which can also be further shrunk to reduce the parasitic capacitance. The choice for 20  $\mu$ m  $\times$  20  $\mu$ m and 60  $\mu$ m  $\times$  80  $\mu$ m pads was made to reduce risks in this proof-of-concept demonstrator. Further development of mainly the post-print metallization process would allow for even far smaller pad sizes below  $10 \ \mu m \times 10 \ \mu m$  on both PIC and EIC, and correspondingly smaller pitches between such pads.

#### 3 Integration process

$\mu$ TP provides an efficient approach for heterogeneous integration with minimal silicon electronic chip-area usage, as the bondpad size can be drastically reduced. The overall system performance is augmented due to lower parasitics, the risks associated with monolithic EPIC chip development are mitigated, and functionality becomes increasingly modularized. This strategy results in improved performance, decreased power consumption, reduced costs, and enhanced chip yield.

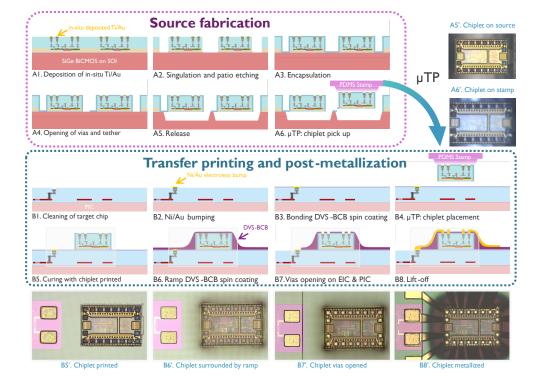

The integration process is schematically depicted in Fig. 2, with A1–A6 corresponding to source fabrication and B1–B8 to  $\mu$ TP and post-metallization process. The source fabrication comprises the definition of EIC chiplets on the source wafer by etching trenches, followed by dielectric encapsulation, tether defining and undercut etching. A poly-dimethylsiloxane (PDMS) stamp is then laminated against the source wafer, followed by fast retraction of the stamp, leaving the chiplet attached to the stamp. The chiplet is aligned and laminated to the target substrate, after which the stamp is retracted. The target photonic substrate is deposited with the electroless Ni/Au, cleaned, and coated with a DVS-BCB adhesive bonding layer onto which the electronic chiplets are printed. After curing, the substrate is coated again with DVS-BCB to form ramps, and the DVS-BCB is etched to form vias to the contact pads.

Fig. 2 A1–A6, Source fabrication steps including in-situ Au deposition, chiplet singulation, encapsulation, via opening, release, and  $\mu$ TP pick-up. A5'-A6': top view of released chiplet on source and stamp corresponding to A5-A6. B1–B8, Transfer printing and post-metallization steps including target cleaning, bumping, DVS-BCB coating,  $\mu$ TP placement, curing, ramping, via opening, and final metallization. B5'-B8': top view of chiplet printed, covered by ramp, via-opened and metallized corresponding to B5-B8.

The metallization traces are then formed to connect the TIA to the PD. More details on the fabrication process can be found in the Methods section.

### 4 Opto-electrical performance

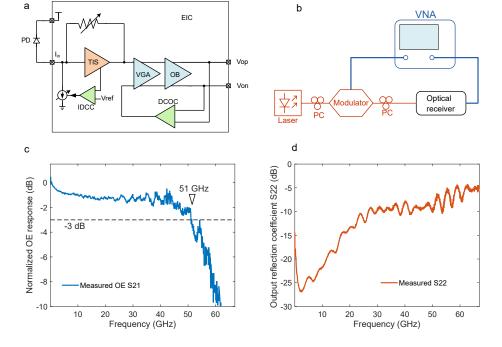

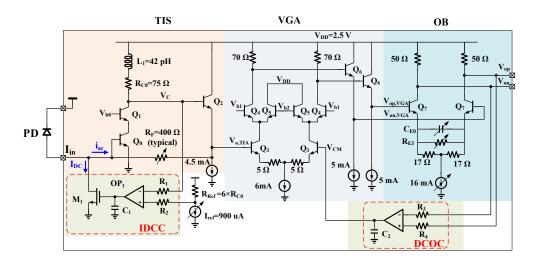

To realize high-speed PAM-4 optical receivers for next-generation optical links, EICs with high bandwidth, low noise, and low power consumption are required. The block diagram of the optical receiver is shown in Fig. 3(a). The EIC consists of a TIA input stage (TIS), a variable gain amplifier (VGA), an output buffer (OB), input DC current cancellation (IDCC), and a DC offset cancellation (DCOC) circuit. The schematic of the EIC can be found in the Supplementary Information.

Although a traveling wave circuit can achieve a higher bandwidth compared with a lumped-element circuit, it consumes much more power and occupies a larger area[5, 33]. Here, we use a lumped-element circuit structure to design the high-speed TIA to realize power-efficient chiplets. A shunt feedback structure is utilized as the TIS for

Fig. 3 Opto-electrical performance. (a) Block diagram of the optical receiver (b) Opto-electrical frequency response experiment setup (c) Measured OE response (d) Measured output reflection coefficient.

low noise, high bandwidth and low power consumption [34]. The IDCC circuit is used to absorb the DC current of the PD and provide a DC bias for the TIS stage. The feedback resistor is designed to be tunable to confront process variations. The digitally programmable VGA further amplifies the voltage signal of the TIS. The VGA, whose input common-mode reference voltage is generated by the DCOC loop, also serves as a single-to-differential converter. The OB with a 50  $\Omega$  output impedance is intended to send the output signals out of the chip for measurement. A tunable continuous-time linear equalizer is implemented in the OB to compensate for the loss at high frequencies. The output DC offset, caused by the VGA and OB, is eliminated by the DCOC circuit. A 2.5 V voltage is used as the power supply to realize low-power operation.

In this work, the TIA chiplet is designed with a small footprint of 300  $\mu$ m × 200  $\mu$ m, allowing high-density integration. The high alignment accuracy of  $\mu$ TP allows the use of small pads of 20  $\mu$ m × 20  $\mu$ m (and potentially smaller), enabling a compact chiplet size. The small pads also reduce the parasitic capacitance at the input and output, allowing an increase in the bandwidth and a reduction in the power consumption.

The opto-electrical (OE) response of the optical receiver is characterized using a VNA; the experiment setup is shown in Fig. 3(b). The grating coupler on the PIC is probed using a fiber probe, and the outputs of the optical receiver are probed using a GSSG RF probe. The measured OE response is shown in Fig. 3(c); the optical receiver

achieves 51 GHz 3-dB bandwidth. The measured output reflection coefficient is shown in Fig. 3(d). The output reflection coefficient S22 is less than -8 dB up to 50 GHz. The OE performance demonstrates the capability of achieving high-speed operation.

#### 5 Data transmission

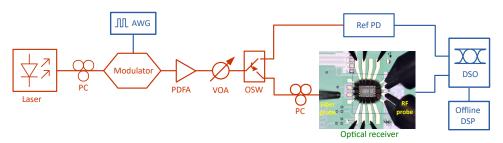

Fig. 4 Data transmission experiment setup

A data transmission experiment is carried out to characterize the time-domain performance of the optical receiver. The measurement setup is shown in Fig. 4. On the transmitter side, the laser is modulated by a  $2^{13}-1$  pseudo-random bit sequence (PRBS) pattern generated by an arbitrary waveform generator (AWG). A 70 GHz reference PD (Finisar XPDV3120) is used to capture the eye diagrams and the extinction ratios of the transmitter. BERs are obtained using the error bit counting method in MATLAB based on the recorded waveforms.

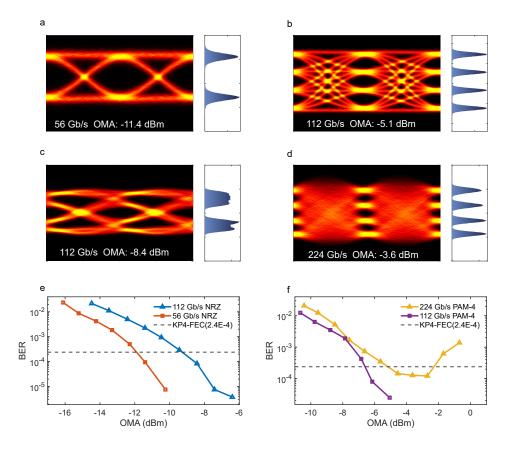

The 56 and 112 Gb/s non-retern-to-zero (NRZ) eye diagrams of the optical receiver measured by the digital sampling oscilloscope (DSO) are shown in Fig. 5 (a) and (c). All the NRZ eye diagrams are open without any equalization on the scope. The measured BER curve is also shown in Fig. 5 (e). Each BER point in the BER curves has at least 10 error bits in the BER counting. The optical receiver achieves -11.9 and -9.2 dBm optical modulation amplitude (OMA) sensitivity at the KP4-forward-error-correction (FEC) threshold of  $2.4 \times 10^{-4}$  for 56 and 112 Gb/s NRZ modulations, respectively. It should be noted that the minimum measured BER is limited by the finite waveforms recorded by the DSO.

The 112 and 224 Gb/s PAM-4 eye diagrams of the optical receiver measured by the DSO are shown in Fig. 5(b) and (d). 6-tap FFEs are employed on the scope to open the 224 Gb/s PAM-4 eye diagrams of the optical receiver. The 112 Gb/s PAM-4 eye diagram is widely open without any equalization used in the scope. The measured PAM-4 BER curves are also shown in Fig. 5(f). The optical receiver achieves -6.6 and -5.2 dBm OMA sensitivity at the KP4-FEC threshold of  $2.4 \times 10^{-4}$  for 112 and 224 Gb/s PAM-4 modulations, respectively. The total power consumption is 115 mW, corresponding to an energy efficiency of 0.51 pJ/b for 224 Gb/s PAM-4 operation.

Fig. 5 Data transmission experiment results. (a) 56 Gb/s NRZ eye diagram measured at -11.4 dBm. (b) 112 Gb/s PAM-4 eye diagram measured at -5.1 dBm. (c) 112 Gb/s NRZ eye diagram measured at -8.4 dBm. (d) 224 Gb/s PAM-4 eye diagram measured at -3.6 dBm with 6-tap FFE. (e) Measured 56 Gb/s and 112 Gb/s NRZ BER curves.(f) Measured 112 Gb/s and 224 Gb/s PAM-4 BER curves.

#### 6 Discussion

The measurement results demonstrate that the  $\mu$ TP-based optical receiver exhibits a high bandwidth, achieving 224 Gb/s PAM-4 operation. To the best of our knowledge, this is the first demonstration of a  $\mu$ TP-based optical receiver. The compact footprint of the EIC chiplet provides the potential for the integration of several chiplets on a single PIC to realize multi-channel IMDD receivers to increase the total data rate. This technique can also be used to realize other optical receivers, for example, coherent receivers and self-coherent receivers, which can utilize advanced modulation formats to achieve higher bit rates per lane.

Table I in the supplementary information shows the comparison with state-of-theart IMDD optical receivers using different integration methods. Ref. [5] reported a 224 Gb/s optical receiver using 2D wirebonding integration, where a traveling-wave transimpedance amplifier has been used to compensate the high parasitic inductance of the bond wires, which results in a relatively high power consumption of 2.2 pJ/b. Ref [6] reported a 264 Gb/s optical receiver using 3D direct-bonding integration, but it still features a power consumption of 1.45 pJ/b and occupies a relatively large EIC chip area of 0.6  $mm^2$ . This work achieves the lowest power consumption of 0.51 pJ/b and the smallest EIC area of 0.06  $mm^2$  among >200 Gb/s PAM-4 optical receivers. Our work provides a new integration method for next-generation high-speed optical receivers. Heterogeneous integration realized by  $\mu$ TP signifies a substantial advancement towards realizing multiterabit-per-second optical interconnects. Such systems enable compact and energy-efficient designs for next-generation computing and communication applications by integrating photonic and electronic functionalities into a unified platform. Such integration strategies establish a foundation for scalable and cost-effective solutions that meet the high-performance demands of modern systems and foster innovation across various application domains.

#### 7 Methods

#### 7.1 Sample preparation

The EICs are manufactured at IHP (Germany) using a tailored version of the SG13G2 SiGe BiCMOS process [35]. Rather than relying on the bulk silicon wafers of the SG13G2 technology, the process flow is modified to be compatible with a 200 mm SOI handle wafer with <100> crystal orientation incorporating a 1- $\mu$ m buried oxide (BOX) layer and a 1.5- $\mu$ m top silicon device layer for the front end of line (FEOL). The back end of line (BEOL) has a height of about 15  $\mu$ m and consists of seven metal layers, i.e. five thin Al-layers and two thick Al-layers. The chiplets are arranged on a dense grid on the reticle. To facilitate the release process, during the mask design it is ensured no metals are present in the spaces between the chiplets.

The processing of the EIC source chip to enable the micro-transfer printing is explained in [36]. After completing the wafer in IHP, Ti/Au is deposited to protect the contact pads and also serves as the process monitor in the following etching processes in X-Celeprint. Then, the chiplets are singulated by inductively coupled plasma (ICP) with a  $C_4F_8/H_2/He$  dry-etching to etch through the BEOL oxide stack and a  $SF_6/C_4F_8$  dry-etching to etch through the FEOL silicon. With another lithography to define the encapsulation patio, the remaining buried oxide (BOX) is etched away by  $C_4F_8/H_2/He$ , isolating all the coupons. Then the substrate is covered by a dielectric double layer of 500-1000 nm  $SiO_2$  and 1.5-2  $\mu$ m SiN. Another lithography and  $C_4F_8/H_2/He$  ICP dry-etch are used to define the tethers and the opening of the contact pads on the chiplets. Undercut and release of the coupons are achieved using a tetramethylammonium hydroxide (TMAH) solution at a ratio of TMAH:DI (1:4).

The target PIC is manufactured using imec's iSIPP300 process, a 300 mm photonic platform for high-speed applications. In the first post-processing step, The target PIC is cleaned using standard wet cleaning recipe with acetone, isopropyl alcohol, and deionized water, and then the aluminum contact pads are electroless-plated with Ni/Au to avoid the oxidation of aluminum and ensure low-ohmic contact during post-printing metallization. The sample is then cleaned again with wet cleaning. After

oxygen plasma, the sample is spin coated with AP3000 as the adhesion promoter for DVS-BCB. DVS-BCB is spin coated and soft cured at 150 °C for 15 min. The EIC chiplet is then transfer printed using a PDMS stamp and placed close to the PD with high placement accuracy of 1  $\mu$ m 3-sigma with micro-TP100 transfer printer. The DVS-BCB was then fully cured in a vacuum oven. Next, 2- $\mu$ m DVS-BCB is spin-coated to form a ramp for metallization followed by a complete cure. Subsequently, the chip is spin-coated with a bilayer of AZ10XT resist to achieve thick coverage over a large topography of more than 20  $\mu$ m. The resist over the contact pads on both the EIC and PIC is exposed and developed. Reflow of the resist is used to create a sloped sidewall on the via to make metallization easier. Dry etching is used to etch the DVS-BCB and the remaining dielectrics. Next, a Ti35E bilayer is used for better coverage for the lift-off lithography. The metal traces are then formed through the evaporation of Ti/Au and defined with a conventional lift-off process.

#### 7.2 Opto-electrical experiment

A laser (Santec TSL-570) generates a 1310 nm 13 dBm optical signal, which is coupled to an O-band lithium niobate Mach–Zehnder Modulator (MZM). The MZM is modulated by one port of a vector network analyzer (VNA) (Keysight PNA-X N5247B). The modulated optical signal is coupled to the optical receiver through an optical fiber. The differential outputs of the optical receiver are probed using a GSSG electrical probe with a 125  $\mu$ m pitch and connected to the ports of the VNA. After the measurement, the S-parameters of the modulator and the electrical probe are de-embedded to obtain the normalized OE response of the optical receiver.

#### 7.3 Data transmission experiment

A 1310 nm 13 dBm optical signal is generated by a continuous-wave (CW) laser (Santec TSL-570). A 256 GSa/s AWG (Keysight M8199B) generates a  $2^{13} - 1$  PRBS signal and drives an O-band lithium niobate MZM directly. The MZM is biased at the quadrature point by a DC supply, followed by a praseodymium-doped fiber amplifier (PDFA) to increase the optical power. A variable optical attenuator (VOA) is used to control the optical power coupled to the PD. An optical switch (OSW) is followed by a reference PD with a 70 GHz bandwidth and a polarization controller. The output of the reference PD is connected to the remote sampling head of a DSO (Keysight N1046A). To compensate for the bandwidth limitation at the transmitter side, de-embedding is utilized in the AWG to obtain a clear eye diagram at the output of the transmitter measured through the reference PD. The grating coupler on the PIC is probed by a fiber probe, and the coupling efficiency is improved by a polarization controller (PC). The outputs of the TIA chiplet are probed by a 67 GHz GSSG electrical probe with a pitch of 125  $\mu$ m and measured by two remote sampling heads of the DSO. The pads of power, ground, and control signals on the PIC are connected with DC probes. BERs are obtained using offline data processing in MATLAB based on the recorded waveforms. The OMAs are calculated based on the average currents of the PD on the PIC measured by a current meter and the extinction ratios after the MZM measured from the reference PD.

Supplementary information. Supplementary information is available.

**Acknowledgements.** This work is supported by EU-funded project CALADAN under grant number 825453.

Author contribution. Y.G. designed the electrical IC and measured the receiver. H.L. developed the micro-transfer printing and metallization process. T.P. designed the photonic IC and helped with the measurement. S.N. helped with electrical IC design. P.H. and C.M. helped with the electrical IC fabrication. P.R., R.L., A.F., A.T. and A.F. performed the release of chiplets. N.S. helped with the measurements. S.Q., B.P., and J.Z. helped with the micro-transfer printing. K.D., T.D., and G.V. assisted with electroless plating of nickel and gold. J.R. performed the spray-coating. D.B., D.V., G.L., N.S., and J.C. helped with the photonic IC fabrication. X.Y., G.R. and P.O. supervised the work. Y.G. and H.L. prepared the manuscript.

#### References

- [1] Nadal, L., Martínez, R., Ali, M., Vílchez, F.J., Fàbrega, J.M., Moreolo, M.S., Casellas, R.: Advanced optical transceiver and switching solutions for next-generation optical networks. Journal of Optical Communications and Networking 16(8), 64–75 (2024)

- [2] Ossieur, P., Moeneclaey, B., Lambrecht, J., Craninckx, J., Martens, E., Van Driessche, J., Declercq, J., Niu, S., Pannier, T., Gu, Y., et al.: High speed transceivers beyond 1.6 Tb/s for data centre networks. In: 49th European Conference on Optical Communications (ECOC 2023), vol. 2023, pp. 1598–1601 (2023)

- [3] Maniotis, P., Kuchta, D.M.: Exploring the benefits of using co-packaged optics in data center and AI supercomputer networks: a simulation-based analysis [invited]. Journal of Optical Communications and Networking 16(2), 143–156 (2024)

- [4] Baehr-Jones, T., Ardalan, S., Chang, M., Jafarlou, S., Serey, X., Zarris, G., Thompson, G., Darbinian, A., West, B., Behnia, B., et al.: Monolithically integrated 112 Gbps PAM4 optical transmitter and receiver in a 45 nm CMOS-silicon photonics process. Optics Express 31(15), 24926–24938 (2023)

- [5] Declercq, J., Moeneclaey, B., Lambrecht, J., Bruynsteen, C., Singh, N., Niu, S., Ossieur, P., Yin, X.: A 64-GHz optical receiver for 128-GBd links using a 55nm SiGe BiCMOS traveling-wave linear transimpedance amplifier. Journal of Lightwave Technology, 1–10 (2025)

- [6] Peczek, A., Wietstruck, M., Winzer, G., Mai, C., Lischke, S., Khafaji, M.M., Schulze, S., Voß, T., Krüger, P., Zimmermann, L.: 132 GBaud PAM4 IM/DD silicon receiver subassembly realized by stacking technology. Journal of Lightwave Technology, 1–6 (2025)

- [7] Patel, D., Sharif-Bakhtiar, A., Carusone, T.C.: A 112-Gb/s -8.2-dBm sensitivity 4-PAM linear TIA in 16-nm CMOS with co-packaged photodiodes. IEEE Journal of Solid-State Circuits 58(3), 771-784 (2023)

- [8] Sentieri, E., Copani, T., Paganini, A., Traldi, M., Palladino, A., Santipo, A., Gerosa, L., Repossi, M., Catrini, G., Campo, M., Radice, F., Diodato, A., Pelleriti, R., Baldi, D., Tarantini, L., Maggi, L., Radaelli, G., Cervini, S., Clerici, F., Moroni, A.: A 4-channel 200Gb/s PAM-4 BiCMOS transceiver with silicon photonics front-ends for Gigabit Ethernet applications. In: 2020 IEEE International Solid-State Circuits Conference (ISSCC), pp. 210–212 (2020)

- [9] Zafrany, A., Burgos, D., Cai, L., Chong, S., Cramm, C., Dadash, S., Giridharan, V., Gurumoorthy, V., Helal, B., Ho, C., Iyer, A., Jantzi, S., Loi, C., Nguyen, T., Parker, K., Pillai, E., Raviprakash, K., Ray, S., Rossi, P., Sun, Z., Tan, A., Tse, L., Wall, B., Wang, L., Wang, J., Wu, T.: A 200Gb/s low power DSP-based optical receiver and transmitter with integrated TIA and laser drivers. In: 2023 Optical Fiber Communications Conference and Exhibition (OFC), pp. 1–3 (2023)

- [10] Rho, D.-W., Park, J.-K., Ji, Y., Yang, S.-J., Choi, W.-Y.: A  $4\lambda \times 50\text{-Gb/s}$  Si photonic WDM transmitter with code-based wavelength calibration and locking. In: 2025 Optical Fiber Communications Conference and Exhibition (OFC), pp. 1–3 (2025)

- [11] Li, K., Thomson, D.J., Liu, S., Zhang, W., Cao, W., Littlejohns, C.G., Yan, X., Ebert, M., Banakar, M., Tran, D., et al.: An integrated CMOS-silicon photonics transmitter with a 112 Gigabaud transmission and picojoule per bit energy efficiency. Nature Electronics 6(11), 910–921 (2023)

- [12] Jo, Y., Oberon, M., Peczek, A., Ji, Y., Kim, M., Kim, H.-K., Kim, M.-H., Seiler, P.M., Lischke, S., Mai, C., Zimmermann, L., Choi, W.-Y.: Novel monolithic allsilicon coherent transceiver sub-assembly based on ring modulators. Journal of Lightwave Technology 42(20), 7298–7306 (2024)

- [13] Seiler, P.M., Voigt, K., Peczek, A., Georgieva, G., Lischke, S., Malignaggi, A., Zimmermann, L.: Multiband silicon photonic ePIC coherent receiver for 64 GBd QPSK. Journal of Lightwave Technology 40(10), 3331–3337 (2022)

- [14] Movaghar, G., Arrunategui, V., Liu, J., Maharry, A., Misak, S., Du, X., Schow, C.L., Buckwalter, J.F.: A monolithic O-band coherent optical receiver for energy-efficient links. IEEE Journal of Solid-State Circuits 59(5), 1409–1420 (2024)

- [15] Lambrecht, J., Ramon, H., Moeneclaey, B., Verbist, J., Verplaetse, M., Vanhoecke, M., Ossieur, P., De Heyn, P., Van Campenhout, J., Bauwelinck, J., Yin, X.: 90-Gb/s NRZ optical receiver in silicon using a fully differential transimpedance amplifier. Journal of Lightwave Technology 37(9), 1964–1973 (2019)

- [16] Gu, Y., Lambrecht, J., Niu, S., Vandierendonck, A., Bruynsteen, C., Coudyzer,

- G., De Bruyn, K., Bauwelinck, J., Yin, X., Ossieur, P.: A 160 Gb/s PAM-4 optical receiver using a fully differential transimpedance amplifier in SiGe BiCMOS. Journal of Lightwave Technology **42**(23), 8237–8244 (2024)

- [17] Ossieur, P., Moeneclaey, B., Coudyzer, G., Lambrecht, J., Craninckx, J., Martens, E., Van Driessche, J., Bruynsteen, C., De Busscher, J., Declercq, J., Gu, Y., Niu, S., Pannier, T., Singh, N., Van Severen, L., Bogaert, L., Maes, D., Vanackere, T., Vissers, E., Zhang, J., Kumari, S., Oldenbeuving, R., Zhang, X., Van Elzakker, G., Van Campenhout, J., Absil, P., Kuyken, B., Yin, X., Torfs, G., Missinne, J., Van Steenberge, G., Roelkens, G., Bauwelinck, J.: Integrated photonics and electronics for optical transceivers supporting AI/ML applications. IEEE Journal of Selected Topics in Quantum Electronics 31(3: AI/ML Integrated Opto-electronics), 1–16 (2025)

- [18] Liu, H., Zhang, Z., Liu, Y., Chen, D., Lu, D., He, J., Li, G., Liu, M., Dang, Z., Xiao, X., Qi, N.: A 4×112 Gb/s PAM-4 silicon-photonic transmitter and receiver chipsets for linear-drive co-packaged optics. IEEE Journal of Solid-State Circuits 59(10), 3263–3276 (2024)

- [19] Xiang, C., Bowers, J.E.: Building 3D integrated circuits with electronics and photonics. Nature Electronics **7**(6), 422–424 (2024)

- [20] Chang, P.-H., Samanta, A., Yan, P., Fu, M., Zhang, Y., On, M.B., Kumar, A., Kang, H., Yi, I.-M., Annabattuni, D., Scott, D., Patti, R., Fan, Y.-H., Zhu, Y., Palermo, S., Yoo, S.J.B.: A 3D integrated energy-efficient transceiver realized by direct bond interconnect of co-designed 12 nm FinFET and silicon photonic integrated circuits. Journal of Lightwave Technology 41(21), 6741–6755 (2023)

- [21] Chang, P.-H., Yan, P., Samanta, A., Fu, M., Zhang, Y., On, M.B., Kumar, A., Kang, H., Yi, I.-M., Annabattuni, D., Scott, D., Patti, R., Fan, Y.-H., Zhu, Y., Ben Yoo, S.J., Palermo, S.: Energy-efficient optical transceiver circuits enabled by 3D heterogeneous integration. In: 2024 IEEE Silicon Photonics Conference (SiPhotonics), pp. 1–2 (2024)

- [22] Roelkens, G., Zhang, J., Bogaert, L., Soltanian, E., Billet, M., Uzun, A., Pan, B., Liu, Y., Delli, E., Wang, D., Oliva, V.B., Ngoc Tran, L.T., Guo, X., Li, H., Qin, S., Akritidis, K., Chen, Y., Xue, Y., Niels, M., Maes, D., Kiewiet, M., Reep, T., Vanackere, T., Vandekerckhove, T., Lufungula, I.L., De Witte, J., Reis, L., Poelman, S., Tan, Y., Deng, H., Bogaerts, W., Morthier, G., Van Thourhout, D., Kuyken, B.: Present and future of micro-transfer printing for heterogeneous photonic integrated circuits. APL Photonics 9(1), 010901 (2024)

- [23] Zhang, J., Muliuk, G., Juvert, J., Kumari, S., Goyvaerts, J., Haq, B., Beeck, C., Kuyken, B., Morthier, G., Van Thourhout, D., et al.: III-V-on-Si photonic integrated circuits realized using micro-transfer-printing. APL photonics 4(11) (2019)

- [24] Roelkens, G., Zhang, J., Bogaert, L., Billet, M., Wang, D., Pan, B., Kruckel, C.J., Soltanian, E., Maes, D., Vanackere, T., et al.: Micro-transfer printing for heterogeneous Si photonic integrated circuits. IEEE Journal of Selected Topics in Quantum Electronics 29(3: Photon. Elec. Co-Inte. and Adv. Trans. Print.), 1–14 (2023)

- [25] Liu, Y., Zhang, J., Bogaert, L., Soltanian, E., Delli, E., Morozov, K., Mikhrin, S., Rimböck, J., Lepage, G., Verheyen, P., Campenhout, J.V., Ossieur, P., Morthier, G., Roelkens, G.: Micro-transfer printing of O-band InAs/GaAs quantum-dot SOAs on silicon photonic integrated circuits. Photonics Research 13(5), 1341– 1352 (2025)

- [26] Vanackere, T., Vandekerckhove, T., Bogaert, L., Billet, M., Poelman, S., Cuyvers, S., Van Kerrebrouck, J., Moerman, A., Caytan, O., Singh, N., Lemey, S., Torfs, G., Ossieur, P., Roelkens, G., Clemmen, S., Kuyken, B.: Heterogeneous integration of a high-speed lithium niobate modulator on silicon nitride using micro-transfer printing. APL Photonics 8(8), 086102 (2023)

- [27] Maes, D., Lemey, S., Roelkens, G., Zaknoune, M., Avramovic, V., Okada, E., Szriftgiser, P., Peytavit, E., Ducournau, G., Kuyken, B.: High-speed uni-travelingcarrier photodiodes on silicon nitride. APL Photonics 8(1) (2023)

- [28] Gomez, D., Thostenson, J., Moore, T., Oswalt, K., Reyes, C., Cok, R., Fecioru, A.: Micro transfer printing for micro assembly of heterogeneous integrated compound semiconductor components. In: CS MANTECH Conference (2022)

- [29] Li, H., Pannier, T., Gu, Y., Loi, R., Ramaswamy, P., Steglich, P., Pan, B., Zhang, J., Ossieur, P., Roelkens, G.: Electronic-photonic integrated circuits through micro-transfer printing. In: 2025 IEEE Silicon Photonics Conference (SiPhotonics), pp. 1–2 (2025)

- [30] Ferraro, F., De Heyn, P., Kim, M., Rajasekaran, N., Berciano, M., Muliuk, G., Bode, D., Lepage, G., Janssen, S., Magdziak, R., et al.: Imec silicon photonics platforms: performance overview and roadmap. In: Next-Generation Optical Communication: Components, Sub-Systems, and Systems XII, vol. 12429, pp. 22–28 (2023)

- [31] Streshinsky, M., Ding, R., Liu, Y., Novack, A., Galland, C., Lim, A.-J., Guo-Qiang Lo, P., Baehr-Jones, T., Hochberg, M.: The road to affordable, large-scale silicon photonics. Optics and Photonics News **24**(9), 32–39 (2013)

- [32] Koch, U., Uhl, C., Hettrich, H., Fedoryshyn, Y., Hoessbacher, C., Heni, W., Baeuerle, B., Bitachon, B.I., Josten, A., Ayata, M., et al.: A monolithic bipolar CMOS electronic-plasmonic high-speed transmitter. Nature Electronics 3(6), 338–345 (2020)

- [33] Säckinger, E.: Broadband Circuits for Optical Fiber Communication. John Wiley

- & Sons, Hoboken, NJ, USA (2005)

- [34] Säckinger, E.: Analysis and Design of Transimpedance Amplifiers for Optical Receivers. John Wiley & Sons, Hoboken, NJ, USA (2017)

- [35] Rücker, H., Heinemann, B., Fox, A.: Half-Terahertz SiGe BiCMOS technology. In: 2012 IEEE 12th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, pp. 133–136 (2012)

- [36] Loi, R., Ramaswamy, P., Farrell, A., Trindade, A.J., Fecioru, A., Rimböck, J., Eartl, S., Pantouvaki, M., Lepage, G., Van Campenhout, J., et al.: Micro transfer printing of electronic integrated circuits on silicon photonics substrates. In: Proc. Eur. Conf. Integr. Opt.(ECIO), Milano, Italy (2022)

- [37] Wu, D., Wang, D., Chen, D., Yan, J., Dang, Z., Feng, J., Chen, S., Feng, P., Zhang, H., Fu, Y., et al.: Experimental demonstration of a 160 Gbit/s 3D-integrated silicon photonics receiver with 1.2-pJ/bit power consumption. Optics Express 31(3), 4129–4139 (2023)

- [38] Lakshmikumar, K., Kurylak, A., Nandwana, R.K., Das, B., Pampanin, J., Brubaker, M., Hanumolu, P.K.: A 7 pA/√Hz asymmetric differential TIA for 100Gb/s PAM-4 links with -14dBm optical sensitivity in 16nm CMOS. In: 2023 IEEE International Solid-State Circuits Conference (ISSCC) (2023)

- [39] Baehr-Jones, T., Ardalan, S., Chang, M., Jafarlou, S., Serey, X., Zarris, G., Thompson, G., Darbinian, A., West, B., Behnia, B., Velev, V., Li, Y.Z., Roelofs, K., Wu, W., Mali, J., Zhan, J., Ophir, N., Horng, C., Narevich, R., Guan, F., Yang, J., Wu, H., Maupin, P., Manley, R., Ahuja, Y., Novack, A., Wang, L., Streshinsky, M.: Monolithically integrated 112 Gbps PAM4 optical transmitter and receiver in a 45nm cmos-silicon photonics process. Opt. Express 31(15), 24926–24938 (2023)

#### 8 Supplymentary

#### 8.1 Transimpedance amplifier chiplet

The simplified schematic of the transimpedance amplifier (TIA) chiplet is shown in Fig. 6. The TIA input stage (TIS) utilizes a typical shunt feedback structure to convert the AC current signal of the PD into a voltage signal. Two electrostatic discharge (ESD) diodes, with a total of 51 fF parasitic capacitance, are placed at the input of the TIS to protect the internal circuits.  $Q_1$  serves to alleviate the Miller effect of the parasitic base-collector capacitor of  $Q_0$ . A shunt inductor  $L_1$ , with  $25 \times 25 \ \mu \text{m}^2$ area, is used to increase the phase margin of the TIA loop. The feedback resistor  $R_F$ , implemented as NMOS transistors and a polysilicon resistor, can be adapted by digital bits to compensate for the process variation.  $M_1$  in the input DC current cancellation (IDCC) is used to absorb the DC current of the PD and the DC current of  $R_F$ .  $C_1$  is used to compensate for the IDCC loop and alleviate the baseline wander.  $R1 = 4k\Omega$ , placed close to the base of  $Q_2$ , is used to prevent the parasitic capacitance of the IDCC from affecting the high-speed path. As  $R_{Ref} = 6 \times R_{C0}$ , the  $Q_0$  collector current  $I_{C,Q_0} \approx 6 \times I_{ref} = 5.4 mA$ , which impacts the overall bandwidth and input-referred noise current of the TIA.  $I_{ref}$  is designed to be tunable and controlled by digital registers.  $R_{Ref}$  and  $R_{C0}$  are placed close to each other in the layout for matching.

Fig. 6 Simplified schematic of the TIA chiplet.

The DC voltage at the input of the TIS is equal to one base-emitter forward bias voltage  $V_{be,Q_0}\approx 0.75V$ . The PD cathode bias voltage can be chosen to be the same as the main supply voltage of 2.5 V, so that the PD is reversely biased with a  $\sim 1.75$  V voltage difference.

The TIS is followed by the variable gain amplifier (VGA) stage, which also serves as a single-to-differential converter. One input of the VGA is connected to the output

of the TIS, the other input is connected to a reference voltage generated by the DCOC. The gain of the VGA can be fine-tuned by changing  $V_{b1}$  and  $V_{b2}$  through digital bits. Two 50  $\Omega$  resistors are used for impedance matching in the output buffer (OB) stage. The OB stage has a tunable CTLE, realized by a tunable capacitor  $C_{E0}$  and a tunable resistor  $R_{E3}$ . The  $R_{E3}$  is realized using NMOS transistors in the triode region, whose resistance is programmable by tuning their gate voltages. The  $C_{E0}$  is realized using PMOS varicaps, which can be fine-tuned by digital registers. The differential

outputs of the OB are also protected by ESD diodes.

# 8.2 Comparison with current state-of-the-art optical receivers using different integrations

Table 1 shows the comparison with the state-of-the-art IMDD optical receivers using different integration methods. This  $\mu$ TP based optical receiver achieves the lowest power consumption of 0.51 pJ/b and the smallest EIC area of 0.06  $mm^2$ .

${\bf Table~1~Comparison~with~current~state-of-the-art~PAM-4~optical~receivers~using~different~integrations.}$

| ref.         | Integration            | EIC<br>technology | Data<br>rate<br>(Gb/s) | $R_T$ (dB $\Omega$ ) | R<br>(A/W) | Sens.<br>@KP4<br>(dBm) | pJ/b | EIC Area $(mm^2)$ | DSP                       |

|--------------|------------------------|-------------------|------------------------|----------------------|------------|------------------------|------|-------------------|---------------------------|

| [16]         | Wire-bonding<br>(2D)   | 130nm<br>BiCMOS   | 160                    | 65                   | 0.8        | -7                     | 0.99 | $0.82^{1}$        | 5-tap FFE                 |

| [5]          | Wire-bonding<br>(2D)   | 55nm<br>BiCMOS    | 224                    | 57.3                 | 0.89       | -4.8                   | 2.2  | $1.38^{1}$        | 10-tap FFE                |

| [37]         | Flip-chip<br>(3D)      | N/A               | 160                    | N/A                  | 0.85       | -2.7                   | 1.2  | N/A               | 51-tap FFE                |

| [38]         | Flip-chip<br>(3D)      | 16nm<br>FinFET    | 106.25                 | 77                   | N/A        | -13.97                 | 0.98 | 0.64              | 12-tap FFE +<br>1-tap DFE |

| [6]          | Direct-bonding<br>(3D) | 130nm<br>BiCMOS   | 264                    | 60                   | 0.9        | N/A                    | 1.45 | 0.6               | 6-tap FFE                 |

| [39]         | Monolithic             | 45nm<br>CMOS      | 112                    | 68                   | 0.245      | N/A                    | 1    | N/A               | N/A                       |

| This<br>work | uTP (3D)               | 130nm<br>BiCMOS   | 224                    | 53.6                 | 0.9        | -5.2                   | 0.51 | 0.06              | 6-tap FFE                 |

<sup>&</sup>lt;sup>1</sup> data path core of one channel.