# FPGA-Enabled Modulo ADC with ×100 Dynamic-Range Expansion: Hardware Design and Performance Evaluation

Zeyuan Li, Wenyi Yan, Lu Gan, Guoquan Li, Hongqing Liu

Abstract—Conventional analog-to-digital converters (ADCs) fail to capture high-dynamic-range (HDR) signals due to clipping. Modulo ADCs circumvent this limitation by folding the input prior to quantization and algorithmically reconstructing the original waveform. This work presents a field-programmable gate array (FPGA)-based modulo ADC platform for systematic HDR performance evaluation. The mixed-signal architecture integrates a precision analog front end with a 200-MHz FPGA control loop that incorporates multi-bit updates and digital undercompensation calibration, ensuring stable folding and accurate feedback generation. The system achieves more than a hundredfold dynamic-range expansion within a 400-kHz bandwidth while maintaining fidelity comparable to that of a conventional ADC. A system-on-chip (SoC)-like implementation enables on-board real-time recovery and supports benchmarking of state-of-theart reconstruction algorithms, providing a compact and practical framework for HDR signal acquisition and evaluation.

Index Terms—Analog-to-digital converters (ADCs), modulo sampling, sampling methods, signal reconstruction, field-programmable gate array (FPGA) implementation.

#### I. Introduction

Analog-to-digital converters (ADCs) convert analog signals into digital data, serving as the bridge between the physical world and computer systems. They are fundamental components in sensors, communication systems, digital signal processing, and test-and-measurement instruments such as oscilloscopes, spectrum analyzers, and network analyzers [1], [2]. However, conventional ADCs suffer from clipping when high-dynamic-range (HDR) signals exceed the input range, leading to irreversible information loss [3]–[5].

Modulo sampling systems [6]–[8] address this limitation by folding the input signal into a bounded interval  $[-\lambda,\lambda)$  prior to digitization, followed by algorithmic reconstruction of the original waveform. For a real-valued signal g(t) with a modulo threshold  $\lambda>0$ , the operation is defined as [8]

$$y(t) = \mathcal{M}_{\lambda}\{g(t)\} = g(t) - 2\lambda \left\lfloor \frac{g(t) + \lambda}{2\lambda} \right\rfloor,$$

(1)

where  $\lfloor \cdot \rfloor$  denotes the floor function. A key performance metric of modulo ADCs is the dynamic-range expansion factor, defined as

$$\rho \triangleq \frac{\|g\|_{\infty}}{\lambda},\tag{2}$$

where  $||g||_{\infty}$  denotes the bounded signal amplitude. The ratio  $\rho$  expresses how many times the input amplitude exceeds the threshold and thus the effective dynamic-range extension.

This work has been submitted to the IEEE for possible publication. Copyright may be transferred without notice, after which this version may no longer be accessible.

Numerous algorithms have been proposed for reconstructing modulo-sampled signals. Among them, approaches based on high-order and first-order difference formulations have been theoretically validated as effective examples [8]–[11]. However, practical hardware implementations capable of verifying their performance under real measurement conditions remain limited, as existing modulo ADC prototypes offer only modest folding depth ( $\rho < 20$ ) and bandwidth [12], [13]. Existing modulo ADC prototypes are typically limited by their use of analog feedback loops or microcontroller-based control. Analog implementations suffer from bandwidth constraints, temperature drift, and stability issues, whereas microcontroller-based systems exhibit insufficient response speed for high-frequency folding. These limitations hinder precise calibration and make systematic performance evaluation difficult.

Seeing the limitations of existing hardware implementations, we develop an field-programmable gate array (FPGA)-based modulo ADC platform as the main control system to provide flexible digital operation, precise calibration, and deeper folding capability. The main contributions of this work are summarized as follows:

- Deeper and high-frequency folding operation: The system adopts a mixed-signal architecture with a 200 MHz FPGA-based digital control loop, supporting up to 400 kHz signal bandwidth and achieving over-hundred-fold dynamic-range expansion ( $\rho > 100$ ).

- Digitally calibrated and SoC-like real-time observation: The SoC-like mixed-signal architecture incorporates digital calibration to reduce folding errors such as overshoot and integrates an on-board direct reconstruction module, enabling real-time monitoring of folding dynamics and system stability.

- Unified and extensible experimental platform: The developed platform supports configurable modulo ADC thresholds and diverse test signals, including both basic and communication waveforms, providing a unified environment for comprehensive evaluations of existing recovery algorithms.

The remainder of this paper is organized as follows. Section II summarizes existing hardware implementations and representative recovery algorithms. Section III describes the proposed FPGA-based mixed-signal prototype in detail. Section IV presents hardware measurement results under various signal configurations. Section V concludes the paper.

#### II. LITERATURE REVIEW

A. Basics of Modulo Sampling and Conventional Dynamic Range Extension techniques

Consider a real bandlimited signal g(t) that is folded prior to digitization by a modulo operation restricting its amplitude to  $[-\lambda,\lambda)$ . The folded waveform is denoted by y(t). Ideal noiseless uniform sampling with sampling period  $T=1/f_s$ , where  $f_s$  is the sampling rate, yields  $y[k]=\mathcal{M}_{\lambda}(g(kT))$ . Digital recovery methods aim to reconstruct the unfolded samples g[k] from the bounded modulo data y[k], producing an approximation  $\tilde{g}[k]$  of the true values.

This approach fundamentally differs from classical HDR techniques. Automatic gain control (AGC) prevents ADC overload by reducing gain when large signal components appear, but global attenuation can bury weak features below the quantization floor [14]–[16]. Oversampling  $\Delta\Sigma$  converters enhance in-band SNR through noise shaping and decimation, proving effective at modest bandwidths, but the required oversampling ratios and decimation complexity scale unfavorably with bandwidth and resolution [17]–[19]. Successive-Approximation-Register (SAR) ADCs achieves energy efficiency and can extend dynamic range (DR) through range switching and multi-step conversions, yet remain constrained by fixed full-scale limits [20]–[22].

In contrast to these approaches that *prevent* signal overload, modulo sampling deliberately accepts localized folding events and shifts DR extension to the *signal processing domain*.

# B. Existing Recovery Algorithm

The modulo samples satisfy the decomposition [8]

$$g[k] = y[k] + \varepsilon_g[k], \qquad \varepsilon_g[k] \in 2\lambda \mathbb{Z},$$

where  $\varepsilon_q[k]$  is the discrete version of the residual signal  $\varepsilon_q(t)$ . Bhandari et al. [8] established the Unlimited Sampling framework (USF), which employs high-order finite differences to unwrap folded samples. When the sampling rate exceeds  $1/(2\Omega e)$ , the modulo operator becomes inactive, enabling accurate recovery of the residual function. Yan et al. [11] further tightened the sampling condition to  $T < 1/\Omega$  and fixed the difference order to two (RSoD) to enhance reconstruction robustness. Subsequent studies adopted first-order formulations for improved stability and computational efficiency: Guo et al. [9] presented the ITER-SIS algorithm, an iterative approach resilient to noise and spectral leakage; Shah et al. [23] proposed the LASSO-B<sup>2</sup>R<sup>2</sup> method, which formulates residual estimation as a sparse recovery problem using LASSO; and Zhang et al. [10] introduced the USLSE technique, combining dynamic programming and Orthogonal Matching Pursuit (OMP) for line spectral estimation of modulo-sampled signals in the frequency domain.

Beyond the single-channel methods reviewed above, several approaches incorporate additional information to resolve folding ambiguities [24]–[28]. Bernardo *et al.* [29] proposed recovery schemes with and without auxiliary 1-bit folding information in the presence of quantization noise. Chinese Remainder Theorem (CRT)-based multi-channel architectures employ multiple modulo ADCs with distinct thresholds to

achieve HDR reconstruction [24], [30]. Guo *et al.* [26] further extended this idea to a quad-channel sub-Nyquist USF system using distinct thresholds and time-delayed channels.

In this work, two recovery modes are considered: (a) When the folding count is known and recorded in the FPGA, the original signal is directly reconstructed from y[k] and the stored count for real-time monitoring and visualization of the folding process, further analyzed in Section III-C3. (b) When the folding count is unknown, only the folded signal is used, and single-channel recovery algorithms reconstruct the waveform for performance evaluation (Section IV).

# C. Prototype Hardware Implementations

Early modulo-sampling hardware prototype employs *purely* analog loops composed of an op-amp integrator and dual comparators for threshold detection and feedback [12], [31]–[34]. The comparators generate polarity-reversed feedback pulses when the integrator output exceeds  $\pm \lambda$ , folding large signals within a limited voltage range. This compact, low-power design operates without digital control or clocking but suffers from distortion at high frequencies due to limited analog bandwidth, integrator saturation, and temperature drift. Guo *et al.* [35] demonstrated that accurate recovery is still achievable by algorithmically compensating folding distortion, albeit with higher computational complexity and dense oversampling requirements. These limitations motivate mixed-signal architectures integrating analog folding with digital counting and DAC feedback for improved stability and control.

The mixed-signal architecture typically comprises an analog front end with an operational-amplifier chain, comparators for threshold detection, and a DAC-based feedback path, while a microcontroller handles digital counting and control. Zhu *et al.* [13] demonstrated an analog–digital prototype integrating these components, achieving a dynamic-range expansion of approximately  $\rho\approx 10$  within an  $\sim 8$  kHz bandwidth. Mulleti *et al.* [36] reported a similar design using a faster Teensy 4.1 controller, reaching about  $\rho\approx 8$  at  $\sim 10$  kHz. In both systems, the folding depth was limited by the supply voltage, threshold level, and DAC resolution, while the effective bandwidth was constrained by control-loop latency, mainly determined by the digital controller response time, analog front-end bandwidth, and DAC settling time.

This work addresses these limitations with an FPGA-based mixed-signal design enabling deeper and more accurate folding through improved timing and digital calibration.

## III. HARDWARE IMPLEMENTATION

# A. System Overview and Implementation Highlights

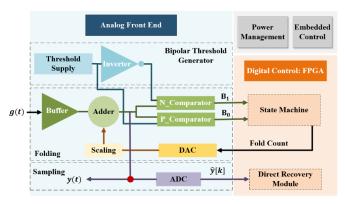

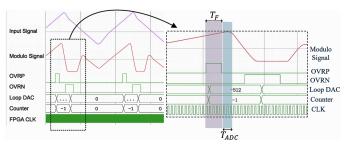

From a signal-flow perspective, Fig. 1 illustrates the operation of the FPGA-based modulo ADC prototype. The input signal g(t) passes through the analog front end (AFE), where it is continuously monitored by a high-speed window comparator. Whenever the input voltage exceeds either threshold  $\pm \lambda$ , the comparator asserts digital flags to the FPGA. A finite-state machine (FSM) interprets these flags and updates a signed folding-count register  $C_f$  at the FPGA control-loop clock rate

Fig. 1: Simplified block diagram of the FPGA-based modulo ADC prototype.

$T_c$ . This register tracks the cumulative number of modulo folds performed in the analog domain and directly drives the DAC.

To model the feedback path, we denote by  $C_f[n]$  the value of the folding-count register  $C_f$  at the n-th FPGA clock cycle. The DAC performs zero-order-hold (ZOH) reconstruction, holding each value  $C_f[n]$  over the interval  $[nT_c, (n+1)T_c)$ . After passing through the AFE scaling stage with calibrated gain  $G_{\rm total}$ , the resulting analog folding-feedback voltage becomes a continuous-time, piecewise-constant signal that can be written as

$$v_f(t) = \sum_{n = -\infty}^{\infty} \left( G_{\text{total}} V_{\text{DAC,step}} C_f[n] \right) \text{Rect}_{T_c}(t - nT_c), (3)$$

where  $V_{\mathrm{DAC,step}}$  is the DAC output increment per fold, and  $\mathrm{Rect}_{T_c}(t)$  denotes a unit-amplitude rectangular pulse of duration  $T_c$ , defined as

$$\operatorname{Rect}_{T_c}(t) = \begin{cases} 1, & 0 \le t < T_c, \\ 0, & \text{otherwise.} \end{cases}$$

(4)

The gain is configured to satisfy  $G_{\rm total}V_{\rm DAC,step}=2\lambda$ , so that each update of the folding-count register applies an exact  $2\lambda$  correction at the AFE summing node. Because the DAC holds the register value constant over each control-loop interval of duration  $T_c$ , the feedback voltage reduces to the simple piecewise-constant form

$$v_f(t) = 2\lambda C_f, \quad t \in [nT_c, (n+1)T_c),$$

where  $C_f$  denotes the current value of the folding-count register during that interval.

The folded waveform y(t) can be observed directly on an oscilloscope or digitized by the on-board ADC, producing discrete samples  $\hat{y}[k]$ , which represent the noisy measurements obtained in practice. These samples can be viewed in real time through the integrated logic analyzer (ILA) in Vivado. A Direct Recovery Module (DRM) within the FPGA reconstructs the signal by combining  $\hat{y}[k]$  with the folding count  $C_f$ .

The design features: (a) a dynamic-range extension of approximately  $\rho > 100$  achieved through precise fold-step control and a digital calibration system; (b) wideband, low-latency folding operation with a detection bandwidth exceeding 400 kHz; and (c) an integrated, extensible platform with

TABLE I: List of hardware components.

| Component      | Model number      | Make              |  |  |

|----------------|-------------------|-------------------|--|--|

| Comparator     | LT1715            | Analog Devices    |  |  |

| DAC            | AD9744            | Analog Devices    |  |  |

| PGA            | VCA824            | Texas Instruments |  |  |

| Adder / Buffer | OPA892            | Texas Instruments |  |  |

| Inverter       | ADA4522           | Analog Devices    |  |  |

| ADC            | AD9288            | Analog Devices    |  |  |

| FPGA           | ZYNQ 7000 XC7Z100 | Xilinx            |  |  |

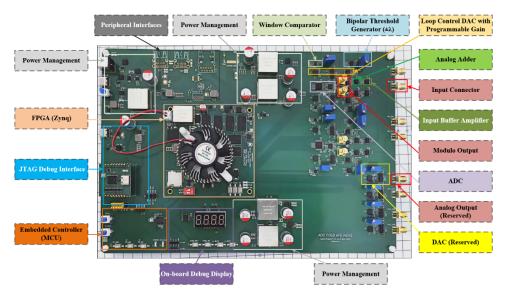

power management and peripheral interfaces supporting both stand-alone and multi-channel operation. Fig. 2 shows the four-channel PCB operating from a ±12 V supply, with one active channel highlighted and peripheral circuitry omitted for clarity. Table I summarizes the key hardware specifications.

#### B. Analog Front-End Design

The AFE of the proposed modulo ADC is designed to generate, detect, and correct threshold-crossing events with high precision and minimal latency. In mixed-signal folding architectures, two hardware factors primarily limit system performance: (a) the supply voltage range, threshold setting, and DAC resolution of the analog circuitry, which together determine the achievable folding depth; and (b) the total feedback-loop delay, which constrains the folding bandwidth. Each analog block in the proposed design is carefully selected and optimized to mitigate these limitations.

1) Precision Threshold Generation: The proposed design employs a precision bipolar threshold generator and a high-speed window comparator to ensure consistent switching behavior. The threshold voltage  $\lambda$  determines both the sensitivity of the folding process and the achievable folding depth, which scales inversely with  $\lambda$  for a fixed supply voltage:

Folding Depth

$$\propto rac{V_{

m supply}}{\lambda}.$$

With  $V_{\rm supply}=\pm 12~{\rm V}$ , smaller thresholds enable proportionally deeper folding but increase the risk of noise-induced false triggering, whereas larger thresholds improve noise immunity at the cost of reduced folding resolution. In this work, a nominal threshold range of  $[-0.5, +0.5]~{\rm V}$  is used, providing a practical trade-off between stability and folding depth. Specifically, for  $V_{\rm supply}=12~{\rm V}$  and a threshold of  $\lambda=0.1~{\rm V}$ , the theoretical maximum folding depth is  $\rho=120$  for an analog front-end fully rail-to-rail.

The threshold generator employs a zero-drift amplifier (ADA4522) and a precision voltage reference to generate symmetric  $\pm \lambda$  limits within the desired range. These components are chosen for their excellent thermal stability and low offset, maintaining voltage balance within  $\pm 0.2\%$  and effectively eliminating temperature-induced drift. Threshold detection is performed using a dual-channel high-speed comparator (LT1715) featuring a 4 ns propagation delay, 150 MHz bandwidth, and a 3.5 mV Schmitt-trigger hysteresis. The hysteresis suppresses chattering near  $\pm \lambda$ , while the matched dual channels ensure synchronized detection of both polarities.

Fig. 2: Photograph of the fabricated FPGA-based modulo ADC prototype. Key components of a single channel are labeled, including the FPGA-based digital loop controller, window comparator, bipolar threshold generator, Loop Control DAC with programmable gain stage, adder, and input buffer. Additional modules, such as the on-board ADC/DAC, power management, and peripheral interfaces, are integrated to enable stand-alone operation and future system expansion.

The comparator outputs are encoded as a 2-bit flag  $[B_1B_0] = [OVRN, OVRP]$ , where:

- 01: Input  $> +\lambda$  (positive over-range),

- 10: Input  $< -\lambda$  (negative over-range),

- **00**: Input within  $[-\lambda, +\lambda)$ .

2) Folding Feedback Generation and Depth Configuration: Conventional modulo-sampling front-ends rely on analog integrator—comparator loops [31], [32]. While simple, their limited bandwidth caps the folding rate, and drift or mismatch causes gain and threshold deviations. Because the folding step is hardware-fixed, calibration and tuning are difficult. This motivates a design with a fully programmable folding threshold.

Using (3), the feedback reduces within each clock interval to  $v_f(t) = G_{\rm total} V_{\rm DAC, step} C_f$ , and the folding step is fixed by  $G_{\rm total} V_{\rm DAC, step} = 2\lambda$ , so that changing  $\lambda$  only requires adjusting the gain. In the prototype design, the output path comprises a 14-bit AD9744 DAC (200 MSPS, with 1 bit reserved for the sign) whose current output is converted to voltage through a Thévenin-equivalent resistor network, followed by a programmable-gain amplifier (VCA824, adjustable  $G \in [0,2] \ {\rm V/V}$ ) and a fixed  $\times 10$  buffer stage. This configuration provides a total gain range of  $G_{\rm total} \in [0,20] \ {\rm V/V}$ , a bandwidth of  $200 \ {\rm MHz}$ , and a slew rate of  $500 \ {\rm V/\mu s}$ .

**Practical Limitation and Multi-Bit Step Design.** To enhance adaptability across different threshold settings  $\lambda$  while operating within the fixed supply voltage ( $\pm 12$  V), a programmable multi-bit update scheme is employed, where each fold corresponds to  $2^q$  DAC codes:

$$V_{\text{DAC.step}} = 2^q V_{\text{LSB}}.$$

(5)

where  $V_{\rm LSB} = V_{\rm FS}/2^{13}$  and  $V_{\rm FS}$  is the full-scale output voltage of the DAC. The parameter q provides real-time control over the effective DAC resolution, ensuring consistent folding

symmetry and balanced dynamic-range utilization. Following this design principle, the folding feedback is expressed as

$$v_f(t) = G_{\text{total}} 2^q V_{\text{LSB}} C_f. \tag{6}$$

The achievable range of bipolar folding depth is

$$C_f \in [-2^{13-q}, 2^{13-q} - 1]$$

(7)

For example, to achieve a dynamic-range expansion of  $\rho = 108$ , the system must satisfy  $\rho/2 < C_{f,\text{max}}$ . Choosing q = 7 gives  $C_{f,\text{max}} = 63$ , which meets this requirement. Although smaller values of q also satisfy the inequality, the largest admissible q is selected to ensure efficient utilization of the DAC resolution without wasting bits.

3) Wideband Summation: The real-time summation of the input and feedback signals is implemented using a unity-gain summing amplifier. With a 500 MHz gain-bandwidth product, 500 V/ $\mu$ s slew rate, and < 40 ns settling time, the OPA892 provides high linearity and wide bandwidth.

# C. Digital Loop Controller

The FPGA serves as the central digital controller that manages folding detection, counter updates, and folding voltage compensation under a unified clock domain.

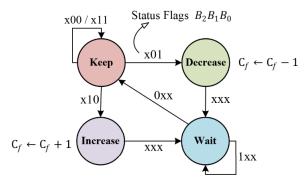

1) Folding Controller: The FPGA-implemented FSM (200 MHz) processes AFE comparator outputs to control the fold count  $C_f$ . It receives the 2-bit status  $[B_1B_0]$  from Section III-B1 and wait flag  $B_2$  (indicating settling completion).

The FSM (Fig. 3) operates through four states:

- **KEEP**: Hold  $C_f$ ,  $[B_2B_1B_0] = [x00]/[x11]$ , where x denotes a don't-care bit.

- **INCREASE**:  $C_f \leftarrow C_f + 1$  if  $[B_2B_1B_0] = [x10]$ .

- **DECREASE**: $C_f \leftarrow C_f 1$  if  $[B_2B_1B_0] = [x01]$ .

- WAIT: Keep  $C_f$  unchanged while  $[B_2 = 1]$ , allowing AFE settling and preventing oscillation.

Fig. 3: Control loop FSM: States **KEEP/WAIT** (hold  $C_f$ ), **INCREASE/DECREASE**  $(C_f \pm 1)$ . Transitions depend on  $[B_2B_1B_0]$  and "x" means don't-care.

- 2) System Clocking and Synchronization: To ensure precise synchronization among the ADC, Folding controller, and loop-control DAC, a unified clock network is implemented using an FPGA-integrated phase-locked loop (PLL). A 50 MHz reference is multiplied inside the FPGA to generate phase-aligned clocks for all subsystems. The ADC is driven by a 100 MHz clock advanced by 60° to align sampling with the settled feedback signal, while the controller and DAC operate on 200 MHz in-phase clocks. This configuration provides deterministic timing and stable high-speed operation for the modulo ADC system.

- 3) Direct Recovery Module: FPGA integrates a direct recovery module for on-chip reconstruction of the original input signal. It combines the stored folding count  $C_f$  with the sampled modulo signal  $\hat{y}[k]$ , acquired from the on-board ADC after the analog front end and thus subject to practical errors such as quantization, jitter, and offset. The recovered waveform is computed as

$$\tilde{g}[k] = \hat{y}[k] - 2\lambda C_f, \tag{8}$$

enabling real-time reconstruction and direct hardware verification of folding accuracy and dynamic-range expansion, which will be further analyzed in Section IV.

Comparison with existing work. Previous prototypes using STM32 or Teensy controllers relied on interrupt-driven routines, limited by software latency and sequential task execution [13], [36]. Microsecond-level response delays led to missed folding events and inaccurate counter updates at high input frequencies. The lack of a shared clock among the microcontroller unit (MCU), ADC, and DAC further caused phase misalignment and folding jitter. In contrast, the FPGA implements all control logic in parallel hardware pipelines, enabling clock-synchronous response and deterministic timing.

# D. Folding Calibration

During measurements, transient overshoot was observed at the folding edges, appearing as short voltage spikes beyond the threshold range. These spikes arise from abrupt voltage discontinuities in the folding process, which excite reflections along the feedback path. Because of the finite bandwidth of the amplifier and DAC, the reflected components are partially amplified, producing overshoot at the analog front end. This

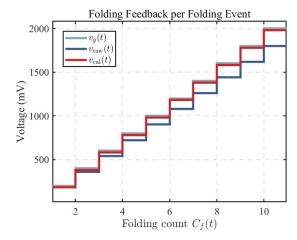

Fig. 4: Folding feedback voltage for  $\lambda=100~\mathrm{mV}$  with  $C_f$  varying from 1 to 10:  $v_f(t)=C_f200~\mathrm{mV}$  (ideal),  $v_{\mathrm{raw}}(t)=C_f180~\mathrm{mV}$  ( $\Delta V=20~\mathrm{mV}$ , uncalibrated), and  $v_{\mathrm{cal}}(t)=v_f(t)-20~\mathrm{mV}$  (calibrated).

overshoot distorts the modulo signal and consequently degrades the accuracy of subsequent signal reconstruction.

To suppress this effect, a controlled under-compensation strategy was introduced. In the ideal case, after  $C_f$  folding events, the folding feedback  $v_f(t)$  should follow (??). In practice, however, the actual feedback voltage is intentionally designed to be slightly smaller to suppress overshoot caused by abrupt voltage transitions:

$$v_{\text{raw}}(t) = C_f G_{\text{total}} 2^q V_{\text{LSB}} < v_f(t). \tag{9}$$

The feedback deviation is defined as

$$v_f(t) - v_{\text{raw}}(t) = C_f \, \Delta V,\tag{10}$$

where  $\Delta V = 2\lambda - G_{\rm total} \, 2^q V_{\rm LSB}$ . This difference grows linearly with the folding count. To compensate for the accumulated error, the FPGA adds a digital correction term  $(C_f - 1)\Delta V$ , resulting in a calibrated residual

$$v_{\rm cal}(t) = v_{\rm raw}(t) + (C_f - 1)\Delta V = v_f(t) - \Delta V,$$

(11)

which remains constant regardless of the number of folds.

Fig. 4 illustrates the digital calibration process of the controlled under-compensation scheme. In this simulation, the threshold is set to  $\lambda=100$  mV, yielding the ideal folding feedback  $v_f(t)=C_f\,2\lambda=C_f\,200$  mV. To suppress transient overshoot, the hardware feedback step is intentionally reduced to  $v_{\rm raw}(t)=C_f\,180$  mV, corresponding to an empirically chosen under-compensation margin of  $\Delta V=20$  mV. Without calibration, this discrepancy accumulates linearly with  $C_f$ . After digital correction, the calibrated feedback  $v_{\rm cal}(t)=v_f(t)-20$  mV closely matches the ideal response, ensuring stable folding across varying  $C_f$ .

# E. Bandwidth Limitation

The folding bandwidth is limited by both analog and digital delays. On the analog side, the finite slew rates of the DAC and summing amplifier slow the folding transition, whereas the comparator's 150 MHz bandwidth is sufficient. Digitally, the FPGA response time determines how quickly a correction

Fig. 5: Timing-limited folding for a  $610\,\mathrm{kHz}$  triangular input with threshold  $\lambda=0.36\,\mathrm{V}$ . The full trace is shown (left) and a zoom near the threshold crossing is shown (right). Traces include the input (purple), modulo output (red), OVRP/OVRN flags, DAC step, fold counter, and the  $200\,\mathrm{MHz}$  clock. Loop delay results in an overfold below  $-\lambda$ , causing spurious OVRN and counter errors.

can be applied; at high input slew rates, the loop reacts too slowly to keep the signal within the threshold range.

To characterize these limits, a 610 kHz triangular input with  $\lambda = 0.36 \,\mathrm{V}$  was applied, and internal traces were captured (Fig. 5). The signals include the input, modulo output, OVRP/OVRN flags, the DAC update step  $(-2^9 = -512)$ codes), the fold counter  $C_f$ , and the  $200\,\mathrm{MHz}$  clock. The loop delay  $T_F$ , defined as the interval between the rising and falling edges of OVRP, is five FPGA cycles (25 ns). There is also an additional latency  $T_{ADC}$  between the OVRP falling edge and the actual modulo transition. At 610 kHz, the combined delay  $T_F + T_{ADC}$  allows the input to continue rising after OVRP assertion, introducing a mismatch between the ideal and measured folding edges. Because the transition is no longer sharp relative to the input period, the delayed correction  $(C_f \leftarrow C_f - 1)$  arrives after the slope reversal, driving the modulo output below  $-\lambda$ . This *over-fold* corrupts the fold count and induces oscillation.

#### IV. REAL EXPERIMENTS

This section presents a comprehensive evaluation of the proposed modulo ADC system, including comparisons with a conventional ADC, verification of its SoC-like signal acquisition capability, and experimental validation of existing recovery algorithms using real folded hardware data.

# A. Comparison with a Conventional ADC

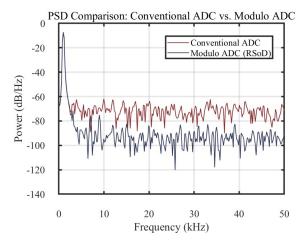

Following [9], [31], [34], the folded outputs were recorded using a Tektronix TDS1012C-EDU 8-bit oscilloscope. The on-board ADC was bypassed to allow software-controlled oversampling and to avoid ADC-induced gain errors during MATLAB-based reconstruction and analysis.

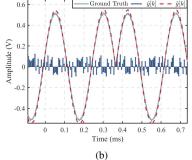

In this experiment, the conventional ADC operated at full scale, with its threshold set equal to the maximum input amplitude to ensure no clipping under nominal conditions. For comparison, the modulo ADC was configured with a threshold of  $\lambda=0.1\,\mathrm{V}$  and a dynamic-range factor of  $\rho=108$ , using a  $1\,\mathrm{kHz}$  input. The RSoD recovery method [11] was adopted for reconstruction. Fig. 6 shows the corresponding power spectral

Fig. 6: Power spectral density (PSD) of the recovered  $1 \, \text{kHz}$  sinusoid with a resolution of b = 7 bits/sample.

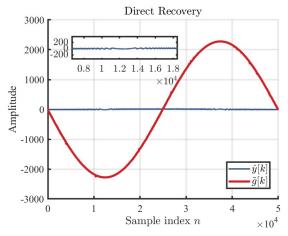

Fig. 7: Measured modulo signal  $\hat{y}[k]$  and directly recovered waveform  $\tilde{g}[k]$  at  $\rho = 91.56$  with a modulo threshold of 0.1 V.

density (PSD) with ADC resolution b=7. The conventional ADC exhibits a higher noise floor, whereas the modulo ADC with RSoD reconstruction reduces it by approximately  $20\,\mathrm{dB}$  over the  $5\,\mathrm{kHz}$  to  $45\,\mathrm{kHz}$  band, demonstrating improved noise suppression and reconstruction fidelity.

#### B. On-Board Direct Signal Recovery

This experiment aims to verify the direct on-board recovery capability of the proposed modulo ADC system. The folded waveform was acquired by the on-board AD9288 ADC and stored in the FPGA memory in real time. As shown in Fig. 7, the modulo threshold was set to  $\pm 0.1$  V, corresponding to  $\pm 25$  in digital representation.

At  $\rho=91.56$ , the reconstructed signal achieves a signal-to-noise and distortion ratio (SINAD) of 44 dB, which is nearly identical to the native 46 dB SINAD of the AD9288 operating within its linear range. This demonstrates that the proposed modulo ADC architecture preserves signal integrity while effectively extending the dynamic range far beyond that of the original ADC. The close SINAD consistency confirms the precise timing alignment, accurate feedback calibration,

TABLE II: Performance comparison for basic test signals (sine and periodic sinc) under various  $\rho$ , bandwidths B, and repetition frequencies  $f_m$ , with  $\lambda = 0.1$  V. Metrics: OF (dark red = smallest) and SNR<sub>r</sub> (bold = highest).

| Input Signal Type | Input Signal Parameters |                        | RSoD [11] |                               | ITER-SIS [9] |                               | LASSO-B <sup>2</sup> R <sup>2</sup> [23] |                               | USLSE [10] |             |

|-------------------|-------------------------|------------------------|-----------|-------------------------------|--------------|-------------------------------|------------------------------------------|-------------------------------|------------|-------------|

|                   | ρ                       | $f_m$ (kHz)            | OF        | $SNR_r(dB)$                   | OF           | $SNR_r(dB)$                   | OF                                       | $SNR_r(dB)$                   | OF         | $SNR_r(dB)$ |

|                   | 2.84                    | 100                    | 6.49      | 21.62                         | 11.11        | 29.44                         | 8.33                                     | 23.38                         | 7.04       | 22.44       |

| Sine              | 22.2                    | 10                     | 17.86     | 22.57                         | 71.42        | 20.24                         | 71.42                                    | 22.30                         | 62.5       | 20.54       |

|                   | 102                     | 1                      | 41.67     | 23.37                         | 62.5         | 6.37                          | 50                                       | 0.49                          | 50         | 0.33        |

| Sinc              | ρ                       | $B, f_m \text{ (kHz)}$ | OF        | $\mathrm{SNR}_r(\mathrm{dB})$ | OF           | $\mathrm{SNR}_r(\mathrm{dB})$ | OF                                       | $\mathrm{SNR}_r(\mathrm{dB})$ | OF         | $SNR_r(dB)$ |

|                   | 3.24                    | 410, 23 (kHz)          | 3.81      | 24.31                         | 2.97         | 23.86                         | 3.93                                     | 22.22                         | 3.48       | 21.76       |

| Sinc              | 9.16                    | 99, 5 (kHz)            | 7.01      | 23.09                         | 11.48        | 27.79                         | 12.63                                    | 22.78                         | 12.63      | 24.31       |

|                   | 29.80                   | 18, 1 (kHz)            | 15.43     | 16.43                         | 46.30        | 17.13                         | 46.30                                    | 16.07                         | 46.30      | 13.47       |

TABLE III: Performance comparison of RSoD [11], ITER-SIS [9], LASSO-B<sup>2</sup>R<sup>2</sup> [23], and USLSE [10] using communication-type test signals with different B and  $\rho$ . Metrics: OF (dark red = smallest) and SNR<sub>T</sub> (bold = highest).

| Input Signal Parameters |       | RSoD [11] |       | ITER-SIS [9] |       | LASSO       | D-B <sup>2</sup> R <sup>2</sup> [23] | USLSE [10]  |       |             |

|-------------------------|-------|-----------|-------|--------------|-------|-------------|--------------------------------------|-------------|-------|-------------|

| Type                    | ρ     | B (kHz)   | OF    | $SNR_r(dB)$  | OF    | $SNR_r(dB)$ | OF                                   | $SNR_r(dB)$ | OF    | $SNR_r(dB)$ |

| QAM                     | 10.40 | 4         | 12.50 | 28.06        | 25.00 | 34.70       | 25.00                                | 23.10       | 25.00 | 20.88       |

| BPSK                    | 5.20  | 2         | 17.86 | 23.44        | 22.73 | 33.64       | 22.73                                | 23.39       | 19.23 | 23.55       |

| FSK                     | 8.00  | 2         | 20.83 | 23.24        | 20.83 | 33.76       | 20.83                                | 22.63       | 41.67 | 21.48       |

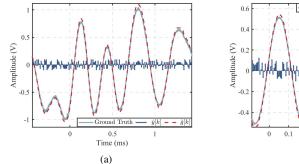

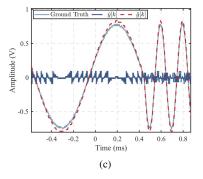

Fig. 8: Reconstruction results of communication signals using RSoD [11]: (a) QAM, (b) BPSK, and (c) FSK.

and high quality of the folded signal, validating the robustness of the overall hardware design.

## C. Comparison with Existing Recovery Algorithm

We benchmark against RSoD [11], ITER-SIS [9], LASSO- $B^2R^2$  [23] and USLSE [10] under the reconstructed signal-to-noise ratio (SNR<sub>r</sub>):

$$SNR_r = 10 \log_{10} \frac{\sum_k |g[k]|^2}{\sum_k g[k] - \tilde{g}[k]|^2}.$$

(12)

The ground truth and the folded output were recorded using a Tektronix TDS,1012C-EDU 8-bit oscilloscope.

1) Basic Test Signals: We tested the existing algorithms using basic signals, including single-tone sine waves and periodic bandlimited sinc inputs, each configured with different dynamic ranges  $\rho$ , signal frequencies  $f_m$ , and main-lobe bandwidths B. The performance metrics are the oversampling factor (OF), defined as OF =  $f_s/f_{\rm Nyq}$ , and SNR $_r$  defined in (12). Here,  $f_{\rm Nyq}$  denotes the Nyquist frequency. The modulo ADC threshold  $\lambda$  is fixed at  $\lambda=0.1~\rm V$ .

As summarized in Table II, at low dynamic ranges ( $\rho < 10$ ), all methods yield SNR $_r$  above 20 dB. As  $\rho$  increases, ITER-SIS and LASSO–B $^2$ R $^2$  require significantly larger sampling factors to sustain reconstruction quality, whereas RSoD preserves similar accuracy with up to threefold reduction in OF. USLSE exhibits stable but moderate performance across all cases. At high dynamic ranges ( $\rho > 100$ ), RSoD maintains SNR $_r$  around 23 dB, while iterative and optimization-based approaches degrade rapidly.

2) Communication-Signal Experiments: To further evaluate the reconstruction performance of the proposed system under practical signal conditions, we tested several typical communication-modulated waveforms, including quadrature amplitude modulation (QAM), binary phase-shift keying (BPSK), and frequency-shift keying (FSK) signals. As summarized in Table III, RSoD exhibits the smallest oversampling factors across all QAM and BPSK test cases while maintaining comparable reconstruction quality to the more computationally intensive ITER-SIS and LASSO-B<sup>2</sup>R<sup>2</sup> algorithms. Fig. 8 presents the reconstruction results of the communication-signal experiments using the RSoD.

#### V. CONCLUSION AND FUTURE WORK

This paper presents a mixed-signal FPGA-based modulo ADC platform that achieves more than a 100-fold dynamic-range expansion within a 400 kHz bandwidth and incorporates an under-compensation calibration scheme. The on-board direct reconstruction demonstrates that the proposed design achieves a SINAD of 44 dB, comparable to a conventional ADC, while extending the measurable amplitude range by two orders of magnitude. Benchmark experiments using both basic and communication signals further show that all evaluated algorithms perform similarly at moderate  $\rho$ , whereas only RSoD maintains reliable reconstruction at large  $\rho$ .

Future work will focus on improving loop bandwidth and latency control to support higher-frequency inputs. The multiple on-board modulo ADC channels will also be exploited to enable synchronized multi-channel acquisition and to further evaluate multi-channel recovery algorithms.

#### REFERENCES

- S. Konwar and B. Datta Sahoo, "Johnson counter-based multiphase generation for VCO-based ADC for direct digitization of low amplitude sensor signals," *IEEE Transactions on Instrumentation and Measure*ment, vol. 72, pp. 1–4, 2023.

- [2] S. B. Nair, N. Suresh, A. C. Sreekantan, and S. Kaarthik, "An efficient digitizer for measurement of low-magnitude currents with wide span," *IEEE Transactions on Instrumentation and Measurement*, vol. 71, pp. 1–10, 2022.

- [3] R. Koma, M. Fujiwara, S. Kimura, and N. Yoshimoto, "Wide dynamic range reception of TDM-based DCO-OFDM signals using optical domain power equalization and symmetrical clipping techniques," *Journal* of *Lightwave Technology*, vol. 33, no. 8, pp. 1623–1629, 2015.

- [4] Y. M. Jo, D. H. Woo, S. G. Kang, and H. C. Lee, "Very wide dynamic range roic with pixel-level ADC for SWIR FPAs," *IEEE Sensors Journal*, vol. 16, no. 19, pp. 7227–7233, 2016.

- [5] G. Guarnieri, S. Marsi, and G. Ramponi, "High dynamic range image display with halo and clipping prevention," *IEEE Transactions on Image Processing*, vol. 20, no. 5, pp. 1351–1362, 2011.

- [6] A. Bhandari, F. Krahmer, and R. Raskar, "On unlimited sampling," in 2017 International Conference on Sampling Theory and Applications (SampTA), 2017, pp. 31–35.

- [7] —, "Unlimited sampling of sparse signals," in 2018 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2018, pp. 4569–4573.

- [8] —, "On unlimited sampling and reconstruction," *IEEE Transactions on Signal Processing*, vol. 69, pp. 3827–3839, 2020.

- [9] R. Guo and A. Bhandari, "ITER-SIS: Robust unlimited sampling via iterative signal sieving," in ICASSP 2023 - 2023 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2023, pp. 1–5.

- [10] Q. Zhang, J. Zhu, F. Qu, and D. W. Soh, "Line spectral estimation via unlimited sampling," *IEEE Transactions on Aerospace and Electronic Systems*, vol. 60, no. 5, pp. 7214–7231, 2024.

- [11] W. Yan, Z. Li, L. Gan, H. Liu, and G. Li, "Difference-based recovery for modulo sampling: Tightened bounds and robustness guarantees," 2025. [Online]. Available: https://arxiv.org/abs/2509.12971

- [12] Y. Zhu, R. Guo, and A. Bhandari, "Ironing the modulo folds: Unlimited sensing with 100x bandwidth expansion," in 15th International Conference on Sampling Theory and Applications, 2025. [Online]. Available: https://openreview.net/forum?id=U54f3iAQ36

- [13] J. Zhu, J. Ma, Z. Liu, F. Qu, Z. Zhu, and Q. Zhang, "A modulo sampling hardware prototype and reconstruction algorithms evaluation," *IEEE Transactions on Instrumentation and Measurement*, vol. 74, pp. 1–11, 2025.

- [14] R. Bolaños-Pérez, J. M. Rocha-Pérez, A. Díaz-Sánchez, J. Ramirez-Angulo, and E. Tlelo-Cuautle, "CMOS analog AGC for biomedical applications," *Electronics*, vol. 9, no. 5, p. 878, 2020.

- [15] M. Rovetta, J. F. R. Baggio, and R. Moraes, "An automatic gain control circuit to improve ECG acquisition," *Research on Biomedical Engineering*, vol. 33, no. 4, pp. 378–389, 2017.

- [16] L. Cai, X. Song, Z. Lu, X.-P. Yu, K.-S. Yeo, J.-M. Chen, and B. K. Thangarasu, "A linear-in-decibel automatic gain control amplifier with dual mode continuous gain tuning," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 70, no. 7, pp. 2752–2761, 2023.

- [17] T. Johnson and S. P. Stapleton, "RF class-D amplification with bandpass sigma-delta modulator drive signals," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 12, pp. 2507–2520, 2006.

- [18] Z. Tan, C.-H. Chen, Y. Chae, and G. C. Temes, "Incremental delta-sigma ADCs: A tutorial review," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 67, no. 12, pp. 4161–4173, 2020.

- [19] R. H. Walden, "Analog-to-digital converter survey and analysis," *IEEE Journal on Selected Areas in Communications*, vol. 17, no. 4, pp. 539–550, 1999.

- [20] X. Tang, J. Liu, Y. Shen, S. Li, L. Shen, A. Sanyal, K. Ragab, and N. Sun, "Low-power SAR ADC design: Overview and survey of stateof-the-art techniques," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 69, no. 6, pp. 2249–2262, 2022.

- [21] S.-C. Kuo, J.-S. Huang, Y.-C. Huang, C.-W. Kao, C.-W. Hsu, and C.-H. Chen, "A multi-step incremental analog-to-digital converter with a single opamp and two-capacitor SAR extended counting," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 7, pp. 2890–2899, 2021.

- [22] D.-J. Chang, W. Kim, M.-J. Seo, H.-K. Hong, and S.-T. Ryu, "Normalized-full-scale-referencing digital-domain linearity calibration for SAR ADC," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 2, pp. 322–332, 2017.

- [23] S. B. Shah, S. Mulleti, and Y. C. Eldar, "LASSO-based fast residual recovery for modulo sampling," in ICASSP 2023 - 2023 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2023, pp. 1–5.

- [24] L. Gan and H. Liu, "High dynamic range sensing using multi-channel modulo samplers," in 2020 IEEE 11th Sensor Array and Multichannel Signal Processing Workshop (SAM), 2020, pp. 1–5.

- [25] R. Guo and A. Bhandari, "Unlimited sampling of fri signals independent of sampling rate," in ICASSP 2023 - 2023 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2023, pp. 1–5.

- [26] R. Guo, Y. Zhu, and A. Bhandari, "Sub-nyquist USF spectral estimation: k frequencies with 6k + 4 modulo samples," *IEEE Transactions on Signal Processing*, vol. 72, pp. 5065–5076, 2024.

- [27] V. Pavlíček, R. Guo, and A. Bhandari, "Bits, channels, frequencies and unlimited sensing: Pushing the limits of sub-Nyquist prony," in 2024 32nd European Signal Processing Conference (EUSIPCO), 2024, pp. 2462–2466.

- [28] D. Florescu, "Multichannel modulo sampling with unlimited noise," in ICASSP 2025 - 2025 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2025, pp. 1–5.

- [29] N. I. Bernardo, S. B. Shah, and Y. C. Eldar, "Modulo sampling: Performance guarantees in the presence of quantization," *IEEE Transactions on Signal Processing*, pp. 1–14, 2025.

- [30] W. Yan, L. Gan, S. Hu, and H. Liu, "Towards optimized multi-channel modulo-ADCs: Moduli selection strategies and bit depth analysis," in ICASSP 2024 - 2024 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2024, pp. 9496–9500.

- [31] A. Bhandari, F. Krahmer, and T. Poskitt, "Unlimited sampling from theory to practice: Fourier-prony recovery and prototype ADC," *IEEE Transactions on Signal Processing*, vol. 70, pp. 1131–1141, 2022.

- [32] D. Florescu, F. Krahmer, and A. Bhandari, "The surprising benefits of hysteresis in unlimited sampling: Theory, algorithms and experiments," *IEEE Transactions on Signal Processing*, vol. 70, pp. 616–630, 2022.

- [33] D. Florescu and A. Bhandari, "Unlimited sampling with local averages," in Proc. IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), 2022, pp. 5742–5746.

- [34] Y. Zhu and A. Bhandari, "Unleashing dynamic range and resolution in unlimited sensing framework via novel hardware," in 2024 IEEE SENSORS, 2024, pp. 1–4.

- [35] R. Guo and A. Bhandari, "Bandwidth expansion in modulo ADCs and USF: Theory, algorithms and hardware experiments," 10 2025.

- [36] S. Mulleti, E. Reznitskiy, S. Savariego, M. Namer, N. Glazer, and Y. C. Eldar, "A hardware prototype of wideband high-dynamic range analog-to-digital converter," *IET Circuits, Devices & Systems*, vol. 17, no. 4, pp. 181–192, 2023. [Online]. Available: https://onlinelibrary.wiley.com/doi/abs/10.1049/cds2.12156