# Aquas: Enhancing Domain Specialization through Holistic Hardware-Software Co-Optimization based on MLIR

Yuyang Zou, Youwei Xiao, Yansong Xu, Chenyun Yin, Yuhao Luo, Yitian Sun, Ruifan Xu, Renze Chen and Yun Liang Peking University Beijing, China

## **Abstract**

Application-Specific Instruction-Set Processors (ASIPs) built on the RISC-V architecture offer specialization opportunities for various applications. However, existing frameworks from the open-source RISC-V ecosystem suffer from limited performance due to restricted hardware synthesis and rigid compiler support. To address these challenges, we introduce Aquas, a holistic hardware-software codesign framework built upon MLIR. Aquas enhances ASIP synthesis with fast memory access capability via a burst DMA engine and advanced high-level synthesis (HLS) optimizations. On the compiler side, we propose an e-graph based retargetable approach with a novel matching engine for efficient instruction matching. Evaluation demonstrates up to 9.27× speedup on real-world workloads, including point cloud processing and LLM inference.

## 1 Introduction

Edge computing is increasingly driving the need for Application-Specific Instruction-Set Processors (ASIPs), which accelerate applications through hardware specialization while maintaining programmability and generality with instruction set architecture extensions (ISAXs). RISC-V [23]-based ASIPs have been widely adopted in domains across signal processing [17], machine learning inference [2, 27], cryptography [5, 12, 15], and computer graphics [19, 20]. The design of high-performance ASIPs presents a significant hardware-software co-design challenge, demanding a framework that can both generate specialized hardware and adapt software to leverage it effectively.

Despite recent advances [14, 25], creating a truly holistic ASIP design framework requires overcoming three fundamental challenges. First, a powerful and agile synthesis framework is needed to generate efficient hardware for diverse workloads. Commercial tools like Synopsys ASIP Designer [18] offer fine-grained control but rely on low-level languages such as nML [21], requiring significant expertise and manual effort that hinders agility. Research frameworks have their own limitations, too. Longnail [14] provides a high-level synthesis (HLS) based hardware synthesis flow but lacks expressiveness for complex control patterns or custom memories, confining it to simple ISAXs. APS [25] exhibits performance constraints due to microarchitectural limits, such as memory bandwidth, and a lack of crucial synthesis optimizations—such as array partitioning and loop transforms common in HLS frameworks [1, 10, 26, 28]—to generate highly parallel designs.

Second, a robustly retargetable compiler is essential to automatically leverage these complex ISAXs. The RISC-V ecosystem exhibits tremendous diversity in instruction backends, with countless instruction extensions featuring varying semantics and computational patterns. However, current compiler technologies remain

primitive and lack true retargetability—unable to systematically adapt to this wide variety of custom backends. Longnail [14] offers no compiler support, and APS [25] provides only basic pattern matching, lacking the sophisticated program transformation capabilities required. Even commercial tools [18] require users to write C-code in the exact way that exposes the ISAX pattern, or use intrinsic explicitly. The fused semantics of modern ISAXs, which often contain internal loops and complex memory access patterns, render trivial pattern-matching techniques insufficient. Furthermore, application code must be structurally transformed to align with the ISAX, yet existing frameworks fall short.

Third, the hardware and software design flows should be integrated within a unified, holistic infrastructure. Separate toolchains prevent iterative co-design and optimization. While Longnail and HLS tools like HECTOR [26] and Dynamatic [10] use the MLIR [11] infrastructure, they do not integrate a complete compiler retargeting flow, thereby missing the opportunity to leverage a unified infrastructure for comprehensive co-optimization.

In this work, we present Aquas, a holistic, MLIR-based framework for automated hardware-software co-design that generates optimized ASIPs and their corresponding compiler support. To overcome hardware synthesis limitations, Aquas provides a complete flow to specify and generate ISAXs with a burst-capable Direct Memory Access (DMA) interface, eliminating memory bottlenecks. By leveraging MLIR's optimization infrastructure, our framework applies advanced HLS techniques to generate highly parallel hardware that fully exploits data-level parallelism. For the compiler, Aquas proposes a novel and robust retargetable approach through the seamless interaction with the e-graph [24] data structure. E-graph supports joint application of algebraic and controlflow rewrites while compactly maintaining the space of possible program variants to expose ISAX offloading opportunities. We propose a hybrid skeleton-components matching engine to effectively map application patterns to complex ISAXs. Finally, Aquas unifies the entire ASIP design flow-from hardware specification through synthesis to compiler retargeting-within the MLIR infrastructure. This unified approach enables seamless co-optimization across the hardware-software boundary and facilitates agile design iteration.

Our contributions are as follows:

- We introduce Aquas, a holistic open-source framework for unified ASIP hardware-software co-design built upon MLIR.

- We propose an enhanced synthesis flow with burst-capable DMA, memory subsystem support, and advanced HLS optimizations that unleash the performance potential of ASIP ISAXs.

- We design a novel e-graph-based retargetable compiler for automatic adoption of ISAXs, featuring a skeleton-component matching engine to map application code to complex instructions.

1

We demonstrate using two real-world case studies, point-cloud analysis and CPU large language model (LLM) inference. Compared to the baseline Rocket core, *Aquas* achieves up to 9.27× and 7.60× speedup on individual kernels, and 1.96× and 2.09× end-to-end speedup, respectively, with less than 34.41% area overhead on end-to-end. Against the high-performance BOOMv3 out-of-order core, it achieves competitive performance while saving 67% chip area, showcasing its area efficiency for domain-specific workloads.

#### 2 Preliminaries

# 2.1 Architectural Description Languages

Architecture Description Languages (ADLs) are widely adopted to specify the functional behavior, structural organization, and instruction set of custom processor instructions. Related works proposes languages including nML [21], CodAL [6], CoreDSL [14] and CADL [25]. Among them, CADL is designed to simplify ISAX customization by focusing on a high-level, untimed behavioral description. CADL defines an ISAX's encoding, internal state, and behavioral functionality. CADL also supports a set of interface operations that describe ISAXs' interactions with the base processor.

## 2.2 MLIR Infrastructure and E-graph

MLIR [11] is a modular compiler infrastructure for defining intermediate representations at different abstractions and constructing analysis and transformations for optimizations at the appropriate abstractions. Built on top of MLIR, CIRCT [7] provides *dialects* specified for hardware design. Hardware synthesis is a process of lowering high-level abstractions into low-level designs, and MLIR's multi-level ecosystem provides affinitive support. High-level synthesis (HLS) frameworks HECTOR [26] and Dynamatic [10], as well as ASIP synthesis framework Longnail [14], are built with MLIR. Given ASIP customization's requirements for combining hardware synthesis and compiler support, MLIR demonstrates exceptional adaptability in building a holistic toolchain.

An e-graph [31] maintains a congruence-closed equivalence relation over expression nodes, inducing a partition into equivalence classes (e-classes) and enabling non-destructive rewriting and costbased extraction [4, 29]. An e-node is a function symbol applied to child identifiers, where each identifier denotes a child e-class. An eclass is the equivalence class of e-nodes under that relation, storing all members currently known to be semantically identical. The basic e-graph operations include e-matching that finds the given pattern in an e-graph, union that manipulates e-classes, and extraction that finds the best expression from the *e-graph*. In step ② of Figure 3, the dotted boxes represent e-classes, which group e-nodes that are considered equivalent. Though recent efforts [13, 30] have explored integrating e-graphs with MLIR, they remain fundamentally segmented, where MLIR transforms are still applied in a destructive manner. We need a new integration mechanism to tightly couple MLIR and *e-graph* to expose all opportunities of ISAX offloading.

#### 3 Unified Toolchain

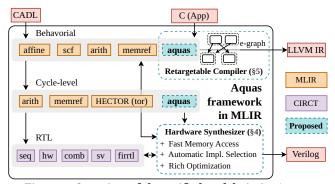

Aquas contributes a unified toolchain for agile, flexible, and fully optimized ASIP design. As shown in Figure 1, Aquas makes full use of MLIR's existing dialects and introduces new abstractions

Figure 1: Overview of the unified toolchain in Aquas.

to build the cross-level flow for both the hardware synthesis and compiler support. Specifically, Aquas introduces the aquas dialect, which extends existing features of [25] with operations for fast memory access and optimization directives (Section 4.1). At the microarchitecture level, Aquas introduces a burst DMA engine based on TileLink-UH for data transfers without host processor involvement, as well as a hierarchically organized scratchpad memory (Section 4.2). The synthesis flow (Section 4.3) lowers the behavioral description to the cycle-level. Aquas collectively leverages MLIR's analysis and transformation capabilities for parallelism optimization and utilizes CIRCT to efficiently generate transactional hardware with dynamic execution pipelines. For automatic ISAX offloading, Aquas introduces a novel, retargetable compilation flow (Section 5) based on the tight interaction between MLIR and e-graph. We propose a new rewrite application flow and the skeleton-component pattern matching mechanism to fully expose and exploit ISAXs' acceleration opportunities.

## 4 Synthesis Framework

In this section, we describe how *Aquas* synthesizes efficient hardware. We first design blockwise memory operations and synthesis directives based on CADL language [25]. We then address memory bottlenecks through a memory subsystem with burst-capable DMA and banked scratchpad memory. Finally, we outline the synthesis flow for generating optimized hardware.

# 4.1 Language Design for Optimizations

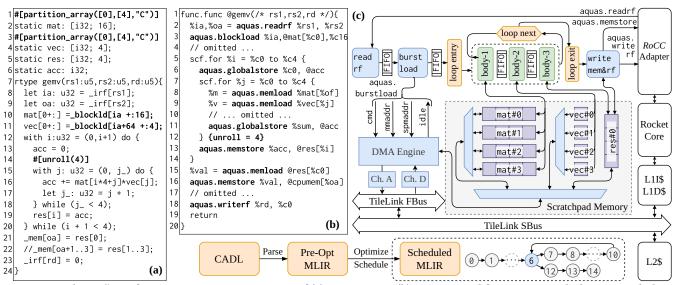

Aquas introduces blockwise memory access operations and dedicated synthesis directives to simplify the specification of optimized ISAXs. These extensions guide the synthesizer to implement fast data transfers and exploit data-level parallelism. Figure 2 presents the synthesis flow from specific ISAX description to efficient hardware using Aquas.

Blockwise Memory Access. We introduce \_blockld and \_blockst operations, as shown in line 10-11 of Figure 2(a), representing blockwise memory transfers. These operations specify the start address of the main memory, transfer length (in element count), and the target array, providing an explicit, implementation-independent interface for large data transfers. During synthesis, these operations are lowered to appropriate memory access mechanisms based on transfer size, enabling the backend to select combinations of single-shot accesses and burst DMA transfers.

Figure 2: Synthesis flow of gemv using Aquas. It consists of (a) CADL input, (b) MLIR parsed from CADL including aquas dialect, and (c) synthesized hardware including DMA engine, scratchpad memory, and main execution pipeline.

*Optimization Directives.* To exploit data-level parallelism enabled by efficient memory access, we introduce optimization directives to guide hardware synthesis. Available directives include array partitioning, loop unrolling, and loop pipelining. In Figure 2(a), the fully unrolled inner loop (line 14) enables parallel computation of four multiply-accumulate operations. To support this access pattern, both mat and vec arrays are cyclically partitioned into four banks (lines 1-4), allowing simultaneous access.

Aquas's frontend parses the ISAX description into MLIR, leveraging standard dialects such as scf, memref, and arith, while introducing a custom dialect, aquas, for processor interaction operations. As shown in Figure 2(b), read and write to the register file are lowered to aquas.readrf and aquas.writerf, while single-shot memory store and block memory load are lowered to aquas.memstore and aquas.blockload, respectively. Directives such as unroll marked on the inner loop are translated into MLIR attributes attached to corresponding operations (line 12).

## 4.2 Fast Memory Access via DMA

To generate efficient ISAXs that exploit data-level parallelism and avoid repeated main memory accesses, *Aquas* synthesizes static arrays into hierarchically organized scratchpad memory modules. These modules are structurally subdivided into independent physical banks guided by array partition directives.

Burst-Capable DMA Engine. Aquas incorporates a burst-capable DMA engine that enables fast data transfers between the banked scratchpad and main memory, significantly outperforming single-shot memory access for large data blocks. As shown in Figure 2(c), the DMA engine connects directly to the Frontend Bus of Rocket-Tile via TileLink-UH, with cache coherency handled automatically. The DMA also exposes control signals directly to the ISAX module. This hardware-driven control mechanism bypasses processor intervention and eliminates the software configuration overhead found in traditional memory-mapped DMA. This DMA engine provides

a high-throughput alternative to the RoCC memory port. In the Chipyard SoC, we characterize the parameters of both methods: the RoCC port (used for single-shot access) typically requires 2–3 cycles per element, whereas the burst DMA, after an initial latency of 15 cycles for loads and 5 for stores, achieves a sustained throughput of one element per cycle at full bus width.

Partition-Aware DMA Access. The DMA engine accesses the banked scratchpad through a unified top port with address mapping logic that decodes each global address to bank selection and local bank offset based on the partitioning scheme. When the 64-bit DMA bus width exceeds individual bank widths, each DMA word is distributed across multiple physical banks in a single cycle. In Figure 2(c), the four-way partitioned mat allows each DMA word to deliver two consecutive 32-bit elements across adjacent banks in a single cycle. When partitioning is not explicitly specified, the synthesis flow can automatically partition arrays to match the DMA bus width, eliminating width mismatches. This avoids unnecessary FIFOs and additional clock cycles for data width conversion.

# 4.3 Hardware Synthesis Flow

During hardware synthesis, *Aquas* first parses our description to MLIR, then applies implementation selection, optimization, and scheduling guided by directives, and finally lowers to transactional hardware

Implementation Selection for Blockwise Memory Operations. The implementation-independent blockload and blockstore operations in aquas dialect are lowered to either single-shot memory accesses (memload / memstore) or burst DMA transfers (burstload / burststore) based on transfer size. The selection involves a crucial trade-off: single-shot access offers lower initial latency for small transfers but is limited by its per-transaction handshake overhead on large blocks, whereas burst access provides high throughput but is penalized by a substantial fixed startup overhead on minimal

data transfers. Determining the optimal combination is therefore essential.

Given arbitrary divisibility of data blocks and padding for segments under the burst length  $\mathcal{B}=\{2^l\mid l\in\mathbb{N},$  BusWidth  $\leq 2^l\leq$  CachelineWidth $\}$ , we partition the total required data transfer D into  $x_{bur,b}$  burst transfers of size  $b\in\mathcal{B}$  and  $x_{ss}$  single-shot transfers of fixed data size  $d_{ss}$ . We denote the latency of each burst transfer of size b as  $t_{bur}(b)$  (whose characteristics are described in Section 4.2), and the latency of each single-shot transfer as  $t_{ss}$ . The task of minimizing overall latency by finding the optimal partition is thus formulated as an Integer Linear Programming (ILP) optimization problem:

$$\begin{aligned} & \min_{x_{bur,b},x_{Ss}} & & \sum_{b \in \mathcal{B}} t_{bur}(b) \cdot x_{bur,b} + t_{ss} \cdot x_{ss} \\ & \text{s.t.} & & \sum_{b \in \mathcal{B}} b \cdot x_{bur,b} + d_{ss} \cdot x_{ss} \geq D, \quad x_{bur,b}, x_{ss} \in \mathbb{N}_0 \end{aligned}$$

We solve this ILP to determine the optimal burst and single-shot combination for each block operation.

*Optimizations and Scheduling.* Loops are raised from scf to affine dialect to enable aggressive transformations. We apply optimization passes leveraging the HECTOR[26] for loop unrolling, pipelining, and array partitioning. For scheduling, *Aquas* formulates constraints, including ISAX-core interaction latencies and memory attributes, in a modulo scheduling problem.

Dynamic Pipeline Elaboration. The scheduled MLIR is lowered to a dynamic pipeline architecture following transactional [9] semantics. Each pipeline stage corresponds to a transaction that fires when dependencies are satisfied, with inter-stage FIFO queues providing latency-insensitive composition. In Figure 2(c), arithmetic operations map to firrtl combinational logic, while aquas dialect operations like aquas.burstload and aquas.readrf become transactional calls to DMA and RoCC adapters with valid-ready handshakes, respectively. Loops are decomposed into specialized transactions: loop entry initializes variables, loop body stages execute operations, and loop next routes control flow based on continuation conditions. The resulting transactional hardware is then lowered to FIRRTL through an MLIR pass we implement, which resolves resource conflicts by automatic arbitration logic insertion. Finally, FIRRTL is synthesized into Verilog by CIRCT.

## 5 Retargetable Compiler

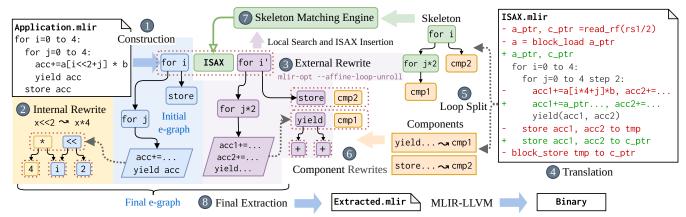

We propose a retargetable compilation flow for ASIP, as shown in Figure 3. We first provide MLIR-based interaction with the *e-graph*. Then we project the hardware-specific operations in ISAX to software-level representations using *semantic translation*. Finally, we propose a *skeleton-component* pattern matching scheme to automate the identification and application of offloading opportunities.

## 5.1 Interaction between MLIR and e-graph

We introduce bidirectional translation between MLIR and *e-graph* to compactly represent equivalent program variants, exposing matching opportunities for ISAXs.

**From MLIR to e-graph:** We encode MLIR programs into the *e-graph* by mapping each operation to an e-node whose children are the e-classes of that operation's Static Single-Assignment (SSA) operands. Within each MLIR block, we distinguish *roots*—operations that enforce ordering constraints, including terminators (e.g., yield),

side-effecting operations (e.g., memref.store), and control-flow operations—from other order-independent operations. When a control-flow operation contains MLIR regions, we encode each region's block in the *e-graph* as a tuple(...) e-node that comprises its roots as children, sequencing in program order. The non-root operations within that block become dataflow subtrees in the *e-graph*, attached beneath the e-nodes of the roots that consume their results. This encoding preserves MLIR's ordering and dominance relationship within the *e-graph* structure. During equality saturation, only the dataflow subtrees undergo rewriting, while the tuple of roots remains fixed to maintain program order.

From e-graph to MLIR: Conversely, translating the e-graph back to MLIR is witness extraction: we first select one e-node from each reachable e-class. Control-flow operations map directly one-to-one to their MLIR counterparts. For each such operation, we iteratively reconstruct its contained blocks by materializing the tuple's roots in precise order and emitting their dataflow subtrees as SSA values. This consistent bidirectional translation ensures lossless conversion between MLIR and the e-graph by preserving execution order and side-effects in both directions, while still exposing rich dataflow equivalences for optimization.

Figure 3 further illustrates *e-graph* construction in step ①, where we use "for i" to denote both the loop operation and its region for brevity. The outer loop in the *e-graph* has a store node and a nested loop as its children, while the body of "for j" is abstracted as a parallelogram. Across steps ①, ③, and ③, MLIR and the *e-graph* are repeatedly converted back and forth, demonstrating the tight, seamless interaction enabled by our bidirectional mapping.

# 5.2 Hybrid Rewriting

With the bidirectional access, we can now fully explore equivalent program variants through a retargetable rewrite application. *E-graph* rewrites excel at scalar transformations but cannot naturally express control-flow reconstructing. MLIR provides powerful loop optimizations. Our framework combines *e-graph* and MLIR transformations. Specifically, our method proceeds along two axes of optimization. **Internal rewrites** apply dataflow equivalences directly within the *e-graph* using *Egglog* [31] fixpoint reasoning system. **External rewrites** manage the interaction between the *e-graph* and MLIR's control-flow passes by shuttling selected program fragments back and forth between the two representations. Both types of rewrites operate on the same *e-graph*, allowing dataflow optimizations and control-flow restructurings to accumulate rather than overwrite one another.

A key challenge in external rewrites is deciding *which* loop shapes to materialize and explore. At this stage, it is crucial to steer loops toward desirable target forms rather than blindly enumerate all possibilities; naive exploration would cause the *e-graph* to grow explosively. To avoid this blowup, we analyze loop structures using their nesting depth and trip counts. Based on this analysis, we apply standard control-flow passes (e.g., tiling, unrolling) to reshape loops into forms that expose target ISAX patterns. Finally, the optimized loops are translated back into the *e-graph* as new *e-*nodes, which are unioned with their original *e-*classes.

Step 2 and 3 in Figure 3 demonstrates this synergy. The original gemv application contains a two-level loop with non-affine index

Figure 3: End-to-end workflow of the Aquas retargetable compiler. 1 to 3 correspond to the steps for compiling an application.

expressions, which blocks MLIR's loop transformations. An internal rewrite first canonicalizes the index computation ( $i \ll 2 \Rightarrow i * 4$ ). Subsequently, the compiler leverages a cost model to extract a program variant that avoids non-affine (e.g., " $\ll$ ") access within loops, enabling more aggressive affine transformation during external rewrite. It then collects loop parameters from the target ISAX, which efficiently guides MLIR in performing a tailored loop unrolling pass with a factor of 4 in the inner loop. The resulting optimized loop is then merged back into the *e-graph*. Through this sequence of transformations, the optimized program becomes semantically equivalent to the target ISAX, enabling reliable ISAX-level matching.

#### 5.3 Semantic Translation

ISAXs specified in MLIR using the *Aquas* dialect explicitly capture hardware-specific semantics such as register file accesses and static array operations. Application code, however, operates on abstract memory addresses and values. We bridge this gap through *semantic translation*, which projects ISAX descriptions into equivalent software-level representations by eliminating hardware-specific transport operations while preserving computational semantics.

This translation is implemented as an MLIR pass that operates on two categories of hardware-specific operations. As depicted in step 4 of Figure 3, register operations such as read\_rf and write\_rf are eliminated by substituting register references with their corresponding SSA values (e.g., rs1 is replaced with a\_ptr). Memory operations, such as block\_load/block\_store to static arrays, are replaced with direct main memory accesses. In the example, temporary buffers (tmp, a) are eliminated, and all memory operations are unified to direct accesses via pointers (a\_ptr, c\_ptr). The translated ISAX representation retains only software-visible control flow and memory operations, making it structurally comparable to application code in the e-graph.

# 5.4 Skeleton-Components Pattern Matching

Next, we decompose each ISAX into a control skeleton and dataflow components to enable reliable and scalable matching within this search space. The skeleton captures the program's control structure and ordering constraints and is used to enforce correct execution

order and loop-carried dependencies among key operations in each block, while each component is a pattern tree rooted at one child of the block's root tuple (Step **⑤** in Section 5.1), such as a terminator or a side-effect node.

During matching, we encode components as *Egglog* rewrite rules to tag the side-effect-free dataflow subtrees beneath their respective roots. These rules are then applied to attach labels to the corresponding e-classes. Guided by the skeleton, a skeleton matching engine identifies candidate e-classes whose enclosing blocks satisfy the required loop/region structure and contain the complete component set. It then performs a series of checks, including ordering, dominance/visibility, loop-carried dependencies, and effect constraints. On success, an atomic *ISAX* node is emitted into the matched e-class (which will later be lowered to an intrinsic call to the ISAX). If the ISAX carries effects, this node serves as the unique sequencing point; purely dataflow ISAXs add no extra effect carriers.

Step **6** and **7** in Figure 3 respectively illustrate the two matching stages for a gemv ISAX. The ISAX has a two-level loop skeleton and two components (one store and one yield). In the matching phase, *Egglog* first tags components (**Comp1** and **Comp2**) to the corresponding e-classes. The skeleton matching machine then selects the for node introduced by the external rewrites in Section 5.2, whose tiled loop satisfies the skeleton; after validating order and dependences, we insert a gemv ISAX with parameters bound from the component matches.

Finally, after matching, *Aquas* extracts a single optimized program with ISAX calls from the *e-graph* (Step ③) and leverages the MLIR-LLVM pipeline to produce the final ISAX-accelerated binary.

#### 6 Experiments

In this section, we evaluate *Aquas* through two case studies targeting distinct domains: point-cloud analysis and large language model (LLM) dequantization. We first focus on the performance improvements and overheads of generated ISAXs for key computational kernels in these applications. Subsequently, we assess the efficacy of our *e-graph*-based compiler infrastructure in automating the mapping of software workloads onto these ISAXs.

|     |               |                                  |               |               |               |               | •            |               |              |

|-----|---------------|----------------------------------|---------------|---------------|---------------|---------------|--------------|---------------|--------------|

|     | Cana          | Execution Cycle Counts (Speedup) |               |               |               | Timing Period |              | Overall Area  |              |

|     | Case          |                                  | BOOMv3        | ICCAD'25 [25] | Aquas (ours)  | ICCAD'25 [25] | Aquas (ours) | ICCAD'25 [25] | Aquas (ours) |

| PCL | v3ddist_vv    | 495                              | 178 (2.78×)   | 229 (2.16×)   | 137 (3.61×)   | +0.10%        | +7.43%       | +41.06%       | +16.42%      |

|     | vcovmat3d_vs  | 853                              | 303 (2.82×)   | 131 (6.51×)   | 92 (9.27×)    | -0.61%        | +7.12%       | +64.21%       | +14.43%      |

|     | vfpsmax       | 60                               | 54 (1.11×)    | 76 (0.79×)    | 41 (1.46×)    | +3.97%        | +0.20%       | +92.00%       | +7.22%       |

|     | vgemv3d       | 127                              | 95 (1.34×)    | 202 (0.63×)   | 50 (2.54×)    | +2.03%        | -0.20%       | +37.63%       | +6.31%       |

|     | ICPAlgo       | 81466                            | 47879 (1.70×) | 99372 (0.82×) | 41596 (1.96×) | +1.93%        | +11.02%      | +216.98%      | +34.41%      |

| LLM | decompression | 737                              | 320 (2.30×)   | 189 (3.90×)   | 97 (7.60×)    | -0.10%        | +0.41%       | +43.61%       | +6.31%       |

|     | gemm          | 437                              | 385 (1.14×)   | 928 (0.47×)   | 59 (7.41×)    | +1.12%        | +0.10%       | +52.01%       | +6.01%       |

|     | DecAttn       | 26735                            | 22316 (1 20×) | 40570 (0.66×) | 12802 (2.09×) | -0.81%        | +1.83%       | +91 02%       | +11 66%      |

Table 1: Performance and hardware overheads of custom instructions for point-cloud analysis and CPU LLM inference

# 6.1 Experiment Setup

We select Rocket core[3] as our base processor core, on which we integrate our customized ISAXs using *Aquas*. We compare it against: (1) the original 5-stage-pipelined Rocket core running general C programs without ISAXs, (2) the Rocket core integrated with ISAXs using APS [25], and (3) a medium-configuration out-of-order BOOMv3 core [32] without ISAXs, serving as a more powerful general-purpose baseline to evaluate the performance and area efficiency of *Aquas* in domain-specific applications. Performance data (cycles) is collected via cycle-accurate simulation using Verilator [22]. Area and timing metrics are obtained using Synopsys Design Compiler 2022.03, targeting the sky130 process. Under this flow, the baseline Rocket runs at a maximum frequency of 101.7MHz with a total area of 4.27mm², and BOOMv3 achieves 60.02MHz and 17.34mm². All results are collected at the Tile scale with default cache size. For the whole flow, we use CIRCT [7] version e2b32a4.

## 6.2 Case study: Point-Cloud Analysis

The Iterative Closest Point (ICPAlgo) is a fundamental algorithm for 3D registration, essential for spatial alignment in point-cloud analysis [16]. This workload employs multi-stage iterative optimization to find the optimal transformation matrix for aligning source and target point clouds, which is compute-intensive with non-trivial control flow. We design a set of ISAXs, including computing the Euclidean distance (v3ddist\_vv), covariance matrix (vcovmat3d\_vs), maximum comparison (vfpsmax), matrix-vector multiplication (vgemv3d), to accelerate this algorithm.

Table 1 details the performance and overhead results of these ISAXs. Compared to the baseline Rocket core, Aquas achieves speedups of 1.46×-9.27×, substantially outperforms APS [25], which in some cases is slower than the base processor due to bounded memory access. This speedup stems from Aquas's ability to overcome the memory-bound limitations inherent in APS and generate efficient hardware. Specifically, by supporting burst memory access, Aquas achieves 1.92×-2.60× speedup in the memory access phase compared to APS. For the full pipeline, Aquas achieves a 1.96× speedup, comparable to high-performance general-purpose core BOOMv3 but with 67% area saving. As for overheads, these ISAXs incur less than 7.43% timing degradation due to more aggressive scheduling, along with less than 16.42% extra area for the individual, and 34.41% for the whole set, attributed to the banked scratchpad and unrolled multipliers. Despite these costs, Aquas achieves better area efficiency than APS by flexibly adjusting pipeline stages to reduce FIFO usage based on user-specific optimization directives.

Table 2: E-graph compiler statistics for ISAXs. AF: algebraic form, NS: numeric semantics, RE: reuse/CSE.

| Case         | Control-flow<br>Difference | Dataflow<br>Difference | Int./Ext.<br>Rewrites | Initial/Saturated<br>e-nodes |  |

|--------------|----------------------------|------------------------|-----------------------|------------------------------|--|

| v3ddist_vv   | Tile(8)                    | AF, RE                 | 25/1                  | 138/700                      |  |

| vcovmat3d_vs | Tile(4)                    | AF, NS, RE             | 24/1                  | 187/556                      |  |

| vfpsmax      | Tile+Unroll                | NS, RE                 | 15/2                  | 263/1212                     |  |

| vgemv3d      | Unroll(2)                  | NS, RE                 | 15/1                  | 104/359                      |  |

| ICPAlgo      | Tile+Unroll                | AF, NS, RE             | 30/3                  | 696/2842                     |  |

| decompress   | Tile(4)                    | NS                     | 9/1                   | 282/606                      |  |

| gemm         | Unroll(2)                  | NS, RE                 | 16/1                  | 131/394                      |  |

| DecAttn      | Tile+Unroll                | NS, RE                 | 20/2                  | 415/1026                     |  |

## 6.3 Case study: CPU LLM Inference

Recent work, such as DECA [8], identifies the weight decompression as a primary bottleneck in CPU-based LLM inference. We implemented two ISAX units, weight decompression, and 4x4 gemm with int16 datatype to accelerate the full Decompression and Attention (DecAttn) pipeline. Our evaluation demonstrates that Aquas achieves substantial speedups of 7.60× for decompression and 7.41× for gemm relative to the Rocket baseline, whereas APS and BOOMv3 show limited gains for decompression (3.90× and 2.30×, respectively) and gemm (0.47× and 1.14×, respectively). For the complete DecAttn pipeline, Aquas achieves a 2.09× speedup over Rocket, outperforms BOOMv3. This performance disparity is attributed to the fully customized dataflow enabled by enhanced memory bandwidth; Aquas's burst memory access provides a 5.75× (decompression) and 1.84× (gemm) speedup in the memory access phase alone compared to APS. This performance is achieved at a modest implementation cost. Integrating these ISAXs incurs an area overhead of less than 11.66% without noticeable frequency degradation (1.83%).

## 6.4 Compiler Support In Pattern-Matching

Table 2 summarizes *e-graph* compilation statistics for different cases, in which ISAX and C-code exhibit great variability in both control and dataflow. To validate our skeleton-component matching, we attempted encoding entire ISAX patterns as monolithic *e-graph* rules; this failed due to excessive complexity and syntactic brittleness. In contrast, our hybrid rewriting strategy successfully matched all valid patterns to ISAX calls. Specifically, each case costs 9-30 internal rewrites for dataflow and 1-3 external rewrites for control flow. Both rewrite types are essential and non-interchangeable, demonstrating the necessity of hybrid rewriting. Notably, our compiler

automatically identifies loop structure differences and applies targeted external loop transformation rewrites on demand, achieving successful matches in a single external rewrite pass for each loop. Throughout this process, e-node counts remain tractable, avoiding exponential blowup even for complex end-to-end workloads.

#### 7 Conclusion

This paper presents Aquas, a holistic MLIR-based framework for ASIP hardware-software co-design. Unified in MLIR infrastructure, Aquas provides an enhanced synthesis flow with burst-capable DMA and HLS optimizations for efficient hardware generation, and introduces a novel e-graph-based compiler with skeleton-component matching to automatically map applications to complex ISAXs. Evaluations on point-cloud analysis and LLM inference demonstrate up to  $9.27\times$  kernel speedup and  $1.96-2.09\times$  end-to-end acceleration over baseline Rocket, showcasing its high effectiveness for domain-specific acceleration.

#### References

- AMD. 2025. AMD Vitis<sup>™</sup> HLS. https://www.amd.com/en/products/software/ adaptive-socs-and-fpgas/vitis/vitis-hls.html

- [2] Giorgos Armeniakos, Alexis Maras, Sotirios Xydis, and Dimitrios Soudris. 2025. Mixed-precision Neural Networks on RISC-V Cores: ISA extensions for Multi-Pumped Soft SIMD Operations. In Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design. Association for Computing Machinery, New York, NY, USA, 1–9. https://doi.org/10.1145/3676536.3676840

- [3] Krste Asanović, Rimas Avižienis, and Jonathan Bachrach. 2016. The Rocket Chip Generator. Technical Report UCB/EECS-2016-17. Berkeley, CA. http://www.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-17.html

- [4] Yaohui Cai, Kaixin Yang, Chenhui Deng, Cunxi Yu, and Zhiru Zhang. 2025. SmoothE: Differentiable E-Graph Extraction. In Proceedings of the 30th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 1 (ASPLOS '25). Association for Computing Machinery, New York, NY, USA, 1020–1034. doi:10.1145/3669940.3707262

- [5] Hao Cheng, Georgios Fotiadis, Johann Großschädl, Daniel Page, Thinh H. Pham, and Peter Y. A. Ryan. 2024. RISC-V Instruction Set Extensions for Multi-Precision Integer Arithmetic: A Case Study on Post-Quantum Key Exchange Using CSIDH-512. In Proceedings of the 61st ACM/IEEE Design Automation Conference (DAC '24). Association for Computing Machinery, New York, NY, USA, 1–6. doi:10.1145/3649329.3657347

- [6] Codasip. 2025. CodAL RISC-V architecture description language Codasip. https://codasip.com/products/codasip-studio/codal/

- [7] Schuyler Eldridge, Prithayan Barua, Aliaksei Chapyzhenka, Adam Izraelevitz, Jack Koenig, Chris Lattner, Andrew Lenharth, George Leontiev, Fabian Schuiki, Ram Sunder, Andrew Young, and Richard Xia. 2021. MLIR as Hardware Compiler Infrastructure. In Workshop on Open-Source EDA Technology (WOSET).

- [8] Gerasimos Gerogiannis, Stijn Eyerman, Evangelos Georganas, Wim Heirman, and Josep Torrellas. 2025. DECA: A Near-Core LLM Decompression Accelerator Grounded on a 3D Roofline Model. In Proceedings of the 58th IEEE/ACM International Symposium on Microarchitecture (MICRO '25). Association for Computing Machinery, New York, NY, USA, 184–200. doi:10.1145/3725843.3756073

- [9] James C. Hoe and Arvind. 2000. Synthesis of operation-centric hardware descriptions. In Proceedings of the 2000 IEEE/ACM international conference on Computeraided design (ICCAD '00). IEEE Press, San Jose, California, 511–519.

- [10] Lana Josipović. 2025. dynamatic: DHLS (Dynamic High-Level Synthesis) compiler based on MLIR. https://github.com/EPFL-LAP/dynamatic

- [11] Chris Lattner, Mehdi Amini, Uday Bondhugula, Albert Cohen, Andy Davis, Jacques Pienaar, River Riddle, Tatiana Shpeisman, Nicolas Vasilache, and Oleksandr Zinenko. 2021. MLIR: Scaling Compiler Infrastructure for Domain Specific Computation. In 2021 IEEE/ACM International Symposium on Code Generation and Optimization (CGO). 2–14. doi:10.1109/CGO51591.2021.9370308

- [12] Huimin Li, Nele Mentens, and Stjepan Picek. 2022. A scalable SIMD RISC-V based processor with customized vector extensions for CRYSTALS-kyber. In Proceedings of the 59th ACM/IEEE Design Automation Conference (DAC '22). Association for Computing Machinery, New York, NY, USA, 733–738. doi:10.1145/3489517. 3530552

- [13] Jules Merckx, Alexandre Lopoukhine, Samuel Coward, Jianyi Cheng, Bjorn De Sutter, and Tobias Grosser. 2025. eqsat: An Equality Saturation Dialect for Nondestructive Rewriting. doi:10.48550/arXiv.2505.09363 arXiv:2505.09363 [cs].

- [14] Julian Oppermann, Brindusa Mihaela Damian-Kosterhon, Florian Meisel, Tammo Mürmann, Eyck Jentzsch, and Andreas Koch. 2024. Longnail: High-Level Synthesis of Portable Custom Instruction Set Extensions for RISC-V Processors from Descriptions in the Open-Source CoreDSL Language. In Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3. ACM, La Jolla CA USA, 591–606. doi:10.1145/3620666.3651375

- [15] Tianwei Pan, Tianao Dai, Jianlei Yang, Hongbin Jing, Yang Su, Zeyu Hao, Xiaotao Jia, Chunming Hu, and Weisheng Zhao. 2025. Finesse: An Agile Design Framework for Pairing-based Cryptography via Software/Hardware Co-Design. In Proceedings of the 52nd Annual International Symposium on Computer Architecture. ACM, Tokyo Japan, 65–77. doi:10.1145/3695053.3731033

- [16] Radu Bogdan Rusu and Steve Cousins. 2011. 3D is here: Point Cloud Library (PCL). In IEEE International Conference on Robotics and Automation (ICRA). IEEE, Shanghai, China.

- [17] Paul Scheffler, Luca Colagrande, and Luca Benini. 2024. SARIS: Accelerating Stencil Computations on Energy-Efficient RISC-V Compute Clusters with Indirect Stream Registers. In Proceedings of the 61st ACM/IEEE Design Automation Conference (DAC '24). Association for Computing Machinery, New York, NY, USA, 1-6. doi:10.1145/3649329.3658494

- [18] Synopsys, Inc. 2025. ASIP Designer. https://www.synopsys.com/dw/ipdir.php? ds=asip-designer

- [19] Blaise Tine, Varun Saxena, Santosh Srivatsan, Joshua R. Simpson, Fadi Alzammar, Liam Cooper, and Hyesoon Kim. 2023. Skybox: Open-Source Graphic Rendering on Programmable RISC-V GPUs. In Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3 (ASPLOS 2023). Association for Computing Machinery, New York, NY, USA, 616–630. doi:10.1145/3582016.3582024

- [20] Blaise Tine, Krishna Praveen Yalamarthy, Fares Elsabbagh, and Kim Hyesoon. 2021. Vortex: Extending the RISC-V ISA for GPGPU and 3D-Graphics. In MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO '21). Association for Computing Machinery, New York, NY, USA, 754–766. doi:10. 1145/3466752.3480128

- [21] Johan Van Praet, Dirk Lanneer, Werner Geurts, and Gert Goossens. 2008. Chapter 4 - nML: A Structural Processor Modeling Language for Retargetable Compilation and ASIP Design. In *Processor Description Languages*. Systems on Silicon, Vol. 1. Morgan Kaufmann, Burlington, 65–93. doi:10.1016/B978-012374287-2.50007-0

- [22] Veripool. 2025. Veripool. https://www.veripool.org/verilator/

- [23] Andrew Waterman, Yunsup Lee, David A. Patterson, and Krste Asanović. 2014. The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.0. Technical Report UCB/EECS-2014-54. EECS Department, University of California, Berkeley, Berkeley, CA. http://www2.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-54.html

- [24] Max Willsey, Chandrakana Nandi, Yisu Remy Wang, Oliver Flatt, Zachary Tatlock, and Pavel Panchekha. 2021. egg: Fast and extensible equality saturation. Artifact for "Fast and Extensible Equality Saturation" 5, POPL (Jan. 2021), 23:1–23:29. doi:10.1145/3434304

- [25] Youwei Xiao, Yuyang Zou, Yansong Xu, Yuhao Luo, Yitian Sun, Chenyun Yin, Ruifan Xu, Renze Chen, and Yun Liang. 2025. APS: Open-Source Hardware-Software Co-Design Framework for Agile Processor Specialization. In 2025 IEEE/ACM International Conference On Computer Aided Design (ICCAD). Munich, Germany.

- [26] Ruifan Xu, Youwei Xiao, Jin Luo, and Yun Liang. 2022. HECTOR: A Multi-level Intermediate Representation for Hardware Synthesis Methodologies. In 2022 IEEE/ACM International Conference On Computer Aided Design (ICCAD). San Diego, California, USA, 1–9. https://ieeexplore.ieee.org/document/10068908 ISSN: 1558-2434.

- [27] En-Yu Yang, Tianyu Jia, David Brooks, and Gu-Yeon Wei. 2021. FlexACC: A Programmable Accelerator with Application-Specific ISA for Flexible Deep Neural Network Inference. In 2021 IEEE 32nd International Conference on Application-specific Systems, Architectures and Processors (ASAP). 266–273. doi:10.1109/ASAP52443.2021.00046 ISSN: 2160-052X.

- [28] Hanchen Ye, HyeGang Jun, Hyunmin Jeong, Stephen Neuendorffer, and Deming Chen. 2022. ScaleHLS: a scalable high-level synthesis framework with multi-level transformations and optimizations: invited. In Proceedings of the 59th ACM/IEEE Design Automation Conference (DAC '22). Association for Computing Machinery, New York, NY, USA, 1355–1358. doi:10.1145/3489517.3530631

- [29] Jiaqi Yin, Zhan Song, Chen Chen, Yaohui Cai, Zhiru Zhang, and Cunxi Yu. 2025. e-boost: Boosted E-Graph Extraction with Adaptive Heuristics and Exact Solving. In 2025 IEEE/ACM International Conference On Computer Aided Design (ICCAD). Munich, Germany.

- [30] Abd-El-Aziz Zayed and Christophe Dubach. 2025. DialEgg: Dialect-Agnostic MLIR Optimizer using Equality Saturation with Egglog. In Proceedings of the 23rd ACM/IEEE International Symposium on Code Generation and Optimization (CGO '25). Association for Computing Machinery, New York, NY, USA, 271–283. doi:10.1145/3696443.3708957

- [31] Yihong Zhang, Yisu Remy Wang, Oliver Flatt, David Cao, Philip Zucker, Eli Rosenthal, Zachary Tatlock, and Max Willsey. 2023. Better Together: Unifying

- Datalog and Equality Saturation. Artifact for "Better Together: Unifying Datalog and Equality Saturation" 7, PLDI (June 2023), 125:468–125:492. doi:10.1145/3591239

- [32] Jerry Zhao, Ben Korpan, Abraham Gonzalez, and Krste Asanovic. 2020. SonicBOOM: The 3rd Generation Berkeley Out-of-Order Machine. In The Fourth Workshop on RISC-V for Computer Architecture Research (CARRV).