# Lattice Surgery Aware Resource Analysis for the Mapping and Scheduling of Quantum Circuits for Scalable Modular Architectures

BATUHAN KESKIN\*, EPFL, Switzerland

CAMERON AFRADI\*, University of California, Berkeley, USA

SYLVAIN LOVIS, EPFL, Switzerland

MAURIZIO PALESI, University of Catania, Italy

PAU ESCOFET, Universitat Politècnica de Catalunya, Spain

CARMEN G. ALMUDEVER, Universitat Politècnica de València, Spain

EDOARDO CHARBON, EPFL, Switzerland

Quantum computing platforms are evolving to a point where placing high numbers of qubits into a single core comes with certain difficulties such as fidelity, crosstalk, and high power consumption of dense classical electronics. Utilizing distributed cores, each hosting logical data qubits and logical ancillas connected via classical and quantum communication channels, offers a promising alternative. However, building such a system for logical qubits requires additional optimizations, such as minimizing the amount of state transfer between cores for inter-core two-qubit gates and optimizing the routing of magic states distilled in a magic state factory.

In this work, we investigate such a system and its statistics in terms of classical and quantum resources. First, we restrict our quantum gate set to a universal gate set consisting of CNOT, H, T, S, and Pauli gates. We then developed a framework that can take any quantum circuit, transpile it to our gate set using Qiskit, and then partition the qubits using the KaHIP graph partitioner to balanced partitions. Afterwards, we built an algorithm to map these graphs onto the 2D mesh of quantum cores by converting the problem into a Quadratic Assignment Problem with Fixed Assignment (QAPFA) to minimize the routing of leftover two-qubit gates between cores and the total travel of magic states from the magic state factory. Following this stage, the gates are scheduled using an algorithm that takes care of the timing of the gate set. As a final stage, our framework reports detailed statistics such as the number of classical communications, the number of EPR pairs and magic states consumed, and timing overheads for pre- and post- processing for inter-core state transfers. These results help to quantify both classical and quantum resources that are used in distributed logical quantum computing architectures.

CCS Concepts: • Computing methodologies  $\rightarrow$  Quantum computing; • Computer systems organization  $\rightarrow$  Dependable and fault-tolerant systems and networks; • Software and its engineering  $\rightarrow$  Compilers.

Additional Key Words and Phrases: lattice surgery; surface code; quantum error correction; resource estimation; quantum compilation; circuit mapping; scheduling; modular quantum architectures; fault-tolerant quantum computing

## 1 Introduction

Distributed quantum computing (DQC) for quantum information applications is a promising development for overcoming current problems in quantum computers, such as high noise due to large amounts of qubits in close proximity, cross-talk between qubits, and dense control and readout electronics that lay near the qubits [19, 23, 32]. Similar to the classical computing domain,

Authors' Contact Information: Batuhan Keskin, EPFL, Lausanne, Switzerland, batuhan.keskin@epfl.ch; Cameron Afradi, University of California, Berkeley, California, USA, cameronafradi@berkeley.edu; Sylvain Lovis, EPFL, Lausanne, Switzerland, sylvain.lovis@epfl.ch; Maurizio Palesi, University of Catania, Catania, Italy, maurizio.palesi@unict.it; Pau Escofet, Universitat Politècnica de Catalunya, Barcelona, Spain, pau.escofet@upc.edu; Carmen G. Almudever, Universitat Politècnica de València, València, Spain, cargara2@upv.edu.es; Edoardo Charbon, EPFL, Lausanne, Switzerland, edoardo.charbon@epfl.ch.

<sup>\*</sup>Both authors contributed equally to this research.

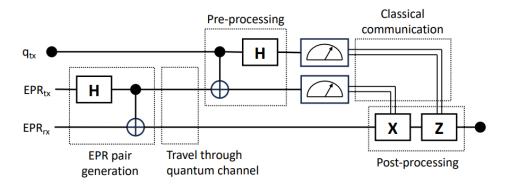

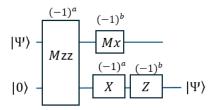

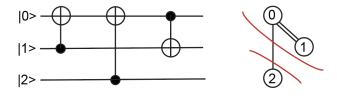

Fig. 1. Simple teleportation circuit

future quantum computers will also be integrated with networks, routers, and modular cores [6]. Such a structure should have the capability to communicate between cores using both classical and quantum channels. Usually, the quantum channel encompasses an EPR pair generator and distributor to implement the circuit in Figure 1, while the classical channels are used to route the measurement results in the quantum teleportation circuits [17]. Significant progress has been made to create these quantum channels using photon-shuttling interconnects, capable of shuttling microwave photons along a superconducting waveguide to facilitate remote entanglement between spatially separated quantum modules [2] or utilizing low-loss aluminum coaxial interconnects, which have demonstrated inter-module quantum state transfer and Bell state entanglement with fidelities up to 99% [25]. Other methods have proposed using microwave photons for entanglement generation [3] for superconducting qubits, entangling gates for neutral atoms using Rydberg-blockade interactions [14], and shuttling ions for ion-trapped computers [20].

For fault-tolerant quantum applications with distributed cores, the structure of these entanglement generation and the layout of the cores must be designed with additional care. Since each core contains logical qubits, the gate operations have to be done without destructing the encoding capability of the qubits both for inter-core and intra-core operations. Considering logical qubits produced by rotated surface codes, there are two ways of employing logical qubits over a DQC. Logical qubits may be encoded on all/some of the cores by encoding the logical state onto the physical qubits that are in different cores [33], or alternatively, logical qubits in each of the cores are encoded over some set of physical qubits within the same core. To do the former method, the system has to generate the necessary connection between physical qubits (GHZ state) each time there is a stabilizer check [30]. In the latter approach, the direction of this work, inter-core operations are only required for logical gates between logical qubits residing on different cores.

Building on this framework, an effective DQC architecture must not only ensure the fault-tolerant execution of logical operations, but also provide scalable mechanisms for routing, scheduling, and supplying essential non-Clifford resources [7]. In particular, the efficient movement of logical states and the provisioning of magic states across a network of cores is critical for enabling universal computation while keeping both quantum and classical resource overhead manageable. Motivated by these challenges, our work makes the following contributions:

• We developed a simulation framework for DQC with logical qubits to analyze classical and quantum resource consumption.

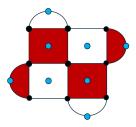

Fig. 2. Distance-3 Rotated Surface Code. Black circles are data qubits, blue circles are ancilla qubits. Red and white represent different stabilizer checks such as X and Z.

- We devised a routing system that uses logical ancillas with logical smooth teleportation gates for state transfer between logical qubits to schedule and route distant CNOTs and magic states.

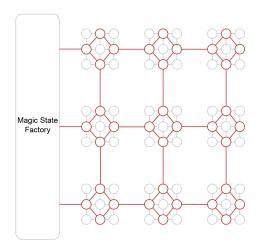

- We introduced a Magic State Factory (MSF) connected to a 2D mesh of quantum cores from

one edge to supply magic states for T and S gates, and a new optimization procedure for

the qubit-to-core and core-to-mesh placement by taking into account the routing of CNOTs

and magic states.

- We created a scheduling algorithm that parallelizes and pipelines gates as much as possible according to the availability of logical qubits and timing of logical gates.

- We ran different benchmarks and report the consumed resources for both quantum NoC and classical NoC.

## 2 Background

## 2.1 Surface Code

It is necessary to first introduce the concepts of surface code and lattice surgery (LS), as they appear frequently in this work. The surface code is a topological quantum error correction code [21]. It is one of the most well-known and studied quantum error correction codes that uses X and Z checks for detecting bit flips and phase flips occurring on the physical qubits. These checks stabilize the logical system, so it is also referred to as a stabilizer code [16]. Utilizing this a mechanism, a logical qubit can be built by encoding the state over some number of physical qubits. It is well-suited for 2D meshes of qubits, as it works well with the fact that qubits can only interact with their nearest neighbors. A surface code is defined with the notion of [n, k, d] where n is the number of physical qubits used, k is the number of maximum encodings that the code can support, and k is the code distance and determines the level of error protection. In this work, it is assumed that k is always one and k is defined by the user. In addition, the structure of the logical qubit within this work is a rotated surface code [5]. It is illustrated in Figure 2.

## 2.2 Lattice Surgery and Logical Gates

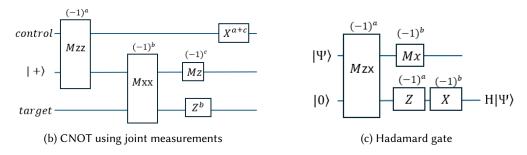

Lattice surgery is a clever method of executing logical gates by using additional qubits between logical patches. It does so without destructing the ability of error detection by turning on and off stabilizers in between patches. It can merge two logical states into one state, or it can split a logical composite state into two logical states. Usually, it is assumed that there are physical ancilla qubits between the logical patches that are either in the ground state or in the plus state. These qubits can be used to create additional stabilizers between two patches. After checking these stabilizers d rounds, where d is the distance of the code, the states of the two logical qubits are merged into a single state. This process is called surface merging. After the merging operation, by measuring the

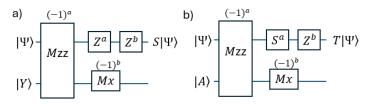

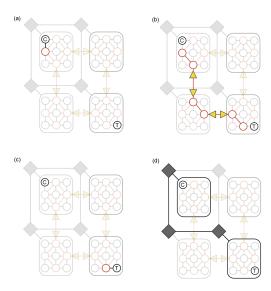

(a) S and T gates with magic states

Fig. 3. Universal gate set operations that require lattice surgery. System uses (a) S and T gates, (b) CNOT gate, and (c) Hadamard gate. Pauli operations are done via software.

boundary data qubits of these two patches and turning off the stabilizers, the single state can be split into two logical states. This operation is called surface splitting. For more details of LS we refer to [18]. The concept of LS changes some of the fundamentals of quantum gates. For instance, to be able to do a CNOT gate between two logical qubits there is a need for a logical ancilla qubit. Also, the Hadamard gate utilizes a logical ancilla to prevent rotating the code space. In Figure 3a, S and T gates are illustrated with magic states  $|Y\rangle = (|0\rangle + i|1\rangle)/\sqrt{2}$  and  $|A\rangle = (|0\rangle + e^{i\pi/4}|1\rangle)/\sqrt{2}$  respectively.

In Figure 3b, the CNOT gate is illustrated. In total, it uses two joint measurements and, to perform it correctly, one additional ancillary patch is needed. It is assumed that this fault-tolerant CNOT gate is completed in 2d cycles where d is the distance of the logical qubit.

In Figure 3c, the Hadamard gate is illustrated. In total, it uses one joint measurement and to perform it without rotating the codespace, one additional ancillary patch is needed. It is assumed that this fault-tolerant Hadamard gate is completed in d cycles.

In Figure 4, the Smooth Teleportation protocol is illustrated. This gate enables the teleportation of a logical state from one patch to another by applying a series of joint merge and split measurements and a single measurement of the logical state [11]. The resulting information is then used to apply Pauli corrections on the transferred logical state. Within this framework, the Smooth Teleportation gate is frequently employed to route the desired state from logical data qubit to an ancilla and subsequently across the ancilla network to other ancillas within the same core. For inter-core state transfer, the same gate is utilized; however, when a state reaches the ancilla that is located at the edge of a core, it uses EPR pairs to teleport the state to the other nearest neighboring core. More detailed explanations are given in the following sections.

Throughout this framework, we utilize a universal gate set consisting of CNOT, H, T, S, and Pauli gates (X,Y,Z). The correction gates that come from the measurement results are assumed to be done on the software side. Even though the S gate correction within the T gate is in the Clifford

Fig. 4. Smooth teleportation protocol of a logical state

gate set, we still include it in our analysis and assume it is done on the qubit since it requires LS and a magic state to be done fault-tolerantly.

#### 3 Prior work

From a circuit-compilation and runtime analysis of quantum circuits perspective, there are fundamental approaches to modular quantum architectures. Since cores would be located far away from each other on a real hardware, the compilation of the quantum circuit should place the qubits in these cores so that the cost of having inter-core state transfers is minimized. This problem is NP-hard [24]. It is usually considered as balancing subgraphs while minimizing the cuts between these subgraphs, which in our case are quantum cores. Various methods are proposed to achieve better mapping efficiency for DQC. Reducing collective communication by using communication buffers [36], converting this problem into a dynamic network flow [9] problem, or using Reinforcement Learning agents [27, 29]. There are other methods that have been developed by taking into account the time slices and creating a cost matrix for non-local operations, then minimizing the total cost by using graph partitioning algorithms [4] or assignment algorithms [13].

Overall, our work differs from these previous approaches, as we also consider the routing of magic states as a non-local operation. In a real hardware, it makes sense to have a different unit that specializes to generate and distillate magic states. Additionally, in our work we consider the gate operations for logical qubits both locally and non-locally. This makes our work more complete and close to real-world hardware. Furthermore, by explicitly modeling both local and distributed operations, our approach captures the impact of classical and quantum communication on performance and resource usage [12]. This allows for a more realistic evaluation of scheduling, routing, and entanglement management, which are essential for scalable fault-tolerant quantum computing. We have gathered several concepts together to have a more complete resource analysis of DQC with logical qubits.

# 4 Proposed Architecture for DQC

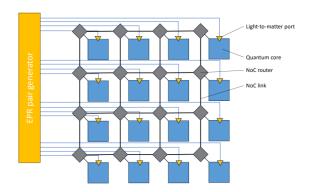

A previous work was done [26] that assumed an all-to-all connection within a core, with each core directly hosting physical qubits. This structure is illustrated in Figure 5. In this architecture, all the cores have access to an EPR pair generator and a classical Network on Chip (NoC) of links and routers. By enabling both local and distributed operations, such a modular approach provides a pathway toward scalable quantum computation while mitigating limitations arising from hardware such as noise, connectivity, and dense control electronics.

However, this proposal does not account for logical qubits, the routing of magic states needed for logical gates, logical qubit operations via LS, and architecture optimization for mapping the quantum circuits to such structures.

In this regard, we propose an extension to such architectures that includes a 2D mesh of quantum cores each hosting an equal number of logical data qubits and logical ancilla patches. This mesh

Fig. 5. Multi-core quantum architecture [26]

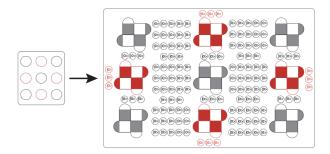

Fig. 6. Structure of one core

has a connection to an EPR pair distribution unit as in Figure 5. In addition, it has a connection to a MSF as in Figure 10. Using these two blocks, which act as support units to the computing unit (which is the distributed cores), our proposal represents a complete system for fault-tolerant DQC.

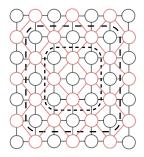

In Figure 6, the inside of a core is shown. The red rotated surface code patches are logical ancillas, and the gray patches are logical data qubits. The remaining qubits in between patches are used to implement merge and split operations for LS. The physical qubits on the core edges (red circles) are assumed to be used for inter-core operations.

In this framework, it is assumed that the diagonal merge and split operations can be performed using the idea in [15] by utilizing the qubits in between two nearest logical ancilla to satisfy the merge and split operations. This is illustrated in Figure 7. This feature forms the basis of routing states over the ancilla network for doing distant CNOTs and magic state travel. In this setup, whenever a logical qubit needs to do a single-gate operation that requires a magic state, it is routed from the MSF to the nearest ancilla by implementing a series of smooth teleportation and inter-core teleportation. Then, the logical data qubit and the ancilla interact using joint measurements with LS.

These cores are connected to each other by facilitating EPR pair distribution that enables smooth teleportation operations between two distant ancilla patches located in neighboring cores. It is assumed that by using these EPR pairs, the merge and split operations can be done by teleporting the CNOT gate over the cores as in [28]. Since every ancilla patch on the core edge has additional physical qubits, CNOTs needed for stabilizer checks can be transferred between cores as in Figure 8.

Fig. 7. Diagonal Merge and Split

Fig. 8. LS between cores

The necessary number of EPR pairs for this operation to be fault-tolerant is  $O(d^2)$ , where d is the code distance. This is because they are consumed every inter-core operation, and stable operations should be checked at least d rounds consecutively. In this framework, it is assumed that EPR pairs can be distributed to each edge logical ancilla on a core. A core with  $n^2$  logical qubits has  $(n^2+1)/2$  logical data qubits and  $(n^2-1)/2$  logical ancilla qubits. In total, a core has (n-1)/2 logical ancillas per edge and 2n-2 total logical ancillas that can access EPR pairs to transfer a state to the nearest core.

On a real hardware, this configuration makes sense because the communication would be bottlenecked if the cores had very few quantum channels. In such a case, the scheduler would be unable to efficiently parallelize the gates, as there would not be space for different state transfers at the same time. Building such a structure is also necessary for the proposed idea of utilizing the ancilla network for transferring magic states and enabling distant CNOTs.

## 5 Fault Tolerant Operations

The first part of simulating a quantum circuit on our architecture requires decomposing the circuit to a set of instructions that tell the system what to execute during each time slice. While systems using physical qubits just need to communicate locations of physical qubits and their corresponding gates, the multi-step structure of fault-tolerant operations on a logical qubit requires a system for scheduling and routing. We also take measures in employing path-finding methods in our architecture to pipeline the execution of fault-tolerant gates.

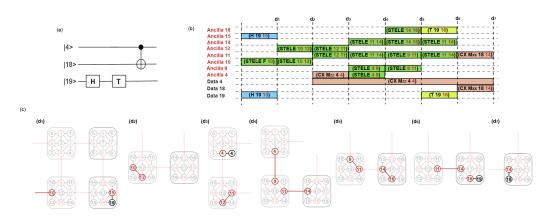

Fig. 9. Execution of a CNOT gate by (a) instantaneous transversal preparation of adjacent logical ancilla into the plus state and Mzz operation between logical ancilla and control logical data qubit, (b) movement of the state of logical ancilla, (c) Mxx operation between logical ancilla and target logical data qubit, and (d) classical communication of results between cores on NoC

## 5.1 Order of Operations

Supporting LS operations within the architecture requires defining the sequencing of both resource allocation and LS. Single-qubit gates require logical ancilla to be prepared in order to perform a LS operation. The Hadamard and Smooth Teleportation gates require logical ancilla to be initialized in either the plus or zero state, which can be done instantaneously on available on-core ancilla. In contrast, the S and T gates require magic states that must first be distilled in an MSF off the mesh and then transferred to an available ancilla on the core. The two-qubit CNOT gate also requires an ancilla prepared in the plus state; however, the structure of the fault-tolerant operation can be leveraged so that logical qubits remain stationary, while the ancilla state is transferred. Figure 9 shows the stationary implementation of the CNOT in our architecture. This differs from current physical qubit distributed works, where all participating qubits must reside within the same core to perform multi-qubit gates. By exploiting the sequencing of LS operations, we have developed an innovative sequence and routing structure that keeps data logical qubits fixed in place, enabling new optimization strategies for quantum processing units within a mesh.

## 5.2 Scheduling and Routing Operations

As discussed, logical data qubits within our architecture remain fixed while ancilla logical qubits are used to support fault-tolerant gate operations. At any moment within the circuit, the ancilla are either unused or being used within an LS operation. We introduce a network of ancilla within our architecture in order to schedule and route operations.

We can represent our network of ancilla as a weighted graph as shown in Figure 10. The vertices are the ancilla themselves and the edges represent potential merge operations between different ancilla logical qubits. Scheduling the gate operations now devolves into a path-finding exercise considering the order of operations in a fault-tolerant gate. We implement a modified Dijkstra's

Fig. 10. Ancilla network can be represented as a graph for path finding methods

Table 1. Timing and logical ancilla allocation used within the scheduler for fault tolerant gates where d is the code distance.

| Gate Type            | Cycles | Logical Ancilla State  |

|----------------------|--------|------------------------|

| Pauli                | 0      | None                   |

| S                    | d      | Magic State            |

| T                    | d/2d   | Magic State            |

| Hadamard             | d      | Transversal Zero State |

| Smooth Teleportation | d      | Transversal Plus State |

| Controlled-NOT       | 2d     | Transversal Plus State |

algorithm (Algorithm 1) within our work to handle this path finding. Dijkstra's algorithm is a search algorithm used to find the shortest path between nodes in a weighted graph with non-negative edge weights [10]. Within our algorithm, the weight of an edge between two vertices is given by the larger execution end time plus the time needed for state movement. This is done in order to minimize the total execution time of the circuit. The time required for each operation is reported in Table 1. However, the weights of an edge can be changed depending on what is being optimized. For example, if we only want to minimize total core-to-core operations, we can set all inner core edges to an equal weight, all core-to-core edges to a higher weight, and then sequence parallel operations.

Within the simulation our path finding algorithm tests all available adjacent ancilla, and adjacent ancilla combinations in the case of two qubit gates, and chooses whichever produces the smallest increase in execution time. The time steps within our algorithm are given by the cycles of syndrome measurement, which depends on the code distance. The scheduler also takes steps to ensure the

# Algorithm 1 Scheduling fault-tolerant operations

```

1: function Schedule(CIRCUIT)

for all GATE \in CIRCUIT do

2:

if GATE is CNOT then

3:

PATH \leftarrow DIJKSTRA(q_1, q_2)

map (CNOT<sub>MZZ</sub>, PATH) \rightarrow (q_1, ancillas)

5:

map (PATH, CNOT<sub>MXX</sub>) \rightarrow (q_2, ancillas)

6:

else if GATE is T or S then

7:

PATH \leftarrow DIJKSTRA(factory, q_1)

map (PATH, GATE) \rightarrow (q_1, ancillas)

9:

else if GATE is H then

10:

map (GATE) \rightarrow (q_1, ancillas)

11:

end if

12:

end for

13:

14: end function

```

Fig. 11. (a) Sample circuit parsed to the (b) scheduler with (c) execution of the circuit at each cycle

accuracy of the circuit. We prevent idling of logical qubits by delaying the start of CNOT gates if the best path of the ancilla starts at some time after the end of the joint Z operation. Furthermore, even though the joint Z for the CNOT operation only takes d cycles, the end time of the execution in the scheduler is set to the end time of the joint X operation so that no operations can occur on the logical data qubit until post-processing has occurred. Both of these concepts are shown in the example scheduler in Figure 11. The scheduler naturally routes and parallelizes the execution of the quantum circuit while not interfering with the circuit's logic. It acts agnostic to other systems in the layout, such as the NoC and EPR pair communication, but does account for the time needed to distill magic states.

For Dijkstra's algorithm [10] implemented with a binary heap, the complexity is  $O((|E| + |V|) \log |V|)$ . Within our graph, the nodes are logical qubits, and the edges are potential merge operations between logical qubits facilitated by physical qubits. The parameters of a graph with symmetric cores are defined as modular dimensions  $m_x$  and  $m_y$ , core dimension c, and number

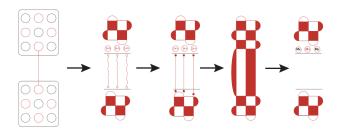

Fig. 12. Symmetric scaling of core with logical qubit placement at sizes 3, 5, and 7

Fig. 13. Example of partitioning a circuit between two cores

of gates N. The number of qubits within our system, Q, can be given as  $m_x m_y c^2$ . The number of connections between adjacent cores and the magic state factory is  $(m_x m_y + m_x (m_y - 1))((c - 1)/2)$ . The first term of the unscaled equation represents the horizontal connections, which include connections to the MSF, and the second term represents the vertical connections. The connections within a core is given by  $2c(c-1)+(c-1)^2$ , where the first term represents non-diagonal connections, and the second term represents diagonal connections. Note that the number of edges in a core scales by a  $c^2$  factor due to the scaling of cores as seen in Figure 12. The edges within the core must also be scaled by the number of cores within a system, which is  $m_x m_y$ . It can then be seen that the total number of edges within the graph is asymptotically bounded by the  $m_x m_y c^2$  term, which is equivalent to the number of logical qubits within the system. The complexity of the algorithm simplifies to  $O(Q \log Q)$ . The scheduling algorithm iterates over the set of gates, so the final complexity can be given by  $O(N \cdot Q \log Q)$ .

# 6 Systems Optimization

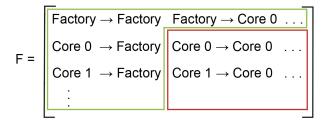

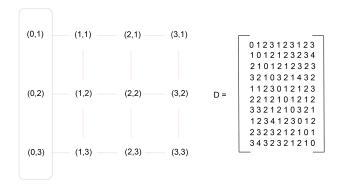

While our scheduler takes steps to pipeline instructions, further operations can be taken to optimize the time and resources used in the circuit execution. The architecture has two layers that we jointly optimize. We approach both optimizations by trying to limit the amount of inter-core operations (Algorithm 2). Two operations lead to inter-core movement, movement of magic states for a T or S gate and movement of an ancilla state for multi-qubit operations. The first relates to how qubits are assigned to a core and where cores are placed in relation to each other on the mesh. Meanwhile, the optimization of magic state routing relates to where cores are placed in relation to the distillation factory. Within both parts of the optimization, we leverage the fact that logical data qubits within our architecture are stationary.

Fig. 14. Flow matrix used in quadratic assignment where the red box represents inter-core operations from CNOTS collected by the edges between partitons and the green box represents the amount of inter-core operations from magic state routing

Fig. 15. Distance matrix for a 6x6 mesh

## 6.1 Qubits to Core Optimization

Within the first part of the algorithm, we utilize a graph partitioning method to minimize the amount of inter-core CNOT operations. As seen in Figure 13, the vertices represent the qubits and the edges represent a CNOT operation. In partitioning this graph, we group the qubits into equal sized cores, minimizing the amount of CNOT operations that require movement between cores. We use KaHIP partitioning within our simulation to handle the zero imbalance partitions [31].

## 6.2 Optimizing Core Placement Within a Mesh

After partitioning the qubits we are left with a set of cores and the leftover edges between them. Furthermore, we still have not considered the inter-core operations from routing magic states. Both of these criteria are handled when optimizing the placement of cores onto the mesh. This is a novel approach, as past optimization models usually consider an all-to-all connection, neglecting movement of states along the mesh and from a system (MSF) off the mesh. In the second part of our optimization algorithm, we have two variables to consider, the distance between locations on the mesh and the amount of core-to-core and factory-to-core inter-core operations. By rephrasing inter-core operations as the amount of flow between cores and prep states, the problem reduces to minimizing the total amount of flow.

The optimization problem becomes a quadratic assignment problem (QAP), as introduced in [22]. QAP is finding an optimal assignment of facilities to locations in order to minimize the total cost, where the cost depends on both the flow between facilities and the distance between locations.

This problem is known to be NP-hard, and even approximate solutions become computationally challenging as the system size increases.

We want to assign cores to the mesh in order to minimize the amount of inter-core operations. The problem is:

minimize

$$\sum_{i,j\in[n]} f_{i,j} d_{\pi(i)\pi(j)} \text{ where } \pi \in \prod$$

(1)

$f_{i,j}$  represents the flow between the cores i and j, the amount of inter-core operations, and  $d_{\pi(i)\pi(j)}$  represents the distance between locations in the mesh, assigned by the current permutation of i and j. In a mesh topology, the distance is given by the Manhattan distance. The flow matrix structure that uses the results of the graph partitioning can be seen in Figure 14, and an example distance matrix can be seen in Figure 15. We can account for the prep state module by considering N+1 cores and fixing the location of the first spot in all permutations, so we have permutations of size N+1 but only permutating over N values. This will allow us to consider the flow of both inter-core operations from CNOTs and inter-core operations from routing the magic states. The problem then becomes a quadratic assignment problem with fixed assignment (QAPFA). The problem is NP-hard, but it can be solved exactly for fewer than ten cores in a reasonable amount of time. For larger meshes, we implement the heuristic Robust Taboo Search as it can efficiently handle larger sets of cores and the iterative approach makes it an ideal choice for implementing a fixed permutation [34, 35].

While we use leftover edges from the partitions to construct the core-to-core inter-core operations, we use a weighted system for assigning inter-core operations between the factory and cores. The S gates are weighted to a constant since they require one magic state, while the T gates are weighted as 1.5 × the constant since we give it a probability of also requiring an S gate following the execution of a T gate. The overall flow of the algorithm involves first partitioning the cores, then using the partitioned graph to construct the flow matrix while the distance matrix is constructed from the inputted mesh, and lastly either directly solving the quadratic assignment problem or using our chosen heuristic.

## 6.3 Qubit Placement Within a Core

This part of the optimization assigns qubits to a core by sorting each core's qubit list that comes from the previous step according to a precomputed weight vector, where each weight reflects the total number of T and S gates associated with that qubit. By ordering the qubits in descending weight, the most resource-intensive qubits in regard of magic states are placed closest to the MSF. The remaining qubits follow in decreasing priority, ensuring that placement aligns with computational demand (Algorithm 3). This would conclude the hierarchical optimization within our model regarding the mapping of the qubits.

## 7 Results

The proposed framework was tested with different quantum circuits, generated from Qiskit [1], and different layouts to demonstrate the feasibility of optimizing core placement in a 2D mesh. First, only a random placement of qubits to cores is implemented. Then, only the KaHIP algorithm was used to place the qubits more efficiently to the cores to reduce the inter-core CNOTs. Lastly, the new optimization stage that is introduced in this work was implemented together with KaHIP. The results clearly indicate that even for small number of gates there is a significant improvement on the number of executed gates, EPR pairs, total travel of magic states, and total cycles of the circuit. Different circuits with varying core and mesh sizes, gate probabilities, and number of gates were

## Algorithm 2 Optimizing mapping of logical cores and qubits

```

1: function OPTIMIZE(CIRCUIT)

for all GATE \in CIRCUIT do

2:

if GATE is CNOT then

3:

CREATE EDGE(GRAPH, q_1, q_2)

4:

else if GATE is S then

5:

WEIGHT[q_1] += weight constant

else if GATE is T then

7:

WEIGHT[q_1] += weight \ constant \cdot 1.5

end if

9:

end for

10:

CORES \leftarrow PARTITION(GRAPH)

11:

for all CORE \in CORES do

12:

FLOW[CORE_i][CORE_i] \leftarrow

13:

COUNT\_EDGES(CORE_i, CORE_i)

14:

end for

15:

for all LOC \in MESH do

16:

DIST[LOC_i][LOJ_i] \leftarrow

17:

|x_i-x_j|+|y_i-y_j|

18:

end for

19:

for i = 0 to NUM\_CORES do

20:

CORE_i \leftarrow CORES[i]

21:

FLOW[FACTORY][CORE_i] \leftarrow

22:

SUM(WEIGHT[qubit] for qubit in CORE_i)

23:

FLOW[CORE_i][FACTORY] \leftarrow

24:

FLOW [FACTORY] [CORE;]

25:

DIST[FACTORY][CORE_i] \leftarrow x_i

DIST[CORE_i][FACTORY] \leftarrow

27:

DIST[FACTORY][CORE_i]

end for

29:

MAP \leftarrow \text{QUADRATIC}(\text{FLOW, DIST})

30:

31: end function

```

## **Algorithm 3** Optimizing mapping of qubits in a core

```

1: function InsideCorePlacement(MAPPEDCORES,WEIGHT)

2: for i = 0 to NUM_CORES - 1 do

3: sort MAPPEDCORES[i]

4: for a and b in MAPPEDCORES[i]

5: respect to WEIGHT[a] > WEIGHT[b]

6: end for

7: MAP ← FILL FIRST CLOSE TO MSF

8: end function

```

analyzed to find the best structures and see the best gains in terms of statistics. This is essential to reduce the undesired cost of these modular architectures and find the most efficient layout.

Table 2. Random 10,000 Gate Circuit | 6x6 Mesh | 5x5 Core Size | Code Distance 3 | 468 Logical Qubits | 60/40 one-qubit gate/two-qubit gate.

| Stats-Mapping      | Part.+ QAPFA | Part.  | Random |

|--------------------|--------------|--------|--------|

| Executed Gates     | 110448       | 114100 | 129257 |

| EPR Pairs          | 241623       | 250785 | 288090 |

| Magic State Travel | 40868        | 43191  | 45088  |

| Cycles             | 10944        | 11298  | 13701  |

Table 3. Random 10,000 Gate Circuit | 6x6 Mesh | 5x5 Core Size | Code Distance 3 | 468 Logical Qubits | Clustered 80/20 20/80 one-qubit gate/two-qubit gate.

| Stats-Mapping      | Part.+ QAPFA | Part.  | Random |

|--------------------|--------------|--------|--------|

| Executed Gates     | 93058        | 106584 | 136924 |

| EPR Pairs          | 196308       | 229536 | 302337 |

| Magic State Travel | 22885        | 35402  | 35751  |

| Cycles             | 11145        | 11187  | 15390  |

Table 2 shows an improvement in all statistics after optimizing the core placement in the mesh. The circuit used for this benchmark has a six-to-four ratio of one- and two-qubit gates. It is shown that by using the new optimization on the mapping side, the total travel of the magic states was significantly reduced. It also reduced the total number of gates, EPR pairs, and total cycles.

Table 3 shows a circuit with an uneven distribution of gates. Half of the logical qubits have significantly more CNOTs than T and S gates while the other half has the reversed probability. Our placement algorithm shows a strong improvement on the total travel of magic states. This is due to our optimization algorithm placing cores with a high number of gates that utilize magic states closer to the MSF. This benchmark is a good example of the benefits of using our algorithm.

Table 4 has a circuit with the same probability for all the gates. It has a significant gain in all statistics. Although the number of gates, number of qubits, and the layout is the same as previous benchmarks, it results in lower executed gates and EPR pairs consumed since it has a lower amount of CNOTs.

Table 5 is an example of exactly solving the placement of cores in our mesh instead of using a heuristic. Since the number of cores is just nine, it is well in the upper bound of the size of a mesh for QAPFA to have an exact solution. However, in this benchmark, we kept the number of gates higher than in the previous benchmarks. The results clearly present gains in all statistics when our optimization is used after partitioning.

Table 6 shows how much the layout of the mesh affects the efficiency of resource consumption. Compared to Table 2, this benchmark has more cores, but each core has a smaller number of qubits. Also, this layout is potentially inefficient since it is not a square and the ratio of cores that can reach the MSF is lower compared to Table 2. Even though the number of qubits is very close, and

Table 4. Random 10,000 Gate Circuit | 6x6 Mesh | 5x5 Core Size | Code Distance 3 | 468 Logical Qubits | Same Probability for All the Gates.

| Stats-Mapping      | Part.+ QAPFA | Part. | Random |

|--------------------|--------------|-------|--------|

| Executed Gates     | 79736        | 84326 | 93857  |

| EPR Pairs          | 177615       | 18669 | 212517 |

| Magic State Travel | 51768        | 55701 | 56058  |

| Cycles             | 10470        | 10536 | 13920  |

Table 5. Random 30,000 Gate Circuit | 3x3 Mesh | 5x5 Core Size | Code Distance 3 | 117 Logical Qubits | 60/40 one-qubit gate/two-qubit gate.

| Part.+ QAPFA | Part.                     | Random                                        |

|--------------|---------------------------|-----------------------------------------------|

| 188925       | 190407                    | 194393                                        |

| 383409       | 386181                    | 398007                                        |

| 55176        | 56515                     | 56429                                         |

| 50226        | 50646                     | 50988                                         |

|              | 188925<br>383409<br>55176 | 188925 190407<br>383409 386181<br>55176 56515 |

$\label{logical Qubits | 60/40 one-qubit gate/two-qubit gate} Table 6. \ Random 10,000 \ Gate \ Circuit \ | \ 8x12 \ Mesh \ | \ 3x3 \ Core \ Size \ | \ Code \ Distance \ 3 \ | \ 480 \ Logical \ Qubits \ | \ 60/40 \ one-qubit gate/two-qubit gate.}$

| Stats-Mapping      | Part.+ QAPFA | Part.  | Random |

|--------------------|--------------|--------|--------|

| Executed Gates     | 118458       | 125823 | 143877 |

| EPR Pairs          | 403767       | 429480 | 500994 |

| Magic State Travel | 46702        | 51315  | 52880  |

| Cycles             | 14007        | 15300  | 18378  |

the number of gates is equal, this structure results in almost more than two times the amount of EPR pairs consumed and more than three times the amount of cycles needed to execute the circuit.

Table 7 shows the same number of qubits with the same circuit that was used for Table 6, but with a much more efficient inverse configuration. This benchmark has more cores that are connected to the MSF. This enables the flow of magic states from more channels and reduces the traffic of the total flow. Even though the number of qubits is the same and the number of gates is equal, this structure consumes lower EPR pairs, finishes in lower cycles, results in lower total travel of magic states, and the QAPFA optimization gives more gain compared to just partitioning.

Table 8 presents a benchmark involving a Cuccaro Adder circuit [8]. In this circuit, CNOT, and T gates are dominant and almost symmetrically distributed among the qubits. Following core

Table 7. Random 10,000 Gate Circuit | 12x8 Mesh | 3x3 Core Size | Code Distance 3 | 480 Logical Qubits | 60/40 one-qubit gate/two-qubit gate.

| Stats-Mapping      | Part.+ QAPFA | Part.  | Random |

|--------------------|--------------|--------|--------|

| Executed Gates     | 105607       | 112480 | 131747 |

| EPR Pairs          | 361431       | 387522 | 459477 |

| Magic State Travel | 35701        | 38047  | 40482  |

| Cycles             | 12324        | 13128  | 18378  |

Table 8. Quantum Adder Circuit 12,117 Gate Circuit | 6x6 Mesh | 5x5 Core Size | Code Distance 3 | 468 Logical Qubits

| Stats-Mapping      | Part.+ QAPFA | Part.  | Random |

|--------------------|--------------|--------|--------|

| Executed Gates     | 228096       | 230045 | 299010 |

| EPR Pairs          | 548856       | 553824 | 712053 |

| Magic State Travel | 192548       | 193989 | 207971 |

| Cycles             | 38568        | 39546  | 87573  |

Table 9. Random 10,000 Gate Circuit | 12x8 Mesh | 3x3 Core Size | Code Distance 3 | 480 Logical Qubits | 60/40 one-qubit gate/two-qubit gate.

| Stats-Mapping | Part.+ QAPFA | Part.   | Random  |

|---------------|--------------|---------|---------|

| Traffic(bits) | 4906906      | 5250268 | 6205824 |

Table 10. Random 10,000 Gate Circuit | 8x12 Mesh | 3x3 Core Size | Code Distance 3 | 480 Logical Qubits | 60/40 one-qubit gate/two-qubit gate.

| Stats-Mapping | Part.+ QAPFA | Part.   | Random  |

|---------------|--------------|---------|---------|

| Traffic(bits) | 5499568      | 5776172 | 6766422 |

placement optimization, a significant improvement in decoding cycles and EPR pairs is observed relative to random mapping.

Apart from these results, our framework also tracks statistics regarding the classical communication. Specifically, we count all the measurement results and circuit instructions that must be routed between cores. Tables 9,10, and 11 report the total amount of classical bits to complete execution of the circuit. These bits are routed from core-to-core as illustrated in Figure 9.

These three benchmarks provide a useful comparison of layouts. Although the ratio of the total volume between the table layouts (number of gates  $\times$  number of qubits) is similar, post-optimized traffic between Table 9 and Table 11 shows a great difference. The layout in Table 11 results in

Table 11. Random 10,000 Gate Circuit | 6x6 Mesh | 5x5 Core Size | Code Distance 3 | 468 Logical Qubits | 60/40 one-qubit gate/two-qubit.

| Stats-Mapping | Part.+ QAPFA | Part.   | Random  |

|---------------|--------------|---------|---------|

| Traffic(bits) | 3982107      | 4124900 | 4716853 |

better traffic-to-volume ratio, since the cores are larger and the need for inter-core operations is lower compared to the layout in Tables 9 and 10.

#### 8 Conclusion and Future Work

In this work, we constructed a system that can be used to understand the necessary resources for DQC with logical qubits. We have completed a three-phase process. First, we designed a scheduling algorithm that uses a network of ancilla qubits to route the logical states from one position to another. Then, we used a classical NoC to emulate the classical traffic for all these operations. This gives a clear understanding of classical resource consumptions and timing of a quantum circuit that use this system. Finally, we designed a robust mapping framework that takes care of minimizing the two-qubit gates between cores while also optimizing the total travel of magic states for the T and S gates. We think that this approach is wise for two points. Firstly, it reduces the routing of magic states for better quality T and S gates. Secondly, it places the qubits that are used for the T and S gates preferentially close to a point. This could bring advantages since these logical qubits should be decoded with a higher priority over other qubits. Essentially, the core idea is to approach the two-qubit gates and the T gates jointly. Such a system should reduce the inter-core CNOTs. At the same time, it should also give a higher priority to the qubits that have more T and S gates, since for decoding and better quality magic states, these qubits should be placed near the MSF and decoder units.

This work could be extended by incorporating decoders and an additional optimization layer for their placement. Decoders are a crucial component of fault-tolerant quantum applications, and it would be valuable to investigate how they influence classical resource consumption as well as the compilation of quantum circuits. An interesting direction for another potential future work is to study the role of EPR pair distribution in this framework. Optimizing how entanglement is generated, allocated, and consumed could reveal important trade-offs between classical resource usage and quantum circuit compilation. Adding an optimization layer dedicated to entanglement management would provide significant insights and benefits to our proposed framework.

## 9 Acknowledgments

Authors acknowledge funding from the EC through HORIZON-EIC-2022-PATHFINDEROPEN-01-101099697 (QUADRATURE).

#### References

[1] Gadi Aleksandrowicz, Thomas Alexander, Panagiotis Barkoutsos, Luciano Bello, Yael Ben-Haim, David Bucher, Francisco Jose Cabrera-Hernández, Jorge Carballo-Franquis, Adrian Chen, Chun-Fu Chen, Jerry M. Chow, Antonio D. Córcoles-Gonzales, Abigail J. Cross, Andrew Cross, Juan Cruz-Benito, Chris Culver, Salvador De La Puente González, Enrique De La Torre, Delton Ding, Eugene Dumitrescu, Ivan Duran, Pieter Eendebak, Mark Everitt, Ismael Faro Sertage, Albert Frisch, Andreas Fuhrer, Jay Gambetta, Borja Godoy Gago, Juan Gomez-Mosquera, Donny Greenberg, Ikko Hamamura, Vojtech Havlicek, Joe Hellmers, Łukasz Herok, Hiroshi Horii, Shaohan Hu, Takashi Imamichi, Toshinari Itoko, Ali Javadi-Abhari, Naoki Kanazawa, Anton Karazeev, Kevin Krsulich, Peng Liu, Yang Luh, Yunho Maeng, Manoel Marques, Francisco Jose Martín-Fernández, Douglas T. McClure, David McKay, Srujan Meesala, Antonio Mezzacapo, Nikolaj Moll, Diego Moreda Rodríguez, Giacomo Nannicini, Paul Nation, Pauline Ollitrault, Lee James O'Riordan,

Hanhee Paik, Jesús Pérez, Anna Phan, Marco Pistoia, Viktor Prutyanov, Max Reuter, Julia Rice, Abdón Rodríguez Davila, Raymond Harry Putra Rudy, Mingi Ryu, Ninad Sathaye, Chris Schnabel, Eddie Schoute, Kanav Setia, Yunong Shi, Adenilton Silva, Yukio Siraichi, Seyon Sivarajah, John A. Smolin, Mathias Soeken, Hitomi Takahashi, Ivano Tavernelli, Charles Taylor, Pete Taylour, Kenso Trabing, Matthew Treinish, Wes Turner, Desiree Vogt-Lee, Christophe Vuillot, Jonathan A. Wildstrom, Jessica Wilson, Erick Winston, Christopher Wood, Stephen Wood, Stefan Wörner, Ismail Yunus Akhalwaya, and Christa Zoufal. 2019. *Qiskit: An Open-source Framework for Quantum Computing*. doi:10.5281/zenodo.2562111

- [2] Aziza Almanakly, Beatriz Yankelevich, Max Hays, Bharath Kannan, Réouven Assouly, Alex Greene, Michael Gingras, Bethany M. Niedzielski, Hannah Stickler, Mollie E. Schwartz, Kyle Serniak, Joel Î-j. Wang, Terry P. Orlando, Simon Gustavsson, Jeffrey A. Grover, and William D. Oliver. 2025. Deterministic remote entanglement using a chiral quantum interconnect. Nature Physics 21, 5 (March 2025), 825–830. doi:10.1038/s41567-025-02811-1

- [3] James Ang, Gabriella Carini, Yanzhu Chen, Isaac Chuang, Michael Austin DeMarco, Sophia E. Economou, Alec Eickbusch, Andrei Faraon, Kai-Mei Fu, Steven M. Girvin, Michael Hatridge, Andrew Houck, Paul Hilaire, Kevin Krsulich, Ang Li, Chenxu Liu, Yuan Liu, Margaret Martonosi, David C. McKay, James Misewich, Mark Ritter, Robert J. Schoelkopf, Samuel A. Stein, Sara Sussman, Hong X. Tang, Wei Tang, Teague Tomesh, Norm M. Tubman, Chen Wang, Nathan Wiebe, Yong-Xin Yao, Dillon C. Yost, and Yiyu Zhou. 2022. Architectures for Multinode Superconducting Quantum Computers. arXiv:2212.06167 [quant-ph] https://arxiv.org/abs/2212.06167

- [4] Jonathan M. Baker, Casey Duckering, Alexander Hoover, and Frederic T. Chong. 2020. Time-sliced quantum circuit partitioning for modular architectures. In Proceedings of the 17th ACM International Conference on Computing Frontiers (CF '20). ACM, 98–107. doi:10.1145/3387902.3392617

- [5] H. Bombin and M. A. Martin-Delgado. 2007. Optimal resources for topological two-dimensional stabilizer codes: Comparative study. *Phys. Rev. A* 76 (Jul 2007), 012305. Issue 1. doi:10.1103/PhysRevA.76.012305

- [6] Sergey Bravyi, Oliver Dial, Jay M. Gambetta, Darío Gil, and Zaira Nazario. 2022. The future of quantum computing with superconducting qubits. *Journal of Applied Physics* 132, 16 (Oct. 2022). doi:10.1063/5.0082975

- [7] Sergey Bravyi and Alexei Kitaev. 2005. Universal quantum computation with ideal Clifford gates and noisy ancillas. *Phys. Rev. A* 71 (Feb 2005), 022316. Issue 2. doi:10.1103/PhysRevA.71.022316

- [8] Steven A. Cuccaro, Thomas G. Draper, Samuel A. Kutin, and David Petrie Moulton. 2004. A new quantum ripple-carry addition circuit. arXiv:quant-ph/0410184 [quant-ph] https://arxiv.org/abs/quant-ph/0410184

- [9] Daniele Cuomo, Marcello Caleffi, Kevin Krsulich, Filippo Tramonto, Gabriele Agliardi, Enrico Prati, and Angela Sara Cacciapuoti. 2023. Optimized Compiler for Distributed Quantum Computing. ACM Transactions on Quantum Computing 4, 2, Article 15 (Feb. 2023), 29 pages. doi:10.1145/3579367

- [10] E. W. Dijkstra. 1959. A note on two problems in connexion with graphs. Numer. Math. 1, 1 (Dec. 1959), 269–271. doi:10.1007/BF01386390

- [11] Alexander Erhard, Hendrik Poulsen Nautrup, Michael Meth, Lukas Postler, Roman Stricker, Martin Stadler, Vlad Negnevitsky, Martin Ringbauer, Philipp Schindler, Hans J. Briegel, Rainer Blatt, Nicolai Friis, and Thomas Monz. 2021. Entangling logical qubits with lattice surgery. Nature 589, 7841 (Jan. 2021), 220–224. doi:10.1038/s41586-020-03079-6

- [12] Pau Escofet, Abhijit Das, Sahar Ben Rached, Santiago Rodrigo, Jordi Domingo, Fabio Sebastiano, Masoud Babaie, Batuhan Keskin, Edoardo Charbon, Peter Haring Bolívar, Maurizio Palesi, Elena Blokhina, Bogdan Staszewski, Avishek Nag, Artur Garcia-Sáez, Sergi Abadal, Eduard Alarcón, and Carmen G. Almudéver. 2025. On the Impact of Classical and Quantum Communication Networks Upon Modular Quantum Computing Architecture System Performance. arXiv:2507.08378 [quant-ph] https://arxiv.org/abs/2507.08378

- [13] Pau Escofet, Anabel Ovide, Medina Bandic, Luise Prielinger, Hans van Someren, Sebastian Feld, Eduard Alarcon, Sergi Abadal, and Carmen Almudever. 2025. Revisiting the Mapping of Quantum Circuits: Entering the Multi-core Era. *ACM Transactions on Quantum Computing* 6, 1, Article 4 (Jan. 2025), 26 pages. doi:10.1145/3655029

- [14] Simon J. Evered, Dolev Bluvstein, Marcin Kalinowski, Sepehr Ebadi, Tom Manovitz, Hengyun Zhou, Sophie H. Li, Alexandra A. Geim, Tout T. Wang, Nishad Maskara, Harry Levine, Giulia Semeghini, Markus Greiner, Vladan Vuletić, and Mikhail D. Lukin. 2023. High-fidelity parallel entangling gates on a neutral-atom quantum computer. *Nature* 622 (2023), 268–272. doi:10.1038/s41586-023-06481-y

- [15] Austin G. Fowler and Craig Gidney. 2019. Low overhead quantum computation using lattice surgery. arXiv:1808.06709 [quant-ph] https://arxiv.org/abs/1808.06709

- [16] Daniel Gottesman. 1997. Stabilizer Codes and Quantum Error Correction. arXiv:quant-ph/9705052 [quant-ph] https://arxiv.org/abs/quant-ph/9705052

- [17] Daniel Gottesman and Isaac L. Chuang. 1999. Demonstrating the Viability of Universal Quantum Computation Using Teleportation and Single-Qubit Operations. *Nature* 402 (1999), 390–393. doi:10.1038/46503

- [18] Dominic Horsman, Austin G Fowler, Simon Devitt, and Rodney Van Meter. 2012. Surface code quantum computing by lattice surgery. New Journal of Physics 14, 12 (Dec. 2012), 123011. doi:10.1088/1367-2630/14/12/123011

[19] Hamza Jnane, Brennan Undseth, Zhenyu Cai, Simon C. Benjamin, and Bálint Koczor. 2022. Multicore Quantum Computing. Phys. Rev. Appl. 18 (Oct 2022), 044064. Issue 4. doi:10.1103/PhysRevApplied.18.044064

- [20] V. Kaushal, B. Lekitsch, A. Stahl, J. Hilder, D. Pijn, C. Schmiegelow, A. Bermudez, M. Müller, F. Schmidt-Kaler, and U. Poschinger. 2020. Shuttling-based trapped-ion quantum information processing. AVS Quantum Science 2, 1 (03 2020), 014101. arXiv:https://pubs.aip.org/avs/aqs/article-pdf/doi/10.1116/1.5126186/19738817/014101\_1\_online.pdf doi:10.1116/1.5126186

- [21] A.Yu. Kitaev. 2003. Fault-tolerant quantum computation by anyons. Annals of Physics 303, 1 (Jan. 2003), 2–30. doi:10.1016/s0003-4916(02)00018-0

- [22] Tjalling C. Koopmans and Martin Beckmann. 1957. Assignment Problems and the Location of Economic Activities. *Econometrica* 25, 1 (1957), 53–76. http://www.jstor.org/stable/1907742

- [23] Nicholas LaRacuente, Kaitlin N. Smith, Poolad Imany, Kevin L. Silverman, and Frederic T. Chong. 2025. Modeling Short-Range Microwave Networks to Scale Superconducting Quantum Computation. *Quantum* 9 (Jan. 2025), 1581. doi:10.22331/q-2025-01-08-1581

- [24] Yingling Mao, Yu Liu, and Yuanyuan Yang. 2023. Qubit Allocation for Distributed Quantum Computing. In IEEE INFOCOM 2023 - IEEE Conference on Computer Communications. 1–10. doi:10.1109/INFOCOM53939.2023.10228915

- [25] Jingjing Niu, Libo Zhang, Yang Liu, Jiawei Qiu, Wenhui Huang, Jiaxiang Huang, Hao Jia, Jiawei Liu, Ziyu Tao, Weiwei Wei, Yuxuan Zhou, Wanjing Zou, Yuanzhen Chen, Xiaowei Deng, Xiuhao Deng, Changkang Hu, Ling Hu, Jian Li, Dian Tan, Yuan Xu, Fei Yan, Tongxing Yan, Song Liu, Youpeng Zhong, Andrew N. Cleland, and Dapeng Yu. 2023. Low-loss interconnects for modular superconducting quantum processors. *Nature Electronics* 6, 3 (Feb. 2023), 235–241. doi:10.1038/s41928-023-00925-z

- [26] Maurizio Palesi, Enrico Russo, Davide Patti, Giuseppe Ascia, and Vincenzo Catania. 2024. Assessing the Role of Communication in Scalable Multi-Core Quantum Architectures. In 2024 IEEE 17th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC). IEEE Computer Society, Los Alamitos, CA, USA, 482–489. doi:10.1109/MCSoC64144.2024.00085

- [27] Panagiotis Promponas, Akrit Mudvari, Luca Della Chiesa, Paul Polakos, Louis Samuel, and Leandros Tassiulas. 2024. Compiler for Distributed Quantum Computing: a Reinforcement Learning Approach. arXiv:2404.17077 [quant-ph] https://arxiv.org/abs/2404.17077

- [28] Joshua Ramette, Josiah Sinclair, Nikolas P. Breuckmann, and Vladan Vuletić. 2024. Fault-tolerant connection of error-corrected qubits with noisy links. npj Quantum Information 10, 1 (2024), 58. doi:10.1038/s41534-024-00855-4 Published 10 June 2024.

- [29] Enrico Russo, Maurizio Palesi, Davide Patti, Giuseppe Ascia, and Vincenzo Catania. 2025. Optimizing Qubit Assignment in Modular Quantum Systems via Attention-Based Deep Reinforcement Learning. In 2025 Design, Automation & Test in Europe Conference (DATE). 1–7. doi:10.23919/DATE64628.2025.10992725

- [30] Ciaran Ryan-Anderson, N. C. Brown, C. H. Baldwin, J. M. Dreiling, C. Foltz, J. P. Gaebler, T. M. Gatterman, N. Hewitt, C. Holliman, C. V. Horst, J. Johansen, D. Lucchetti, T. Mengle, M. Matheny, Y. Matsuoka, K. Mayer, M. Mills, S. A. Moses, B. Neyenhuis, J. Pino, P. Siegfried, R. P. Stutz, J. Walker, and D. Hayes. 2024. High-fidelity teleportation of a logical qubit using transversal gates and lattice surgery. Science 385, 6715 (2024), 1327–1331. doi:10.1126/science.adp6016 Epub 2024-09-19; printed 2024-09-20.

- [31] Peter Sanders and Christian Schulz. 2013. Think Locally, Act Globally: Highly Balanced Graph Partitioning. In Experimental Algorithms, 12th International Symposium, SEA 2013, Rome, Italy, June 5-7, 2013. Proceedings, Vol. 7933. Springer, 164–175.

- [32] Kaitlin N. Smith, Gokul Subramanian Ravi, Jonathan M. Baker, and Frederic T. Chong. 2022. Scaling Superconducting Quantum Computers with Chiplet Architectures. In 2022 55th IEEE/ACM International Symposium on Microarchitecture (MICRO). 1092–1109. doi:10.1109/MICRO56248.2022.00078

- [33] Evan Sutcliffe, Bhargavi Jonnadula, Claire Le Gall, Alexandra E. Moylett, and Coral M. Westoby. 2025. Distributed quantum error correction based on hyperbolic Floquet codes. arXiv:2501.14029 [quant-ph] https://arxiv.org/abs/2501. 14029

- [34] E. Taillard. 1991. Robust taboo search for the quadratic assignment problem. Parallel Comput. 17, 4 (1991), 443–455. doi:10.1016/S0167-8191(05)80147-4

- [35] Éric D. Taillard. 1995. Comparison of iterative searches for the quadratic assignment problem. *Location Science* 3, 2 (1995), 87–105. doi:10.1016/0966-8349(95)00008-6

- [36] Anbang Wu, Yufei Ding, and Ang Li. 2023. QuComm: Optimizing Collective Communication for Distributed Quantum Computing. In Proceedings of the 56th Annual IEEE/ACM International Symposium on Microarchitecture (Toronto, ON, Canada) (MICRO '23). Association for Computing Machinery, New York, NY, USA, 479–493. doi:10.1145/3613424. 3614253