# Sneak Path Current Modeling in Memristor Crossbar Arrays for Analog In-Memory Computing

Shah Zayed Riam\*, Zhenlin Pei\*, *Graduate Student Member, IEEE*, Kyle Mooney, *Graduate Student Member, IEEE*, Chenyun Pan, *Senior Member, IEEE*, Na Gong, *Senior Member, IEEE*, and Jinhui Wang, *Senior Member, IEEE*.

Abstract-Memristor crossbar arrays have emerged as a key component for next-generation non-volatile memories, artificial neural networks, and analog in-memory computing (IMC) systems. By minimizing data transfer between the processor and memory, they offer substantial energy savings. However, a major design challenge in memristor crossbar arrays is the presence of sneak path currents, which degrade electrical performance, reduce noise margins, and limit reliable operations. This work presents a closed-form analytical framework based on IMEC A14 (1.4 nm) Technology for accurately estimating sneak path currents in memristor crossbar arrays. The proposed model captures the interdependence of key design parameters in memristor crossbar arrays, including array size, ON/OFF ratio of memristors, read voltage, and interconnect conditions, through mathematically derived relationships. It supports various practical configurations, such as different data patterns and connection strategies, enabling rapid and comprehensive sneak path current modeling. The sensitivity analysis includes how design parameters influence sneak path current and noise margin loss, underscoring the trade-offs involved in scaling crossbar arrays. Validation through SPICE simulations shows that the model achieves an error of less than 10.9% while being up to 4784 times faster than full circuit simulations. This analytical framework offers a powerful tool for quantitative assessment and pre-design/real-time optimization of memristor-based analog inmemory computing (IMC) architectures.

Index Terms—sneak path current, closed-form expression, memristor crossbar array

## I. INTRODUCTION

EMRISTOR, widely recognized as the fourth fundamental circuit element, has become central to the development of next-generation non-volatile memory technologies and emerging analog in-memory computing (IMC) systems, addressing the scaling and efficiency challenges of traditional CMOS-based memories [1]–[7]. The primary architectural manifestation of memristor-based memory is the high-density passive crossbar array, where each cell is located at the intersection of perpendicular wordlines and bitlines [8], [9].

This work is supported in part by the National Science Foundation under grants 2510192, 2502054, 2428981, 2420994, 2427766, 2408064, 2247343, and 2218046. This material was also based upon work supported by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research (ASCR), under Award Number(s) DE-SC0025561. (Corresponding author: Jinhui Wang)

Shah Zayed Riam, Zhenlin Pei, Kyle Mooney, Na Gong, and Jinhui Wang are with the Department of Electrical and Computer Engineering, The University of Alabama, Tuscaloosa, AL 35487 USA (e-mail: jwang231@ua.edu).

Chenyun Pan is with the Department of Electrical Engineering, The University of Texas at Arlington, Arlington, TX 76010 USA.

\*Denotes equal contribution and co-first author.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org

This structure provides exceptional storage density since each cell can be scaled to the nanometer regime without requiring a transistor [10], [11], thereby offering higher bit-per-area ratios than conventional memories [12]. Combined with its non-volatility and fast read capability, the memristor crossbar helps bridge the performance gap in modern memory hierarchies [13]-[16]. Additionally, memristor plays a crucial role in analog computing by enabling fast and direct hardware implementation of vector matrix multiplication in-memory, such as in a neuromorphic computing system. Memristors can perform computation intrinsically through Ohm's and Kirchhoff's laws when placed in crossbar arrays. The output current produced is in the form of weighted summations of input voltage and stored conductance of the memristor. This characteristic of analog IMC results in highly parallel, energyefficient acceleration for signal processing and Artificial Intelligence (AI) tasks, as it removes the need for frequent data transfer between memory and processors [17].

However, a key challenge in fully realizing the advantages of passive memristor crossbar arrays is the sneak path current [18]. Sneak paths are unwanted parallel current routes that occur during read operations, diverting current away from the target cell. In unoptimized crossbars, sneak path currents can dominate the total current by exceeding 50%, leading to substantial read errors and increased power consumption [19]. The absence of gating elements and the fully connected structure of the crossbar cause currents to flow preferentially through low-resistance cells [20], inevitably creating a parallel resistance network that distorts readouts and causes highresistance state (HRS) to be misinterpreted as low-resistance state (LRS) [21]. Moreover, the magnitude and distribution of these parasitic currents are highly data-dependent, varying dynamically with the stored information [22] or data patterns. Analyzing sneak path currents during the pre-design and ongoing design phases is crucial, as their data-dependent variability poses significant reliability challenges [23]. Without precise estimation of these parasitic currents, it becomes difficult to ensure stable performance in terms of noise margin, functional yield, and maximum achievable array size [24].

Some research has focused on mitigating this issue through various strategies. Architectural approaches often incorporate gating elements, such as diodes, transistors, or additional memristors, to suppress unwanted current flow, although at the cost of reduced array density. Alternatively, gateless techniques leverage multi-point read schemes, coding strategies, or logical operations to achieve sneak path free reading [25]–[30]. However, the above studies only limit to the individual

aspects such as data patterns, connection configurations, read voltages, or array sizes, rather than capture the combined influence of all key parameters. Consequently, a unified analytical framework that comprehensively models sneak path behavior across multiple interacting factors remains largely unexplored. In addition, recent Computer-Aided Design (CAD) frameworks such as CiMLoop [31], DNN+NeuroSim [32], MNSIM [33], and CrossSim [34] have advanced the modeling and co-design of IMC architectures. For example, CiMLoop enables full-stack exploration from device to architecture; DNN+NeuroSim provides circuit to algorithm benchmarking for SRAM and emerging non-volatile memories; MNSIM supports hierarchical modeling of digital and analog IMC architectures; and CrossSim simulates ReRAM-based neural training under realistic device nonidealities. However, these tools neither consider sneak path effects nor employ purely passive memristor arrays; instead, they depend on selector or switching devices to mitigate interference, which substantially limits memory density. This highlights the need for a comprehensive analytical framework dedicated to modeling sneak path phenomena in high-density passive crossbar arrays.

A multi-parameter closed-form analytical model is proposed in this paper to provide a unified framework for evaluating the combined influence of critical design parameters, including device conductance (ON/OFF ratio of memristor), array size, read voltage, interconnect resistance, data patterns, and connection strategies. The proposed approach enables accurate pre-design/real-time estimations of key performance indicators such as functional yield, noise margin, and maximum feasible array size, thereby supporting the development of robust and predictable memristor-based architectures. Compared with conventional SPICE simulations, the proposed closed-form model offers several advantages: (1) Speed and efficiency: it provides immediate analytical results, whereas SPICE requires extensive computation, particularly for large arrays with numerous parasitic components; (2) Scalability: the closed-form model can efficiently handle analyses involving thousands or millions of devices, while SPICE simulations slow down significantly as system size increases; (3) Analytical clarity: unlike SPICE, which produces purely numerical outputs, the closed-form approach reveals explicit relationships among parameters such as resistance, voltage, and current; (4) Design optimization: it allows designers to quickly explore trade-offs in parameters like array size and bias voltage without iterative simulations; and (5) Integration with design tools: the derived equations can be easily incorporated into CAD workflows for rapid performance estimation during schematic, layout or system-level design, whereas SPICE models are less adaptable for high-level design automation. This paper will make the following contributions:

- The dependence of the sneak path current in the memristor crossbar array is analyzed for important circuit parameters.

- A closed-form model is proposed for the accurate and efficient estimation of the sneak path current in memristor arrays, and its accuracy and run-time performance are validated against SPICE simulations.

- The sensitivity and noise margins of the sneak path current in the memristor crossbar array are also modeled and deeply analyzed.

- The closed-form model is further compared with the state-of-the-art.

This paper is organized into the following sections. In Section II, models and parameters for the memristor, the interconnect network, and closed-form expressions are presented along with the connection mechanism in array configuration. The results and discussions for the sneak path current, noise margin, the effect of interconnect resistance, sensitivity analysis, and model validation are presented in Section III. Performance and property comparison with the state-of-theart is provided in Section IV. Finally, this paper is concluded in Section V.

#### II. METHODOLOGY

#### A. Design Considerations

The foundation of this analysis is the nanoscale crossbar memristor model presented in [35] based on HP Technology, where the device current is defined in the following equation:

$$I = K \sinh(\alpha V) \tag{1}$$

where  $\alpha$  indicates the degree of nonlinearity in the device. It indicates the sensitive change of device characteristics due to a unit change in voltage. I and V represent the current and voltage, respectively. The parameter K is analogous to the electrical conductance of a linear resistance.

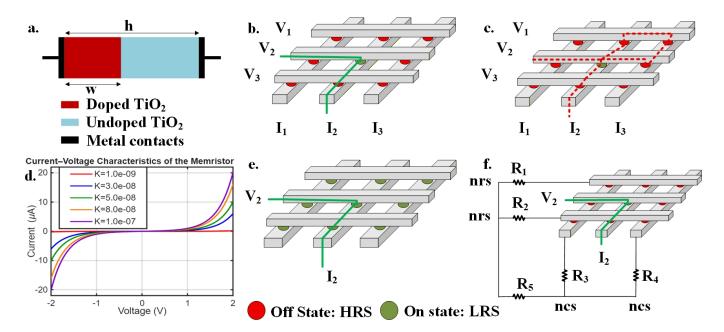

In this configuration, a TiO<sub>2</sub> layer for a total thickness of the device,  $h \leq 10$  nm, is sandwiched between two platinum electrodes. The oxide layer has two constituent layers: a doped region containing oxygen vacancies and an undoped region composed of pure TiO<sub>2</sub>, as shown in Fig. 1 (a). This work is conducted using a parameter value of  $\alpha = 3$  [36] and current versus voltage characteristic for the memristor is shown in Fig. 1 (d) [35].

The current method presented in this paper employs the constant Kon and Koff as the ON and OFF states, respectively. To comprehensively assess the influence of sneak path currents, two representative data patterns are simulated: the 'All Zeros' pattern (best case scenario, minimum sneak path current effect, all the memristors are in the OFF state and the sneak paths are made of OFF resistances in series); and the 'All Ones' pattern (worst case scenario, maximum sneak path current effect). Grounded unselected rows and columns has been explored as a method to mitigate sneak path currents. Grounded rows and columns of unselected cells in an array provides alternating paths for leakage currents to flow instead of the sensing circuit. However, part of the sneak path current still flows through the sense circuit. Four terminal biasing configurations are analyzed: Floating Rows and Columns (FRC), Grounded Rows with Floating Columns (GRFC), Floating Rows with Grounded Columns (FRGC), and Grounded Rows and Columns (GRC), to examine the impact of different connection strategies on the overall array behavior. The grounded rows and columns are implemented using  $0.001\,\Omega$  resistors (near zero), with the corresponding

Fig. 1: (a) Structure of the linear dopant drift memristor model. h represents the total thickness of the device. w represents the thickness of the doped region; (d) Current versus voltage characteristic for the memristor [35]. A  $3 \times 3$  memristive crossbar, where  $V_{dd} = V_2$  is the voltage applied in row 2, and current sensed from column 2: (b) the crossbar without sneak paths where the desired current path is marked in green line, (c) presence of a sneak path which is marked in red line, (e) FRC connection strategy with 'All Ones' (LRS) data pattern, (f) GRC connection strategy with 'All Zeros' (HRS) data pattern. Here, in GRC connection strategy, shorted row nodes are indicated as "nrs" and shorted column nodes are indicated as "ncs".

nodes labeled as node row shorted and node column shorted, respectively.

Fig. 1 presents an abstract depiction of the sneak path phenomenon in the crossbar array, along with schematic representations to illustrate the different combinations of data patterns and connection strategies. The device at the center of the array is the "target device," and the devices sharing a line with the target are called "half-selected devices". To read the "target device", the selected row is pulled up to V<sub>dd</sub> and the selected column is grounded through a resistor. Sneak path occurs when current flows from V<sub>dd</sub> to ground through unselected devices. Therefore, it affects the accuracy of the read operation by degrading the voltage and current delivered to the device. The crossbar interconnect network is modeled at the unit-cell level to accurately capture parasitic effects, incorporating line resistance, stray capacitance to ground, and fringing capacitance between adjacent lines. In this work, the interconnect design dimensions follow the IMEC A14 (1.4 nm) technology node, offering concrete guidance for both academic researchers and industry engineers [37]–[42]. For the IMEC A14 interconnect, metal layers M1 and M2 are primarily employed for internal interconnect within the cell. Layers M1 and M3 exhibit identical geometries, as do M4 and M5. However, M3 can be used for local interconnect within subarrays, and M4 and M5 are for intermediate-level interconnect. Metal layers M6 and above maintain consistent geometries for intermediate- and global-level interconnects. Consequently, layers M3, M5, and M6 are selected to represent interconnects spanning from local to global scales and are

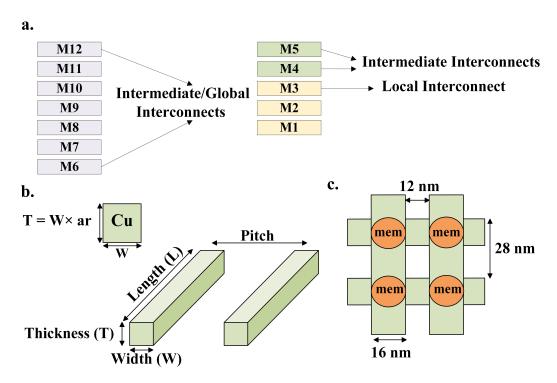

investigated. Fig. 2 (a) presents the utility of metal layers (M1~M12) for different interconnects. The geometry of the Cu interconnect and the pitch (P) is shown in Fig. 2 (b). Here, W, T represent the width and thickness of Cu. The thickness is represented as the product of the width (W) and aspect ratio (ar), and the pitch (P) represents the distance between the centers of two adjacent interconnects. The unit-cell memristor array is shown in Fig. 2 (c) with the corresponding values of W, T, and P. The selected interconnect metal layers provide different parasitic resistance  $R_{\text{line}}$  and capacitance  $C_{\text{line}}$ . The corresponding ranges of interconnect parameters are listed in Table I.

TABLE I: Interconnect Geometry, Resistance, and Capacitance

| Metal | W(nm) | P(nm) | T(nm) | $R_{\mathrm{line}}(\Omega)$ | $C_{\text{line}}(fF)$ |

|-------|-------|-------|-------|-----------------------------|-----------------------|

| M3    | 16    | 28    | 49    | 3.122                       | 3.871e-3              |

| M5    | 16    | 28    | 28    | 5.869                       | 2.871e-3              |

| M6    | 40    | 80    | 80    | 0.7396                      | 1.020e-2              |

TABLE II: Boundary Conditions for Closed-form Models

| Para. | Boundary  | Para.    | Boundary  | Para.    | Boundary |

|-------|-----------|----------|-----------|----------|----------|

| Size  | 4×4:64×64 | $K_{on}$ | 1e-9:1e-7 | $V_{dd}$ | 1V:3V    |

# B. Closed-form Model

Closed-form expressions for the sneak current are presented corresponding to different input variables, e.g., Size (Array Size),  $K_{on}$  (ON/OFF ratio), and  $V_{dd}$  (Read Voltage), as Equation (2). The boundaries for closed-form equation fitting are

Fig. 2: (a) Metal layers M1~M12 are used for interconnect within the cell; (b) Sketch of Cu for interconnect material; (c) Top view of a unit-cell memristor crossbar array for M5/M4 with IMEC A14.

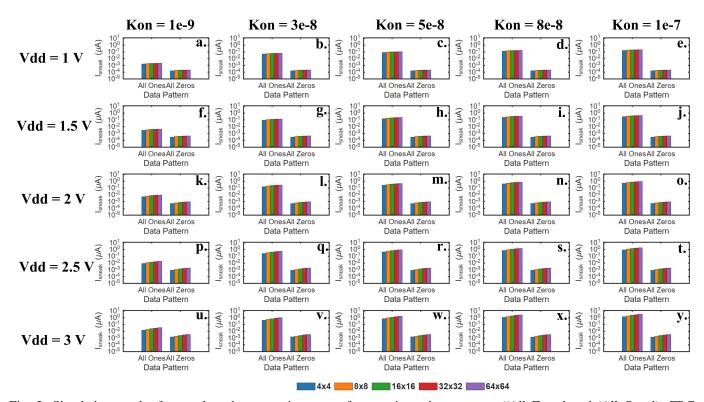

Fig. 3: Simulation results for sneak path current in terms of array sizes, data patterns ('All Zeros' and 'All Ones'), FRC connection strategy, and line resistance M3 ( $R_{line} = 3.122\,\Omega$ ) where the read voltages are incremented along the rows and ON/OFF ratio is incremented along the columns of the subplots. The rise in sneak path current with respect to the increment of the ON/OFF ratio along the columns as  $K_{on} = [1e-9, 3e-8, 5e-8, 8e-8, 1e-7]$  for a specific read voltage: (a~e)  $V_{dd} = 1.0\,V$ ; (f~j)  $V_{dd} = 1.5\,V$ ; (k~o)  $V_{dd} = 2.0\,V$ ; (p~t)  $V_{dd} = 2.5\,V$ ; (u~y)  $V_{dd} = 3\,V$ . Noticeably, for 'All Ones' pattern the sneak path current increases rapidly for the increments of read voltage, ON/OFF ratio, array size compared to the minimal increment of All Zeros data pattern.

TABLE III: Coefficients of Closed-form Expression for M3

| Coeff.   | All 1s FRC    | All 1s GRFC   | All 1s FRGC   | All 1s GRC    | All 0s FRC    | All 0s GRFC   | All 0s FRGC   | All 0s GRC    |

|----------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| $C_1$    | -2.765766e-04 | -5.271610e-04 | -3.118053e-05 | -3.422062e-05 | -2.768951e-04 | -5.173225e-04 | 6.728880e-08  | 7.209101e-08  |

| $C_2$    | -3.552098e-05 | -7.224109e-04 | -9.791516e-04 | -9.441148e-04 | -2.337750e-05 | -7.911723e-05 | -1.496197e-04 | -1.496397e-04 |

| $C_3$    | 4.599539e-03  | 2.568702e-03  | -3.942867e-03 | -3.851644e-03 | 4.602914e-03  | 4.479660e-03  | -8.406540e-04 | -8.401264e-04 |

| $C_4$    | 1.722779e-02  | 3.588961e-02  | -1.070919e-02 | -9.972648e-03 | 1.747226e-02  | 4.457329e-02  | -1.435455e-03 | -1.437187e-03 |

| $C_5$    | -4.296973e-04 | -9.912720e-03 | -3.415353e-02 | -3.305335e-02 | -1.110902e-03 | -1.103802e-03 | -2.031960e-03 | -2.030510e-03 |

| $C_6$    | -1.275372e-03 | -2.229373e-02 | -1.746779e-01 | -1.730254e-01 | -1.192496e-03 | -3.191236e-03 | -6.087109e-03 | -6.086547e-03 |

| $C_7$    | 9.867175e-01  | 6.749072e-01  | -2.319980e-02 | 1.489677e-02  | -3.901237e-02 | -3.450177e-02 | -6.308356e-02 | -6.303070e-02 |

| $C_8$    | -1.056307e-01 | -1.838965e-01 | -3.936425e-01 | -3.919864e-01 | -1.029701e-01 | -1.556039e-01 | -2.579691e-02 | -2.578021e-02 |

| $C_9$    | 1.529703e+00  | 1.871899e+00  | 1.029943e+00  | 1.054458e+00  | 1.521661e+00  | 2.102373e+00  | 2.995661e+00  | 2.995596e+00  |

| $C_{10}$ | -1.154712e+00 | -3.592643e+00 | -8.795638e+00 | -8.468067e+00 | -2.441334e+01 | -2.416504e+01 | -2.428478e+01 | -2.428423e+01 |

TABLE IV: Coefficients of Closed-form Expression for M5

| Coeff.   | All 1s FRC    | All 1s GRFC   | All 1s FRGC   | All 1s GRC    | All 0s FRC    | All 0s GRFC   | All 0s FRGC   | All 0s GRC    |

|----------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| $C_1$    | -2.764303e-04 | -5.369728e-04 | -3.317372e-05 | -3.607482e-05 | -2.795334e-04 | -5.162575e-04 | 1.109504e-06  | 1.100590e-06  |

| $C_2$    | -5.936502e-05 | -1.011910e-03 | -1.426496e-03 | -1.405009e-03 | -4.490970e-05 | -1.323556e-04 | -2.524449e-04 | -2.524109e-04 |

| $C_3$    | 4.487461e-03  | 1.771752e-03  | -5.595220e-03 | -5.549250e-03 | 4.561308e-03  | 4.208091e-03  | -1.425890e-03 | -1.425737e-03 |

| $C_4$    | 1.695349e-02  | 3.218355e-02  | -1.690781e-02 | -1.636382e-02 | 1.732497e-02  | 4.394577e-02  | -2.493809e-03 | -2.492790e-03 |

| $C_5$    | -7.048080e-04 | -1.162975e-02 | -3.488875e-02 | -3.399748e-02 | -2.417057e-04 | -1.852363e-03 | -3.402301e-03 | -3.402806e-03 |

| $C_6$    | -2.179162e-03 | -2.706075e-02 | -1.823875e-01 | -1.810900e-01 | -1.532339e-03 | -5.523961e-03 | -1.053107e-02 | -1.053004e-02 |

| $C_7$    | 9.783429e-01  | 6.228614e-01  | -3.333252e-02 | -2.208753e-03 | -5.741777e-03 | -5.769302e-02 | -1.051583e-01 | -1.051793e-01 |

| $C_8$    | -1.081555e-01 | -1.901170e-01 | -3.993790e-01 | -3.982103e-01 | -1.062961e-01 | -1.624248e-01 | -4.035391e-02 | -4.034864e-02 |

| $C_9$    | 1.524105e+00  | 1.817728e+00  | 9.227569e-01  | 9.431813e-01  | 1.527636e+00  | 2.088758e+00  | 2.976207e+00  | 2.976206e+00  |

| $C_{10}$ | -1.225103e+00 | -4.002326e+00 | -8.767657e+00 | -8.499305e+00 | -2.411070e+01 | -2.436257e+01 | -2.464774e+01 | -2.464794e+01 |

TABLE V: Coefficients of Closed-form Expression for M6

| Coeff.   | All 1s FRC    | All 1s GRFC   | All 1s FRGC   | All 1s GRC    | All 0s FRC    | All 0s GRFC   | All 0s FRGC   | All 0s GRC    |

|----------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| $C_1$    | -2.765330e-04 | -5.136305e-04 | -1.469021e-05 | -1.697019e-05 | -2.744689e-04 | -5.168549e-04 | -1.772653e-07 | -1.834111e-07 |

| $C_2$    | -9.275605e-06 | -3.903261e-04 | -3.335456e-04 | -2.664594e-04 | -1.905130e-05 | -2.198834e-05 | -3.958725e-05 | -3.958864e-05 |

| $C_3$    | 4.723620e-03  | 3.578035e-03  | -1.398252e-03 | -1.188272e-03 | 4.644600e-03  | 4.760412e-03  | -2.236606e-04 | -2.236878e-04 |

| $C_4$    | 1.751128e-02  | 3.976450e-02  | -3.205943e-03 | -2.113479e-03 | 1.729086e-02  | 4.514727e-02  | -3.611497e-04 | -3.607864e-04 |

| $C_5$    | -1.186960e-04 | -7.747277e-03 | -3.295507e-02 | -3.143524e-02 | -6.912710e-04 | -2.288891e-04 | -5.495305e-04 | -5.487445e-04 |

| $C_6$    | -3.378056e-04 | -1.659931e-02 | -1.633178e-01 | -1.609204e-01 | -5.466582e-05 | -7.376962e-04 | -1.586451e-03 | -1.588074e-03 |

| $C_7$    | 9.963053e-01  | 7.411125e-01  | -5.549090e-03 | 4.635883e-02  | -2.498576e-02 | -6.894301e-03 | -1.715344e-02 | -1.712207e-02 |

| $C_8$    | -1.029360e-01 | -1.751892e-01 | -3.814526e-01 | -3.785520e-01 | -1.014793e-01 | -1.482829e-01 | -1.070043e-02 | -1.069628e-02 |

| $C_9$    | 1.534969e+00  | 1.929448e+00  | 1.164724e+00  | 1.196345e+00  | 1.538061e+00  | 2.116129e+00  | 3.012977e+00  | 3.012930e+00  |

| $C_{10}$ | -1.073100e+00 | -3.058583e+00 | -8.790361e+00 | -8.344802e+00 | -2.429351e+01 | -2.392658e+01 | -2.388512e+01 | -2.388481e+01 |

selected to encompass the full range of practical circuit biasing conditions and fabrication considerations. The corresponding ranges are listed in Table II. As shown in Equation (2), the corresponding coefficients are summarized in Tables III, IV, V.

$$I_{sneak} = exp(C_1 \cdot Size^2 + C_2 \cdot Size \cdot ln(K_{on}) + C_3 \cdot Size \cdot V_{dd} + C_4 \cdot Size + C_5 \cdot ln(K_{on})^2 + C_6 \cdot ln(K_{on}) \cdot V_{dd} + C_7 \cdot ln(K_{on}) + C_8 \cdot V_{dd}^2 + C_9 \cdot V_{dd} + C_{10})$$

(2)

# III. RESULTS AND DISCUSSION

# A. Sneak Path Current Analysis

The sneak path effect is examined for different memristor crossbar array sizes; the analysis also includes a range of device parameters and data patterns. The magnitude of the sneak path current and the corresponding array size have a strong correlation. As the size of the array increases, the number of potential parallel sneak paths increases, leading to an increase in the current value of the sneak path for a given memristor resistance at a given input voltage value. Fig. 3 demonstrates the scalability challenge, where dense arrays face exponentially worse sneak path issues. The effect

of the data pattern in the array is also shown in Fig. 3, where all memristors are in a LRS, creating the maximum number of low-resistance parallel paths. Consequently, the "All Ones" pattern consistently results in the highest sneak path current across all array sizes and parameter sets. Similarly, all memristors with a HRS present the highest overall resistance to current flow. As a result, the "All Zeros" pattern consistently yields the lowest sneak path currents in all tested conditions. Additionally, Fig. 3 illustrates how different device parameters can either mitigate or aggravate the sneak path problem. Considering the FRC connection strategy with M3 as the interconnect metal, the dependence of Kon value and Vdd value highly influences the sneak path current as shown in Fig. 3 (ay). As the read voltage  $(V_{dd})$  increases from 1 V to 3 V with a step size of 0.5 V, a significant increase in sneak path current can be observed in Fig. 3 (a, f, k, p, u). The K<sub>on</sub> values are swept while keeping the V<sub>dd</sub> fixed, and the trend of sneak path current is observed across five rows in Fig. 3. The first row indicates the sweeping of Kon with a linear increment for a fixed V<sub>dd</sub>, while the next four rows have similar K<sub>on</sub> sweeping but have different V<sub>dd</sub> values across consecutive rows. As the ON/OFF ratio of memristor gets increased by having K<sub>off</sub> set at 1e-10, and changing K<sub>on</sub> to 1e-9, 3e-8, 5e-8, 8e-8, and 1e-7, the sneak path current also increases,

| D-44    | Cturt    | M-4-1 | Size:8×8, k   | Con:3e-8, Vd | d:1.5V   | Size:16×16,   | Kon:5e-8, V | Vdd:2V   | Size:32×32,   | Kon:8e-8, V | dd:2.5V  |

|---------|----------|-------|---------------|--------------|----------|---------------|-------------|----------|---------------|-------------|----------|

| Pattern | Strategy | Metal | Simulation(A) | Error        | Run-time | Simulation(A) | Error       | Run-time | Simulation(A) | Error       | Run-time |

| All 1s  | FRC      | M3    | 1.089e-07     | -7.017%      | 1916×    | 3.896e-07     | -6.257%     | 835×     | 1.312e-06     | 2.163%      | 2030×    |

| All 1s  | FRC      | M5    | 1.089e-07     | -6.895%      | 768×     | 3.895e-07     | -6.213%     | 159×     | 1.307e-06     | 2.052%      | 4784×    |

| All 1s  | FRC      | M6    | 1.089e-07     | -7.151%      | 1132×    | 3.897e-07     | -6.319%     | 1466×    | 1.316e-06     | 2.325%      | 1821×    |

| All 1s  | GRFC     | M3    | 3.608e-07     | -6.321%      | 1198×    | 1.866e-06     | -7.207%     | 62×      | 8.210e-06     | 7.760%      | 1777×    |

| All 1s  | GRFC     | M5    | 3.608e-07     | -5.789%      | 1103×    | 1.861e-06     | -7.205%     | 2048×    | 7.935e-06     | 7.308%      | 1464×    |

| All 1s  | GRFC     | M6    | 3.609e-07     | -6.993%      | 690×     | 1.870e-06     | -7.405%     | 1355×    | 8.479e-06     | 8.717%      | 1023×    |

| All 1s  | FRGC     | M3    | 1.312e-06     | 10.573%      | 730×     | 8.314e-06     | -4.316%     | 542×     | 2.969e-05     | -3.853%     | 1618×    |

| All 1s  | FRGC     | M5    | 1.312e-06     | 10.857%      | 1378×    | 8.202e-06     | -4.910%     | 137×     | 2.669e-05     | -2.296%     | 1561×    |

| All 1s  | FRGC     | M6    | 1.313e-06     | 10.043%      | 43×      | 8.415e-06     | -3.978%     | 888×     | 3.336e-05     | -4.605%     | 1876×    |

| All 1s  | GRC      | M3    | 1.313e-06     | 10.260%      | 10×      | 8.331e-06     | -4.263%     | 1024×    | 3.014e-05     | -4.124%     | 1230×    |

| All 1s  | GRC      | M5    | 1.312e-06     | 10.618%      | 172×     | 8.218e-06     | -4.857%     | 779×     | 2.703e-05     | -2.529%     | 1694×    |

| All 1s  | GRC      | M6    | 1.313e-06     | 9.584%       | 1091×    | 8.433e-06     | -3.967%     | 2426×    | 3.401e-05     | -4.837%     | 1698×    |

| All 0s  | FRC      | M3    | 3.630e-10     | -6.942%      | 826×     | 7.800e-10     | -6.381%     | 305×     | 1.640e-09     | 2.166%      | 1539×    |

| All 0s  | FRC      | M5    | 3.630e-10     | -7.075%      | 746×     | 7.800e-10     | -6.337%     | 1392×    | 1.630e-09     | 2.753%      | 1646×    |

| All 0s  | FRC      | M6    | 3.630e-10     | -6.964%      | 214×     | 7.800e-10     | -6.286%     | 1382×    | 1.650e-09     | 1.980%      | 1229×    |

| All 0s  | GRFC     | M3    | 1.208e-09     | -8.582%      | 123×     | 3.810e-09     | -7.350%     | 1269×    | 1.162e-08     | 8.837%      | 1385×    |

| All 0s  | GRFC     | M5    | 1.208e-09     | -8.254%      | 977×     | 3.810e-09     | -7.298%     | 1489×    | 1.151e-08     | 8.491%      | 1672×    |

| All 0s  | GRFC     | M6    | 1.208e-09     | -8.930%      | 684×     | 3.820e-09     | -7.701%     | 319×     | 1.171e-08     | 9.336%      | 1873×    |

| All 0s  | FRGC     | M3    | 4.499e-09     | 1.050%       | 965×     | 2.013e-08     | 0.573%      | 600×     | 8.839e-08     | -1.321%     | 1827×    |

| All 0s  | FRGC     | M5    | 4.499e-09     | 1.765%       | 1263×    | 2.011e-08     | 0.837%      | 1352×    | 8.686e-08     | -2.087%     | 1814×    |

| All 0s  | FRGC     | M6    | 4.500e-09     | 0.283%       | 774×     | 2.016e-08     | 0.167%      | 1615×    | 8.978e-08     | -0.420%     | 1167×    |

| All 0s  | GRC      | M3    | 4.499e-09     | 1.049%       | 806×     | 2.013e-08     | 0.571%      | 1176×    | 8.839e-08     | -1.321%     | 1748×    |

| All 0s  | GRC      | M5    | 4.499e-09     | 1.765%       | 954×     | 2.011e-08     | 0.837%      | 930×     | 8.686e-08     | -2.085%     | 945×     |

| All 0s  | GRC      | M6    | 4.500e-09     | 0.281%       | 1078×    | 2.016e-08     | 0.166%      | 1455×    | 8.978e-08     | -0.421%     | 800×     |

TABLE VI: Sneak Path Current Model Validation: Simulation Results, Errors, and Normalized Run-time Improvement

which is observed in Fig. 3. Noticeably, the sneak path current is negligible for small array sizes, but increases significantly for large array sizes for both 'All Ones' and 'All Zeros' data patterns. However, for the 'All Zeros' pattern, the increase of sneak path current is significantly lower at a higher ON/OFF ratio as the resistances tend to become ineffective at a higher ON/OFF ratio.

## B. Noise Margin Analysis

The allowable voltage levels in a CMOS circuit for logic ZERO should be ideally  $V_{OL} = \text{GND}$ , and for logic ONE, it should be  $V_{OH} = V_{dd}$ . However, some variations in these values are acceptable under specific bounds, which are referred to as 'Noise Margin'. The noise margin of a memristor cell is defined as the following equation:

$$Margin_{noise} = V_{one} - V_{zero} \tag{3}$$

where  $V_{one}$  and  $V_{zero}$  denote the voltages of the target cell in the low-resistance and high-resistance states, respectively. For a memristor crossbar array, the voltage values representing logic ONE and ZERO are highly affected due to the sneak path current. The noise margin of a target memristor cell is a strong indicator of whether the cell is operating effectively in an array. A large noise margin means the sensing circuit can easily identify the stored bits despite the sneak path effect and other disturbances. In contrast, a small noise margin usually means that the sensed voltages are too close to distinguish, which makes the cell unreliable and effectively nonfunctional in the array. The sneak path effect on noise margin is indicated by the difference between the sensed voltages corresponding to stored ZEROs and ONEs at the target cell.

For the analysis of the sneak path effect on the noise margin of the memristor array, a normalized parameter is defined [25]:

$$Margin_{noise} = \frac{Margin_{noise\_array}}{Margin_{noise\_device}}$$

(4)

Here, Margin<sub>noise\_device</sub> represents the noise margin of a single device without any interference of the sneak path, as the single device does not counter the sneak path issue, and Margin<sub>noise\_array</sub> represents the voltage difference of the ON and OFF states of a target cell while being subjected to operation in a memristor array. The noise margin of a target cell in an array highly depends on the data pattern stored within memory. For our analysis, only the best case (All Zeros) and the worst case (All Ones) data patterns are introduced.

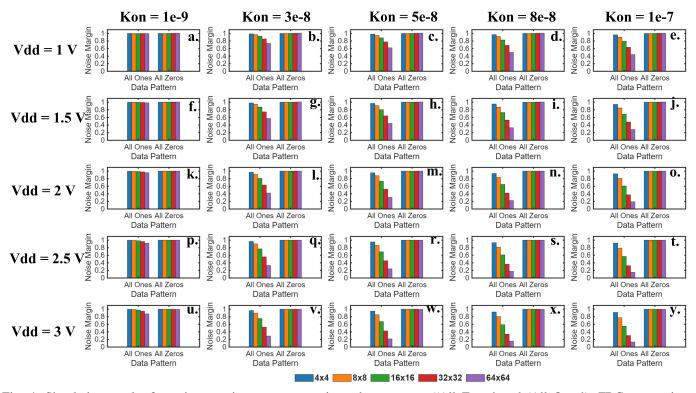

Taking M3 as an example, the simulation results in Fig. 4 demonstrate that at small array sizes the noise margins of both 'All Ones' and 'All Zeros' are almost similar at lower read voltage, e.g.,  $V_{dd}$ = 1 V and smaller ON/OFF ratio, e.g.,  $K_{on}$ = 1e-9. However, as the read voltage and  $K_{on}$  increase, the noise margin of larger arrays tends to decrease significantly. This is due to the increase of the sneak path current in larger arrays for high read voltage and high ON/OFF ratio. Finally, from the results, the added resistance of the sneak paths significantly narrows the noise margin and reduces the maximum possible size of a memristor array. It is the limiting factor for array scalability.

## C. Interconnect Resistance Effect on Sneak Path Current

The analysis demonstrates that the influence of three line resistances (M3, M5, M6),  $R_{\rm line}$ , on sneak path currents becomes more pronounced as the array size scales, though its relative impact remains secondary to the inherent sneak path phenomenon. In small arrays, the line resistance is negligible compared to the memristor resistance. That is why the effect

Fig. 4: Simulation results for noise margin versus array sizes, data patterns ('All Zeros' and 'All Ones'), FRC connection strategy, and line resistance M3 ( $R_{line} = 3.122\,\Omega$ ) where the read voltages are incremented along the rows and ON/OFF ratio is incremented along the columns of the subplots. The fall of noise margin for 'All Ones' data pattern with respect to the increment of the ON/OFF ratio along the columns as  $K_{on} = [1e-9, 3e-8, 5e-8, 8e-8, 1e-7]$  for a specific read voltage: (a~e)  $V_{dd} = 1.0 \text{ V}$ ; (f~j)  $V_{dd} = 1.5 \text{ V}$ ; (k~o)  $V_{dd} = 2.0 \text{ V}$ ; (p~t)  $V_{dd} = 2.5 \text{ V}$ ; (u~y)  $V_{dd} = 3 \text{ V}$ . Noticeably, for 'All Ones' pattern, noise margin rapidly decreases with respect to the increments of read voltage, ON/OFF ratio, array size compared to approximately zero decrease for 'All Zeros' data pattern.

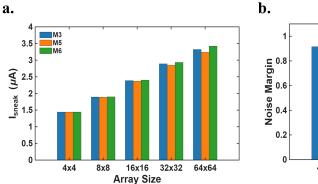

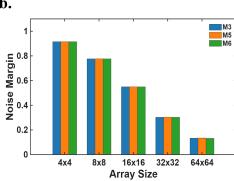

of line resistance is negligible. However, as the array size increases, the cumulative effect of the line resistance becomes more evident. The sneak path current is 3.42  $\mu$ A for a  $64\times64$  array with M6 interconnect compared to 1.44  $\mu$ A in a 4×4 array, as shown in Fig. 5 (a). Although line resistance introduces measurable losses, it does not fundamentally alter the primary conclusion that sneak paths pose a significant challenge to the operation of large-scale memristor crossbar arrays. Similarly, the effect of selected line resistances (M3. M5, M6) for noise margin calculation is also shown in Fig. 5 (b). The line resistances are considerably smaller compared to the memristor resistances and load resistor used for noise margin calculation. It is evident in the figure that as the sneak path current increases in a large array, the noise margin drops accordingly. However, the noise margin values for different line resistances are similar due to the small numerical values of line resistances compared to higher memristor resistances and load resistance.

## D. Model Validation Against SPICE Simulation

To assess the accuracy and applicability of the closedform model of the sneak path current, three sets of samples are selected for each parameter, and the resulting errors are analyzed. For validation, intermediate points are selected instead of boundary points to avoid boundary effects, as fitting constraints at the boundaries may produce artificially small or near-zero errors. Table VI presents the SPICE simulation results and model errors with high efficiency. All errors are below 10.9%, indicating that the proposed model accurately captures the sneak path current. In addition, under the same hardware environment, the proposed model achieves a runtime 10 to 4784 times faster than that of SPICE simulations. The hardware specifications are as follows: CPU Intel Core Ultra 7 256V, base frequency 2.2 GHz, 1 socket, 8 cores, 8 logical processors, and 16 GB of memory.

#### E. Sensitivity Analysis

A detailed and systematic analysis of sneak path currents within passive memristor crossbar arrays is presented, thereby expanding the current research landscape regarding parameter coverage and the depth of analytical modeling. The parameters selected within this study aim to effectively connect circuit-level characteristics with fabrication-level considerations, thus providing a practical framework that integrates theoretical models with physical implementation. Sneak path currents are vital in evaluating the feasibility of array designs. Excessive sneak currents can significantly constrain the maximum achievable size of the array, decrease the noise margin of

Fig. 5: (a) Sneak path current and (b) noise margin of the target cell versus array size for the interconnect layers using the IMEC A14 technology node. The array adopts 'All Ones' data pattern with FRC connection strategy.  $K_{on}$  is 1e-7.  $V_{dd}$  is 3 V.

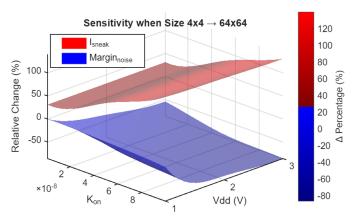

Fig. 6: Relative percentage change in sneak path current and noise margin as  $K_{on}$  and  $V_{dd}$  are varied. The array adopts 'All Ones' data pattern with FRC connection strategy using the IMEC A14 technology node with Cu M3 interconnect.

target cells, and hurt data integrity during read operations. Additionally, the ON/OFF resistance ratio of the devices plays an important role in influencing the severity of sneak paths: a lower contrast between the conductive and resistive states can mitigate undesired currents, whereas a higher ratio may intensify these currents. Moreover, this analysis explicitly considers the impact of interconnect line resistance, which becomes increasingly significant as devices and arrays continue to scale. In advanced technologies, line resistance contributes to voltage degradation along word lines and bit lines, thereby influencing write reliability and read stability. From the closedform analysis, the observed errors result primarily from the limited number of sampled points in SPICE simulations. To balance run-time and model accuracy, the current number of sampling points is limited and array size is set from 4×4 to 64×64. Actually, the resulting errors could be further reduced by increasing the number of points or optimizing the model. Also, the close-form model has good scalability to be applicable for larger array size with the same methodology, which represents a promising direction for future work. Compared with full circuit-level simulations, the proposed model achieves comparable accuracy with substantially reduced time.

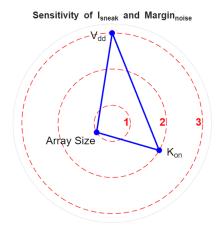

Fig. 7: Radar chart for sensitivity of sneak path current and noise margin to key design parameters.

The fast computing characteristics make the model suitable for large-scale array analysis and design optimization. To quantify the relative impact of array size on the noise margin and sneak path current, respectively, the size-to-margin sensitivity  $(Z_n)$  and size-to-current sensitivity  $(Z_i)$  for noise margin and sneak path current are defined in the following equations. A larger absolute value indicates a stronger sensitivity.

$$Z_n = \frac{Margin_{noise\_64 \times 64} - Margin_{noise\_4 \times 4}}{Margin_{noise\_4 \times 4}}$$

(5)

$$Z_i = \frac{I_{sneak\_64 \times 64} - I_{sneak\_4 \times 4}}{I_{sneak\_4 \times 4}} \tag{6}$$

Taking M3 as an example, Fig. 6 presents the simulation results to quantify the tradeoff among critical design parameters on  $I_{sneak}$  and noise margin. The relative percentage change surface for both sneak current and noise margin is shown with respect to the change of  $V_{dd}$  and  $K_{on}$  values. In this work, the key input parameters across all connection strategies and data patterns are varied systematically, adjusting  $V_{dd}$  by a factor of (3V-1V)/1V=2,  $K_{on}$  for (1e-7-1e-9)/1e-9=99, and array size for  $(64\times64-4\times4)/(4\times4)=255$ . The resulting impact on sneak path current and noise margin is quantitatively ranked to assess parameter sensitivity. This analysis reveals how each parameter

TABLE VII: Comparison with State-of-the-Art

| Device Type                        | [25] | [27] | [26] | [43]      | Current   |

|------------------------------------|------|------|------|-----------|-----------|

| Array size consideration           |      |      |      |           |           |

| Read voltage consideration         |      | ×    | X    | $\sqrt{}$ | $\sqrt{}$ |

| ON/OFF ratio consideration         |      | ×    |      |           |           |

| Data pattern consideration         |      | ×    |      | ×         |           |

| Connection strategy consideration  |      |      | ×    | ×         |           |

| Interconnect model consideration   |      | ×    | ×    | ×         | $\sqrt{}$ |

| Closed-form equation consideration | ×    | ×    |      | ×         |           |

| Accuracy consideration             | ×    | ×    | ×    | ×         |           |

contributes to either aggravating or mitigating sneak path effects. Among the three,  $V_{dd}$  exhibits the highest sensitivity, while array size shows the lowest. Such pre-design evaluation enables early prediction of how expanding the conductance range or lowering the read voltage can support larger array sizes, and vice versa. The trend and comparison for sensitivity are shown in a radar chart, Fig. 7.

## IV. COMPARISON WITH STATE-OF-THE-ART

Table VII provides a thorough comparison between the proposed analytical framework and existing studies on memristorbased systems. While previous research has addressed specific design parameters that influence sneak path behavior, none have comprehensively examined the complete set of interrelated factors affecting array performance. Key parameters, including array size, connection strategy, ON/OFF ratio, interconnect resistance, and read voltage, are essential for accurately evaluating the reliability and scalability of passive memristive memory arrays. In contrast, this study presents a novel and effective analytical approach that integrates all these factors within a cohesive framework. The proposed closedform models demonstrate minimal error across various validation conditions, thus facilitating precise pre-design and realtime estimations, as well as enhanced performance predictions for memristor-based crossbar systems.

## V. CONCLUSION

Sneak path currents significantly disrupt the reliable operation of passive memristor crossbar arrays. Therefore, estimating the sneak path effect during both the pre-design and ongoing design phases is essential for determining feasible array sizes and performance limitations. This work introduces an analytical framework for estimating sneak paths across a diverse range of design parameters and array configurations. The resulting closed-form models demonstrate the relationships of sneak path current with various parameters, revealing linear, exponential, and logarithmic dependencies under different biasing conditions. The proposed model is highly efficient, achieving an error of less than 10.9 % while reducing computation time by a factor of 10 to 4784. This enables accurate and efficient estimation of the impact of sneak paths. The accompanying sensitivity analysis further highlights how variations in design parameters affect both sneak path current and noise margin, providing essential guidance for balancing competing design trade-offs. Such detailed assessments offer designers valuable insights into scalability, functional yield, and performance constraints for future memristor-based analog IMC systems.

#### ACKNOWLEDGMENT

This work is supported in part by the National Science Foundation under grants 2510192, 2502054, 2428981, 2420994, 2427766, 2408064, 2247343, and 2218046. This material was also based upon work supported by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research (ASCR), under Award Number(s) DE-SC0025561.

#### REFERENCES

- [1] L. Chua, "Memristor-the missing circuit element," *IEEE Transactions on circuit theory*, vol. 18, no. 5, pp. 507–519, 2003.

- [2] S. A. Pourbakhsh, X. Chen, D. Chen, X. Wang, N. Gong, and J. Wang, "Sizing-priority based low-power embedded memory for mobile video applications," in 2016 17th International Symposium on Quality Electronic Design (ISQED), 2016, pp. 1–5.

- [3] N. Gong, J. Wang, S. Jiang, and R. Sridhar, "Clock-biased local bit line for high performance register files," *Electronics letters*, vol. 48, no. 18, pp. 1104–1105, 2012.

- [4] J. Edstrom, D. Chen, Y. Gong, J. Wang, and N. Gong, "Data-pattern enabled self-recovery low-power storage system for big video data," *IEEE Transactions on Big Data*, vol. 5, no. 01, pp. 95–105, 2019.

- [5] N. Gong, J. Wang, and R. Sridhar, "Variation aware sleep vector selection in dual vt dynamic or circuits for low leakage register file design," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 7, pp. 1970–1983, 2014.

- [6] D. Chen, J. Edstrom, Y. Gong, P. Gao, L. Yang, M. E. McCourt, J. Wang, and N. Gong, "Viewer-aware intelligent efficient mobile video embedded memory," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 26, no. 4, pp. 684–696, 2018.

- [7] S. A. Khan, M. Oli-Uz-Zaman, and J. Wang, "Pawn: Programmed analog weights for non-linearity optimization in memristor-based neuromorphic computing system," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 13, no. 1, pp. 436–444, 2023.

- [8] I. Vourkas and G. C. Sirakoulis, "Memristive crossbar-based nonvolatile memory," in Memristor-Based Nanoelectronic Computing Circuits and Architectures. Springer, 2015, pp. 101–147.

- [9] S. Shin, K. Kim, and S.-M. Kang, "Analysis of passive memristive devices array: Data-dependent statistical model and self-adaptable sense resistance for rrams," *Proceedings of the IEEE*, vol. 100, no. 6, pp. 2021–2032, 2011.

- [10] K.-H. Kim, S. Gaba, D. Wheeler, J. M. Cruz-Albrecht, T. Hussain, N. Srinivasa, and W. Lu, "A functional hybrid memristor crossbararray/cmos system for data storage and neuromorphic applications," *Nano letters*, vol. 12, no. 1, pp. 389–395, 2012.

- [11] S. H. Jo, K.-H. Kim, and W. Lu, "High-density crossbar arrays based on a si memristive system," *Nano letters*, vol. 9, no. 2, pp. 870–874, 2009.

- [12] M. A. Lastras-Montano and K.-T. Cheng, "Resistive random-access memory based on ratioed memristors," *Nature Electronics*, vol. 1, no. 8, pp. 466–472, 2018.

- [13] H. Uppaluru, Z. Templin, S. Z. Riam, F. Zhao, and J. Wang, "Carbon efficiency of natural organic honey-memristor based neuromorphic computing," in *Proceedings of the Great Lakes Symposium on VLSI 2025*, 2025, pp. 245–251.

- [14] N. Gong, J. Wang, and R. Sridhar, "Variation aware sleep vector selection in dual v<sub>t</sub> dynamic or circuits for low leakage register file design," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 7, pp. 1970–1983, 2014.

- [15] M. Oli-Uz-Zaman, S. A. Khan, W. Oswald, Z. Liao, and J. Wang, "Stuck-at-fault immunity enhancement of memristor-based edge ai systems," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 12, no. 4, pp. 922–933, 2022.

- [16] M. Oli-Uz-Zaman, S. A. Khan, G. Yuan, Y. Wang, Z. Liao, J. Fu, C. Ding, and J. Wang, "Reliability improvement in rram-based dnn for edge computing," in 2022 IEEE international symposium on circuits and systems (ISCAS), 2022, pp. 581–585.

- [17] M. Hu, C. E. Graves, C. Li, Y. Li, N. Ge, E. Montgomery, N. Davila, H. Jiang, R. S. Williams, J. J. Yang et al., "Memristor-based analog computation and neural network classification with a dot product engine," Advanced Materials, vol. 30, no. 9, p. 1705914, 2018.

- [18] P. O. Vontobel, W. Robinett, P. J. Kuekes, D. R. Stewart, J. Straznicky, and R. S. Williams, "Writing to and reading from a nano-scale crossbar memory based on memristors," *Nanotechnology*, vol. 20, no. 42, p. 425204, 2009.

- [19] V. Demin, I. Surazhevsky, A. Emelyanov, P. Kashkarov, and M. Kovalchuk, "Sneak, discharge, and leakage current issues in a high-dimensional 1t1m memristive crossbar," *Journal of Computational Electronics*, vol. 19, no. 2, pp. 565–575, 2020.

- [20] Y. Cassuto, S. Kvatinsky, and E. Yaakobi, "Sneak-path constraints in memristor crossbar arrays," in 2013 IEEE international symposium on information theory, 2013, pp. 156–160.

- [21] F. Gül, "Addressing the sneak-path problem in crossbar rram devices using memristor-based one schottky diode-one resistor array," *Results in Physics*, vol. 12, pp. 1091–1096, 2019.

- [22] Z. Tang, Y. Wang, Y. Chi, and L. Fang, "Comprehensive sensing current analysis and its guideline for the worst-case scenario of rram read operation," *Electronics*, vol. 7, no. 10, p. 224, 2018.

- [23] J. Liang and H.-S. P. Wong, "Size limitation of cross-point memory array and its dependence on data storage pattern and device parameters," in 2010 IEEE International Interconnect Technology Conference, 2010, pp. 1–3.

- [24] A. Chen, "A comprehensive crossbar array model with solutions for line resistance and nonlinear device characteristics," *IEEE Transactions on Electron Devices*, vol. 60, no. 4, pp. 1318–1326, 2013.

- [25] M. A. Zidan, H. A. H. Fahmy, M. M. Hussain, and K. N. Salama, "Memristor-based memory: The sneak paths problem and solutions," *Microelectronics journal*, vol. 44, no. 2, pp. 176–183, 2013.

- [26] R. Joshi and J. M. Acken, "Sneak path characterization in memristor crossbar circuits," *International Journal of Electronics*, vol. 108, no. 8, pp. 1255–1272, 2021.

- [27] H. Manem, G. S. Rose, X. He, and W. Wang, "Design considerations for variation tolerant multilevel cmos/nano memristor memory," in Proceedings of the 20th symposium on Great lakes symposium on VLSI, 2010, pp. 287–292.

- [28] E. Linn, R. Rosezin, C. Kügeler, and R. Waser, "Complementary resistive switches for passive nanocrossbar memories," *Nature materials*, vol. 9, no. 5, pp. 403–406, 2010.

- [29] L. Shi, G. Zheng, B. Tian, B. Dkhil, and C. Duan, "Research progress on solutions to the sneak path issue in memristor crossbar arrays," *Nanoscale Advances*, vol. 2, no. 5, pp. 1811–1827, 2020.

- [30] S. Kannan, J. Rajendran, R. Karri, and O. Sinanoglu, "Sneak-path testing of memristor-based memories," in 2013 26th International Conference on VLSI Design and 2013 12th International Conference on Embedded Systems, 2013, pp. 386–391.

- [31] T. Andrulis, J. S. Emer, and V. Sze, "Cimloop: A flexible, accurate, and fast compute-in-memory modeling tool," in 2024 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). IEEE, 2024, pp. 10–23.

- [32] Y. Luo, X. Peng, and S. Yu, "Mlp+ neurosimv3. 0: Improving onchip learning performance with device to algorithm optimizations," in *Proceedings of the international conference on neuromorphic systems*, 2019, pp. 1–7.

- [33] Z. Zhu, H. Sun, T. Xie, Y. Zhu, G. Dai, L. Xia, D. Niu, X. Chen, X. S. Hu, Y. Cao et al., "Mnsim 2.0: A behavior-level modeling tool for processing-in-memory architectures," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 42, no. 11, pp. 4112–4125, 2023.

- [34] T. R. Maram, R. Barnwal et al., "A deep neural network deployment based on resistive memory accelerator simulation," arXiv preprint arXiv:2304.11337, 2023.

- [35] W. Robinett, G. S. Snider, D. R. Stewart, J. Straznicky, and R. S. Williams, "Demultiplexers for nanoelectronics constructed from nonlinear tunneling resistors," *IEEE transactions on nanotechnology*, vol. 6, no. 3, pp. 280–290, 2007.

- [36] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *nature*, vol. 453, no. 7191, pp. 80–83, 2008.

- [37] Z. Pei, H.-H. Liu, M. Mayahinia, M. Tahoori, F. Catthoor, Z. Tokei, P. Dubey, and C. Pan, "Interconnect/memory co-design and cooptimization using differential transmission lines," *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, 2025.

- [38] Z. Pei, H.-H. Liu, M. Mayahinia, M. B. Tahoori, F. Catthoor, Z. Tőkei, D. B. Abdi, J. Myers, and C. Pan, "Ultra-scaled e-tree-based sram design and optimization with interconnect focus," *IEEE Transactions* on Circuits and Systems I: Regular Papers, 2024.

- [39] H.-H. Liu, S. M. Salahuddin, B. T. Chan, P. Schuddinck, Y. Xiang, G. Hellings, P. Weckx, J. Ryckaert, and F. Catthoor, "Cfet sram dtco, interconnect guideline, and benchmark for cmos scaling," *IEEE Transactions on Electron Devices*, vol. 70, no. 3, pp. 883–890, 2023.

- [40] Z. Pei, M. Mayahinia, H.-H. Liu, M. Tahoori, F. Catthoor, Z. Tokei, and C. Pan, "Technology/memory co-design and co-optimization using e-tree interconnect," in *Proceedings of the Great Lakes Symposium on VLSI 2023*, 2023, pp. 159–162.

- [41] H.-H. Liu, C. Gilardi, S. M. Salahuddin, Z. Pei, P. Schuddinck, Y. Xiang, P. Weckx, G. Hellings, M. G. Bardon, J. Ryckaert et al., "Future design direction for sram data array: Hierarchical subarray with active interconnect," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 71, no. 12, pp. 6495–6506, 2024.

- [42] H.-H. Liu, P. Schuddinck, Z. Pei, L. Verschueren, H. Mertens, S. M. Salahuddin, G. Hiblot, Y. Xiang, B. T. Chan, S. Subramanian et al., "Cfet sram with double-sided interconnect design and dtco benchmark," *IEEE Transactions on Electron Devices*, vol. 70, no. 10, pp. 5099–5106, 2023.

- [43] K. Datta, S. Shirinzadeh, P. L. Thangkhiew, I. Sengupta, and R. Drechsler, "Unlocking sneak path analysis in memristor based logic design styles," in 2022 25th Euromicro Conference on Digital System Design (DSD). IEEE, 2022, pp. 793–800.

Shah Zayed Riam received the B.Sc. and M.S. degrees in electrical engineering from Rajshahi University of Engineering and Technology (RUET), Bangladesh, and the University of Texas at Tyler, USA, respectively, in 2022 and 2024. He is currently pursuing a Ph.D. degree at the University of Alabama, Tuscaloosa, AL, USA. His research interests include memory design, flexible electronics, and electrochemical biosensors. His previous works received a runner-up award at WiSe/YP BIP 2023 and a nomination for the Best Paper Award at IEEE

FLEPS 2023, Boston, MA, USA.

Zhenlin Pei (Graduate Student Member, IEEE) holds the M.S. and Ph.D. degrees in electrical engineering from Columbia University and the University of Texas at Arlington. During his Ph.D., he collaborated with the Interuniversity Microelectronics Centre to develop the Cacti++ framework, which bridges gaps in rapid EDA-based co-design and cooptimization from the transistor to the system level. He is a postdoctoral fellow in the department of electrical & computer engineering at the University of Alabama. He was a senior design engineer in the

IP group for tapeout at Cadence for four years. Research interests include energy-efficient computing from hardware to software, with applications in AI through CAD/EDA & DTCO/STCO, emerging interconnects/beyond-CMOS/memory technologies, AI hardware with privacy, and neuromorphic systems.

**Kyle Mooney** (Graduate Student Member, IEEE) received his B.S. degree in computer engineering from the University of South Alabama in 2023 and is currently pursuing a Ph.D. in Electrical Engineering from the University of Alabama. His research interests include memory design, edge computing, and artificial intelligence.

Chenyun Pan (Senior Member, IEEE) received a B.S. in Microelectronics from Shanghai Jiao Tong University and a Ph.D. in ECE from Georgia Institute of Technology. He is an Associate Professor at the University of Texas at Arlington, and his research focuses on energy-efficient Boolean and non-Boolean computing systems using emerging technologies. He has published over 80 IEEE papers and received several awards, including the Research Spotlight Award from Georgia Institute of Technology, and an early career research award from

the U.S. Department of Energy.

Na Gong (Senior Member, IEEE) received the Ph.D. degree in computer science and engineering from the State University of New York, Buffalo, in 2013. Currently, Dr. Gong is a professor in the Department of Electrical and Computer Engineering at the University of Alabama. Her research interests include power-efficient computing circuits and systems, memory optimization, AI hardware, and hardware privacy. She is the recipient of the best paper nomination from ISVLSI'19, best paper award from EIT'16, best paper nominations from

ISQED'16 and ISLPED'16.

Jinhui Wang (Senior Member, IEEE) is currently a Full Professor and Larry Drummond Endowed Chair with the Department of Electrical and Computer Engineering at the University of Alabama, Tuscaloosa, AL, USA. His research interests include: (1) VLSI System, Digital and Mixed-Signal Integrated Circuit (IC) Design, 3D and 2.5D IC Design, and Emerging Memory; (2) AI Hardware Design, Post/Beyond CMOS Device, such as Memristors, Based Neuromorphic Computing System; and (3) Post/Beyond CMOS Devices Enabled Cybersecurity

and Internet of Things (IoT) Systems. He has published over 200 refereed journal/conference papers and book chapters as well as 31 patents in the area of emerging semiconductor technologies. His previous work has received the Best Paper Award/Nomination at DATE 2021, ISVLSI 2019, ISLPED 2016, ISQED 2016, and EIT 2016.