# SARA: A Stall-Aware Memory Allocation Strategy for Mixed-Criticality Systems

Meng-Chia Lee\*†, Wen Sheng Lim<sup>†</sup>, Yuan-Hao Chang\*<sup>†</sup>, Tei-Wei Kuo<sup>†</sup>

\*Institute of Information Science, Academia Sinica, Taipei, Taiwan

†Department of Computer Science and Information Engineering, National Taiwan University, Taipei, Taiwan r11922052@ntu.edu.tw, tundergod1882@gmail.com, johnson@csie.ntu.edu.tw, ktw@csie.ntu.edu.tw

Abstract—The memory capacity in edge devices is often limited due to constraints on cost, size, and power. Consequently, memory competition leads to inevitable page swapping in memory-constrained mixed-criticality edge devices, causing slow storage I/O and thus performance degradation. In such scenarios, inefficient memory allocation disrupts the balance between application performance, causing soft real-time (soft RT) tasks to miss deadlines or preventing non-real-time (non-RT) applications from optimizing throughput. Meanwhile, we observe unpredictable, long system-level stalls (called *long stalls*) under high memory and I/O pressure, which further degrade performance. In this work, we propose a Stall-Aware Real-Time Memory Allocator (SARA), which discovers opportunities for performance balance by allocating just enough memory to soft RT tasks to meet deadlines and, at the same time, optimizing the remaining memory for non-RT applications. To minimize the memory usage of soft RT tasks while meeting real-time requirements, SARA leverages our insight into how latency, caused by memory insufficiency and measured by our proposed PSI-based metric, affects the execution time of each soft RT job, where a job runs per period and a soft RT task consists of multiple periods. Moreover, SARA detects long stalls using our definition and proactively drops affected jobs, minimizing stalls in task execution. Experiments show that SARA achieves an average of 97.13% deadline hit ratio for soft RT tasks and improves non-RT application throughput by up to 22.32× over existing approaches, even with memory capacity limited to 60% of peak demand.

# I. INTRODUCTION

Due to constraints on cost, size, and power, edge devices are often equipped with limited memory capacity [1-7]. In such memory-limited edge devices, competition for memory among processes leads to frequent page swapping and subsequent slow storage I/O [8, 9], resulting in performance degradation. This highlights the importance of efficient memory allocation to meet application performance requirements. In particular, edge AI applications impose diverse requirements, including both soft real-time (soft RT) applications for responsive user interactions and non-real-time (non-RT) applications for substantial local data storage and processing capabilities [10, 11]. This is because the proliferation of edge AI applications has not only raised user expectations for low-latency inference but also emphasized strong privacy guarantees [12, 13], requiring edge devices to provide efficient services while processing and managing large volumes of privacy-sensitive data locally. In such mixed-criticality systems, inappropriate memory allocation fails to balance the trade-off between real-time guarantees and throughput, potentially causing soft RT tasks to miss deadlines or preventing non-RT applications from optimizing throughput.

Memory allocation strategies based on Linux control groups (cgroups) are widely adopted to manage page-swapping overhead [6, 14–17]. Rather than modifying the Linux page replacement policy to retain specific pages in memory [2, 18]—which incurs high management overhead and lacks adaptability to OS updates—these strategies preserve modular OS design (without OS-level modification). They achieve this by actively controlling the memory space allocated to each application through cgroups in user space.

Among memory allocation approaches using cgroups, current enterprise solutions typically employ greedy approaches that allocate excessive memory to soft RT applications [19], ensuring their timing requirements but at the cost of non-RT application throughput. In contrast, offline profiling [14–16] estimates the memory space required to achieve expected process performance, but does not account for runtime variability (e.g., jitter). Lagar-Cavilla et al. [17] use the online metric to maintain a constant page swapping-in rate for runtime memory allocation, but overlook latency variations of different storage devices, potentially resulting in missed deadlines for soft RT tasks on slower storage. TMO [6] proposes Pressure Stall Information (PSI) to measure the performance impact of memory scarcity, regardless of the type and speed of storage. However, it uses PSI primarily for memory space allocation in data centers to optimize throughput, rather than for mixedcriticality systems.

Additionally, another challenge arises from our experimental observation that memory-constrained systems occasionally experience significant and unpredictable *system-level stalls* (termed "long stalls"), which delay application execution and cause cascading effects, resulting in soft RT task deadline misses and degraded non-RT application throughput.

In this work, we introduce a Stall-Aware Real-Time Memory Allocator (SARA), a novel real-time memory management strategy designed to allocate memory space for mixed-criticality applications on memory-constrained edge devices. SARA aims to satisfy soft RT task timing requirements while optimizing non-RT application throughput. Our main contributions are as follows. First, we identify opportunities for performance balance by (1) allocating just enough memory to soft RT tasks to meet deadlines while optimizing the remaining

memory for non-RT applications, and (2) proposing a novel PSI-based metric,  $s_{intv}$ , to observe how latency caused by memory shortages affects the execution time of each soft RT job, where a job runs per period and a soft RT task consists of multiple periods (Section III-B). Second, based on this observation, we derive appropriate  $s_{intv}$  thresholds to assess memory sufficiency and efficiency for soft RT tasks to meet deadlines and dynamically adjust memory allocation to optimize non-RT application throughput (Section III-C). Third, we formally define long stalls through a systematic analysis of  $s_{intv}$  and implement early job dropping for soft RT tasks when long stalls are detected to mitigate their impact on application performance (Section III-D).

SARA was implemented on Linux kernel version 6.5.0 with cgroup v2 and evaluated using both fast and slow SSDs as swap backends to demonstrate its effectiveness across different hardware configurations. Compared to existing memory management strategies, SARA achieves a high deadline hit ratio of 97.13% on average for soft RT tasks while simultaneously improving non-RT application throughput by up to 22.32×. Notably, we maintain these benefits even with memory capacity limited to 60% of peak demand.

#### II. BACKGROUND AND MOTIVATION

### A. Impacts of Memory Insufficiency

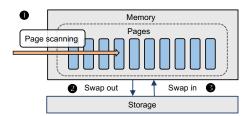

Fig. 1. Linux's Page Replacement Policy.

When memory usage reaches its limit, the Linux kernel employs a sophisticated page replacement mechanism to free up memory space by moving pages that are less frequently accessed to secondary storage (e.g., SSD) [2]. As illustrated in Fig. 1, when a page fault occurs and there is insufficient memory space to accommodate the faulting page, the OS scans pages to identify those that are infrequently accessed for reclamation • [20]. The selected pages are swapped out to storage devices • and makes room for the faulting page to be swapped into memory • 3.

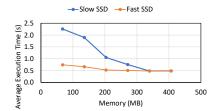

Fig. 2. Impact of memory allocation on application performance.

It is important to note that the page replacement process involves storage I/O operations, which typically incur orders of

magnitude higher latency compared to memory accesses [8, 9]. This can introduce significant overhead to application performance. Fig. 2 shows this performance impact on a soft RT periodic task (Sphinx) under varying memory-constrained configurations on systems with slow and fast SSD. With less memory, the average execution time of soft RT jobs over 500 periods increases, raising the risk of deadline misses, whereas on the fast SSD, the increase is slower due to its higher I/O bandwidth. Conversely, increasing memory improves performance. A similar trend is observed for non-RT applications, where less memory results in lower throughput, with the effect being more pronounced on slow SSDs. Therefore, this highlights the importance of proper memory allocation for meeting performance requirements.

#### B. Pressure Stall Information (PSI)

As shown in Fig. 2, under the same memory allocation, the execution time of the same process may vary depending on the SSD performance. Specifically, the same level of memory scarcity can cause varying degrees of performance degradation based on the SSD's capabilities. Therefore, instead of using metrics like page swapping-in rate [17], we need a metric that reflects performance degradation in relation to SSD characteristics to determine memory allocation.

Fig. 3. PSI metric.

We identify the potential of Pressure Stall Information (PSI), which was proposed in TMO [6], to capture this varying performance impact of memory scarcity. As illustrated in Fig. 3, PSI measures the stall time experienced by processes within a cgroup after a page fault occurs, including memory stalls and I/O stalls<sup>1</sup>. Memory stalls include the time spent on memory reclamation and allocation, I/O operations to reload a page, and reading a page from the swap device. I/O stalls measure the time that processes spend waiting for block I/O completion. PSI aggregates the stall time and reports it in two forms: a percentage and an absolute stall time in  $\mu s$ . The percentage represents the proportion of non-idle processes stalled within an observation window. For example, if the only process in a cgroup experiences 10,000  $\mu s$  of stall time within a 10-second window, this corresponds to a 0.1% stall. Since PSI directly measures the latency caused by memory shortage, it can capture the varying performance impact across different SSDs. However, no previous work has explored how to use PSI to assess the performance of soft RT tasks. Without understanding this relationship, it can result in inefficient memory allocation, as discussed in Section II-C.

<sup>1</sup>CPU stall is negligible in memory-constrained conditions, so we focus on memory and I/O stalls in this paper for clarity.

### C. Challenges in Real-Time Memory Management

Memory resource competition between concurrent processes poses significant performance challenges, especially in memory-constrained, mixed-criticality edge systems. As explained in Section II-A, memory usage significantly affects process performance. If non-RT applications consume excessive memory, they can severely reduce the memory available to soft RT tasks, thereby increasing the risk of missed deadlines. Conversely, if the execution time of the soft RT job per period is minimized by aggressively allocating memory to it, non-RT application throughput decreases. While existing works attempt to address this issue, none leverage PSI, which can capture the performance impact of memory contention across different SSDs. However, designing memory management approaches that utilize PSI remains challenging for two reasons, which are described below.

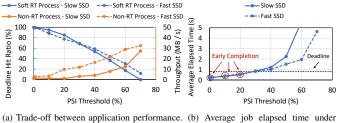

a) Trade-off between application performance. (b) Average Job elapsed time u varying PSI thresholds.

Fig. 4. Examples of inefficient memory management.

#### Balancing trade-off between real-time and throughput.

Fig. 4 illustrates our investigation of PSI-based memory allocation in systems with fast and slow SSDs. We execute a soft RT periodic task for 500 periods concurrently with a non-RT application. To explore the effects of PSI, we systematically vary the PSI threshold for the soft RT task in 10% intervals. These thresholds represent the maximum level of performance degradation that the soft RT task can tolerate. We monitor PSI in each time period, and if it falls below the threshold, memory allocation for the soft RT task is reduced, freeing up memory for the non-RT application. Fig. 4a shows the performance trade-off: lower PSI thresholds (below 20%) lead to increased memory allocation for the soft RT task, improving its deadline hit ratio but reducing non-RT application throughput, and vice versa. This trade-off becomes more pronounced with a fast SSD backend since higher I/O bandwidth allows the PSI of the soft RT task to stay within the thresholds with less memory. As a result, more memory is freed up for the non-RT application, which also benefits from increased I/O bandwidth. However, no single threshold achieves an optimal balance. Fig. 4b shows that under low thresholds (below 20%), soft RT jobs in most periods complete earlier than their deadlines due to memory over-utilization. In fact, these jobs could still meet deadlines with less memory, allowing more memory to be allocated to the non-RT application to optimize throughput. Furthermore, a static threshold results in *unstable elapsed time*. For instance, at a 30% PSI threshold, while the average elapsed time is close to the deadline, the deadline hit ratio is only 69%, indicating that some missed-deadline jobs are experiencing memory under-utilization. These two observations imply the need to find *an appropriate threshold* that can accurately manage the performance of soft RT tasks to balance the performance trade-off. Additionally, it should be *dynamically* adjusted at runtime.

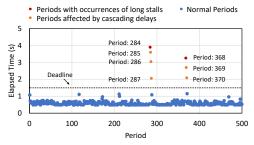

Fig. 5. The impact of long stalls.

Mitigating long system-level stall. When processes contend for scarce memory resources, we observe unpredictable and severe "long system-level stalls" (termed long stalls). These stalls may result from transient peaks in overall resource demand. During such stalls, all user-level processes become suspended, causing significant performance degradation. Fig. 5 illustrates this phenomenon by showing the elapsed time of jobs over 500 periods of a soft RT periodic task (Sphinx) when co-running with a non-RT application (Graphchi). The long stalls significantly prolong job elapsed times (marked in red), creating cascading delays that affect subsequent jobs (marked in orange) and cause a series of deadline misses. This effect extends beyond soft RT tasks and also degrades the throughput of non-RT applications. These observations highlight the critical need for the timely detection and mitigation of unpredictable long stalls to optimize application performance.

### III. THE PROPOSED SARA

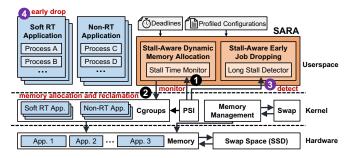

Fig. 6. Overview of the SARA system architecture.

#### A. Overview

We propose SARA, a memory management strategy that efficiently allocates memory space in memory-constrained systems where soft RT applications and non-RT applications compete for memory. The first objective is to balance the performance trade-off between satisfying the timing requirements of soft RT periodic tasks and optimizing the throughput

of non-RT applications. The second objective is to mitigate the impacts of long stalls. Fig. 6 presents the overall system architecture of SARA. First, the stall-aware dynamic memory allocation determines appropriate memory space allocation 2 by monitoring job execution status using our proposed PSIbased metric (i.e.,  $s_{intv}$ )  $\blacksquare$ , where each job runs per period and a soft RT task consists of multiple periods. The design leverages our insight that having each soft RT job complete just before its deadline in each period fosters balancing the performance trade-off, and our observation of how  $s_{intv}$ , driven by memory scarcity, affects execution time. Together, these insights enable dynamic adjustment of ideal threshold and memory allocation. Second, a stall-aware early job dropping mechanism is designed to mitigate the impact of unpredictable long stalls. The key idea is based on our observation of the strong correlation between the elevated  $s_{intv}$  and long stall, helping us to derive an effective detection methodology (3) to proactively drop jobs at the early stage of long stall impacts 4, thereby reducing stall time and preventing cascading performance degradation.

# B. Opportunities in Performance Optimization

Key factor in balancing performance trade-off. As discussed in Section II-C, in memory-constrained systems, the performance of soft RT tasks and non-RT applications exhibits a trade-off, governed by their memory allocation, where performance enhances with the allocated memory. Therefore, to balance the trade-off, we suggest allocating *just enough memory space* to soft RT tasks to ensure each job completes just before its deadline in each period, while *optimizing the remaining memory* for non-RT applications. To achieve this, it is crucial to understand *how memory space allocation affects execution time* during job execution. Given PSI's ability to capture the latency caused by memory shortage, we leverage PSI to understand how memory usage influences execution time.

Leveraging PSI to capture memory impact on execution time. We observe that the stall time, caused by memory shortage and measured by our introduced PSI-based metric, correlates with the execution time of the soft RT job in each period. Specifically, under memory shortage, the execution time ( $t_{exec}$ ) of a soft RT job is extended by the total stall time within a period ( $s_{period}$ ), on top of its Best-Case Execution Time (BCET, denoted as  $t_{BCET}$ ):

$$t_{exec} \approx s_{period} + t_{BCET}$$

(1)

where  $t_{BCET}$  represents the execution time under optimal conditions with unlimited memory resources, and  $s_{period}$  is obtained by accumulating stall measurements over multiple time intervals (i.e., from i=0 to the total number of intervals m in a period):

$$s_{period} = \sum_{i=0}^{m} s_{intv} \tag{2}$$

where  $s_{intv}$  is our proposed PSI-based metric, representing the maximum of memory stalls within each interval  $(s_{mem})$  and

I/O stalls within each interval  $(s_{IO})$ , both measured by PSI as absolute stall time:

$$s_{intv} = \max(s_{mem}, s_{IO}) \tag{3}$$

This formulation was chosen because memory stalls do not always fully encompass I/O stalls, contrary to the example shown in Fig. 3. This occurs because performance degradation from page faults can manifest solely as I/O stall time rather than memory stall time in some cases, as noted by TMO [6].

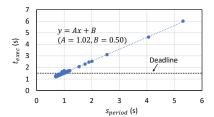

Fig. 7. Profiling of execution time  $(t_{exec})$  vs total  $s_{intv}$  per period  $(s_{period})$  over 500 periods.

Fig. 7 provides the experimental basis for deriving Equation 1. We execute a soft RT periodic task (Sphinx) for 500 periods under a constrained, fixed memory allocation while co-running a non-RT application (Graphchi). Each blue point represents the execution characteristics of the soft RT job in each period, including its execution time and  $s_{period}$ . Curve fitting reveals that these points exhibit a linear relationship, y = Ax + B, where the slope A approaches 1 and the intercept B approximates 0.48, matching the BCET obtained from our profiling. This strongly supports Equation 1. SARA uses this observation to derive the ideal stall time for each job to meet its deadline with just enough memory.

#### C. Stall-Aware Dynamic Memory Allocation

**Deriving the ideal stall time.** From Equation 1, we derive the ideal stall time in a period  $(s_{period}^{ideal})$  for a soft RT job to complete near its deadline (d) with only the necessary amount of memory:

$$s_{period}^{ideal} = d - t_{BCET} - t_{wait} \tag{4}$$

where  $t_{wait}$  accounts for delays in starting the current period due to overruns from the previous period. Fig. 8 illustrates this relationship.  $t_{wait}$  always appears upon job arrival and can be zero or positive. Notably, stall time may be interleaved with execution time.

Fig. 8. Relationship between deadline (d) and ideal stall time in a period ( $s_{period}^{ideal}$ ).

To keep  $s_{period}$  close to  $s_{period}^{ideal}$ , we must dynamically adjust memory allocation before each job completes. This is because

static allocation can lead to varying  $s_{period}$ , as shown in Fig. 7. Additionally, adjusting memory after job completion would be ineffective, as it would either miss its deadline or already consume excessive memory, resulting in early completion. Thus, SARA monitors the stall time at a finer granularity by dynamically distributing the remaining ideal stall time across the remaining intervals, determining the ideal stall time for each monitoring interval  $(s_{intv}^{ideal})$  as follows:

$$s_{intv}^{ideal} = \frac{s_{period}^{ideal} - \sum_{i} s_{intv}^{previous}}{n_{intv}^{remain}}$$

(5)

where  $\sum_{i} s_{intv}^{previous}$  denotes the accumulated stall time from prior intervals. It captures the irregular runtime delays of a dynamic soft RT job and is used to update the remaining ideal stall time accordingly, thereby enabling the proposed method to adapt to dynamic workload behavior.  $n_{intv}^{remain}$  represents the number of remaining monitoring intervals within a period. In this way, we use  $s_{intv}^{ideal}$  to guide memory allocation at each monitoring interval.

**Dynamic memory allocation.** To ensure each soft RT job completes close to its deadline, we adjust memory allocation at each interval to make  $s_{intv}$  approach  $s_{intv}^{ideal}$ , defined in Equation 5. Therefore, when  $s_{intv}$  exceeds  $s_{intv}^{ideal}$ , indicating a potential deadline miss, more memory is allocated to the current job; otherwise, memory is reclaimed to improve the throughput of non-RT applications. The memory adjustment amount is calculated as follows:

$$mem_{alloc} = x \times \frac{s_{intv} - s_{intv}^{ideal}}{l_{intv}}$$

(6)

where x defines the base adjustment unit of memory allocation. Larger deviations between  $s_{intv}$  and  $s_{intv}^{ideal}$  result in proportionally larger memory adjustments, which are normalized by the monitoring interval length  $(l_{intv})$  for consistent scaling.

By identifying opportunities for performance optimization and deriving an appropriate threshold  $(s_{intv}^{ideal})$ , which is dynamically updated based on runtime conditions, SARA effectively enables soft RT tasks to meet deadlines with just enough memory, thereby optimizing the throughput of non-RT applications.

#### D. Stall-Aware Early Job Dropping

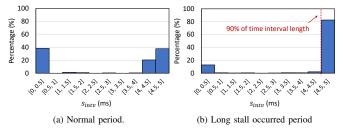

Fig. 9.  $s_{intv}$  distribution of normal and long stall periods.

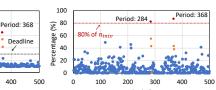

**Defining long stalls.** Timely mitigation of the impact of unpredictable long stalls requires a well-defined criterion to identify their occurrence. Fig. 9 shows distinct  $s_{intv}$  distribution characteristics between normal and long stall occurred Periods with occurrences of long stalls Normal Periods Periods affected by cascading delays

400

(a) Elapsed time of normal and long stallaffected periods.

Period

200

S 4

Elapsed Time (

(b) Percentage of  $n_{intv}$ with  $s_{intv}$  exceeding 90% of the  $l_{intv}$ .

Fig. 10. The correlation between elapsed time and analysis results.

periods of a soft RT periodic task (Sphinx). In the long stall period, the distribution shows that most  $s_{intv}$  values cluster at high magnitudes (i.e., 4.5-5 ms, where 5 ms is the interval length  $l_{intv}$ ), in contrast to the normal period. This pattern reveals the trend of long stalls, which typically occur when a high percentage of intervals encounter severe stalls. Fig. 10 shows how SARA determines the percentage of intervals with severe stalls that qualify as long stalls. Long stall periods (marked in red) exhibit over 80% of intervals with severe stalls (i.e.,  $s_{intv}$  over 90% of  $l_{intv}$ ), which distinguishes them from normal periods. Therefore, we define long stalls as follows.

Definition 1: The long stall is defined as when at least m%of the total monitoring intervals experience a stall time  $s_{intv}$ exceeding n% of the interval length  $l_{intv}$ .

We empirically select the values of m and n from a range of candidates, as long as they effectively distinguish long stall periods from normal ones. These values are determined via profiling only once for each soft RT workload on each system, thereby avoiding additional overhead in subsequent memory management. Moreover, soft RT periodic tasks typically follow similar control paths, allowing the profiling results to reliably detect long stalls.

Detecting long stalls and early job dropping. To prevent cascading delays caused by long stalls, we proactively drop running jobs early if they encounter long stalls, as determined by Definition 1. To drop jobs as early as possible while ensuring that only those unable to meet deadlines are dropped, we detect long stalls when the remaining ideal stall time within the execution period falls below 0 (i.e.,  $s_{period}^{ideal} - \sum_{i} s_{intv}^{previous} <$ 0). This condition can occur before deadlines, allowing early job dropping. Additionally, it indicates inevitable deadline misses due to the lack of additional tolerable stall time. When long stalls are detected, jobs are dropped to prevent cascading delays for jobs in subsequent periods, while also freeing memory for non-RT applications to enhance throughput.

#### IV. PERFORMANCE EVALUATION

# A. Experimental Setup

System configuration. We conducted our experiments on a real system with an Intel<sup>®</sup> Core<sup>TM</sup> i7-13700 (16 cores, 2.10 GHz) CPU with 64 GB DDR5 RAM. For the swap backend, we test on two SSDs—one slow and one fast—to demonstrate SARA's flexibility across heterogeneous storage backends. Specifically, we used a standard SSD (560 MB/s read, 510

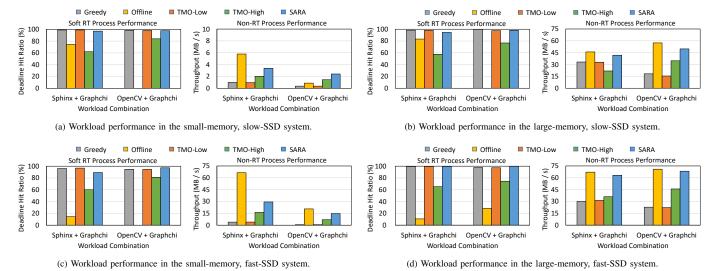

Fig. 11. Performance of soft RT and non-RT workloads under different management approaches on diverse system configurations.

MB/s write) and a high-performance SSD (2100 MB/s read, 1000 MB/s write). The system ran Linux kernel 6.5.0 with cgroup v2. Note that to simulate memory-constrained conditions, we use cgroups to limit memory size to 60% (*small-memory*) and 80% (*large-memory*) of the aggregate peak memory usage of workloads.

TABLE I. Workload characteristics.

| Workload     |     | Sphinx  | OpenCV  | Graphchi |

|--------------|-----|---------|---------|----------|

| Type         |     | Soft RT | Soft RT | Non-RT   |

| Deadline (s) |     | 1.5     | 0.8     | N/A      |

| BCET (s)     |     | 0.48    | 0.14    | N/A      |

| Memory       | Max | 338     | 183     | 272      |

| Usage        | Avg | 281     | 166     | 244      |

| (MB)         | Min | 136     | 97      | 36       |

Workload. We select two representative soft RT workloads from edge AI applications, considering different memory usage patterns: Sphinx [21], a speech recognition application with high memory usage, and OpenCV [22], an image classification application with low memory usage. These soft RT workloads are executed with Graphchi [23], a non-RT, memory-intensive workload that processes and manages graphs. The characteristics of the workloads are described in TABLE I.

**Parameters.** The monitoring interval length,  $l_{intv}$ , is set on the millisecond scale (e.g., 5 ms), as modern systems typically use a kernel tick rate between 100 Hz and 1000 Hz [24]. These kernel timer ticks trigger task switching and may cause stall state transitions, which in turn affect PSI values. Thus, we adopted the millisecond scale to effectively capture these dynamics. The base adjustment unit of memory allocation, x, is set to a small number of megabytes (e.g., 1 MB), considering that the memory usage of workloads is on the order of hundreds of megabytes. This corresponds to less than 1% of the workloads' memory usage, which helps avoid abrupt performance degradation and memory overprovisioning. Based

on the profiling results, m and n are set to 80 and 90 for both Sphinx and OpenCV.<sup>2</sup>

**Baseline.** We evaluated SARA against four memory allocation approaches: Greedy [19], Offline [14–16], TMO-Low and TMO-High [6]. Greedy allocates memory based on the actual usage of soft RT workloads without constraints. Offline determines static memory allocation through offline profiling to meet real-time requirements. TMO-Low, the original TMO parameter setting, uses a conservative 0.1% PSI threshold, while TMO-High uses a higher threshold determined through exhaustive search<sup>3</sup>, bringing the average elapsed time of soft RT tasks just below deadlines. In all these approaches, the non-RT workload uses the remaining memory after allocation for soft RT workloads.

# B. Experimental Result

Overall discussion. Fig. 11 shows the deadline hit ratios of soft RT tasks and the throughput of the non-RT application on our experimental platform under small and large memory configurations with slow and fast SSD backends. SARA achieves a near-optimal average deadline hit ratio of about 97.13%. Meanwhile, compared to Greedy and TMO-Low, which also maintain high deadline hit ratios, SARA improves throughput by  $5.69 \times$  and  $5.89 \times$ , respectively. Notably, the improvement is particularly pronounced in the small-memory, fast-SSD system, reaching up to  $20.96 \times$  and  $22.32 \times$  over Greedy and TMO-Low, respectively. The performance benefits mainly stem from dynamically allocating just enough memory to meet real-time requirements while optimizing the remaining memory for the non-RT application, as well as early job dropping to mitigate long stalls. In the small-memory, fast-SSD system, the non-RT application especially benefits from

<sup>&</sup>lt;sup>2</sup>These parameters are applied for systems with slow SSD, as no long stalls occur on fast SSDs.

<sup>&</sup>lt;sup>3</sup>As TMO is unaware of the relationship between real-time requirements and PSI, it is unsuitable for identifying adaptive thresholds. Thus, we resort to exhaustive search to determine a static one.

additional memory, as it processes large graphs that require sufficient memory. Moreover, the high I/O bandwidth of the fast SSD allows soft RT tasks to use less memory to meet deadlines, while the non-RT application takes advantage of both the additional memory and increased I/O bandwidth.

Although Offline and TMO-High achieve relatively high throughput, they have deadline hit ratios of only 49.61% and 77.11%, respectively. This severe failure to meet the timing requirements of soft-RT tasks is unacceptable. Offline allocates static memory without considering the runtime dynamicity of systems, leading to significant variance in elapsed time. Jobs with longer elapsed times can delay subsequent jobs, potentially resulting in a 0% deadline hit ratio. TMO-High uses a static high threshold that is not adjusted for system variance, causing jobs to miss deadlines or complete early, preventing full optimization of throughput. On the other hand, both Greedy and TMO-Low successfully maintain real-time guarantees; however, they result in significantly low throughput. Greedy allocates unrestricted memory to soft RT tasks, which restricts memory available to the non-RT application, leading to excessive page swapping and degraded throughput. Similarly, TMO-Low allocates excessive memory to soft RT tasks to keep PSI near the low threshold, at the cost of greatly reduced non-RT application throughput. These results highlight that, even with limited memory, SARA effectively satisfies real-time requirements while simultaneously optimizing non-RT application throughput through efficient memory allocation.

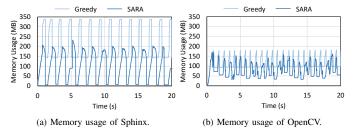

Effectiveness of stall-aware dynamic memory allocation. Fig. 12 compares memory usage patterns of Sphinx and OpenCV when running with Graphchi under SARA and Greedy approaches. It is clear that the stall-aware dynamic memory allocation component enables the soft RT job in each period to use less memory to meet its deadline by dynamically reducing memory allocation when it can tolerate longer stall time. This frees up memory for non-RT applications, significantly improving throughput.

Fig. 12. Memory usage reduction of soft RT periodic tasks with stall-aware dynamic memory allocation.

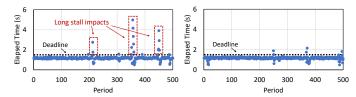

Effectiveness of stall-aware early job dropping. Fig. 13 presents the elapsed time of Sphinx jobs over 500 periods under SARA with and without the stall-aware early job dropping. The figure shows that SARA reduces the occurrence of prolonged jobs and mitigates cascading delays by detecting and dropping stalled jobs in the early stage. SARA improves the deadline hit ratio by 1.2% compared to the scenario with-

(a) Elapsed time of each job over 500 (b) Elapsed time of each job over 500 periods under SARA, without stall-aware periods under SARA. early job dropping.

Fig. 13. Reduction of long stall impacts on Sphinx with stall-aware early job dropping.

out early job dropping, although dropping operations take time and may cause some jobs to slightly exceed their deadlines.

#### V. RELATED WORK

Memory management strategies typically fall into two categories: page pinning [2, 18], and memory space allocation through cgroups [6, 14-17, 19]. Page pinning retains frequently accessed pages in memory for soft RT tasks by modifying the Linux page replacement policy. However, this fine-grained management incurs high management overhead and lacks adaptability to OS updates. In contrast, memory space allocation approaches focus on allocating memory space without managing individual pages, offering better cost-effectiveness and adaptability to system updates. Among memory allocation approaches, current enterprise solutions [19] greedily allocate memory to soft RT tasks to meet timing requirements. The offline profiling approaches [14-16] estimate the required memory for achieving the expected performance for processes based on offline results. Lagar-Cavilla et al. [17] introduce page swapping-in rate as an online metric for allocation decisions. However, we find that these works rely on unsuitable metrics, failing to achieve efficient allocation in mixed-criticality systems. Recent work TMO [6] introduces a new metric, PSI, that directly measures processes experienced stall time due to resource shortage across memory and I/O via the cgroup interface. Nevertheless, TMO remains inadequate for efficient memory allocation in mixed-criticality systems, as it lacks a mechanism to identify adaptive PSI thresholds for accurately monitoring soft RT execution status. Our proposed SARA is the first to establish the relationship between memory shortages and execution time through our proposed PSI-based metric. This relationship enables SARA to achieve our proposal of allocating just enough memory for soft RT tasks to meet deadlines and mitigate long stalls in memoryconstrained systems, thus meeting real-time requirements and improving throughput.

# VI. CONCLUSION

We introduce SARA, a novel stall-aware real-time memory allocator designed to balance the trade-off between real-time requirements and throughput in memory-constrained systems. SARA dynamically and efficiently allocates just enough memory to soft RT tasks to meet deadlines while optimizing the remaining memory for non-RT applications. This allocation is

guided by the ideal stall time, derived from our insight into how memory impacts execution time. It also mitigates long stalls by proactively dropping prolonged jobs, detected based on our definition. SARA maintains near-optimal deadline hit ratios for soft RT tasks while improving non-RT application throughput by up to  $22.32\times$  compared to existing approaches, even when memory capacity is limited to 60% of peak demand.

#### ACKNOWLEDGEMENT

This work was supported in part by National Science and Technology Council under grant nos. 111-2221-E-002-152-MY3, 112-2221-E-002-160-MY3, 114-2927-I-002-525, 114-2927-I-002-532, 114-2223-E-002-011, 114-2221-E-002-219-MY3, 114-2221-E-002-222-MY3, and by Ministry of Education under grant no. 114L900903.

#### REFERENCES

- [1] S. S. N. Larimi, B. Salami, O. S. Unsal, A. C. Kestelman, H. Sarbazi-Azad, and O. Mutlu, "Understanding power consumption and reliability of high-bandwidth memory with voltage underscaling," in 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE). IEEE, 2021, pp. 517–522.

- [2] Z.-W. Wu, Y.-C. Chen, Y.-H. Chang, and T.-W. Kuo, "App: Enabling soft real-time execution on densely-populated hybrid memory system," in 2023 60th ACM/IEEE Design Automation Conference (DAC). IEEE, 2023, pp. 1–6.

- [3] A. Capotondi, M. Rusci, M. Fariselli, and L. Benini, "Cmix-nn: Mixed low-precision cnn library for memory-constrained edge devices," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 5, pp. 871–875, 2020.

- [4] Z. Chang, S. Liu, X. Xiong, Z. Cai, and G. Tu, "A survey of recent advances in edge-computing-powered artificial intelligence of things," *IEEE Internet of Things Journal*, vol. 8, no. 18, pp. 13849–13875, 2021

- [5] S. Deng, H. Zhao, W. Fang, J. Yin, S. Dustdar, and A. Y. Zomaya, "Edge intelligence: The confluence of edge computing and artificial intelligence," *IEEE Internet of Things Journal*, vol. 7, no. 8, pp. 7457– 7469, 2020.

- [6] J. Weiner, N. Agarwal, D. Schatzberg, L. Yang, H. Wang, B. Sanouillet, B. Sharma, T. Heo, M. Jain, C. Tang et al., "Tmo: Transparent memory offloading in datacenters," in Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, 2022, pp. 609–621.

- [7] C. J. Xue, Y. Zhang, Y. Chen, G. Sun, J. J. Yang, and H. Li, "Emerging non-volatile memories: Opportunities and challenges," in Proceedings of the seventh IEEE/ACM/IFIP international conference on Hardware/software codesign and system synthesis, 2011, pp. 325–334.

- [8] A. Tavakkol, J. Gómez-Luna, M. Sadrosadati, S. Ghose, and O. Mutlu, "{MQSim}: A framework for enabling realistic studies of modern {Multi-Queue}{SSD} devices," in 16th USENIX Conference on File and Storage Technologies (FAST 18), 2018, pp. 49–66.

- [9] C.-F. Wu, Y.-H. Chang, M.-C. Yang, and T.-W. Kuo, "Joint management of cpu and nvdimm for breaking down the great memory wall," *IEEE Transactions on Computers*, vol. 69, no. 5, pp. 722–733, 2020.

- [10] M. Cinque, D. Cotroneo, L. De Simone, and S. Rosiello, "Virtualizing mixed-criticality systems: A survey on industrial trends and issues," *Future Generation Computer Systems*, vol. 129, pp. 315–330, 2022.

- [11] M. Cinque, R. Della Corte, A. Eliso, and A. Pecchia, "Rt-cases: Container-based virtualization for temporally separated mixed-criticality task sets," in 31st Euromicro Conference on Real-Time Systems (ECRTS 2019). Schloss-Dagstuhl-Leibniz Zentrum für Informatik, 2019.

- [12] R. Sachdev, "Towards security and privacy for edge ai in iot/ioe based digital marketing environments," in 2020 fifth international conference on fog and mobile edge computing (FMEC). IEEE, 2020, pp. 341–346.

- [13] B. Mao, J. Liu, Y. Wu, and N. Kato, "Security and privacy on 6g network edge: A survey," *IEEE communications surveys & tutorials*, vol. 25, no. 2, pp. 1095–1127, 2023.

- [14] C. Delimitrou and C. Kozyrakis, "Quasar: Resource-efficient and qosaware cluster management," ACM Sigplan Notices, vol. 49, no. 4, pp. 127–144, 2014.

- [15] Y. Sfakianakis, C. Kozanitis, C. Kozyrakis, and A. Bilas, "Quman: Profile-based improvement of cluster utilization," ACM Transactions on Architecture and Code Optimization (TACO), vol. 15, no. 3, pp. 1–25, 2018.

- [16] J. Zhu, R. Yang, X. Sun, T. Wo, C. Hu, H. Peng, J. Xiao, A. Y. Zomaya, and J. Xu, "Qos-aware co-scheduling for distributed long-running applications on shared clusters," *IEEE Transactions on Parallel and Distributed Systems*, vol. 33, no. 12, pp. 4818–4834, 2022.

- [17] A. Lagar-Cavilla, J. Ahn, S. Souhlal, N. Agarwal, R. Burny, S. Butt, J. Chang, A. Chaugule, N. Deng, J. Shahid et al., "Software-defined far memory in warehouse-scale computers," in *Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems*, 2019, pp. 317–330.

[18] D. Lee, J.-C. Kim, C.-G. Lee, and K. Kim, "Mrt-plru: A general

- [18] D. Lee, J.-C. Kim, C.-G. Lee, and K. Kim, "Mrt-plru: A general framework for real-time multitask executions on nand flash memory," *IEEE Transactions on Computers*, vol. 62, no. 4, pp. 758–771, 2012.

- [19] "Tuning workload memory protection, suse," https://documentation.suse. com/sles-sap/15-SP2/html/SLES-SAP-guide/cha-memory-protection. html.

- [20] "Page frame reclamation." [Online]. Available: https://www.kernel.org/doc/gorman/html/understand/understand013.html

- [21] S. Thomas, C. Gohkale, E. Tanuwidjaja, T. Chong, D. Lau, S. Garcia, and M. B. Taylor, "Cortexsuite: A synthetic brain benchmark suite," in 2014 IEEE International Symposium on Workload Characterization (IISWC). IEEE, 2014, pp. 76–79.

- [22] The OpenCV Reference Manual, 2nd ed., Itseez, April 2014.

- [23] A. Kyrola, G. Blelloch, and C. Guestrin, "{GraphChi}:{Large-Scale} graph computation on just a {PC}," in 10th USENIX symposium on operating systems design and implementation (OSDI 12), 2012, pp. 31–46.

- [24] "Linux kernel tick rate." [Online]. Available: https://man7.org/linux/man-pages/man7/time.7.html