# Orders in Chaos: Enhancing Large-Scale MoE LLM Serving with Data Movement Forecasting

Zhongkai Yu\*, Yue Guan\*, Zihao Yu<sup>†</sup>, Chenyang Zhou<sup>‡</sup>, Zhengding Hu \*, Shuyi Pei<sup>§</sup>, Yangwook Kang<sup>§</sup>, Yufei Ding\*, Po-An Tsai<sup>¶</sup>

\*University of California, San Diego

<sup>†</sup>Indiana University Bloomington

<sup>‡</sup>Columbia University

<sup>§</sup>Samsung Semiconductor, Inc.

<sup>¶</sup>NVIDIA

Abstract—Large-scale Mixture of Experts (MoE) Large Language Models (LLMs) have recently become the frontier open weight models, achieving remarkable model capability similar to proprietary ones. But their random expert selection mechanism introduces significant data movement overhead that becomes the dominant bottleneck in multi-unit LLM serving systems.

To understand the patterns underlying this data movement, we conduct comprehensive data-movement-centric profiling across four state-of-the-art large-scale MoE models released in 2025 (200B-1000B) using over 24,000 requests spanning diverse workloads. We perform systematic analysis from both temporal and spatial perspectives and distill six key insights to guide the design of diverse future serving systems. With our insights, we then demonstrate how to improve wafer-scale GPUs as a case study, and show that minor architectural modifications leveraging the insights achieve substantial performance gains, delivering 5.3× and 3.1× average speedups on DeepSeek V3 and Qwen3 respectively. Our work presents the first comprehensive data-centric analysis of large-scale MoE models and a concrete design study using the learned lessons, with profiling traces and simulation framework already open-sourced with >1k downloads. Our traces and results are publicly available at https://huggingface.co/datasets/core12345/MoE\_expert\_selection trace.

#### I. Introduction

Large Language Models (LLMs) have demonstrated remarkable capabilities across diverse domains, including programming assistance [43], [68], translation [1], [37], and chatbots [10], [65]. Since the beginning of 2025, large-scale Mixture of Experts (MoE) LLMs (200B+ model with 100+ experts) have become the leading models for frontier LLMs [6] and the most widely used open weight models.

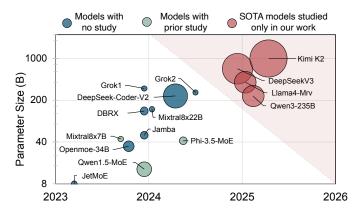

Unlike dense LLMs that activate all model weights uniformly, MoE models dynamically route each token to only a subset of experts, introducing substantial data movement overhead. Such overhead already exceeds 50% of execution time for small models (e.g., Mixtral 8x7B) on modest systems (2-4 GPUs), and it exacerbates further with larger models, such as DeepSeek V3 with 32× experts and 15× parameters deployed on multi-node systems (32+ GPUs) [18], [79]. However, as shown in Figure 1, no prior work has systematically investigated the underlying data movement patterns in large-scale MoE models. Prior studies conducted before the emergence of large-scale MoEs [13], [59], [74] have confined themselves to

Figure 1. MoE LLM models sizes and release dates. Bubble size indicates the number of experts in each layer. Prior studies [7], [54], [59], [82] provide limited analysis of smaller models from narrow perspectives, while our work presents the first comprehensive analysis of multiple unstudied SOTA models.

profiling much smaller models on limited hardware, typically examining only one or two LLMs while reporting simple observations without system-level insights. As parameter size and expert count surge, new patterns have emerged but remain unexplored, leaving significant optimization opportunities on the table. Thus, a comprehensive study of the underlying data movement patterns in SOTA MoE models presents a fruitful opportunity for better efficiency.

If data movement in MoE models were fully unpredictable, it would present significant challenges for deployments on multi-unit systems. From a temporal perspective, the explosive growth in expert combinations would make it impossible to prefetch, cache, or replicate experts in advance. For example, large-scale MoE models like DeepSeek V3 have  $C_{256}^8 = 4,426,165,368$  combinations in expert selection. When served with host memory-offload systems, such unpredictability would result in data movement like expert migrations between GPU and host, incurring substantial overhead, as interunit communication becomes the primary bottleneck. From a spatial perspective, if expert selection were truly random, it would lead to severe workload imbalance across units. When queries from diverse tasks are served concurrently, the number of queries assigned to each expert would vary dramatically,

creating significant workload disparities. Consequently, most units would remain idle and wait for heavily loaded units to finish, resulting in poor hardware resource utilization.

Fortunately, as we later show in the paper, MoE expert selections indeed have predictability that designers can exploit to reduce data movement. To uncover the inherent patterns in MoE models, we conduct a comprehensive data-movement-centric profiling of four state-of-the-art MoE models ranging from 235B to 1000B parameters released in 2025. As highlighted in Figure 1, we profile DeepSeek V3 [36], Llama4 Maverick [41], Qwen3-235B [72], and Kimi K2 [63] across 24,000 requests involving varied tasks, topics, and languages, which consumes >2000 GPU hours in total. We then collect the expert selection trace of all layers and tokens in each request to create an expert selection database of over 150 GB JSON files. From these extensive traces, we conduct a comprehensive analysis to uncover data movement patterns from both temporal and spatial perspectives, making our findings system-agnostic and applicable to various serving architectures at any scale. We then distill six key insights that serve as a solid foundation to understand MoE data movement and directly inform future MoE LLM serving system design, addressing critical questions that have remained unanswered in the field, such as: Is there a correlation between previously selected experts and those selected later? Are there discernible rules underlying the observed expert selection skewness? Do different tasks tend to activate different experts? Our work represents the first systematic effort to characterize data movement patterns at the scale of up-to 1000B model across a wide range of tasks, providing actionable insights that can guide the design of next-generation MoE serving systems.

To demonstrate the broad applicability of our insights, we present a case study on future GPU architecture design. Modern GPUs have adopted multi-chiplet designs due to single-die size limitations [9], [44], [55] and are evolving toward wafer-scale architectures enabled by emerging on-wafer packaging technologies [21], [71]. By applying our insights, we develop two key innovations for future wafer-scale GPUs: (1) A task distribution algorithm with a two-level data-placement-aware command processor architecture that balances workload across dies, and (2) a data-driven predictor with hardware-managed HBM architecture that reduces inter-die communication overhead by automatically caching critical data locally. These techniques achieve an average  $4.0 \times -6.3 \times$  speedup in MoE LLM serving throughput on wafer-scale GPUs.

Our main contributions can be summarized as follows:

- We propose a comprehensive and systematic datamovement-centric profiling across four latest, large-scale MoE models released in 2025 between 235B and 1000B to uncover the data movement patterns from both temporal and spatial perspectives.

- We distill six key insights for designing efficient MoE serving systems based on our profiling and analysis, providing actionable guidance that can inspire future research in MoE serving systems.

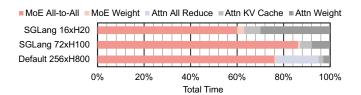

Figure 2. Latency breakdown for different data movement in DeepSeekV3, modeled after various serving configurations, including [16], [17], [36].

- Leveraging these insights, we conduct a case study on wafer-scale GPU architecture design. We proposed two strategies that improve MoE serving performance by 4.0×-6.3× with minor hardware modifications.

- We collect over 70,000 expert selection traces across multiple models and datasets, totaling over 150 GB in JSON format, and have open-sourced (>1k downloads) all traces with our multi-chiplet simulator to facilitate future research on MoE serving systems.

#### II. BACKGROUND

#### A. LLM and MoE Model Architecture

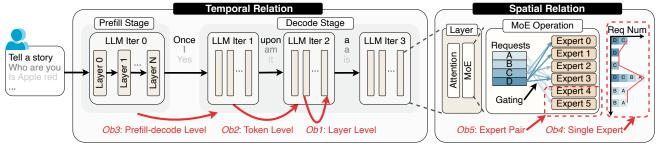

Most state-of-the-art LLMs adopt a decoder-only transformer architecture that follows a token-by-token autoregressive workflow [66]. As shown in Figure 3(a), after users input queries, the serving process is divided into two stages: the prefill stage and the decode stage. During the prefill stage, all input tokens are processed simultaneously to generate the first output token. The decode stage follows immediately, where tokens are generated sequentially. The generated token from each iteration is appended to the input sequence to produce the next token in the following iteration.

The Mixture of Experts (MoE) mechanism is a state-of-theart approach to improve LLM performance and has become prevalent among current frontier LLMs [40]. As shown in Figure 3(b), MoE-based LLMs replace the feed-forward network (FFN) layers in traditional LLMs with MoE layers. In each layer, multiple experts are deployed, and each request is routed to a small subset of the most suitable experts based on a gating mechanism. This innovation enables MoE models to scale model parameters without incurring extra inference overhead, since only a fraction of parameters are activated for each request. However, this mechanism also introduces dynamic randomness, since expert selection is unknown until gating is completed, posing new challenges for serving systems.

# B. Prior MoE Serving Systems

The MoE mechanism constitutes the primary source of data movement overhead in modern serving systems. As illustrated in Figure 2, MoE-related data movement (MoE All-to-All and MoE Weights) dominates the overhead across different DeepSeek V3 serving configurations, accounting for 60%-90% of total latency. To address this overhead, existing research on MoE serving optimization has developed numerous system-level solutions targeting different performance and cost objectives. Edge systems like MoE-Lightning [4] and CoServe [58]

(a) MoE-LLM inference process and temporal relations

(b) MoE operation and spatial Relation

Figure 3. Inference process of MoE LLMs and the categorization method for our proposed data-centric profiling approach.

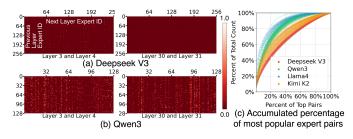

Figure 4. Layer-level temporal correlation heatmaps for (a) Deepseek and (b) Qwen, together with (c) statistical results across all layers, reveal a strong correlation between expert selection in layer N and that in layer N+1.

employ CPU memory offloading techniques to address GPU memory capacity constraints, while server systems such as Comet [79] and MegaScale-Infer [82] leverage multi-GPU architectures and address GPU-GPU communications in MoE for higher throughput. Novel hardware architectures like Duplex [77] explore processing-in-memory to accelerate data movement in MoE LLMs.

However, these prior studies employ a *system-centric* methodology when optimizing for MoE LLMs. Namely, they inherently focus on a specific platform and the corresponding data movement patterns of MoE in such platform (e.g., CPU-GPU, multi-GPU, ML accelerators). As a result, they propose deployment-specific optimizations that may not generalize across different serving platforms, and their insights are often a slice of the overall inherent patterns in MoE LLMs.

In this work, we flip the process and adopt a *model-centric* strategy by conducting system-independent profiling to extract *system-agnostic* insights about MoE data movement patterns. These insights are therefore broadly applicable across various platforms, providing a foundation for optimization strategies that transcend specific system implementations.

#### III. MOE PROFILING AND SYSTEM INSIGHTS

In this section, we conduct a data-movement-centric profiling of the expert selection behavior in four state-of-the-art MoE models: Deepseek V3 (671B), Llama4-Maverick-128E (402B), Qwen3-235B (235B), and Kimi K2 (1000B). All results are averaged over more than 24,000 requests.

# A. Categorization Methodology

As in Figure 3, we categorize MoE expert selection profiling results into two categories: *temporal* and *spatial* relations.

Temporal relations capture time-dependent expert selection patterns where current choices inform future selections. These patterns enable *single-unit strategies* that optimize data movement within individual units through prefetching, caching, and data migration. For example, in multi-chiplet GPU systems, caching experts in local DRAM after remote fetches significantly reduces inter-unit communication. To exploit temporal predictability, we analyze expert selection at multiple time scales shown in Figure 3(a): *layer-level*, *token-level*, and *prefill-decode-level* patterns.

Spatial relations reflect expert selection distribution and imbalance across the system. These patterns enable *multi-unit strategies* that optimize system-wide expert placement and workload distribution. By identifying frequently selected experts and analyzing selection skewness, we design algorithms for workload routing and expert replication that balance traffic among units. We classify spatial relations into *single-expert activation imbalance* and *expert-pair co-activation affinity* as shown in Figure 3(b), and investigate how task types influence these patterns to inform system-level strategies.

# B. Temporal Relations

As shown in Figure 3(a), we classify the temporal relations of expert selection into three categories, arranged in order of increasing time scale. At the layer level, we examine the relationship between two adjacent model layers. At the token level, we focus on the same model layer across two adjacent tokens. At the stage level, we analyze the relationship between the prefill stage and the decode stage.

# 1) Layer-Level: (Ob1)

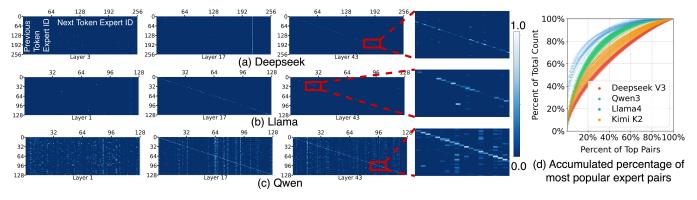

As shown in Figure 4 (a) and (b), we present heatmaps for Deepseek and Qwen illustrating expert selection relationships across adjacent layers. Each pixel in the heatmap displays the conditional probability of selecting expert j in the next layer given that expert i was activated in the previous layer, with bright colors indicating higher probabilities.

The heatmaps reveal clear cross-layer correlations with white dots highlighting specific expert pairs with significantly higher selection probabilities across adjacent layers. However,

Figure 5. Token-level temporal correlation heatmaps for (a) Deepseek, (b) Llama, and (c) Qwen, together with (d) statistical results across all layers, demonstrate a strong correlation between the expert selection for consecutive tokens t and t+1.

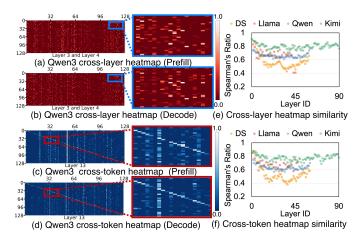

Figure 6. Expert activation patterns remain consistent across prefill and decode stages for both (a, b) cross-layer heatmap and (c, d) cross-token heatmaps. Spearman's ratio quantified in (e, f) shows a strong relation ( $\geq 0.7$ ).

correlation patterns vary across layers within the same model and differ between models due to architectural variations. For instance, patterns between layers 3-4 differ from those between layers 30-31. Qwen3's notably brighter heatmap indicates stronger cross-layer correlations than Deepseek. Beyond the white dots, there are also consistent bright vertical lines, suggesting certain experts are frequently chosen regardless of previous layer selections. These patterns indicate generally popular experts, analyzed further in Sec. III-C1.

To quantify these relationships, we analyze expert pair frequencies across multiple requests and all model layers. The cumulative percentage of the most frequently selected expert pairs is shown in Figure 4(c). The results demonstrate that the top 20% of expert pairs account for 45%, 68%, 80%, and 55% of all activations in Deepseek, Qwen, Llama4, and Kimi K2, respectively. This reveals strong, model-dependent cross-layer correlations, with Llama4 <sup>1</sup> exhibiting the strongest effect and Deepseek the weakest.

# 2) Token-Level: (Ob2)

We examine expert selection relations for the same layer between adjacent tokens in Figure 5. Each pixel in the heatmap displays the conditional probability of selecting expert j in the next token given that expert i was activated in the previous token, with bright colors indicating higher probabilities.

Similar to layer-level patterns, cross-token heatmaps exhibit white dots, bright vertical lines, and variation across layers and models, indicating correlations between adjacent tokens. However, token-level relations reveal a common pattern appearing across all models: the bright diagonal line that indicates the tendency to select the same expert across adjacent tokens. This diagonal pattern emerges predominantly in higher layers (17 and 43) but not in lower layers (1 and 3), regardless of models.

We quantify these token-level relations using the same approach as layer-level relations in subsubsection III-B1. As shown in Figure 5(d), the top 20% of expert pairs account for 40% to 80% of all selections, indicating strong token-level relations. Llama4 exhibits the strongest relation while Deepseek shows the weakest, suggesting future expert selections are most predictable in Llama4.

# 3) Prefill-Decode-Level Correlation: (Ob3)

Building on the layer-level and token-level relations, we observe notable similarities in expert selection patterns between prefill and decode stages. Comparing heatmaps across stages in Figure 6(a)(b)(c)(d), we find similar distributions of bright dots, indicating that expert pairs frequently selected during prefill are also likely selected during decode. This cross-stage consistency suggests expert selection in the decode stage can be predicted using prefill data.

To quantify this similarity, we compute Spearman's ratio  $(\rho)$  across all model layers, comparing prefill and decode heatmaps. Spearman's Ratio  $\rho$  measures monotonic relationships between variables, ranging from -1 (perfect negative correlation) to 1 (perfect positive correlation). Generally,  $|\rho|>0.7$  indicates strong correlation,  $0.4<|\rho|\leq0.7$  indicates moderate correlation, and  $|\rho|\leq0.4$  suggests weak correlation [49]. The results in Figure 6(e)(f) show that most layers demonstrate strong correlation, while a few show moderate correlation. This makes it possible to predict decode-stage

$<sup>^1</sup>$ Llama4 places dense FFN layers between MoE layers, so we analyze correlations between adjacent MoE layers (N and N+2).

expert selection with prefill-stage data.

4) System Insights from Temporal Relation: The observed temporal relations in expert selection motivate us to design fine-grained, dynamic strategies on every single unit to reduce the communications. For example, when expert weights are read from remote memory, such as remote DRAM in multi-chiplet systems, or CXL extension memory in memory-disaggregated systems, caching, migration, and prefetching strategies can be deployed to reduce data movement.

★Insight 1: Prefill-data-driven prediction (Ob3). Leverage the expert selection trace from the prefill stage to predict expert selection during the decoding stage.

Empirical analysis shows that experts selected more frequently during the prefill stage are also likely to be chosen during the decoding stage. Thus, the expert selection information collected during the prefill phase can serve as an important reference for expert selection prediction at the beginning of the decoding stage, when only a few tokens have been generated and reference data is limited. Furthermore, prefill information can also be used to dynamically adjust expert distribution during the decode stage. This is especially useful in modern serving systems that employ parameter disaggregation, where the prefill and decode stages may reside on different machines.

**★Insight 2: Cross-hierarchy memory management** (Ob1, Ob2). Token- and layer-level temporal relations enable dynamic expert prefetching and caching across memory hierarchies.

Layer-level and token-level temporal relations share similarities in definition but differ in their reuse distances, making them suitable for different memory hierarchy levels. Layer-level relation exhibits short reuse distances since consecutive MoE layers execute immediately, while the token-level relation creates longer distances as tokens are generated only after traversing all layers.

This distinction aligns naturally with the complex multiunit MoE serving systems. For example, in multi-chiplet architectures, each die contains LLC and local DRAM, forming a two-level hierarchy. The faster LLC manages experts with short reuse distances (layer-level), while the larger DRAM handles longer distances (token-level). We can leverage layerlevel relations for LLC management and token-level relations for local DRAM management.

This principle extends to other systems where layer-level relations can optimize faster memory tiers and token-level relations can enhance slower tiers: multi-GPU systems with LLC and local DRAM, CXL-based systems with local DRAM and remote CXL memory, SSD offloading systems with DRAM and flash storage, and in-flash computing systems with local and remote flash dies.

Figure 7. Single-expert spatial relation analysis of Llama4 layer 7 shows: (a) non-uniform expert activation distribution; (b) expert selection strongly correlates with task type; (c) expert activation patterns shift significantly when language changes while content remains identical.

#### C. Spatial Relation

As shown in Figure 3(b), we analyze spatial patterns in expert selection for both single-expert activation imbalance and expert pair co-activation affinity. For single experts, we examine statistical skewness and the factors affecting each expert's activation. For expert pairs, we analyze co-activation properties across all two-expert combinations.

1) Single Expert Activation Imbalance: (Ob4)

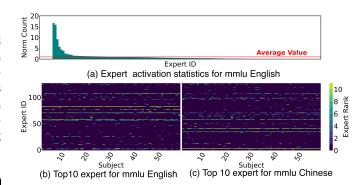

We examine expert selection frequency at each layer, presenting results for layer 7 of Llama4 in Figure 7. After normalizing selection counts by the average, we observe pronounced skewness where a subset of experts is activated over 16 times more frequently than average. This workload imbalance suggests system designs should duplicate or decentralize frequently used experts.

To investigate selection patterns across different tasks, we analyze all 57 MMLU subjects spanning diverse fields, including biology, history, and math, etc [23]. Figure 7(b) shows the top 10 most popular experts for each subject. Horizontal bright lines indicate certain experts are consistently activated regardless of subject, while remaining popular experts vary significantly between subjects, demonstrating both overlap and distinction in task-based expert selection.

We further examine task impact using Chinese version of MMLU in MMLU Pro [67] with identical questions but different languages. Figure 7(c) reveals distinctly different patterns: although 5-6 experts remain popular across subjects, only two overlap with English MMLU's most frequently selected experts. This confirms that task characteristics, including language, significantly influence expert selection, enabling task-aware serving systems that optimize expert distribution to balance workloads and reduce data movement.

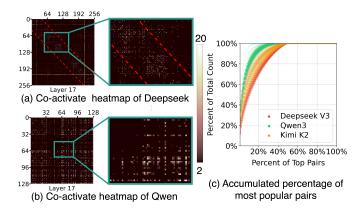

2) Expert Pair Co-activation Affinify: **(Ob5)** Beyond single expert patterns, we observe spatial relations for expert pairs where certain experts are more likely to be co-activated. We present co-activation heatmaps in Figure 8(a)(b), where both axes indicate expert IDs. Each pixel represents an expert pair with values showing co-activation frequency normalized by theoretical random selection probability:  $p = \frac{1}{2} \left( \frac{1$

Figure 8. Co-activation probability heatmap of expert pair for (a) Deepseek and (b) Qwen, together with (c) statistical results across all layers, demonstrating that specific expert pairs exhibit high simultaneous activation probabilities.

$\frac{2}{n(n-1)}$ , where n is the number of experts.

Bright dots appear with probabilities 20-40 times higher than theoretical values, indicating strong co-activation tendencies. All heatmaps exhibit central symmetry since expert pair (i,j) equals (j,i). In Deepseek's heatmap Figure 8(a), frequently activated pairs lie between red lines forming bright squares, reflecting Deepseek's routing restriction where tokens are routed only to adjacent nodes to reduce communication overhead. This suggests the potential of separating co-activated expert pairs to balance workload.

We quantify this relation by aggregating data across all layers in Figure 8(c). The top 10% of expert pairs account for 60-80% of total activations, indicating strong skewness in pair selection. Qwen exhibits even stronger co-activation relations than Deepseek, suggesting that expert distribution strategies separating frequently co-activated experts can significantly improve system performance.

We only analyze Deepseek and Qwen since Llama selects one expert per MoE layer, eliminating co-activation relations.

3) System Insights from Spatial Relation.: Spatial Relation enables coarse-grained, static strategies to address workload imbalance across system. These strategies could be applied at system startup or during periodic redistribution (e.g., every 10 minutes) through appropriate task distribution.

**★Insight 3: Expert-placement-aware workload distribution** (<u>Ob4</u>, <u>Ob5</u>). Employ expert placement information to design workload-balanced task distribution strategies.

Expert placement in serving systems can change dynamically due to expert migration strategies. Therefore, when allocating workload to system units, expert placement should be considered for better workload balance. Besides, the design space for task allocation could be enlarged with emerging new systems. Traditional multi-GPU systems tend to allocate experts to local GPUs to avoid cross-unit communication. However, in multi-chiplet GPUs, we can consider allocating tasks to remote dies for better workload balance as inter-unit

communication becomes faster.

**★Insight 4: Popular expert decentralization** (*Ob4*). Duplicate or decentralize frequently used experts to balance workloads.

Expert skewness causes workload imbalance and suboptimal resource utilization. Duplicating popular experts across multiple compute units distributes load more evenly. Additionally, avoiding co-location of highly popular experts on the same unit further enhances workload balance.

**★Insight 5: Expert-pair separation (***Ob5***).** Separate frequently co-activated expert pairs to maximize parallelism.

Certain experts are frequently activated simultaneously, exhibiting strong co-activation patterns. Assigning these co-activated expert pairs to different compute units maximizes hardware parallelism and prevents workload concentration on specific units. However, separation also introduces cross-unit communication overhead. The effectiveness depends on system topology and batch size, requiring careful trade-off between parallelism benefits and communication costs.

**★Insight 6: Workload-aware serving system (0b4).** Leverage the workload information, like task type and language, to make expert migration prior to serving.

Hot experts vary by task and language. English queries, for instance, activate different expert subsets than Chinese queries. Providing task metadata during serving enables proactive expert placement: when workloads are predominantly English, systems can pre-duplicate or reassign English-relevant experts, reducing communication and balancing loads. This task-to-expert mapping requires only one-time offline profiling per model and can be reused throughout deployment, making the approach practical and efficient.

# IV. CASE STUDY: FUTURE GPUS ARCHITECTURE DESIGN FOR MOE MODELS

In this section, we adopt future GPU architecture design as a use case to validate our proposed insights. We follow <a href="Insight 3">Insight 3</a> to design a task allocation algorithm and leverage the temporal relation insights (<a href="Insight 1">Insight 1</a> and <a href="Insight 2">Insight 2</a>) to build a data-driven predictor. We also make slight architectural modifications to support the task allocation algorithm and the data-driven predictor.

# A. Trend of Future GPU Architecture

GPU vendors are increasingly adopting multi-chiplet architectures to overcome single-die performance limitations. As Moore's Law approaches its limits [38] and single-die size remains constrained by photomask dimensions (800-1,000 mm<sup>2</sup>), advanced packaging technologies like TSMC's CoWoS [26], Samsung's X-Cube [53], and Intel's EMIB [39]

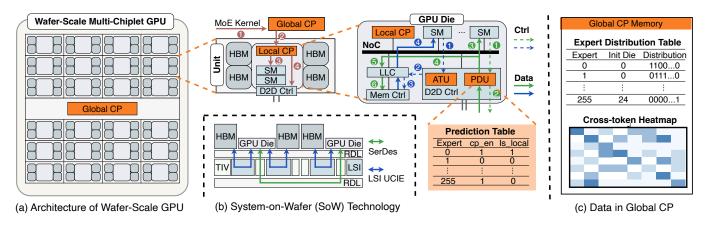

Figure 9. (a) Wafer-scale multi-chiplet GPU architecture with additional units highlighted in orange. (b) SoW (System-on-Wafer) technology structure. (c) Data format in the Global Command Processor for our proposed task distribution strategy.

enable multiple chiplets within a single package. Leading vendors have adopted such designs: AMD's MI300 [55] integrates eight compute chiplets, NVIDIA's Blackwell features two chiplets [44], and upcoming Rubin expects four [45].

This trend is evolving toward wafer-scale systems [24]. TSMC's System-on-Wafer (SoW) technology accommodates up to 24 compute dies and 96 HBM dies on a single wafer, exceeding 200,000 mm<sup>2</sup> [52]. As shown in Figure 9(a), a typical wafer-scale multi-chiplet GPU consists of multiple units, each containing a GPU die and several HBM dies interconnected in a mesh topology. Such systems contain over 10 TB of HBM and PFLOPS-level computing power, supporting extremely large models and batch sizes.

The TSMC SoW technology shown in Figure 9(b) connects each GPU die to local HBM dies through local-silicon interconnects (LSI) [25], with adjacent GPU dies communicating via LSI vertically or XSR SerDes links horizontally. Although LSI and SerDes both provide terabit-level bandwidth, inter-GPU-die communication remains the primary bottleneck. Remote data access requires multiple hops across die-to-die links, resulting in high latency. Simultaneous remote HBM access by multiple dies creates bandwidth contention and traffic congestion, further degrading performance.

#### B. Challenges of serving MoE with future GPUs

Unlike current multi-GPU systems, wafer-scale GPUs can fit entire MoE models on a single chip and support batch sizes over 10,000. However, current GPU architectures introduce two key limitations for such large-scale chips.

Simplistic Task Allocation. Current GPUs integrate a CPU in their SoC to serve as a command processor and allocate tasks to all SMs. However, the traditional command processors treat all SMs equally, ignoring their physical locations and data placement [20], [32]. This oblivious task-to-SM assignment generates excessive D2D traffic and ignores MoE expert selection skewness, leading to poor utilization when most dies remain idle while others become overloaded.

**Inadequate Local HBM Management.** Current GPUs treat all HBM dies as uniform memory space, but wafer-scale GPUs

connect each compute die directly to local HBM, where access is significantly faster than a remote HBM. Frequently accessed experts in remote HBM could be cached locally to minimize D2D traffic, but current GPUs do not distinguish between local and remote HBM and therefore generate unnecessary traffic.

# C. Motivation and Insights

To address these challenges, we propose two strategies with architectural support. First, based on <a href="Insight 3">Insight 3</a> that identifies the need for expert-placement-aware task distribution, we propose an intelligent task allocation algorithm with a multi-level, data-placement-aware command processor architecture. This approach considers expert placement and selection skewness across dies, enabling dynamic task allocation that minimizes D2D traffic while balancing workload.

Second, leveraging Insight 1 and Insight 2 that reveal the predictability behind expert selection across different timescales, we introduce a data-driven predictor with hardware-managed HBM architecture. Local HBM caches frequently accessed experts from remote dies, while a lightweight predictor analyzes selection patterns to estimate future needs, caching predicted experts locally to reduce D2D traffic.

These enhancements work independently, each delivering significant improvements with minor hardware modifications. Combined, they provide up to 20% additional benefit over individual deployment. We implement both strategies through architectural changes to maintain consistency with existing GPU programming models, which treat GPUs as single-die devices without exposing die-level control. If future programming models provide more fine-grained features, these strategies could alternatively be implemented at the system level without architectural changes.

# D. Architecture Design

1) Architecture Overview: To support our proposed predictor and task allocation algorithm, we implement two architectural modifications with minimal overhead, as illustrated in Figure 9(a). These changes, highlighted in orange, consist of

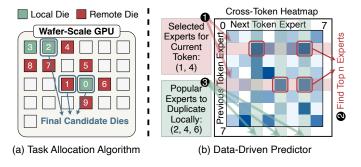

Figure 10. Proposed task allocation algorithm and data-driven predictor.

an enhanced Command Processor structure and an extended D2D controller design.

First, we redesign the Command Processor (CP) with a two-level hierarchical structure: a Global CP at the wafer level and Local CPs within each die. The Global CP maintains system-wide expert selection and placement information for intelligent resource management. Second, we extend the D2D controller with an Address Translation Unit (ATU) and a Prediction Unit (PDU). The ATU translates remote HBM addresses to local addresses when remote data is duplicated, while the PDU identifies important remote data requiring duplication. These enable autonomous caching of remote data in local HBM and intelligent redirection of data requests, reducing inter-die communication overhead.

2) Key Data Structures: There are two key data structures: Global CP data and the PDU prediction table.

Global CP Data Structures: As shown in Figure 9(c), the Global CP maintains two structures. The expert distribution table stores each expert's initial die ID and distribution status as an n-bit binary code, where each bit indicates expert presence on the corresponding die. The cross-token heatmap records expert activation patterns over time, providing historical data for prediction generation.

<u>PDU</u> Prediction <u>Table:</u> Each PDU stores a prediction table with two key fields per expert: the cp\_en bit indicating whether the expert should be cached locally (calculated by Global CP and transferred before computation), and the is\_local bit tracking whether the expert is already cached (maintained by PDU itself).

- 3) Workflow During Kernel Launch: When a new kernel launches (1), the Global CP implements our task allocation algorithm to split the MoE kernel into sub-kernels for each die and executes the predictor algorithm to generate duplication guidance (cp\_en field is PDU). The Global CP then sends sub-kernels and prediction information to local CPs (2). After receiving the guidance information from Global CP, each local CP allocates tasks to its SMs (3) and configures the prediction table in the D2D controller for local HBM management (4). After computation, the local CP collects expert duplication statistics and sends them to the Global CP to update expert distribution information.

- 4) Dataflow for Remote Data Access: We integrate ATU and PDU into the D2D controller to support hardware-

# Algorithm 1: Task Allocation Algorithm

```

Input: expert_reqs_dict, expert_die_map

Output: allo\_plan

Initialize the workload of each die: load per die;

for (expert_id, req_num) in expert_req_dict do

candi\_list \leftarrow GenCandidateList (expert\_id,

3

4

candi\ list \leftarrow Sort\ (candi\ list,

i \mapsto load\_per\_die[i]);

candi\_list \leftarrow candi\_list[0:max\_split\_num];

while req\_num > 0 do

costs\_of\_dies \leftarrow \texttt{CostModel}(candi\_list):

7

8

target \ die \leftarrow Argmin(costs \ of \ dies);

allo_plan.append([expert_id, target_die,

req\_blk]);

Update(load_per_die);

10

req\_num \leftarrow req\_num - req\_blk;

11

allo\_plan \leftarrow MergeTasks(allo\_plan);

12

13 return allo_plan;

Function GenCandidateList (expert_id, dis):

14

local\ die\ list = expert\ die\ map[expert\ id];

15

remote die list = FindNearDies (local die list,

16

\mathbf{return}\ local\_die\_list + remote\_die\_list;

17

```

managed HBM by modifying the remote data access flow. With these two units, our architecture automatically duplicates important remote data in local HBM, with green lines representing non-duplicated data reads and blue lines representing duplicated data reads, as shown in Figure 9(a).

Remote Data Read (Non-duplicated): When an SM reads remote data not in local HBM (1), the D2D controller routes the request conventionally (2). Upon return, the PDU checks the Prediction Table to make a duplication decision and sends data to the SM regardless of the decision (3). If duplication is required, the PDU writes to LLC and local HBM (4, 5), updates the address into ATU, and sets the is\_local bit in PDU's Prediction Table to 1.

Local Data Read (Duplicated): When an SM reads remote data already cached in local HBM (1), the ATU translates the remote address to a local address and redirects the request to LLC (2). The LLC and memory controller then retrieve data and send it back to the SM(3, 4).

5) Algorithm Design: This subsection presents our task allocation algorithm and data-driven predictor, both implemented by the global CP.

Task Allocation Algorithm: Since accurate task distribution is NP-hard, we propose two heuristic mechanisms: a candidate mechanism that reduces the number of dies to consider and a block-granularity distribution mechanism that searches for approximate solutions among candidates.

This algorithm splits MoE kernel computation into subtasks for individual dies based on expert selection and distribution information. As shown in algorithm 1, the input  $expert\_reqs\_dict$  contains the number of requests belonging to each expert, while  $expert\_die\_map$  provides dynamic expert distribution information from the Expert Distribution

Table in Figure 9(c), indicating where each expert is stored.

The algorithm iterates through all experts to generate allocation plans. For each expert, it creates a candidate die list including dies storing expert weights and their adjacent dies (shown as green and red in Figure 10(a)). We sort candidates by workload and limit the list to  $max_split_num$ dies, determined by the expert's request count (line 3-5). Requests are distributed to candidate dies in blocks of size 50 to balance efficiency and accuracy (line 6-11). For each block, the algorithm selects the optimal die using our cost model, which considers DRAM access, computation, and dieto-die communication. Finally, we merge blocks allocated to the same die to generate the final allocation plan (line 12). Data-Driven Predictor: Our predictor algorithm, implemented by the global CP, uses current MoE kernel expert selection information to predict popular experts for the next token on each die. This prediction result is transferred to local CPs and configured in each die's PDU to guide hardware-managed local HBM. As shown by the red shadow in Figure 10(b), we first identify corresponding rows from the heatmap based on current expert selection  $(\mathbf{1})$ , then select the top n experts from each row (2) and identify corresponding experts for the next token as prediction results, denoted by the green shadow (3). In this example, a die computes experts 1 and 4 during the current MoE kernel and we predict experts 2, 4, and 6 will be used next. Since this die only reads experts 1 and 4 currently, we duplicate only expert 4 in its local DRAM.

# V. EVALUATION

#### A. Experiment Setup

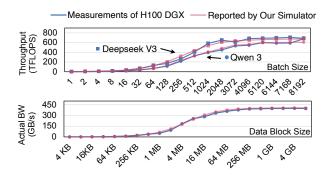

**Methodology:** We conduct experiments using trace-driven simulation on a validated simulator. Expert selection traces are collected by deploying SGLang [80] on an 8×H100 DGX server and an 8×H200 AWS instance.

We developed a custom multi-chiplet GPU simulator in Python since existing tools are inadequate for our needs. Cycle-accurate simulators like Gem5 [3], gpgpusim [2], and mgpusim [57] accurately model single GPUs but are too slow for large-scale systems with 20+ GPUs serving batch sizes exceeding 15,000. Event-driven ASTRA-sim [69] supports multi-GPU systems but lacks MoE serving support and detailed single-GPU microarchitecture modeling. To ensure accuracy, we validated our simulator against real data from an 8×H100 DGX server, as shown in Sec. V-B.

Our simulator models multi-chiplet GPU components, including LLC, HBM, compute units, and D2D links across all dies. A central resource manager simulates contention and congestion by dividing each expert execution into multiple events and managing simultaneous execution of thousands of events. The simulator supports configurable die numbers, placement, and connectivity. To balance accuracy and efficiency, we simulate MoE models at expert slice granularity, with each expert comprising two slices.

**Metric:** We measure pure MoE layer performance during the decode stage as modern LLM serving systems show a trend

Table I HARDWARE CONFIGURATIONS

|               | X-die                                                                                        | Y-die | DRAM<br>BW | D2D<br>BW | DRAM  | Cmpt Power<br>per Die (FP8) |

|---------------|----------------------------------------------------------------------------------------------|-------|------------|-----------|-------|-----------------------------|

| Dojo          | 5                                                                                            | 5     | 2 TB/s     | 1.5 TB/s  | 80GB  | 1000 TFLOPS                 |

| TSMC-SoW      | 3                                                                                            | 8     | 2 TB/s     | 1.5 TB/s  | 80GB  | 1000 TFLOPS                 |

| Dojo-Enhanced | 5                                                                                            | 5     | 8 TB/s     | 2 TB/s    | 180GB | 4500 TFLOPS                 |

|               | LLC hit latency: 100ns, LLC miss penalty: 110ns,<br>LLC write latency: 30ns, LLC size: 64 MB |       |            |           |       |                             |

| Other Params  | D2D link latency: 200ns, Routing Alg: XY routing,                                            |       |            |           |       |                             |

|               | Command and address size for each remote request: 16B                                        |       |            |           |       |                             |

Loca HBM access latency: 300 ns

toward fine-granularity disaggregation. Traditional LLMs benefit from separating prefill and decode stages across different machines, as demonstrated by DistServe [81] and subsequent works [47], [70]. For MoE models, this disaggregation extends further. MegaScale-Infer [82] separates attention and MoE operations onto different machines for optimal batch sizes. Following this trend, we focus on optimizing MoE operations during the decode stage.

**Hardware Configuration:** We evaluate two multi-chiplet topologies: Tesla Dojo [60], [61] and the TSMC SoW roadmap [64]. As summarized in Table I, Dojo uses a  $5\times5$  2D mesh, while TSMC SoW adopts an  $8\times3$  2D mesh. These choices reflect a deployed system (Dojo) and near-future industry support (TSMC SoW).

For both the Dojo and TSMC SoW configurations, each chiplet is A100-like, providing 1,000 TFLOPS FP8 compute, 80GB HBM, 2TB/s local HBM bandwidth, and 1.5 TB/s inter-die bandwidth to adjacent chiplets. We also include an extended experiment in Sec. V-F with a Dojo-Enhanced configuration, where each die is B300-like to reflect an anticipated hardware performance trend in the future. We reserve 10% of DRAM for system and hardware management.

Baseline Configurations: We compare our approach against the simple strategy currently used by GPU. The Base configuration assigns equal numbers of experts to each die but ignores expert placement when allocating tasks. We implement three variants: Allo Only uses solely our task allocation strategy; Pred Only includes only the data-driven predictor; and Allo+Pred combines both techniques. These configurations evaluate the individual and combined effects of our proposed methods.

**Models and Workloads:** We conduct evaluations with real traces collected from Qwen3 and Deepseek V3. The traces are gathered from diverse datasets, including MMLU [23], MMLU Pro [67], ChineseSimpleQA [22], and LiveCodeBench [29], comprising over 24,000 requests per model.

#### B. Validation of Simulator

We validate our simulator using real measurements from an 8×H100 DGX server. We evaluate both single-GPU execution and two-GPU peer-to-peer (P2P) communication. For single-GPU execution, we benchmark GEMM operations for experts in the MoE layer across varying batch sizes for both DeepSeek and Qwen. For P2P communication, we measure data migra-

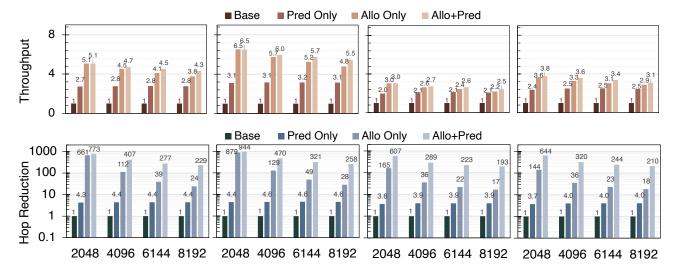

Figure 11. Throughput of MoE layers (Top) and hop number reduction ratio (Bottom). All figures are scaled to baseline.

Figure 12. Simulator validation with real data generated from 8xH100 DGX, including both MoE GEMM (Top) and P2P data transfer (Bottom) test cases.

tion between two GPUs over payload sizes ranging from 4 KB to 4 GB. To ensure simulation fidelity, we calibrate key parameters to fit the measured data. As shown in Figure 12, the simulator's error remains within 5% for all test cases.

# C. Throughput

We evaluate MoE decode stage throughput in Figure 11, with results normalized to the baseline configuration.

Comparison across models: Our Allo+Pred strategy achieves  $5.3 \times$  throughput improvement on Deepseek and  $3.1 \times$  on Qwen. Deepseek shows greater improvement due to its larger number of experts (256 vs. 128) and more complex expert selection patterns. Without our expert placement-aware allocation, serving Deepseek introduces significantly more inter-unit communication than Qwen. Since our task allocation strategy places computation close to data, it yields more substantial improvements on Deepseek.

Comparison across chiplet architectures: Our Allo+Pred strategy shows  $3.7 \times$  improvement on Dojo and  $4.7 \times$  on TSMC, despite similar die counts (25 vs. 24). The improvement on TSMC is more substantial due to its rectangular

layout, where dies are farther apart, introducing more interunit communication without strategic task allocation.

# D. Hop Reduction

We report hop counts in Figure 11 to show the reduction in inter-unit communication. Hop count is the sum of Manhattan distances for all cross-unit communications. Higher hop counts indicate frequent cross-die data movement. We normalize results to baseline and report hop reduction ratios, where a ratio of 10 means hop count is reduced to 1/10.

**Pred Only** reduces hop counts by  $3.7 \times -4.4 \times$ , aligning with performance results in Figure 11. This indicates cross-unit communication is the primary bottleneck in baseline, and reducing hop counts proportionally improves performance.

**Allo Only** reduces hop counts by  $7.2 \times -10.8 \times$ , exceeding the performance improvement range of  $17 \times -661 \times$ . This shows that with our allocation algorithm, inter-unit communication is no longer the sole bottleneck. While reducing hop counts still improves performance, the improvement is not proportional.

Allo+Pred reduces hop counts by over  $210 \times -944 \times$  compared to baseline and achieves  $10 \times$  improvement over Allo Only. However, performance improvement is only  $2.5 \times -6.5 \times$  over baseline, with just  $1.2 \times$  average improvement over Allo Only. This demonstrates that hop count is no longer a performance bottleneck. Our task allocation successfully places computation near relevant data. Most tasks are distributed to local dies holding related experts, with only extremely popular experts requiring remote allocation. This leads to minimal D2D traffic and shifts the bottleneck to workload distribution.

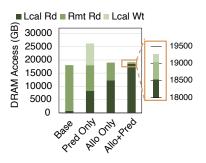

# E. DRAM Access Breakdown

We provide a breakdown of DRAM access patterns in Figure 13 to show how our strategies reduce inter-unit communication. We categorize DRAM access into three types: reads from local dies, reads from remote dies, and writes to local dies, where writes to local dies only occur when we duplicate a remote expert locally. Most reads in the baseline

Figure 13. DRAM access breakdown for Qwen3 on TSMC-SoW Configuration with batch size 4096.

Figure 14. Host CPU implementation overhead under varying models and batch sizes.

are from remote dies, resulting in high inter-unit traffic and poor performance. With our strategies (Pred Only, Allo Only, and Allo+Pred), most remote DRAM reads are converted to local DRAM reads, significantly reducing traffic. Compared with Pred Only, Allo+Pred achieves fewer remote reads by allocating most tasks to local dies, with only extremely popular experts requiring computation across multiple dies. Compared with Allo Only, Allo+Pred further reduces remote reads by caching popular experts in local HBM.

#### F. Comparison with Host CPU-Based Implementation

Our task allocation algorithm runs on a new GPU command processor, but it could, in principle, be executed on the host CPU with a higher overhead. As shown in Figure 14, we evaluate both the Dojo and Dojo-Enhanced configurations. In Dojo, the overhead of host-CPU allocation is 5.2%–6.4% for DeepSeek V3 and 11.1%–14.2% for Qwen3. In Dojo-Enhanced, the overhead rises to 19.3%–23.8% for DeepSeek V3 and 42.0%–51.6% for Qwen3.

**DeepSeek vs Qwen:** Qwen3 incurs higher overhead than DeepSeek V3 due to CPU–GPU data transfers over PCIe, which occur once per MoE layer. The CPU needs the Expert Distribution Table from the GPU to run the allocator, and the allocation results must be sent back to the GPU before kernel execution. Qwen3 has (i) more MoE layers (94 vs. 58), increasing transfer frequency, and (ii) smaller per-layer compute, which amplifies the relative cost of transfers.

**Dojo vs Dojo-Enhanced:** Dojo-Enhanced shows over 3.7× higher overhead than Dojo because its GPU dies are significantly faster, making fixed PCIe transfer costs dominate more. As GPU performance outpaces interconnect bandwidth, implementing the allocator in the GPU command processor becomes increasingly necessary to sustain performance.

# G. Discussion

This wafer-scale GPU architecture serves as a case study demonstrating the practical applicability of our proposed insights, which constitute the paper's primary contribution. Our design implements only a subset of the proposed insights to validate their effectiveness. We follow Insight 3 for task allocation and leverage temporal relation insights (Insight 1

and part of Insight 2) to build a data-driven predictor. However, the remaining insights offer significant potential for further exploitation in wafer-scale architectures. For instance, Insight 2 could inform LLC prefetch strategies and enhance task allocation algorithms that consider LLC data placement. Spatial relation insights (Insight 4 and Insight 5) could optimize initial expert placement, which could be further refined by incorporating task information from Insight 6. Importantly, our insights extend far beyond this case study to benefit diverse future systems, including multi-GPU clusters [79], [82], CXL-based or CPU-based memory disaggregation [4], [13], Flash-based multi-hierarchy systems [51], [76], and other emerging architectures and systems.

#### VI. RELATED WORK

MoE model behavior studies: Several MoE model tech reports [8], [30], [42], [56] provide the MoE routing patterns as part of their evaluation. For example, the Mixtral report [30] shows the temporal locality of expert selection by reporting the percentage of repetitive assignment. The OLMoE report [42] shows the co-activation pattern and domain specialization among the experts. A blog post from SGLang [16] shows expert distribution statistics for the DeepSeekV3 model and the inherent imbalance in expert selection and similarity between prefill and decode. None of these studies provides a comprehensive profiling across multiple large-scale (>200B) MoE models, nor do they present a data-movement-centric methodology to highlight the opportunities like this paper.

Data movement optimization for MoE LLM inference Various prior work [4], [11], [12], [19], [27], [28], [31], [33], [34], [54], [77]–[79] have focused on improving the efficiency of MoE LLM inference by reducing data movement. For example, Lina [34] exploits the skewness in expert selection to dynamically schedule resources during inference and balance traffic across multiple GPUs. LYNX [19] dynamically reduces active experts while preserving model accuracy. Pregate MoE [28] uses a pre-gating function to alleviate the dynamic nature of expert selection. Sida [11] builds an offline hash function to predict expert usage to reduce data movement between CPU and GPU. MoE-Lightning [4] leverages a CPU-GPU pipeline and paged weights to improve resource utilization. Eliseev and Mazur [12] exploit expert locality and leverage LRU caching to manage GPU and CPU memory. This work aims to reduce data movement in MoE LLM inference of today's systems, and our case study shows that data-driven profiling across multiple models provides a solid base to optimize not only current but future systems of any scale.

Wafer-Scale and Chiplet Architectures As single chip scaling slows down, packaging technologies such as wafer-scale and chiplet packaging have become a promising path to further improve compute efficiency for future systems. Recent work in this area either focuses on the interconnect design [5], [14], [15], [35], [48], [73], [75] of wafer-scale and chiplet systems, or general data placement for specific algorithms [21], [62] and applications [46], [50], [71]. In contrast, our work is the first to study the implications of serving large-scale MoE LLMs in a

wafer-scale GPU and propose data-movement-centric HW/SW co-design optimizations.

# VII. CONCLUSION

In this work, unlike previous MoE serving works that adopt system-centric approaches and develop deployment-specific strategies, we study MoE model serving from a model-focused perspective We conducted comprehensive data-movement-centric profiling of the latest large-scale MoE models (200B-1000B) to extract system-agnostic insights. These insights reveal underlying patterns behind seemingly random data movement, providing actionable guidance for designing diverse future MoE serving systems. We validate our insights on a wafer-scale GPU architecture and achieve significant performance improvements with minimal modifications.

#### REFERENCES

- J. Achiam, S. Adler, S. Agarwal, L. Ahmad, I. Akkaya, F. L. Aleman, D. Almeida, J. Altenschmidt, S. Altman, S. Anadkat *et al.*, "Gpt-4 technical report," *arXiv*, 2023.

- [2] A. Bakhoda, G. L. Yuan, W. W. Fung, H. Wong, and T. M. Aamodt, "Analyzing cuda workloads using a detailed gpu simulator," in 2009 IEEE international symposium on performance analysis of systems and software, 2009.

- [3] N. Binkert, B. Beckmann, G. Black, S. K. Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R. Hower, T. Krishna, S. Sardashti et al., "The gem5 simulator," ACM SIGARCH computer architecture news, 2011.

- [4] S. Cao, S. Liu, T. Griggs, P. Schafhalter, X. Liu, Y. Sheng, J. E. Gonzalez, M. Zaharia, and I. Stoica, "Moe-lightning: High-throughput moe inference on memory-constrained gpus," in *Proceedings of the 30th ACM International Conference on Architectural Support for Programming Languages and Operating Systems*, 2025.

- [5] S. Chen, S. Pal, and R. Kumar, "Waferscale network switches," in 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA). IEEE, 2024, pp. 215–229.

- [6] W.-L. Chiang, L. Zheng, Y. Sheng, A. N. Angelopoulos, T. Li, D. Li, B. Zhu, H. Zhang, M. Jordan, J. E. Gonzalez et al., "Chatbot arena: An open platform for evaluating llms by human preference," in Forty-first International Conference on Machine Learning, 2024.

- [7] K. T. Chitty-Venkata, S. Madireddy, M. Emani, and V. Vishwanath, "Lexi: Layer-adaptive active experts for efficient moe model inference," arXiv preprint arXiv:2509.02753, 2025.

- [8] D. Dai, C. Deng, C. Zhao, R. Xu, H. Gao, D. Chen, J. Li, W. Zeng, X. Yu, Y. Wu et al., "Deepseekmoe: Towards ultimate expert specialization in mixture-of-experts language models," arXiv preprint arXiv:2401.06066, 2024.

- [9] P. Dalmia, R. S. Kumar, and M. D. Sinclair, "Cpelide: Efficient multichiplet gpu implicit synchronization," in 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO), 2024.

- [10] S. K. Dam, C. S. Hong, Y. Qiao, and C. Zhang, "A complete survey on llm-based ai chatbots," arXiv, 2024.

- [11] Z. Du, S. Li, Y. Wu, X. Jiang, J. Sun, Q. Zheng, Y. Wu, A. Li, H. Li, and Y. Chen, "Sida: Sparsity-inspired data-aware serving for efficient and scalable large mixture-of-experts models," *Proceedings of Machine Learning and Systems*, vol. 6, pp. 224–238, 2024.

- [12] A. Eliseev and D. Mazur, "Fast inference of mixture-of-experts language models with offloading," arXiv preprint arXiv:2312.17238, 2023.

- [13] Z. Fang, Y. Huang, Z. Hong, Y. Lyu, W. Chen, Y. Yu, F. Yu, and Z. Zheng, "Klotski: Efficient mixture-of-expert inference via expertaware multi-batch pipeline," in *Proceedings of the 30th ACM Interna*tional Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, 2025.

- [14] Y. Feng, D. Xiang, and K. Ma, "Heterogeneous die-to-die interfaces: Enabling more flexible chiplet interconnection systems," in *Proceedings* of the 56th Annual IEEE/ACM International Symposium on Microarchitecture, 2023, pp. 930–943.

- [15] —, "A scalable methodology for designing efficient interconnection network of chiplets," in 2023 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, 2023, pp. 1059– 1071

- [16] S. T. from LMSYS Org. (2025) Deploying deepseek with pd disaggregation and large-scale expert parallelism on 96 h100 gpus. [Online]. Available: https://lmsys.org/blog/2025-05-05-large-scale-ep/

- [17] —... (2025) Together with sglang: Best practices for serving deepseekr1 on h20-96g. [Online]. Available: https://lmsys.org/blog/2025-09-26sglang-ant-group/

- [18] S. Go and D. Mahajan, "Moetuner: Optimized mixture of expert serving with balanced expert placement and token routing," arXiv preprint arXiv:2502.06643, 2025.

- [19] V. Gupta, K. Sinha, A. Gavrilovska, and A. P. Iyer, "Lynx: Enabling efficient moe inference through dynamic batch-aware expert selection," arXiv preprint arXiv:2411.08982, 2024.

- [20] A. Gutierrez, B. M. Beckmann, A. Dutu, J. Gross, M. LeBeane, J. Kalamatianos, O. Kayiran, M. Poremba, B. Potter, S. Puthoor et al., "Lost in abstraction: Pitfalls of analyzing gpus at the intermediate language level," in 2018 IEEE International Symposium on High Performance Computer Architecture (HPCA), 2018.

- [21] C. He, Y. Huang, P. Mu, Z. Miao, J. Xue, L. Ma, F. Yang, and L. Mai, "Waferllm: Large language model inference at wafer scale," in 19th USENIX Symposium on Operating Systems Design and Implementation (OSDI 25). USENIX Association, 2025.

- [22] Y. He, S. Li, J. Liu, Y. Tan, W. Wang, H. Huang, X. Bu, H. Guo, C. Hu, B. Zheng *et al.*, "Chinese simpleqa: A chinese factuality evaluation for large language models," *arXiv preprint arXiv:2411.07140*, 2024.

- [23] D. Hendrycks, C. Burns, S. Basart, A. Zou, M. Mazeika, D. Song, and J. Steinhardt, "Measuring massive multitask language understanding," arXiv preprint arXiv:2009.03300, 2020.

- [24] S. Hou, W. C. Chen, C. Hu, C. Chiu, K. Ting, T. Lin, W. Wei, W. Chiou, V. J. Lin, V. C. Chang et al., "Wafer-level integration of an advanced logic-memory system through the second-generation cowos technology," *IEEE Transactions on Electron Devices*, 2017.

- [25] S. Hou, H. Hsia, C. Tsai, K. Ting, T. Yu, Y. Lee, F. Chen, W. Chiou, C. Wang, C. Wu et al., "Integrated deep trench capacitor in si interposer for cowos heterogeneous integration," in 2019 IEEE International Electron Devices Meeting (IEDM). IEEE, 2019, pp. 19–5.

- [26] Y.-C. Hu, Y.-M. Liang, H.-P. Hu, C.-Y. Tan, C.-T. Shen, C.-H. Lee, and S. Hou, "Cowos architecture evolution for next generation hpc on 2.5 d system in package," in 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), 2023.

- [27] C. Hwang, W. Cui, Y. Xiong, Z. Yang, Z. Liu, H. Hu, Z. Wang, R. Salas, J. Jose, P. Ram et al., "Tutel: Adaptive mixture-of-experts at scale," Proceedings of Machine Learning and Systems, vol. 5, pp. 269–287, 2023

- [28] R. Hwang, J. Wei, S. Cao, C. Hwang, X. Tang, T. Cao, and M. Yang, "Pre-gated moe: An algorithm-system co-design for fast and scalable mixture-of-expert inference," in 2024 ACM/IEEE 51st Annual International Symposium on Computer Architecture (ISCA). IEEE, 2024, pp. 1018–1031.

- [29] N. Jain, K. Han, A. Gu, W.-D. Li, F. Yan, T. Zhang, S. Wang, A. Solar-Lezama, K. Sen, and I. Stoica, "Livecodebench: Holistic and contamination free evaluation of large language models for code," arXiv preprint arXiv:2403.07974, 2024.

- [30] A. Q. Jiang, A. Sablayrolles, A. Roux, A. Mensch, B. Savary, C. Bamford, D. S. Chaplot, D. d. l. Casas, E. B. Hanna, F. Bressand et al., "Mixtral of experts," arXiv preprint arXiv:2401.04088, 2024.

- [31] K. Kamahori, T. Tang, Y. Gu, K. Zhu, and B. Kasikci, "Fiddler: CPU-GPU orchestration for fast inference of mixture-of-experts models," in *The Thirteenth International Conference on Learning Representations*, 2025. [Online]. Available: https://openreview.net/forum?id=N5fVv6PZGz

- [32] M. LeBeane, K. Hamidouche, B. Benton, M. Breternitz, S. K. Reinhardt, and L. K. John, "Comp-net: Command processor networking for efficient intra-kernel communications on gpus," in *Proceedings of the 27th International Conference on Parallel Architectures and Compilation Techniques*, 2018.

- [33] J. Li, S. Tripathi, L. Rastogi, Y. Lei, R. Pan, and Y. Xia, "Optimizing mixture-of-experts inference time combining model deployment and communication scheduling," arXiv preprint arXiv:2410.17043, 2024.

- [34] J. Li, Y. Jiang, Y. Zhu, C. Wang, and H. Xu, "Accelerating distributed moe training and inference with lina," in 2023 USENIX Annual Technical Conference (USENIX ATC 23), 2023, pp. 945–959.

- [35] Z. Li and D. Wentzlaff, "Lucie: A universal chiplet-interposer design framework for plug-and-play integration," in 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO). IEEE, 2024, pp. 423–436.

- [36] A. Liu, B. Feng, B. Xue, B. Wang, B. Wu, C. Lu, C. Zhao, C. Deng, C. Zhang, C. Ruan et al., "Deepseek-v3 technical report," arXiv preprint arXiv:2412.19437, 2024.

- [37] Y. Lu, W. Zhu, L. Li, Y. Qiao, and F. Yuan, "Llamax: Scaling linguistic horizons of llm by enhancing translation capabilities beyond 100 languages," arXiv, 2024.

- [38] M. Lundstrom, "Moore's law forever?" Science, 2003.

- [39] R. Mahajan, R. Sankman, N. Patel, D.-W. Kim, K. Aygun, Z. Qian, Y. Mekonnen, I. Salama, S. Sharan, D. Iyengar et al., "Embedded multi-die interconnect bridge (emib)—a high density, high bandwidth packaging interconnect," in 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), 2016.

- [40] S. Masoudnia and R. Ebrahimpour, "Mixture of experts: a literature survey," Artificial Intelligence Review, pp. 275–293, 2014.

- [41] Meta. (2025) Llama4 technical report. [Online]. Available: https://ai.meta.com/blog/llama-4-multimodal-intelligence/

- [42] N. Muennighoff, L. Soldaini, D. Groeneveld, K. Lo, J. Morrison, S. Min, W. Shi, P. Walsh, O. Tafjord, N. Lambert *et al.*, "Olmoe: Open mixtureof-experts language models," *arXiv preprint arXiv:2409.02060*, 2024.

- [43] D. Nam, A. Macvean, V. Hellendoorn, B. Vasilescu, and B. Myers, "Using an Ilm to help with code understanding," in *Proceedings of the IEEE/ACM 46th International Conference on Software Engineering*, ser. ICSE, '24, 2024.

- [44] NVIDIA, "Nvidia blackwell architecture overview," https://resources. nvidia.com/en-us-blackwell-architecture, 2025.

- [45] —, "Nvidia gtc 2025," https://www.nvidia.com/gtc/, 2025.

- [46] M. Odema, L. Chen, H. Kwon, and M. A. Al Faruque, "Scar: Scheduling multi-model ai workloads on heterogeneous multi-chiplet module accelerators," in 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO). IEEE, 2024, pp. 565–579.

- [47] R. Qin, Z. Li, W. He, J. Cui, F. Ren, M. Zhang, Y. Wu, W. Zheng, and X. Xu, "Mooncake: Trading more storage for less computation—a {KVCache-centric} architecture for serving {LLM} chatbot," in 23rd USENIX Conference on File and Storage Technologies (FAST 25), 2025.

- [48] S. Rashidi, W. Won, S. Srinivasan, P. Gupta, and T. Krishna, "Fred: A wafer-scale fabric for 3d parallel dnn training," in *Proceedings of the* 52nd Annual International Symposium on Computer Architecture, 2025, pp. 34–48.

- [49] P. Schober, C. Boer, and L. A. Schwarte, "Correlation coefficients: appropriate use and interpretation," *Anesthesia & analgesia*, 2018.

- [50] Y. S. Shao, J. Clemons, R. Venkatesan, B. Zimmer, M. Fojtik, N. Jiang, B. Keller, A. Klinefelter, N. Pinckney, P. Raina et al., "Simba: Scaling deep-learning inference with multi-chip-module-based architecture," in Proceedings of the 52nd annual IEEE/ACM international symposium on microarchitecture, 2019, pp. 14–27.

- [51] Y. Sheng, L. Zheng, B. Yuan, Z. Li, M. Ryabinin, B. Chen, P. Liang, C. Ré, I. Stoica, and C. Zhang, "Flexgen: High-throughput generative inference of large language models with a single gpu," in *International Conference on Machine Learning*, 2023.

- [52] P.-C. Shih, A.-J. Su, K.-H. Tam, T.-C. Huang, K. Chuang, and J. Yeh, "Sow-x: A novel system-on-wafer technology for next generation ai server application," in 2025 IEEE 75th Electronic Components and Technology Conference (ECTC). IEEE, 2025.

- [53] J. Shin, H. Eslampour, S. Jeong, W. Kim, S. Yong, S.-O. Ahn, E. Park, and S. Song, "Signal integrity of die-to-die interface with advanced packages for co-packaged optics," in 2024 IEEE 33rd Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 2024.

- [54] A. Skliar, T. van Rozendaal, R. Lepert, T. Boinovski, M. Van Baalen, M. Nagel, P. Whatmough, and B. E. Bejnordi, "Mixture of cacheconditional experts for efficient mobile device inference," arXiv preprint arXiv:2412.00099, 2024.

- [55] A. Smith, G. H. Loh, J. Wuu, S. Naffziger, T. Huang, H. McIntyre, R. Mangaser, W. Jung, and R. Swaminathan, "Amd instinct™ mi300x accelerator: Packaging and architecture co-optimization," in 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). IEEE, 2024.

- [56] X. Sun, Y. Chen, Y. Huang, R. Xie, J. Zhu, K. Zhang, S. Li, Z. Yang, J. Han, X. Shu et al., "Hunyuan-large: An open-source moe model with 52 billion activated parameters by tencent," arXiv preprint arXiv:2411.02265, 2024.

- [57] Y. Sun, T. Baruah, S. A. Mojumder, S. Dong, X. Gong, S. Treadway, Y. Bao, S. Hance, C. McCardwell, V. Zhao et al., "Mgpusim: Enabling multi-gpu performance modeling and optimization," in *Proceedings of the 46th International Symposium on Computer Architecture*, 2019.

- [58] J. Suo, X. Liao, L. Xiao, L. Ruan, J. Wang, X. Su, and Z. Huo, "Coserve: Efficient collaboration-of-experts (coe) model inference with limited memory," in *Proceedings of the 30th ACM International Conference* on Architectural Support for Programming Languages and Operating Systems, 2025.

- [59] S. Tairin, S. Mahmud, H. Shen, and A. Iyer, "emoe: Task-aware memory efficient mixture-of-experts-based (moe) model inference," arXiv preprint arXiv:2503.06823, 2025.

- [60] E. Talpes, D. D. Sarma, D. Williams, S. Arora, T. Kunjan, B. Floering, A. Jalote, C. Hsiong, C. Poorna, V. Samant et al., "The microarchitecture of dojo, tesla's exa-scale computer," *IEEE Micro*, 2023.

- [61] E. Talpes, D. Williams, and D. D. Sarma, "Dojo: The microarchitecture of tesla's exa-scale computer," in 2022 IEEE Hot Chips 34 Symposium (HCS), 2022.

- [62] Z. Tan, H. Cai, R. Dong, and K. Ma, "Nn-baton: Dnn workload orchestration and chiplet granularity exploration for multichip accelerators," in 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2021, pp. 1013–1026.

- [63] K. Team, Y. Bai, Y. Bao, G. Chen, J. Chen, N. Chen, R. Chen, Y. Chen, Y. Chen, Y. Chen et al., "Kimi k2: Open agentic intelligence," arXiv preprint arXiv:2507.20534, 2025.

- [64] TSMC. (2025)Tsmc's generation next of system-onwill make today's cpus and package wafer gpus look feeble [Online]. pathetically in comparison. Available: https://www.pcgamer.com/hardware/processors/tsmcs-next-generationof-system-on-wafer-packaging-will-make-todays-cpus-and-gpus-lookpathetically-feeble-in-comparison/

- [65] S. Vakayil, D. S. Juliet, S. Vakayil et al., "Rag-based llm chatbot using llama-2," in 2024 7th International Conference on Devices, Circuits and Systems (ICDCS), 2024.

- [66] A. Vaswani, N. Shazeer, N. Parmar, J. Uszkoreit, L. Jones, A. N. Gomez, Ł. Kaiser, and I. Polosukhin, "Attention is all you need," Advances in neural information processing systems, 2017.

- [67] Y. Wang, X. Ma, G. Zhang, Y. Ni, A. Chandra, S. Guo, W. Ren, A. Arulraj, X. He, Z. Jiang et al., "Mmlu-pro: A more robust and challenging multi-task language understanding benchmark," Advances in Neural Information Processing Systems, 2024.

- [68] Y. Wang, W. Wang, S. Joty, and S. C. H. Hoi, "Codet5: Identifier-aware unified pre-trained encoder-decoder models for code understanding and generation," arXiv, 2021.

- [69] W. Won, T. Heo, S. Rashidi, S. Sridharan, S. Srinivasan, and T. Krishna, "Astra-sim2. 0: Modeling hierarchical networks and disaggregated systems for large-model training at scale," in 2023 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2023.

- [70] B. Wu, S. Liu, Y. Zhong, P. Sun, X. Liu, and X. Jin, "Loongserve: Efficiently serving long-context large language models with elastic sequence parallelism," in *Proceedings of the ACM SIGOPS 30th Symposium on Operating Systems Principles*, 2024, pp. 640–654.

- [71] Z. Xu, D. Kong, J. Liu, J. Li, J. Hou, X. Dai, C. Li, S. Wei, Y. Hu, and S. Yin, "Wsc-llm: Efficient llm service and architecture co-exploration for wafer-scale chips," in *Proceedings of the 52nd Annual International* Symposium on Computer Architecture, 2025, pp. 1–17.

- [72] A. Yang, A. Li, B. Yang, B. Zhang, B. Hui, B. Zheng, B. Yu, C. Gao, C. Huang, C. Lv et al., "Qwen3 technical report," arXiv preprint arXiv:2505.09388, 2025.

- [73] Q. Yang, T. Wei, S. Guan, C. Li, H. Shang, J. Deng, H. Wang, C. Li, L. Wang, Y. Zhang et al., "Pd constraint-aware physical/logical topology co-design for network on wafer," in *Proceedings of the 52nd Annual International Symposium on Computer Architecture*, 2025, pp. 49–64.

- [74] J. Yao, Q. Anthony, A. Shafi, H. Subramoni, and D. K. D. Panda, "Exploiting inter-layer expert affinity for accelerating mixture-of-experts model inference," in 2024 IEEE International Parallel and Distributed Processing Symposium (IPDPS). IEEE, 2024.

- [75] X. Yu, D. Jiang, J. Deng, J. Liu, C. Li, S. Yin, and Y. Hu, "Cramming a data center into one cabinet, a co-exploration of computing and hardware

- architecture of waferscale chip," in *Proceedings of the 52nd Annual International Symposium on Computer Architecture*, 2025, pp. 631–645.

- [76] Z. Yu, S. Liang, T. Ma, Y. Cai, Z. Nan, D. Huang, X. Song, Y. Hao, J. Zhang, T. Zhi et al., "Cambricon-llm: A chiplet-based hybrid architecture for on-device inference of 70b llm," in 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO), 2024.

- [77] S. Yun, K. Kyung, J. Cho, J. Choi, J. Kim, B. Kim, S. Lee, K. Sohn, and J. H. Ahn, "Duplex: A device for large language models with mixture of experts, grouped query attention, and continuous batching," in 2024 57th IEEE/ACM International Symposium on Microarchitecture (MICRO), 2024.

- [78] M. Zhai, J. He, Z. Ma, Z. Zong, R. Zhang, and J. Zhai, "{SmartMoE}: Efficiently training sparsely-activated models through combining offline and online parallelization," in 2023 USENIX Annual Technical Conference (USENIX ATC 23), 2023, pp. 961–975.

- [79] S. Zhang, N. Zheng, H. Lin, Z. Jiang, W. Bao, C. Jiang, Q. Hou, W. Cui, S. Zheng, L.-W. Chang, Q. Chen, and X. Liu, "COMET: Fine-grained computation-communication overlapping for mixture-of-experts," in *Eighth Conference on Machine Learning and Systems*, 2025. [Online]. Available: https://openreview.net/forum?id=fGgQS5VW09

- [80] L. Zheng, L. Yin, Z. Xie, C. L. Sun, J. Huang, C. H. Yu, S. Cao, C. Kozyrakis, I. Stoica, J. E. Gonzalez et al., "Sglang: Efficient execution of structured language model programs," Advances in neural information processing systems, 2024.

- [81] Y. Zhong, S. Liu, J. Chen, J. Hu, Y. Zhu, X. Liu, X. Jin, and H. Zhang, "{DistServe}: Disaggregating prefill and decoding for goodput-optimized large language model serving," in 18th USENIX Symposium on Operating Systems Design and Implementation (OSDI 24), 2024.

- [82] R. Zhu, Z. Jiang, C. Jin, P. Wu, C. A. Stuardo, D. Wang, X. Zhang, H. Zhou, H. Wei, Y. Cheng et al., "Megascale-infer: Serving mixtureof-experts at scale with disaggregated expert parallelism," arXiv preprint arXiv:2504.02263, 2025.