# PRO-V-R1: Reasoning Enhanced Programming Agent for RTL Verification

Yujie Zhao<sup>1</sup>, Zhijing Wu<sup>1</sup>, Boqin Yuan<sup>1</sup>, Zhongming Yu<sup>1</sup>, Hejia Zhang<sup>1</sup>, Wentao Ni<sup>1</sup>, Chia-Tung Ho<sup>2</sup>, Haoxing Ren<sup>2</sup>, Jishen Zhao<sup>1</sup>

<sup>1</sup>University of California San Diego <sup>2</sup>NVIDIA

{yuz285,b4yuan,zhy025,hez024,w2ni,jzhao}@ucsd.edu

neverakwu@gmail.com,chiatungh@nvidia.com,haoxingr@nvidia.com

#### **Abstract**

Register-Transfer Level (RTL) verification is a primary bottleneck consuming 60-70% of development time. While Large Language Models (LLMs) show promise for RTL automation, their performance and research focus have overwhelmingly centered on RTL generation rather than verification. Current methods for RTL verification rely on large scale proprietary models (e.g., GPT-40) to generate Python-based functional references, incurring a high cost and raising data-privacy risks. To date, an end-to-end open-source solution for autonomous verification remains absent.

We introduce PRO-V-R1, the first trainable open-source agentic framework for autonomous RTL verification. Our contributions are threefold: (1) we design PRO-V sys, a modular agentic system that couples LLM-based reasoning with programmatic tool use for RTL verification; (2) we establish a data construction pipeline that leverages existing RTL datasets to build simulation-validated, expert-level trajectories tailored for supervised fine-tuning (SFT) RTL verification agents; and (3) we implement an efficient reinforcement learning (RL) algorithm that uses verification-specific rewards derived from program-tool feedback to optimize the end-to-end verification workflow. Our empirical evaluation demonstrates PRO-V-R1 achieves a 57.7% functional correctness rate and 34.0% in robust fault detection, significantly outperforming the base model's 25.7% and 21.8% (respectively) from the state-of-the-art (SOTA) automatic verification system. This configuration also outperforms large-scale proprietary LLMs in functional correctness and shows comparable robustness for fault detection.

### Pro-V Training Code:

$https://github.com/pettingllms\hbox{-}ai/PettingLLMs$

### Pro-V Agentsys Code:

https://github.com/stable-lab/Pro-V

# 1 introduction

Hardware design verification is a critical stage in the VLSI design flow, ensuring that a Register-Transfer Level (RTL) implementation faithfully conforms to its functional specification. In simulation-based verification, this process fundamentally relies on an executable testbench that applies constrained stimuli to the Design Under Test (DUT), monitors its responses, and compares them against the expected behavior; the quality of this testbench largely

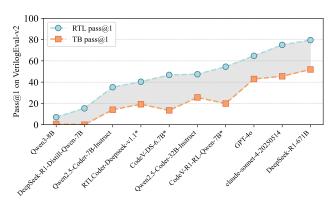

Figure 1: Performance comparison of different LLMs on RTL (green line) and testbench (blue line) generation. Models marked with \* are RTL-specific. TB pass@1 denotes that the golden reference RTL code passes the LLM-generated testbench.

determines which functional defects can be exposed before tapeout [1, 11]. However, constructing effective testbenches remains a labor-intensive process, which often accounts for 60% to 70% of the total development time, representing a significant bottleneck in the modern hardware design cycle [28].

Recent advances in large language models (LLMs) for verilog enable a promising path to automating verification workflows. Nevertheless, the vast majority of current research targets RTL generation, yielding numerous benchmark datasets [10, 15, 34] and specialized models [16, 31, 37, 39, 41]. In parallel with this distribution of research effort, we observe a divergence in model capabilities. As depicted in Fig. 1, contemporary LLMs perform consistently better in RTL generation (green line) compared to testbench generation (blue line)

While testbench generation is critical and presents a significantly greater challenge, research into LLM-based verification still heavily relies on commercial LLMs. To navigate the difficulty of direct hardware description generation, current efforts are converging on a more pragmatic paradigm: instead of generating complete Verilog testbenches, these approaches use LLMs to generate a *Python-based functional reference model (FRM)* for the DUT[22, 23, 30], which emulates its intended functional behavior. This Python-centric design is capability-driven, as modern code LLMs are substantially stronger on Python than on Verilog [3, 15].

However, this reliance on large-scale proprietary models (e.g., GPT-40) introduces critical limitations. Beyond high inference costs and data-privacy risks for sensitive IPs, the inability to fine-tune

```

Verilog Code

Python Code

reg [3:0] q = 1000

q = "1000"

// q3=1, q2=0, q1=0, q0=0

# q[0]=1,q[1]=0,q[2]=0,q[3]=0

```

Figure 2: Semantic gap in indexing and slicing: Verilog's significance-based q[3] (MSB) contrasts with Python's offset-based q[0]. Also, Verilog's inclusive-range slice q[3:2] ('10') maps to Python's half-open range q[0:2].

these generalist "black-box" models leads to frequent hallucinations, particularly where Python and Verilog semantics diverge (e.g., conflicting indexing and slicing mechanics, as shown in Fig. 2). While open-source efforts focus on RTL generation, verification lacks comparable open-source datasets and training frameworks. Consequently, a fully open-source, end-to-end solution for autonomous testbench generation remains absent.

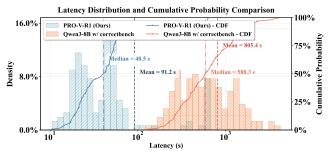

A clear path forward is to train open-source models capable of mastering the autonomous RTL verification workflow. However, realizing this goal presents three significant challenges due to the complexity of hardware verification: (i) Agentic System Inefficiency: SOTA baselines like CorrectBench [23] are computationally expensive (avg. 805 s/task) while using open-source model and are prone to storage explosion from complex compilation processes; (ii) Supervised Fine-tuning (SFT) Data Scarcity: Existing public datasets are predominantly tailored for RTL design and implementation, resulting in a critical lack of ground-truth verification trajectories required to effectively fine-tune agents for verification tasks; and (iii) Missing RL Training Framework: The field lacks a dedicated training framework to optimize agentic verification policies via reinforcement learning.

To address these challenges, we introduce PRO-V-R1: the first end-to-end open-source solution for autonomous RTL verification that enhances LLM reasoning with programmatic tools. Our contributions are as follows:

- We design PRO-V sys, a novel agentic system that enhances LLM reasoning with programmatic tool for autonomous RTL verification.

- We establish a data construction pipeline that leverages existing RTL datasets to construct verified expert-level trajectories tailored for the SFT of RTL verification agents.

- We implement an efficient RL algorithm using verification-specific structured rewards from programmatic tool feedback to optimize the end-to-end verification workflow.

Empirically, PRO-V-R1 achieves **57.7%** functional correctness and **34.0%** fault detection, outperforming SOTA agent system baselines (25.7%/21.8%) and matching or exceeding proprietary LLMs. Moreover, it provides an **8.8**× **speedup**, averaging just **91 s/task**.

### 2 Background and Motivation

# 2.1 LLM-based Verilog generation and verification

The preponderance of research in LLMs for RTL has concentrated on RTL code generation, including significant open-source efforts such as benchmark datasets [10, 15, 34] and specialized models [16, 31, 37, 39, 41]. In contrast, the emerging paradigm of LLM-aided RTL verification has shifted from direct HDL generation—a known challenge [3, 15]—towards generating Python-based FRMs [22, 23, 30]

within agent-controllable verification environments. However, this approach relies almost exclusively on large-scale, proprietary LLMs (e.g., GPT-40) [22, 30]. This dependency introduces high inference costs, data-privacy risks, and reliability issues; as "black-box" generalists, they cannot be fine-tuned and are prone to hallucinations where Python and Verilog semantics diverge. Consequently, agent systems, curated datasets, and training frameworks for LLM-aided RTL verification are scarce, leaving the community without open, reproducible models specialized for this new functional verification flow.

# 2.2 Tool-Enhanced LLM Agents with Post-training

Tool-enhanced agents leverage LLMs as controllers to interact with external, domain-specific tools [19, 26], often structured within a modular "agent flow" (e.g., planner, executor) to solve complex tasks [13]. An agent's effectiveness hinges on clear tool APIs [20, 21] and a robust policy for tool invocation. This policy is typically established via SFT on expert demonstrations, and then refined using RL from environmental feedback [18, 36]. The RL phase optimizes the policy by assigning a scalar "verified reward" to the agent's output, favoring actions that yield high-reward outcomes.

While this SFT-then-RL paradigm has been successfully applied in diverse domains, including mathematical reasoning [4, 7], web navigation [9, 38], and scientific discovery [2, 17], its application to hardware verification remains largely unexplored. This gap exists because a complete, effective training loop for verification requires addressing three critical, domain-specific challenges: (i) overcoming the scarcity of high-quality, verified reasoning traces for SFT; (ii) designing a trainable agent loop with a reward function that translates sparse simulation outcomes into a dense learning signal; and (iii) developing an effective optimization algorithm for credit assignment within the complex, multi-step agentic workflow. Our work is the first to bridge this gap by establishing this complete loop.

#### 3 Methods

To address the challenges in Sec. 1 and 2, we introduce PRO-V-R1, a program-tool-enhanced agentic framework for autonomous RTL verification, composed of two primary components: (1) an agentic verification system that instantiates modular agents equipped with specialized programmatic tools to interface with industrial simulators; and (2) an agentic training framework for RTL verification to optimize the full agentic workflow.

#### 3.1 Agentic Verification System

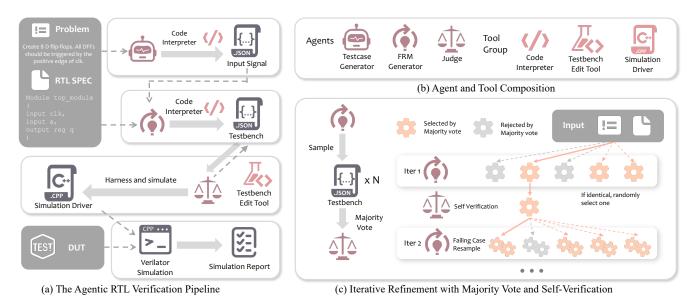

Our framework executes RTL verification through an autonomous agentic system, as illustrated in Fig 3. Leveraging the LLMs' tooluse capabilities and the industry-standard simulators like Verilator, our system mitigates the inherent limitations and hallucination associated with LLMs directly generating complex hybrid RTL testbenches, thereby enhancing the fidelity and correctness of the generated verification artifacts. This process integrates a society of agents with a specialized toolset (Fig. 3 (b)). The architecture is composed of three distinct agentic roles: the <u>Testcase Generator</u>, the <u>FRM Generator</u>, and the Judge. These agents are equipped with

Figure 3: Overview of the autonomous agent-based framework for RTL design verification. (a) The Agentic RTL Verification Pipeline, detailing the end-to-end process from high-level prompt and RTL specification to a final simulation report. (b) Agent and Tool Composition, defining the set of agentic roles and their corresponding callable tools. (c) Iterative Refinement with Majority Vote and Self-Verification, illustrating the sampling, selection, and self-correction loop used to enhance the quality of generated testbenches.

Table 1: Summary of Program-Based Tool APIs.

| <b>Tool Name</b> | Tool API            | <b>Argument Schema</b>                                                                                                   | <b>Example Argument</b>             | Output Artifact |                  |        |

|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|--------|

| Code Interpreter | <python></python>   | Python code snippet                                                                                                      | "def step(x): retu<br>0x3D) & 0xFF" | ırn ((x«1) ^    | Execution        | Output |

| Testbench Editor | <tb_edit></tb_edit> | op (add replace remove); target<br>(JSON Pointer of the field to mod-<br>ify); value (new content for ad-<br>d/replace). | location","value":                  | ","w":"0"},     | Updated<br>bench | Test-  |

a Tool Group comprising the *Code Interpreter*, the *Testbench Edit Tool*, and the *Simulation Driver*. The end-to-end verification flow (Fig. 3 (a)), detailed below, is executed in three main stages:

**1 Testcase Generation.** LLMs exhibit known weaknesses in operations requiring high numerical fidelity, such as precisely generating long numerical sequences (e.g., 256-bit vectors) [32, 33]. This inability directly conflicts with the stringent demands of RTL verification, which requires bit-accurate, width-sensitive (e.g., 128/512-bit), and multi-cycle stimuli. To overcome this challenge, the <u>Testcase Generator</u> (Fig. 3 (b)) adopts a program generation approach. As shown in the first stage of Fig. 3 (a), instead of attempting to directly emit long bit strings, the agent first reasons about the desired test scenario. It then executes a short Python script via the *Code Interpreter* to programmatically construct the required input sequences. This approach guarantees bit-accuracy, bypasses the LLM's fidelity limitations, and produces an Input Signal with functionally valid, coverage-driven test vectors.

**2** Testbench Generation and Functional Modeling. The FRM Generator (Fig. 3 (b)) takes the JSON Input Signal from step 1 and the RTL SPEC to construct a testbench.json artifact, pairing input vectors with cycle-aligned expected outputs.

To achieve this, the agent leverages LLM-based code generation (Sec. 2.2) to sample N Python-based FRMs acting as "golden" behavioral oracles. These scripts are executed by the *Code Interpreter* to compute N sets of expected outputs for the step  $\bigcirc$  testcases. This program-aided approach circumvents LLM limitations in direct arithmetic [8, 12] by applying precise, executable logic.

(Fig. 3 (b)) receives the *N* candidate artifacts from step 2 and drives a self-improvement loop (Fig. 3 (c)) combining majority voting with verification. First, the system selects the most consistent candidate via majority voting. The Judge then validates the selected outputs; if errors are detected, it performs targeted corrections by invoking the *Testbench Edit Tool*. As detailed in Tab. 1, this tool allows the agent to programmatically add, replace, or remove entries in testbench. json (e.g., rectifying a single failing vector). Upon validation or budget exhaustion, the final testbench. json is passed to the *Simulation Driver* to compile and orchestrate the Verilator simulation. This driver validates the DUT by comparing its actual execution results—driven by the stimuli from step 1 —against the expected reference outputs encapsulated in the testbench. json.

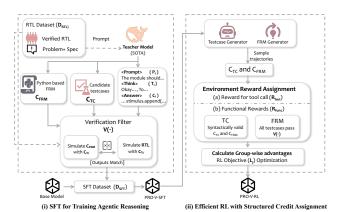

Figure 4: Overview of Agentic training framework.

# 3.2 Agentic training framework for RTL verification

While the agentic system detailed in Sec. 3.1 establishes a robust verification loop, its effectiveness is inherently constrained by the reliance on general-purpose LLMs. These models struggle with precise instruction following (e.g., tool arguments, role confusion), lack specialized RTL domain knowledge (e.g., bit-order conventions), and possess weak intrinsic logical and coding abilities for model generation and debugging. To evolve these generalists into domain experts, we propose a hybrid training methodology: (i) initiating with SFT on verified, expert-level trajectories synthesized from existing RTL datasets via a custom data construction pipeline, and (ii) implementing an efficient RL algorithm that leverages verification-specific structured rewards derived from programmatic tool feedback to optimize the end-to-end workflow.

(i) SFT for Agentic Reasoning. Existing public datasets for hardware design, such as those focused on Verilog generation [14, 40] (as illustrated in Sec. 2.1), primarily consist of verified (Problem, RTL) pairs, which we denote as  $\mathcal{D}_{RTL}$ . While suitable for simple generation tasks, these datasets lack the comprehensive reasoning traces and hardware verification references required to train our specific agentic workflow.

To construct our SFT dataset, we leverage these existing datasets as a foundation and establish a dedicated data construction pipeline to synthesize the verification specific expert-level reasoning trajectories and tool interactions. For each problem, we use its golden RTL design and prompt a SOTA 'teacher' model to generate trajectories for two agent roles: the <u>Testcase Generator</u> and the <u>FRM Generator</u>. The teacher model generates candidate testcases ( $C_{TC}$ ) and a corresponding Python-based FRM,  $C_{FRM}$ . A trace is only accepted after passing a strict <u>verification filter</u>,  $\mathcal{V}(\cdot)$ , which is defined as:

$$\mathcal{V}(C_{TC}, C_{FRM}, RTL)$$

$$\equiv [\operatorname{Sim}(RTL, C_{TC}) = \operatorname{Sim}(C_{FRM}, C_{TC})] \tag{1}$$

This filter ensures the agentic flow successfully generates a runnable test harness (composed of  $C_{TC}$  and  $C_{FRM}$ ) and that the golden RTL's simulation output precisely matches the FRM's output for all test-cases  $C_{TC}$ . This process validates the functional correctness of the generated  $C_{FRM}$ . We then collect these verified interactions to form our curated SFT dataset,  $\mathcal{D}_{SFT}$ . Each data point  $d \in \mathcal{D}_{SFT}$  is a

trajectory composed of components for each agent, structured as:  $(P_i, T_i, C_i)$ , where  $i \in \{\text{TC}, \text{FRM}\}$ . Here,  $P_i$  represents the prompt,  $T_i$  is the reasoning trace, and  $C_i$  is the generated code for agent i.

The SFT objective trains the model parameters  $\theta$  by minimizing the standard log-likelihood loss over all prompt-response pairs (x,y) derived from  $\mathcal{D}_{SFT}$  (e.g.,  $x=P_i,y=T_i\oplus C_i$ , where  $\oplus$  denotes concatenation):

$$\mathcal{L}_{SFT}(\theta) = -\sum_{(x,y)\in\mathcal{D}_{SFT}} \sum_{t=1}^{|y|} \log P_{\theta}(y_t|y_{< t}, x)$$

(2)

where  $y_t$  is the t-th token of the target response y.

(ii) Efficient RL with Structured Credit Assignment. While SFT provides the model with a foundational capability to mimic expert trajectories in  $\mathcal{D}_{SFT}$ , we introduce a subsequent reinforcement learning phase to enable our agents to generalize and discover policies that maximize verification success. We utilize Group Relative Policy Optimization (GRPO) [5, 27] to fine-tune the SFT model through direct interaction with the verification environment.

For a given task q, we sample G complete trajectories  $\{\tau_i\}_{i=1}^G$ . Each trajectory  $\tau_i$  is a composition of the sub-trajectories from its constituent agents:  $\tau_i = \tau_{i,\text{TC}} \oplus \tau_{i,\text{FRM}}$ , representing the full generation from the Testcase Generator and the FRM Generator.

To enable precise credit assignment, we define distinct rewards for each agent  $j \in \{\text{TC}, \text{FRM}\}$ . The reward for each agent's subtrajectory  $\tau_{i,j}$  is a composite signal:

$$R(\tau_{i,j}) = R_{func}^{j}(\tau_i) + w_{fmt}R_{fmt}^{j}(\tau_{i,j})$$

(3)

where  $\tau_i = \tau_{i,TC} \oplus \tau_{i,FRM}$  is the full trajectory,  $R^j_{fmt}(\tau_{i,j})$  is the agent-specific reward for generating syntactically correct tool calls, and  $w_{fmt}$  is a weighting hyperparameter. The functional rewards  $R^j_{func}$  are computed separately for each agent based on the full trajectory's outputs ( $C_{TC}$  and  $C_{FRM}$ ):

- TC Agent Functional Reward ( $R_{func}^{\rm TC}$ ): This is a binary reward for generating a *runnable harness*. It is 1 if  $C_{TC}$  and  $C_{FRM}$  are syntactically valid and can be successfully compiled and simulated together, and 0 otherwise.

- FRM Agent Functional Reward ( $R_{func}^{FRM}$ ): This is the primary verification success reward. It is 1 only if all test cases pass verification—that is, the strict filter  $\mathcal{V}(\cdot)$  (defined in Eq. (1)) evaluates to true. This reward is contingent on the harness being runnable (i.e.,  $R_{func}^{TC} = 1$ ).

For each agent  $j \in \{\text{TC}, \text{FRM}\}$ , let  $\{\tau_{i,j}\}_{i=1}^G$  be a minibatch of sub-trajectories and  $R(\tau_{i,j})$  the composite reward in Eq. (3). We normalize rewards *per agent*:

$$A_{i,j} = \frac{R(\tau_{i,j}) - \bar{R}_j}{\max(\operatorname{std}(\{R(\tau_{k,j})\}_{k=1}^G), \, \varepsilon)},\tag{4}$$

where  $\bar{R}_j$  and  $\mathrm{std}(\cdot)$  are the mean and standard deviation over agent j's batch, and  $\varepsilon > 0$  avoids division by zero.

The GRPO objective sums agent-wise clipped-ratio losses:

$$\mathcal{L}_{GRPO}(\theta) = \sum_{j \in \{TC, FRM\}} \mathcal{L}_{j}(\theta)$$

(5)

where

$$\mathcal{L}_{j}(\theta) = \mathbb{E}_{i,t \in \tau_{i,j}} \left[ \min \left( \rho_{i,t} A_{i,j}, \right) \right]$$

(6)

$$\operatorname{clip}(\rho_{i,t}, 1 - \lambda, 1 + \lambda) A_{i,j}$$

with per-token likelihood ratio  $\rho_{i,t} = \frac{\pi_{\theta}(a_{i,t}|s_{i,t})}{\pi_{\theta_{\text{old}}}(a_{i,t}|s_{i,t})}$  and clipping parameter  $\lambda > 0$ . This critic-free formulation yields stable updates aligned with the agent-specific rewards.

# 4 Experiments

# 4.1 Experimental Setup

Hardware. All training and evaluation are conducted on NVIDIA H100 GPUs in a single-node setup. Simulator. We use Verilator 5.042 (2025-11-02) [29] as the cycle-accurate simulator. Models. Our teacher model for SFT data generation is DEEPSEEK-V3.2 (Oct. 2025) [6], accessed via its official API. The base model is QWEN3-8B [25]. SFT Protocol. We train QWEN3-8B[24] using the AdamW optimizer (learning rate  $2 \times 10^{-5}$ ). We use a global batch size of 256, bfloat16 mixed precision, and gradient clipping at 1.0. RL (GRPO) Protocol. Key hyperparameters include: FRM sample number N = 5, learning rate  $1 \times 10^{-6}$ , clipping parameter  $\lambda = 0.2$ , group size G = 4, format reward weight  $w_{fmt} = 0.3$ , and  $\varepsilon = 1 \times 10^{-8}$ for advantage normalization. The maximum prompt and response lengths are both 4k tokens. During sampling for training rollouts, we use temperature 1.0 and top-p = 0.95; for evaluation, we use temperature 0.0. Benchmarks. We employ two primary benchmarks: VerilogEval-v2 [35] and RTLLM v2.0 [10]. To rigorously evaluate testbench robustness—a key metric for verification—we utilize DeepSeek-V3.2 to generate a set of 10 RTL mutants per problem for both datasets. The mutants are essential for assessing a testbench's ability to detect faults, moving beyond simple compilation. Metrics. Following the methodology of CorrectBench [23], we adopt its three-level protocol on VerilogEval-v2 to assess distinct aspects of testbench quality: EVALO (Viability): Assesses fundamental syntactical and simulation viability. It reports the fraction of TBs that successfully compile and execute without simulation runtime errors. This serves as a baseline check for structural correctness. EVAL1 (Functional Correctness): Assesses the primary correctness of the *generated* testbench. It reports the fraction of TBs that successfully compile and pass simulation when run against the golden RTL code in the benchmarks. This metric validates the TB's ability to correctly "pass" a known-good design. EVAL2-80/90/100 (Robustness & Fault Detection): Quantifies the testbench's fault-detection capability using the generated RTL mutants. This metric reports the fraction of problems where the generated TB's verdict (pass/fail) matches the reference TB's verdict on at least 80%, 90%, and 100% of the mutants, respectively. This metric, therefore, evaluates the testbench's critical ability to identify faulty RTL implementations.

# 4.2 Key Results

Tab. 2 shows that PRO-V-R1 with PRO-V system consistently matches or exceeds much larger proprietary models on end-to-end testbench quality. On VerilogEval-v2, PRO-V-R1-8B attains 57.7% on Eval1 and 34.0% on Eval2-100, outperforming GPT-40 and all existing open models, and approaching the best results of multi-hundredbillion-parameter systems such as DeepSeek-R1 and Claude. More importantly, our method maintains relatively strong robustness: the gap between Eval1 and Eval2 metrics is significantly smaller than for most baselines, especially on RTLLM v2.0, where GPT-40 and other foundations degrade sharply from high Eval1 to very low Eval2 scores, indicating that they often emit short, low-diversity stimuli that can validate the golden RTL but rarely expose mutants. In contrast, the PRO-V agents learn to construct richer Python testbenches that both compile reliably (high Eval0) and exercise corner cases (higher Eval2-80/90/100), while domain-specific baselines such as RTLCoder and CodeV either underperform on Eval1 or collapse on Eval2, reflecting insufficient fault coverage. A remaining limitation is that on the hardest VerilogEval-v2 robustness setting (Eval2-100), very large proprietary models still retain a small advantage, suggesting headroom for further scaling of training data and RL optimization, but PRO-V-R1 already narrows the verification gap with a compact, fully open 8B model.

# 4.3 Ablation Study

We conduct an ablation study to dissect the contribution of each component in our framework, which is presented in Tab. 3.

We first establish baselines. A vanilla Qwen3-8B model almost completely fails on VerilogEval-v2. We then evaluate CorrectBench [23],

Table 2: Overall results on VerilogEval-v2 and RTLLM v2.0.

| Category               | Model                        | Open<br>Source | VerilogEval-v2 |       |          |          | RTLLM v2.0 |       |       |                   |          |           |

|------------------------|------------------------------|----------------|----------------|-------|----------|----------|------------|-------|-------|-------------------|----------|-----------|

| category               |                              |                | Eval0          | Eval1 | Eval2-80 | Eval2-90 | Eval2-100  | Eval0 | Eval1 | Eval2-80          | Eval2-90 | Eval2-100 |

| Foundation models      | GPT-40                       | ×              | 90.4           | 43.0  | 39.7     | 36.5     | 27.6       | 90.0  | 42.0  | 18.0              | 14.0     | 6.0       |

|                        | DeepSeek-R1-671B*            | ✓              | 87.2           | 51.9  | 44.9     | 40.4     | 35.9       | 72.0  | 28.0  | 16.0              | 10.0     | 6.0       |

|                        | claude-sonnet-4-20250514     | ×              | 94.9           | 45.5  | 41.7     | 39.7     | 35.9       | 88.0  | 30.0  | $\overline{10.0}$ | 4.0      | 2.0       |

|                        | DeepSeek-R1-Distill-Qwen-7B* | ✓              | 0.0            | 0.0   | 0.0      | 0.0      | 0.0        | 0.0   | 0.0   | 0.0               | 0.0      | 0.0       |

|                        | Qwen3-8B                     | ✓              | 0.6            | 0.6   | 0.6      | 0.6      | 0.0        | 0.0   | 0.0   | 0.0               | 0.0      | 0.0       |

|                        | Qwen2.5-Coder-7B-Instruct    | ✓              | 70.5           | 14.1  | 10.3     | 9.6      | 7.7        | 58.0  | 8.0   | 0.0               | 0.0      | 0.0       |

|                        | Qwen2.5-Coder-32B-Instruct   | ✓              | 72.4           | 25.6  | 22.4     | 19.9     | 18.0       | 66.0  | 8.0   | 4.0               | 2.0      | 2.0       |

| Domain specific models | RTLCoder-Deepseek-v1.1       | <b>√</b>       | 75.0           | 19.2  | 12.8     | 10.9     | 8.3        | 70.0  | 6.0   | 0.0               | 0.0      | 0.0       |

|                        | CodeV-R1-RL-Qwen-7B          | ✓              | 81.4           | 19.9  | 15.4     | 11.5     | 10.3       | 84.0  | 4.0   | 2.0               | 2.0      | 2.0       |

|                        | CodeV-DS-6.7B                | ✓              | 37.2           | 13.5  | 6.4      | 3.2      | 2.6        | 64.0  | 20.0  | 4.0               | 0.0      | 0.0       |

| Ours                   | PRO-V-DS-8B w/ PRO-V sys     | <b>√</b>       | 93.6           | 50.6  | 35.9     | 34.0     | 27.6       | 78.0  | 26.0  | 16.0              | 12.0     | 4.0       |

|                        | PRO-V-R1-8B w/ PRO-V sys     | ✓              | 94.8           | 57.7  | 44.2     | 37.8     | 34.0       | 78.0  | 28.0  | 18.0              | 14.0     | 6.0       |

**Bold** numbers indicate the best result in each column, and <u>underlined</u> numbers indicate the second-best. Rows not annotated with "w/ PRO-V sys" report vanilla-model performance. "PRO-V-DS-8B" denotes the SFT-only stage, while "PRO-V-R1-8B" denotes the subsequent RL-tuned model.

Table 3: Ablation Study of the PRO-V Framework on VerilogEval-v2. We progressively add our agentflow (PRO-V Flow), (SFT), and RL to the base model.

|                                    | VerilogEval-v2 |       |          |      |      |  |  |

|------------------------------------|----------------|-------|----------|------|------|--|--|

| Model / Method                     | Eval0          | Eval1 | Eval2-80 | -90  | -100 |  |  |

| Qwen3-8B                           | 0.6            | 0.6   | 0.6      | 0.6  | 0.0  |  |  |

| Qwen3-8B w/ Correct-<br>Bench [23] | 47.4           | 25.6  | 23.7     | 23.1 | 21.8 |  |  |

| Qwen3-8B w/ PRO-V<br>sys           | 64.7           | 39.1  | 35.9     | 32.1 | 28.2 |  |  |

| PRO-V-DS-8B w/ PRO-V<br>sys        | 93.6           | 50.6  | 35.9     | 34.0 | 27.6 |  |  |

| PRO-V-R1-8B w/ PRO-<br>V sys       | 94.9           | 57.7  | 44.2     | 37.8 | 34.0 |  |  |

the SOTA agentic system, which improves the scores (Eval1: 25.6, Eval2-100: 21.8). However, its performance is constrained by its design. CorrectBench employs a complex hybrid generation strategy where the agent must produce multiple languages (e.g., HDL, Python). This multi-language requirement increases the cognitive load on the LLM, often leading to hallucinations and semantic errors.

In contrast, using the same base LLM within our PRO-V sys already yields superior gains (Eval1: 39.1, Eval2-100: 28.2). This superior baseline performance is attributed to our design, which leverages a "program-tool-enhanced-reasoning" approach. The agent's task is simplified to only generating Python code, which then use tool interaction. This single-language focus significantly reduces hallucinations and improves reliability. Moreover, adding post-training on top of the sys (PRO-V-R1) dramatically improves the test harness correctness, boosting Eval0 from 64.7 to 94.9 and Eval1 to 57.7, reaching 44.2/37.8/34.0 on Eval2-80/90/100, respectively.

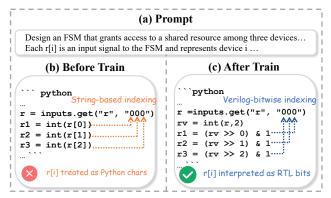

Case Study: Impact of Post-Training. Fig. 5 presents a compelling case study on the impact of our post-training process on semantic reasoning. Given a prompt to design an FSM with a multibit input vector  $\mathbf{r}$  (a), the base LLM (b) misinterprets the vector as a Python string. This fundamental misunderstanding leads it to generate incorrect, string-based indexing (e.g., int( $\mathbf{r}[0]$ )) to access what it believes are characters. In contrast, our post-trained model (c) correctly grasps the hardware context and Verilog semantics, identifying  $\mathbf{r}$  as an RTL bit vector and generating the proper Verilog-compliant bitwise operations to access individual bits. This demonstrates that our post-training successfully imbues the model with high-quality reasoning for RTL verification.

Efficiency Analysis. Our framework is also highly efficient. As analyzed in Fig. 6, the SOTA agent system, CorrectBench (using Qwen3-8B), has a mean latency of 805.4 s per task. In stark contrast, our method completes verification with a mean latency of only 91.2 s and a median of 48.3 s, realizing an 8.8× speedup in mean latency. This efficiency gain stems from two key factors. First, our training method ensures the model maintains high-quality reasoning traces, which greatly reduces reasoning time. Second, we avoid the primary bottleneck found in CorrectBench—its computationally expensive self-check mechanism, which requires the LLM to generate 20 different RTL implementations simply to verify its

Figure 5: Post-training case study (task 2013\_q2afsm). (a) Input prompt. (b) Base LLM fails by treating input as a Python string. (c) Our model correctly generates Verilog bitwise operations.

Figure 6: Latency distribution comparison between PRO-V-R1 and the CorrectBench (Qwen3-8B) baseline.

own output. Our method replaces this by generating N=5 Python programs in parallel per iteration and typically succeeding within 1-2 self-consistency iterations (max 3), reducing the required LLM inference steps and overall latency.

#### 5 Conclusion

In this paper, we present PRO-V-R1, the first trainable open-source agentic verification framework that couples LLMs with program-in-the-loop tools for automated RTL testbench generation. Centered on the PRO-V system, PRO-V-R1 reduces verification to Python-only functional reference modeling, mitigating semantic mismatches between Verilog and Python. Integrated with SFT on simulation-validated multi-agent trajectories and GRPO-based RL with verification-structured rewards, our 8B PRO-V-R1 model achieves 57.7% functional correctness (Eval1) and 34.0% full-mutant robustness (Eval2-100) on VerilogEval-v2, surpassing GPT-40 (43.0% / 27.6%) and the SOTA agentic baseline CorrectBench (25.6% / 21.8%), while delivering a 8.8× speed up (91s vs. 805s per task). PRO-V-R1 thus represents a concrete step toward practical, reproducible, and efficient LLM-based RTL verification, offering a robust blueprint for future domain-specialized verification agents.

### References

- Janick Bergeron. 2003. Writing Testbenches: Functional Verification of HDL Models. Kluwer Academic Publishers, New York, NY. doi:10.1007/978-1-4615-0302-6

- [2] Andres M. Bran, Sam Cox, Oliver Schilter, Carlo Baldassari, Andrew D. White, and Philippe Schwaller. 2023. ChemCrow: Augmenting Large-Language Models

- with Chemistry Tools. arXiv preprint arXiv:2304.05376 (2023). https://arxiv.org/abs/2304.05376

- [3] Mark Chen, Jerry Tworek, et al. 2021. Evaluating Large Language Models Trained on Code. arXiv preprint arXiv:2107.03374 (2021). https://arxiv.org/abs/2107.03374

- [4] Wenhu Chen, Xueguang Ma, Xinyi Wang, and William W. Cohen. 2022. Program of Thoughts Prompting: Disentangling Computation from Reasoning for Numerical Reasoning Tasks. arXiv preprint arXiv:2211.12588 (2022). https://arxiv.org/abs/2211.12588

- [5] DeepSeek-AI. 2025. DeepSeek-R1: Incentivizing Reasoning Capability in LLMs via Pure Reinforcement Learning. arXiv preprint arXiv:2501.12948 (2025). https://arxiv.org/abs/2501.12948

- [6] DeepSeek AI. 2025. DeepSeek-V3.2-Exp Model. https://huggingface.co/deepseek-ai/DeepSeek-V3.2-Exp. Technical report available at https://github.com/deepseek-ai/DeepSeek-V3.2-Exp/blob/main/DeepSeek\_V3\_2.pdf.

- [7] Luyu Gao, Aman Madaan, Shuyan Zhou, et al. 2022. PAL: Program-Aided Language Models. In NeurIPS. https://arxiv.org/abs/2211.10435

- [8] Luyu Gao, Andy Zou, Xueliang Chen, and et al. 2023. PAL: Program-Aided Language Models. In Proceedings of ICML. https://arxiv.org/abs/2211.10435

- [9] Hongliang He, Wenlin Yao, Kaixin Ma, Wenhao Yu, Yong Dai, Hongming Zhang, Zhenzhong Lan, and Dong Yu. 2024. WebVoyager: Building an End-to-End Web Agent with Large Multimodal Models. In Proceedings of the 62nd Annual Meeting of the Association for Computational Linguistics (Volume 1: Long Papers). Association for Computational Linguistics, 5777–5794.

- [10] HKUST RTLLM Team. 2024. RTLLM: RTL Generation with Large Language Models (Benchmark Repository). https://github.com/hkust-zhiyao/RTLLM.

- [11] Charalambos Ioannides and Kerstin I Eder. 2012. Coverage-directed test generation automated by machine learning—a review. ACM Transactions on Design Automation of Electronic Systems (TODAES) 17, 1 (2012), 1–21.

- [12] Qi Li, Kun Liu, Junjie Wang, and et al. 2024. GSM-PLUS: A Comprehensive Benchmark for Evaluating Mathematical Reasoning Robustness of LLMs. In Proceedings of ACL. https://aclanthology.org/2024.acl-long.163.pdf

- [13] Zhuofeng Li, Haoxiang Zhang, Seungju Han, Sheng Liu, Jianwen Xie, Yu Zhang, Yejin Choi, James Zou, and Pan Lu. 2025. In-the-Flow Agentic System Optimization for Effective Planning and Tool Use. arXiv preprint arXiv:2510.05592 (2025).

- [14] Meng Liu, Wenji Fang, Yao Lu, Qijun Zhang, Hongce Zhang, and Zhiyao Xie. 2025. CraftRTL: High-quality Synthetic Data Generation for Verilog Code Models with Correct-by-Construction Non-Textual Representations and Targeted Code Repair. In *International Conference on Learning Representations (ICLR)*. https://proceedings.iclr.cc/paper\_files/paper/2025/file/e112a4671e8779aa9f640a0e3f81bd26-Paper-Conference.pdf

- [15] Mingjie Liu, Nathaniel Pinckney, Brucek Khailany, and Haoxing Ren. 2023. Verilogeval: Evaluating large language models for verilog code generation. In 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD). IEEE, 1–8.

- [16] Zirui Liu, Yubo Fang, Qijun Liu, Zhiyao Xie, Srivatsa Rangachar, Jiacheng Yang, Binyu Yang, Peiyu Wang, Yixiao Zhang, Naman Gupta, Yanzhi Wang, and Haoxing Ren. 2023. RTLCoder: Fully Open-Source and Efficient LLM-Assisted RTL Code Generation Technique. arXiv:2312.08617 [cs.CL]

- [17] Chenhao Lu, Nestor Shinn, David Ha, and Jeff Clune. 2024. The AI Scientist: Towards Fully Automated Open-Ended Scientific Discovery. arXiv preprint arXiv:2408.06292 (2024). https://arxiv.org/abs/2408.06292

- [18] Yujun Lu, Jialu Kandt, Ya-Lin Chang, and et al. 2023. AdaPT: A General Adaptive Planning and Tool-use Framework for Language Agents. In Advances in Neural Information Processing Systems (NeurIPS).

- [19] Grégoire Mialon, Roberto Dessì, Eleonora Lome, and et al. 2023. Augmented Language Models: a Survey. In Transactions of the Association for Computational Linguistics.

- [20] Shishir G Patil, Tianjun Geng, Xuechen Liu, and Peng E. 2023. Gorilla: Large Language Model Connected with Massive APIs. In Advances in Neural Information Processing Systems (NeurIPS).

- [21] Yujia Qin, Shihao Cai, Yifan Kou, Yixin Chen, Zongqian Zhang, Cheng Li, Qingda Yang, Michihiro Yasunaga, Hong Yang, Yushi Zhao, et al. 2024. ToolLLM: Facilitating Large Language Models to Master 16000+ Real-world APIs. In The Twelfth International Conference on Learning Representations (ICLR).

- [22] Ruidi Qiu, Grace Li Zhang, Rolf Drechsler, Ulf Schlichtmann, and Bing Li. 2024. Autobench: Automatic testbench generation and evaluation using llms for hdl design. In Proceedings of the 2024 ACM/IEEE International Symposium on Machine Learning for CAD. 1–10.

- [23] Ruidi Qiu, Grace Li Zhang, Rolf Drechsler, Ulf Schlichtmann, and Bing Li. 2024. Correctbench: Automatic testbench generation with functional self-correction using llms for hdl design. arXiv preprint arXiv:2411.08510 (2024).

- [24] Qwen Team. 2025. Qwen3: A Family of Strong, Open Foundation and Instruction Models. https://huggingface.co/Qwen/Qwen3-8B-Base.

- [25] Qwen Team, Alibaba Cloud. 2025. Qwen3 Large Language Model Series. https://github.com/QwenLM/Qwen3. Model card for 8B variant available at https://huggingface.co/Qwen/Qwen3-8B.

- [26] Timo Schick, Jane Dwivedi-Yu, Nathan Scales, Roberta Raileanu, et al. 2023. Toolformer: Language Models Can Teach Themselves to Use Tools. In *NeurIPS*. https://arxiv.org/abs/2302.04761

- [27] Zihan Shao, Yongchao Chen, et al. 2024. DeepSeekMath: Pushing the Limits of Mathematical Reasoning in Open Language Models. arXiv preprint arXiv:2402.03300 (2024). https://arxiv.org/abs/2402.03300

- [28] Dong-Hyun Shin, Min-Soo Wie, Young-Min Kim, and Yong-Hee Lee. 2020. Efficient bug detection in functional verification using multi-armed bandits. In 2020 20th International Conference on Control, Automation and Systems (ICCAS). IEEE, 671–675

- [29] Wilson Snyder et al. 2025. Verilator: The Open-Source Verilog Simulator. https://verilator.org. Version 5.042 (2025-11-02).

- [30] Yan Tan, Xiangchen Meng, Zijun Jiang, and Yangdi Lyu. 2025. AutoVeriFix: Automatically Correcting Errors and Enhancing Functional Correctness in LLM-Generated Verilog Code. arXiv preprint arXiv:2509.08416 (2025).

- [31] Shailja Thakur, Baleegh Ahmad, Hammond Pearce, Benjamin Tan, Brendan Dolan-Gavitt, Ramesh Karri, and Siddharth Garg. 2024. VeriGen: A Large Language Model for Verilog Code Generation. ACM Transactions on Design Automation of Electronic Systems 29, 5, Article 93 (2024).

- [32] Ning Xu et al. 2025. A Linguistic and Math Expert's Struggle with Simple Word-Based Counting. In *Proceedings of NAACL*. https://aclanthology.org/2025.naacl-long.172.pdf

- [33] Gilad Yehudai et al. 2024. StringLLM: Understanding the String Processing Capability of Large Language Models. arXiv preprint arXiv:2410.01208 (2024). https://arxiv.org/abs/2410.01208

- [34] Haoxiang Yuan, Nathaniel Pinckney, et al. 2025. Revisiting VerilogEval: A Year of Improvements in Large Language Models for Verilog. arXiv preprint arXiv:2408.11053 (2025). https://arxiv.org/abs/2408.11053

- [35] Haoxiang Yuan, Nathaniel Pinckney, et al. 2025. Revisiting VerilogEval: A Year of Improvements in Large Language Models for Verilog (HTML version). https://arxiv.org/html/2408.11053v2.

- [36] Zinuo Zeng, Linyi Wang, Jiateng Wang, and et al. 2024. Agentic SLMs: A Survey and Framework on Small Language Models as Agents. arXiv preprint arXiv:2406.01429 (2024).

- [37] Yang Zhao, Di Huang, Chongxiao Li, Pengwei Jin, Ziyuan Nan, Tianyun Ma, Lei Qi, Yansong Pan, Zhenxing Zhang, Rui Zhang, et al. 2024. Codev: Empowering LLMs for verilog generation through multi-level summarization. arXiv preprint arXiv:2407.10424 (2024).

- [38] Shuyan Zhou, Frank F. Xu, Hao Zhu, et al. 2023. WebArena: A Realistic Web Environment for Building Autonomous Agents. arXiv preprint arXiv:2307.13854 (2023). https://arxiv.org/abs/2307.13854

- [39] Yaoyu Zhu et al. 2025. CodeV-R1: Reasoning-Enhanced Verilog Generation. arXiv preprint arXiv:2505.24183 (2025).

- [40] Yaoyu Zhu, Di Huang, Hanqi Lyu, Xiaoyun Zhang, Chongxiao Li, Wenxuan Shi, Yutong Wu, Jianan Mu, Jinghua Wang, Yang Zhao, Pengwei Jin, Shuyao Cheng, Shengwen Liang, Xishan Zhang, and Rui Zhang. 2025. QiMeng-CodeV-R1: Reasoning-Enhanced Verilog Generation. arXiv:2505.24183 [cs.LG]

- [41] Yaoyu Zhu, Di Huang, Hanqi Lyu, Xiaoyun Zhang, Chongxiao Li, Wenxuan Shi, Yutong Wu, Jianan Mu, Jinghua Wang, Yang Zhao, Pengwei Jin, Shuyao Cheng, Shengwen Liang, Xishan Zhang, Rui Zhang, Zidong Du, Qi Guo, Xing Hu, and Yunji Chen. 2025. CodeV-R1: Reasoning-Enhanced Verilog Generation. arXiv preprint arXiv:2505.24183 (2025). https://arxiv.org/abs/2505.24183