# FLASHFORMER: WHOLE-MODEL KERNELS FOR EFFICIENT LOW-BATCH INFERENCE

Aniruddha Nrusimha  $^1$  William Brandon  $^1$  Mayank Mishra  $^2$  Yikang Shen  $^2$  Rameswar Panda  $^2$  Jonathan Ragan-Kelley  $^1$  Yoon Kim  $^1$

#### **ABSTRACT**

The size and compute characteristics of modern large language models have led to an increased interest in developing specialized kernels tailored for particular training and inference workloads. Existing kernels primarily optimize for compute utilization, targeting the large-batch training and inference settings. However, low-batch inference, where memory bandwidth and kernel launch overheads are significant factors, remains important for many applications of interest such as in edge deployment and latency-sensitive applications. This paper describes FLASHFORMER, which fuses the entire transformer forward pass into a single kernel for accelerating low-batch inference of large language models. Across various model sizes and quantizations settings, FLASHFORMER achieves nontrivial speedups compared to existing inference kernels.

# 1 Introduction

As the utility and popularity of deep learning models has steadily increased, there has been an increasing interest in low-level *kernel design*, i.e., developing specialized programs tailored to optimize particular workloads on the target hardware. This has been particularly true for large language models (LLMs) based on the transformer architecture, due to a dramatic increase in task performance across domains for these models obtained from *model scaling* (i.e., increasing parameter counts and computational costs per forward pass) and *inference scaling* (i.e., generating more tokens in parallel or serially).

While most accelerator vendors develop high performance kernels for common linear algebra routines such as matrix multiplications, these general-purpose kernels are often not sufficient for LLM inference. Consequently, there has been much recent work on kernels that accelerate the inference of transformer-based LLMs, such as FLASHDECODING (Dao et al., 2023) and PAGEDATTENTION (Kwon et al., 2023). These kernels achieve efficiency gains by optimizing parts of operations common to the transformer inference pipeline. For example, FLASHDECODING modifies the work partitioning in FLASHATTENTION (Dao et al., 2022; Dao, 2024) for better parallelization during transformer decoding, while PAGEDATTENTION saves GPU memory by organizing the KV cache, thus allowing larger batch sizes.

Preprint.

Most existing kernels are optimized to maximize throughput for large matrix-matrix multiplications (matmuls). The key to doing so on modern accelerators is to maximize the utilization of special matrix-multiply units (MMU)—called Tensor Cores on NVIDIA hardware and MXUs on TPUs—which provide most of the computational performance of the chip. In either large-batch inference or training, this design choice optimizes the primary bottleneck of these kernels, i.e., the computational cost of matmuls with high arithmetic intensity (computation per element of data movement).

However, many use cases operate under different constraints. For example, low-batch inference is primarily bottlenecked by the memory bandwidth costs of parameter and KV-cache movement; depending on the size of the model, kernel launch overheads that arise from launching multiple separate kernels for each transformer layer can also be a bottleneck. Low-batch inference workloads arise in many real-world applications, such as edge deployment, latency-sensitive applications, and more recently, inference-time scaling via longer rollouts. Moreover, low-batch inference does not obtain significant benefits from using MMUs on the hardware since the problem sizes are not bottlenecked by compute.

Writing fast kernels for these workloads requires further innovation along two common directions in kernel development research: 1) Increased operator fusion, or packing an increasing number of instructions and operations into a single kernel and 2) Increased specialization, or generating kernels that more closely optimized for the particular problem. This paper describes a strategy for writing a highly optimized inference kernel that runs the entire forward pass of a transformer-based LLM in a single kernel, and is spe-

<sup>&</sup>lt;sup>1</sup>Massachusetts Institute of Technology, Cambridge, MA, USA <sup>2</sup>MIT-IBM Watson AI Lab, Cambridge, MA, USA. Correspondence to: Aniruddha Nrusimha <anin@mit.edu>.

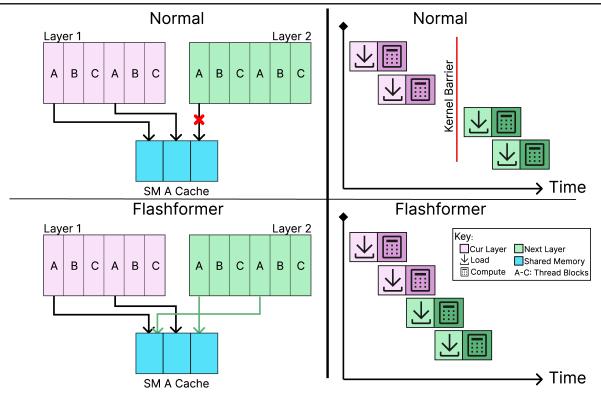

**Figure 1:** Depiction of the key benefit of FLASHFORMER. The top half depicts normal transformer execution with multiple kernels. After all chunks of Layer 1 have been loaded into the SM cache, we cannot start loading Layer 2 (top left). This, coupled with kernel overhead, leads to a break in memory loads and computation (top right). With FLASHFORMER, we fuse kernels to enable overlapping across prior kernel barriers (bottom left). This leads to more efficient overlapping and faster runtime (bottom right).

cialized for a particular model configuration (such as the number of attention heads, embedding dimension, etc) and the target hardware architecture. We use meta-programming, a shared pipelined buffer, and fast synchronization mechanisms to create a fully fused and specialized kernel. The resulting kernel, which we call FLASHFORMER, exploits increased overlapping of memory movement and the single fused kernel amortizes the launch overhead for the kernel over the entire forward pass. We apply this kernel to accelerate low-batch inference of Llama models (Grattafiori et al., 2024), and find that it offers consistent speedups over existing decoding kernels.

#### 2 BACKGROUND

# 2.1 Transformer Architecture

We target the Llama (Grattafiori et al., 2024) family of transformer architectures, which make use of the pre-RMSNorm (Jiang et al., 2023), Grouped Query Attention (Ainslie et al., 2023), RoPE (Su et al., 2021), and SwiGLU FFN layers (Shazeer, 2020). Each layer of a transformer model consists of six matrix operations, commonly grouped into five sublayers. Each sublayer has one matrix operation, except for the "core attention" layer, 1 which has two. The matrix

operations per layer with their respective input and output activations are listed in Table 1. These components are common to many other recent families of LLMs.

During autoregressive token-by-token generation, each matrix operation takes as input a large matrix stored in global memory as well as an activation computed by a previous operation.

Transformer LLMs are parameterized by the number of layers, model dimension, FFN dimension, head dimension, and the number of attention and key-value heads. The models we generate kernels for are shown in Table 2.

# 2.2 GPU Programming and Architecture

GPU programming optimizes over three interleaved hierarchies: the program hierarchy, the hardware hierarchy, and the memory hierarchy. The program hierarchy structures computations into kernels, thread blocks, warps, and threads to effectively expose parallelism.<sup>2</sup> The hardware hierarchy maps thread blocks onto streaming multiprocessors (SMs) which is sub-divided into multiple warp schedulers responsible for running a warp which is a collection of 32 threads executing the same instruction. Individual threads are re-

<sup>&</sup>lt;sup>1</sup>Since "attention layer" could be ambiguous, we use "core attention" to refer to the operation  $\operatorname{softmax}(\alpha \boldsymbol{Q} \boldsymbol{K}^{\top}) \boldsymbol{V}$ .

<sup>&</sup>lt;sup>2</sup>We use the NVIDIA GPU hardware terminology throughout this work; other architectures use different terms for similar hardware components.

| Matrix Operation                            | Matrix Load           | Input                                              | Output                                              |

|---------------------------------------------|-----------------------|----------------------------------------------------|-----------------------------------------------------|

| QKV Projection                              | $W_{QKV}$             | $RMSNorm(\boldsymbol{x})$                          | $oldsymbol{Q}[i], oldsymbol{K}[i], oldsymbol{V}[i]$ |

| $oldsymbol{Q} oldsymbol{K}^	op$ computation | $oldsymbol{K}[:i]$    | $oldsymbol{Q}[i]$                                  | $oldsymbol{S}[i]$                                   |

| $oldsymbol{PV}$ computation                 | $oldsymbol{V}[:i]$    | $\operatorname{softmax}(\alpha \boldsymbol{S}[i])$ | 0                                                   |

| <b>Attention Output Projection</b>          | $W_{a_{out}}$         | $vector(\boldsymbol{O})$                           | $oldsymbol{a}_{out}$                                |

| GLU In/Gate Projection                      | $oldsymbol{W}_{FFN1}$ | $RMSNorm(oldsymbol{x} + oldsymbol{a}_{out})$       | $oldsymbol{g}_{inter}$                              |

| GLU Output Projection                       | $oldsymbol{W}_{FFN2}$ | $\mathrm{SwiGLU}(oldsymbol{g}_{inter})$            | $oldsymbol{g}_{out}$                                |

**Table 1:** Transformer matrix operations for decoding for Llama 3.1. Here i is the current sequence position, and x is the residual stream.  $W_{QKV}$ ,  $W_{a_{out}}W_{FFN1}$  and  $W_{FFN2}$  represent corresponding parameter matrices, and Q, K and V represent the query, key, and value matrices respectively. S represents the attention logits, P the attention weights, and  $a_{out}$  the output of attention.  $g_{inter}$  and  $g_{out}$  represent the output of the GLU input/gate projection and the final GLU output of the GLU layer respectively.

| Model         | Layers | $d_{model}$ | $d_{inter}$ | $d_{head}$ | $n_{q\_heads}$ | $n_{kv\_heads}$ |

|---------------|--------|-------------|-------------|------------|----------------|-----------------|

| Llama 3.1 8B  | 32     | 4096        | 14336       | 128        | 32             | 8               |

| Llama 3.1 70B | 80     | 8192        | 28672       | 128        | 64             | 8               |

Table 2: Configuration of Llama 3.1 8B and 70B, for which we develop FLASHFORMER kernel.

sponsible for the core computations. Finally, the memory hierarchy manages the placement of data in registers, shared memory, and global memory to minimize latency and maximize throughput. Table 3 provides an overview of the three hierarchies.

At each level except the thread level, it is possible for multiple elements of the program hierarchy to exist on the same hardware if they satisfy certain hardware and memory constraints. In particular, multiple warps can exist on one warp scheduler provided there is enough space in registers, and-multiple thread blocks can co-locate on an SM if there is enough shared memory and register space.

# 2.3 Decoding Workload and GPU Overlapping

The general strategy for overlapping in most GPU work-loads is to partition the workload at each program level such that the corresponding hardware level is oversubscribed, i.e., the hardware has more work that it can execute. This oversubscription allows tasks to overlap: when one task is stalled awaiting resources—such as data loading from global to shared memory—other tasks continue executing arithmetic computations. Similarly, when one warp is waiting on a shared memory load, another warp can issue its computational instructions.

However, this strategy does not work well for inherently sequential workloads such as the sequential computations of transformer layers. Each matrix operation in Table 1 depends on the completion of the operations before it, and each transformer layer depends on the the completion of the previous transformer layer. As a result, in normal execution there is no opportunity for overlapping between different kernels, as shown in Section 1. Furthermore, inference kernel launch overheads can cause a nontrivial slowdown for fast decoding kernels, as noted by Spector et al. (2023).

# 2.4 Operator Fusion

One solution to the problem of overlapping is *kernel fusion*, which involves taking two or more kernels and combining them into a single kernel. Existing kernel fusions can be divided into two types. The first type fuses a single (or multiple) pointwise operations (such as an activation function) into a matrix operation. These pointwise operations are directly applied to either the input of the matrix or its output or both. These types of fusions are now commonly automated through tools such as XLA (Sabne, 2020) or PyTorch Compile (Ansel et al., 2024).

The second type involves restructuring multiple operations to remove the need for global synchronization and reduce redundant data movement between multiple matrix operations. A notable recent example of this is the FLASHATTENTION series of kernels (Dao et al., 2022; Dao, 2024; Shah et al., 2024b), which fuses the  $\boldsymbol{Q}\boldsymbol{K}^T$  computation, softmax calculation, and  $\boldsymbol{P}\boldsymbol{V}$  computation into one kernel, reducing the memory movement from HBM to SRAM and significantly increasing arithmetic intensity over an unfused kernel.

# 3 PRELIMINARY STUDY WITH DEEP LINEAR NETWORKS

We motivate the development of whole-model kernels for transformer inference by demonstrating the latency benefits in the case of *deep linear networks*. Insofar as deep linear networks make use of simpler primitives (i.e., just a stack of linear layers), speedups would be difficult to realize; thus, any speedups observed in this setting would provide promising motivation for fusing the entire transformer forward pass. We measure the latency reduction from eliminating kernel overheads at a variety of widths and depths, and ablate the latency reduction from overlapping

| <b>Program Level</b> | Hardware Level | Count   | Memory Pool  | Capacity             |

|----------------------|----------------|---------|--------------|----------------------|

| Kernel               | GPU            | 1       | Global (HBM) | 80 GB                |

| Threadblock          | SM             | 132     | Shared       | 228KB/SM             |

| Warp                 | Warp Scheduler | 4/SM    | -            | -                    |

| Thread               | Cuda Core      | 32/Warp | Registers    | 256KB/SM, 1KB/thread |

**Table 3:** The hierarchies of the GPU and and capacities on an H100 GPU. SM stands for Streaming Multiprocessor. Note that multiple thread blocks can coexist on an SM, and multiple warps on a warp scheduler.

| Dim | Layers | Baseline | Fused | + Overlap |

|-----|--------|----------|-------|-----------|

|     | 1      | 0.013    | 0.013 | 0.012     |

| 2K  | 4      | 0.050    | 0.029 | 0.027     |

|     | 32     | 0.403    | 0.169 | 0.154     |

|     | 1      | 0.021    | 0.021 | 0.021     |

| 4K  | 4      | 0.084    | 0.060 | 0.060     |

|     | 32     | 0.675    | 0.423 | 0.423     |

|     | 1      | 0.062    | 0.062 | 0.062     |

| 8K  | 4      | 0.250    | 0.221 | 0.218     |

|     | 32     | 1.998    | 1.543 | 1.513     |

**Table 4:** Latencies of stacked linear layers, measured in ms. Baseline refers to stacking separate kernel launches, Fused combines the forward pass into a single kernel. + Overlap is same as fused but makes use of cross layer overlapping of memory movement.

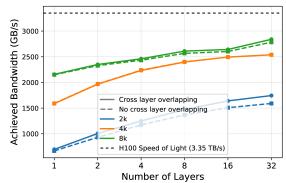

memory movement across layers. We measure both the execution time and achieved memory bandwidth; since our workloads are memory-bound, higher memory bandwidth indicates better hardware utilization.

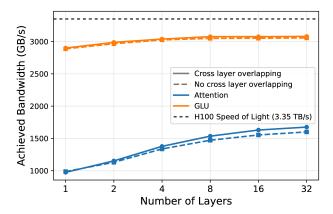

Kernel fusion across layers. We first study fusing the linear layers into a single kernel thus eliminating kernel overheads. We use a cooperative square linear kernel with a dynamic number of layers with a batch-one input (i.e., a vector). As a cooperative kernel, only one thread block runs per SM. Each thread block works on a predetermined portion of the workload, and performs a global sync in between layers. For different problem sizes (model dimension / number of layers), we perform autotuning across the number of consumer warps, number of pipeline stages, and size of each stage of the memory pipeline. The latency is shown in Table 4, and the memory bandwidth is shown in Figure 2. We find that kernel fusion across layers improves realized memory bandwidth. This effect is larger for smaller layers and diminishes as the number of fused layers increases.

**Memory overlapping.** A benefit of working with a single kernel is that we can initiate memory movement for future layers before the computation for current layers finishes. The additional benefits of memory overlapping are shown in Table 4, representing an additional few percentage points of latency improvement over the fused kernel.

These promising initial results motivate the development of whole-model kernels for transformer inference.

Figure 2: Memory bandwidth achieved by fused stacked linear layers. Cross layer overlapping refers to starting to load weights for future layers before computation for the current layer has finished.

#### 4 METHODS

# 4.1 General Kernel Design Principles

We first elaborate on the key challenges in designing a family of whole-model kernels and describe how FLASHFORMER overcomes these challenges.

**Metaprogramming for static optimization.** New kernels need to be implemented for each model tested. Writing such kernels manually is time intensive and prone to bugs. Implemented kernels can vary greatly depending on factors such as model dimension and quantization settings. To address this, we developed a metaprogramming language (in Python) called CHEETAH<sup>3</sup>, which, given the dimension sizes of the model, performs static workload partitioning based on predetermined rules.

Concretely, because the exact workload is known at kernel generation, we can determine at compile time what memory operations and computations are necessary. In the memory-bound regime, we can load every element of our network parameters and KV cache exactly once. While this requires fully replicating the input, the cost of input data movement is orders of magnintude less than parameter and cache data movement. CHEETAH automates the index math and static workload distribution and outputs CUDA kernels, thus efficiently generating these static workload schedules. An example of the metaprogamming language, along with a generated kernel, is provided in Table 5, with more advanced examples in Table 10 in the appendix.

<sup>3</sup>https://github.com/cheetah-lang

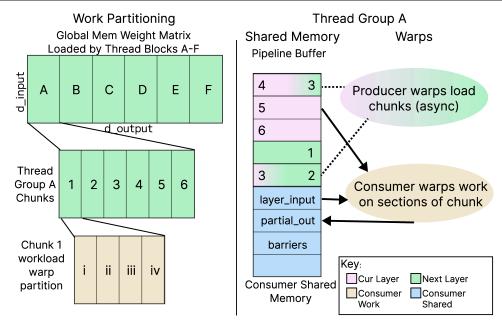

**Figure 3:** Left: Work partitioning between and within thread groups. The work for the matrix in global memory is split between thread groups. The work for each thread group is split into chunks for the pipeline buffer. Within the chunk, the work is divided into chunks. Right: Thread Group A work partitioning. Producer warps manage the pipeline buffer asynchronously, while consumer warps work synchronously on sections of chunks.

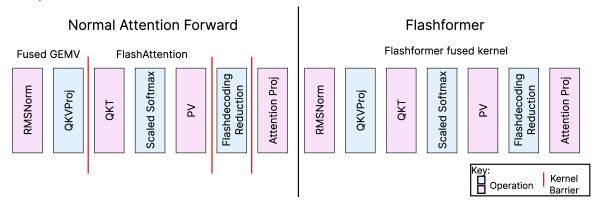

**Figure 4:** Conceptual diagram of a standard attention forward pass and our method. Left: a standard attention forward pass in an inference pipeline, broken down into four kernels. Right: FlashFormer, where all operations are part of one kernel invocation.

As seen in Figure 3, the workload is divided among different thread blocks, then within a thread block into multiple chunks. Finally, each chunk is processed by a series of warps in a series of operations. Factors like inter-thread block workload partitioning, chunk sizes, and intra chunk workload partitioning are optimized to maximize utilization of hardware resources, especially global-to-shared memory bandwidth.

**Memory pipeline.** Each layer has different sized matrices and different shared memory requirements. As shown in Figure 3, we design and implement a unified memory pipeline that allows for the memory movement of arbitrary layers to overlap, and for memory movement to overlap all other operations. This overlapping of memory movement with computation is also referred to as a producer-

consumer pipeline design and is used by generally used by fast GEMM-based kernels like FlashAttention-3 for Hopper GPUs (Shah et al., 2024a).

Specifically, each matrix listed in Table 1 is split into chunks of a fixed size in bytes. This chunk size remains the same throughout the model, although the data type of the chunk, number of elements, and matrix dimensions are subject to change. Each matrix's chunks are split among thread blocks at compile time. While all weight matrix chunks are loaded every iteration, KV cache chunks are only loaded as needed. Due to this structure, different sections of the matrix buffer can store matrix chunks from different layers or sublayers. The number of matrix buffers stored at a given time is the "depth" of the pipeline, and the size of one matrix buffer is the size of each pipeline stage.

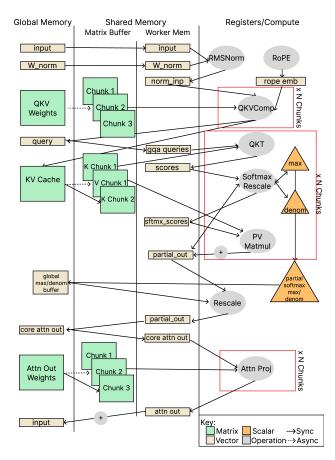

**Figure 5:** The Attention forward pass per layer. Large matrices (green) are loaded asynchronously from global, and do not wait on warps performing computation. The consumers works synchronously, with 3 global synchronizations per attention forward pass. Each of the repeated computations (in red) corresponds to a asynchronously loaded matrix split into chunks.

Global memory ordering. One potential issue with our approach is that the inputs for subsequent layers rely on the outputs of prior layer. Given the relaxed memory ordering of CUDA computations, we use a per thread global memory fence coupled with an atomic-based global synchronization mechanism to synchronize volatile reads and writes. This application of a traditional atomic synchronization ensures all participating threads' global memory operations are visible to all other participating threads before continuing execution to avoid a read-after-write race condition. While atomic-based synchronization is far from novel, using it to combine different transformer layers into a single fused kernel has not been explored before to our knowledge.

#### 4.2 Transformer-specific Kernel Design

We now describe how the above principles are operationalized for the transformer architecture.

**Attention.** We divide the attention sublayer into three parts, each of which has synchronous global communica-

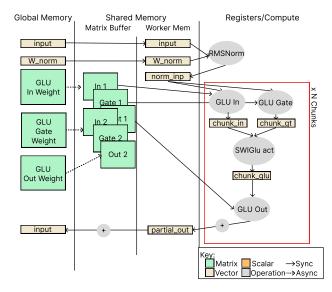

**Figure 6:** The GLU forward pass. Large matrices (green) are loaded asynchronously from global, and do not wait on consumers. The consumers works synchronously, with no synchronization to global within the sublayer.

tion between them: QKV Projection, Core Attention, and Attention Output Projection. A comparison of standard workload partitioning to ours can be found in Figure 4. Figure 5 delineates a more detailed diagram of the operations within each of the above parts.

In the batch one case, both QKV Projection and Attention Output projection are matrix vector operations. For these operations, we cache the input in shared memory, and each chunk of the matrix corresponds to some number of rows of the weight matrix. We compute RMSNorm, RoPE, and then QKV projection, and add the outputs of Attention Output projection directly to the residual stream.

For Core Attention, the thread blocks are split among the different KV heads, and for each KV head, each SM retains a replicated copy of queries which multiply with that particular KV head. The KV cache is then partitioned into matrix chunks, which are fed into the memory buffers. Since our pipelined approach has no memory ordering that guarantees the elements of the KV cache correspond to the current token, we synchronously load the keys and values for the current token.

After the entire KV cache has been read and the partial core attention output computed, we perform a reduction per KV head before writing to a shared buffer. The reduction occurs in three stages. First, each thread block writes required metadata for the FLASHDECODING-like reduction, e.g. the maximum logit and the softmax denominator. In the second stage, each thread block reads the combined metadata and computes the global softmax denominator. It then rescales its output by the ratio of the thread block's softmax denominator.

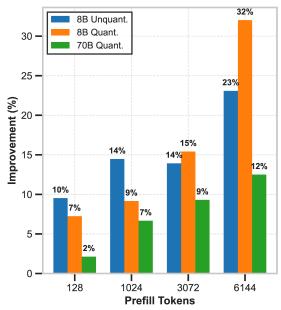

**Figure 7:** Percentage improvements in decoding tokens per second (TPS) of our kernel over GPTFast.

nator to the combined softmax denominator, as in Milakov & Gimelshein (2018). Finally, all threads add their rescaled outputs to a cumulative sum in global memory. Compared to the FLASHDECODING kernel (Dao et al., 2023), the reduction is fused into the output computation kernel, removing one activation round trip.

**GLU.** In our kernel, the GLU in/gate operation is a matrix vector operation very similar to the QKV and Attention Output Projection operations in Attention, as shown in Figure 6. Unlike those operators, the output of each chunk of the GLU in/gate operation is not written to global memory. Instead, we compute the SwiGLU activation on the outputs of the GLU in/gate function and then multiply it with a matrix chunk of GLU out. We then keep a vector of size  $d_{model}$  for accumulating partial outputs. With this approach, we can iterate through the entirety of the GLU computation without needing to do any synchronization or reduction. At the end the computation, we reduce all of these partial outputs along with the input. See Figure 6 for a full schematic.

## 5 EXPERIMENTS

#### 5.1 Experimental Setup

We apply our kernel to three models: Llama 3.1 8B unquantized, Llama 3.1 8B quantized, and Llama 3.1 70B quantized. We compare with two strong baselines that are widely used in practice: GPTFast<sup>4</sup> and vLLM<sup>5</sup> (Kwon et al., 2023). We enable all optimizations where possible. In particular, we enable CUDA graphs to decrease kernel launch overheads in our baselines.

per output. We only measure decoding speed, as prefill is compute bound. As a result, we only need to generate enough tokens to achieve a good estimate of the per-token latency with a given amount of prefill. All experiments are performed on one H100 SXM GPU.

We test a variety of prefill lengths, and generate 128 tokens

#### 5.2 Main Results

Batch size = 1 case. We first focus on the batch size = 1 setting and show the results in Table 6 and Figure 7. On unquantized Llama 3.1 8B, we find that our kernel achieves a 8-20% speedup over GPTFast, and up to a 61% speedup over vLLM. We observe similar improvements with quantization, where we use GPTQ (Frantar et al., 2022) to perform weight-only integer quantization to 4 bits with a group size of 128. While this computation is likely bottlenecked by the operations needed for dequantization and not memory bandwidth, our approach allows us better to overlap dequantization with memory movement and computation.

We also evaluate on a large quantized model, Llama 3.1 70B. Our expectation was that the gains at 70B would be smaller than at 8B. This is because larger models have more opportunities for overlapping within a kernel. This decreases the need for overlapping between kernel launches. The results, shown in Table 6, are small improvements (2%) at short sequence lengths increasing to 13% at longer sequence lengths.

Larger batch sizes. We perform experiments with batch size two and four with the unquantized 8B model. We consider the case where KV caches are entirely distinct between elements of the batch, and generation for all queries within the batch starts and stops at the same time. These batched kernels are still input stationary: weights are read in exactly once, and inputs are fully replicated on each SM. The synchronization and bandwidth savings from the batch size one case hold in the slightly larger batch setting, as shown in Table 7. However, memory bandwidth utilization decreases, as the increased shared memory pressure does force smaller memory pipelines or a minimal L1 cache.

**Discussion.** Two trends emerged in our experiments. First, FLASHFORMER had the largest speedups at the longest sequence lengths. We suspect this is due to our method of partitioning the KV cache. The size of our pipeline stages is 64KB, which corresponds to 256 keys or values with head dim 128 and BF16 precision. With 8 SMs per KV head, we need 4096 keys and values to provide one matrix chunk per participating SM. At longer sequence lengths this problem vanishes. Instead, FLASHFORMER overlaps more of the core attention computation and reduction with memory movement, improving bandwidth utilization. Future work can explore better optimization of workloads at different sequence lengths.

<sup>4</sup>https://github.com/pytorch-labs/gpt-fast

5https://github.com/vllm-project/vllm

# **Python Implementation**

# **Generated CUDA Kernel**

**Table 5:** Upper Left: Python kernel source. Upper Right: Generated CUDA kernel. Our metaprogramming language generates CUDA kernels from a Python interface. We use this to automate index math, perform static workload scheduling, and build kernel metaprogramming tools. More advanced examples can be found in Table 7 in the appendix.

| Model  | Prefill | Tokens per second |      |             |  |

|--------|---------|-------------------|------|-------------|--|

| Size   | Size    | GPTFast           | vLLM | FLASHFORMER |  |

| 8B     | 128     | 168               | 146  | 184         |  |

| (BF16) | 1024    | 159               | 144  | 182         |  |

|        | 3072    | 158               | 141  | 180         |  |

|        | 6144    | 143               | 138  | 176         |  |

| 8B     | 128     | 290               | 193  | 311         |  |

| (INT4) | 1024    | 284               | 186  | 310         |  |

|        | 3072    | 266               | 189  | 307         |  |

|        | 6144    | 228               | 175  | 301         |  |

| 70B    | 128     | 47                | -    | 48          |  |

| (INT4) | 1024    | 45                | -    | 48          |  |

|        | 3072    | 43                | -    | 47          |  |

|        | 6144    | 40                | -    | 45          |  |

**Table 6:** Prefill size and tokens per second (TPS) for the model configurations in the batch one case for the LLama 3.1 series of models. We were unable to get vLLM numbers for LLama 3.1 70B quantized results due to system errors.

The second trend we observe is that smaller models benefit more from our technique than larger models, as evidenced by Figure 7. This is likely due to the fact that very large models have more opportunities for overlapping within each operation, and thus gain less benefit from overlapping between operations.

#### 5.3 Ablations & Analysis

We next perform a series of ablations and analyses.

**Pipeline depth.** We investigate how increasing pipeline stages affects kernel performance for the unquantized Llama 3.1 8B model. Our kernel design requires a minimum of two concurrent memory buffers during GLU computation. Consequently, a two-stage pipeline cannot overlap memory operations during GLU in/gate operations. The kernel was primarily optimized for a 64KB pipeline stage size. Performance measurements comparing two versus three pipeline stages at 3072 sequence length reveal that three

| Batch Size | SL   | GPTFast | vLLM | FLASHFORMER |

|------------|------|---------|------|-------------|

| 2          | 128  | 308     | 286  | 328         |

| 4          | 128  | 608     | 564  | 616         |

| 2          | 1024 | 556     | 560  | 648         |

| 4          | 1024 | 504     | 548  | 600         |

**Table 7:** Batched tokens per second for unquantized Llama 3.1 8B under various settings. SL Stands for sequence length.

| Pipeline Stage Size | Number of Stages | TPS |

|---------------------|------------------|-----|

| 64KB                | 2                | 170 |

| 64KB                | 3                | 179 |

| 32KB                | 3                | 143 |

| 32KB                | 4                | 138 |

| 32KB                | 5                | 130 |

**Table 8:** Llama 3.1 8B unquantized pipeline depth ablation at sequence length 3072. We primarily optimize for 64KB pipeline stage size, and thus have worse workload partitioning at 32KB.

stages achieves a 5% speedup over two stages, as shown in Table 8.

Due to shared memory capacity constraints, we cannot implement four pipeline stages at 64KB per stage. To test deeper pipelines, we halved the pipeline stage size, though these configurations were not as thoroughly optimized as the larger stage implementations. Results indicate that while four pipeline stages outperform three, five stages do not yield further improvements over four. At this depth, pipeline management overhead negates the benefits of deeper pipelining.

**Attention & GLU kernels.** We measure the latency and memory bandwidth of stacked layers of Attention and GLU blocks, similar to our motivating study with stacked linear layers. The results are in Table 9 and Figure 8.

For latency, we see that double digit latency improvements

| Module | Layers | Baseline | Fused | +Overlap |

|--------|--------|----------|-------|----------|

|        | 1      | 0.089    | 0.089 | 0.090    |

| Attn   | 4      | 0.357    | 0.264 | 0.256    |

|        | 32     | 2.857    | 1.761 | 1.683    |

|        | 1      | 0.122    | 0.122 | 0.122    |

| GLU    | 4      | 0.488    | 0.466 | 0.464    |

|        | 32     | 3.905    | 3.689 | 3.661    |

**Table 9:** Component-wise latencies for multilayer attention and GLU kernels, in ms. Baseline does not fuse any layers. Fused refers to a kernel that fuses across layers without memory overlapping. + Overlap incorporates cross-layer memory overlapping.

occur from cross layer fusion, and single digit improvements occur from cross layer memory overlapping, regardless of layer type. Additionally, we ablate the width and depth of our pipeline for the Attention and GLU kernels. While the the attention and linear layers are fastest with a depth 2 pipeline, the GLU layer is fastest with a depth 3 pipeline. As GLU represents the majority of parameters and latency, the composite kernel is fastest with a depth 3 pipeline. Future work may look at adaptively changing pipeline size throughout the model

For memory bandwidth, while stacked GLU blocks are able exceed 90% of machine peak, our stacked attention blocks achieve roughly 50% of machine peak. Compared to GLU layers, attention layers have more logic, special functions, and synchronization with less memory movement to hide them. Note that as nearly eighty percent of layer parameters are in GLU layers, the bandwidth of our resulting kernel is much closer to the bandwidth of the stacked GLU layer.

#### 6 DISCUSSION & LIMITATIONS

# 6.1 Handwritten vs Compiled Kernels

One interesting direction of research is automatically compiling whole-model kernels. MIRAGE (Wu et al., 2025) recently added support to user their kernel generator to automatically generate whole model kernels. We implemented an optimized Llama3 in for Hopper GPUs in their framework and compared TPS numbers. Unfortunately their benchmarking tools combine prefill and decoding latency, but even when generating without any prefill the peak performance we achieved was 153 TPS with LLama3 8B. The difference in performance appears to be due to better work partitioning, decreased synchronization, and greater overlapping in our kernel. Currently, the greater exploration space opened up by handwriting kernels leads to 20% performance gains in our case.

#### 6.2 Compile vs. Runtime optimization

The work partitioning within our kernels—in particular, the partitioning of matrix chunks between thread blocks—is

**Figure 8:** Attention and GLU memory bandwidth in an unquantized Llama 3.1 8B kernel. While GLU nears hardware peak, our attention implementation achieves closer to 50% of peak bandwidth. As GLU dominates memory usage, net bandwidth is much closer to GLU memory bandwidth.

determined at compile time. This simplifies kernel logic and minimizes communication to global memory.

However, there are drawbacks to this strategy. At every point of synchronization, the entire GPU is held back by the slowest SM. Furthermore, it can lead to inefficiency when the amount of work changes at runtime, which happens with the KV cache. For our workloads, we tried to avoid this problem through careful division of memory loads. Works such as ThunderMLA (Spector et al., 2023) also implement a dynamic workload partitioning for a persistent FLASHATTENTION style Multi Latent Attention (DeepSeek-AI, 2024) kernel, controlled through a global instruction buffer. Their persistent kernel accesses a global memory buffer to determine what problem to work on next.

We hope that future work explores dynamic runtime optimized versions of FLASHFORMER, and explores the trade-off between increased inter thread block communication to better balance the workload and decreased inter thread block communication to minimize per thread block latency.

# 6.3 Limitations

Our work is limited insofar as we target the single-GPU, low-batch setting for the Hopper family of architectures. We focus on this setting to demonstrate the practicality of the core ideas introduced in this paper, including aggressive specialization and the feasibility of a kernel design with a static workload schedule. We hope that future work applies these ideas to larger-batch, multi-GPU settings on different families or architectures, as well as to non-transformer models. Furthermore while we contribute a custom kernel metaprogramming library with customizable kernel templates, further work is needed to extend our abstractions to a greater variety of models and multi-GPU settings.

## 7 RELATED WORK

**Specialized Transformer model kernels.** Due to the fact that the linear / GLU layers are standard linear algebra operations, most of the focus of specialized transformer kernel design has focused on optimizing attention. The FlashAttention (Dao et al., 2022; Dao, 2023; Shah et al., 2024b) restructures the attention computation to a numerically equivalent version that fused all of core attention. This general strategy is widespread and was used in many attention or attention-like operations.

Accelerator Kernel DSLs, such as Triton (Tillet et al., 2019), are used to simplify the kernel generation process by grouping computation into conceptual tiles. Specialized tools such as FlexAttention (Guessous et al., 2024) further allow for simple kernel generation for attention like workloads. Recently, automatic fusion of pointwise operators has continued to improve and become a staple of all modern machine learning libraries. XLA (Sabne, 2020) and PyTorch Compile (Ansel et al., 2024) automate fusion of pointwise operations for Jax (Bradbury et al., 2018) and PyTorch respectively.

Concurrent to this work, ThunderMLA (Spector et al., 2023) introduce a persistent kernel for MultiHead Latent Attention (DeepSeek-AI, 2024) layers that has each thread block dynamically schedule its own workload.

Low batch inference optimizations. Better kernel design is far from the only research area pursuing greater inference efficiencies. Two of the most important research directions in low batch inference are speculative decoding and quantization.

Speculative decoding (Leviathan et al., 2022) performs autoregressive inference on a small model and multi-token inference on a larger model. This relies on similarity between the model distributions and the relative speed of the small model. The critical idea was that the large verifier model would run at an effective batch size as long as the number of consecutive tokens fed into the model. Conditioned on the tokens verification, a single large model load could generate multiple tokens. Further iterations (Cai et al., 2024; Ankner et al., 2024; Li et al., 2024) improved upon this formula by using draft heads computed on the model's outputs instead of a separate draft model.

Weight quantization methods (Frantar et al., 2022; Yao et al., 2022; Chee et al., 2023) have accelerated decoding by enabling lower and lower bit precisions for weight loads. This decreases the cost of memory movement, and thus improves inference speed. However, this is not perfect, as most of these methods utilize scarce GPU resources for dequantization.

# 8 CONCLUSION

We introduce a new method for overlapping operations between layers for transformer decoding workloads. We develop a family of kernels that leverage this new method of overlapping, and empirically verify the performance of these models on real workloads.

#### ACKNOWLEDGEMENTS

This work was supported by the National Science Foundation under CAREER Award No. 2441872 and the MIT-IBM Watson AI Lab.

#### REFERENCES

- Ainslie, J., Lee-Thorp, J., De Jong, M., Zemlyanskiy, Y., Lebrón, F., and Sanghai, S. Gqa: Training generalized multi-query transformer models from multi-head checkpoints. *arXiv preprint arXiv:2305.13245*, 2023.

- Ankner, Z., Parthasarathy, R., Nrusimha, A., Rinard, C., Ragan-Kelley, J., and Brandon, W. Hydra: Sequentially-dependent draft heads for medusa decoding, 2024.

- Ansel, J., Yang, E., He, H., Gimelshein, N., Jain, A., Voznesensky, M., Bao, B., Bell, P., Berard, D., Burovski, E., Chauhan, G., Chourdia, A., Constable, W., Desmaison, A., DeVito, Z., Ellison, E., Feng, W., Gong, J., Gschwind, M., Hirsh, B., Huang, S., Kalambarkar, K., Kirsch, L., Lazos, M., Lezcano, M., Liang, Y., Liang, J., Lu, Y., Luk, C., Maher, B., Pan, Y., Puhrsch, C., Reso, M., Saroufim, M., Siraichi, M. Y., Suk, H., Suo, M., Tillet, P., Wang, E., Wang, X., Wen, W., Zhang, S., Zhao, X., Zhou, K., Zou, R., Mathews, A., Chanan, G., Wu, P., and Chintala, S. PyTorch 2: Faster Machine Learning Through Dynamic Python Bytecode Transformation and Graph Compilation. In 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2 (ASPLOS '24). ACM, April 2024. doi: 10.1145/3620665.3640366. URL https: //pytorch.org/assets/pytorch2-2.pdf.

- Bradbury, J., Frostig, R., Hawkins, P., Johnson, M. J., Leary, C., Maclaurin, D., Necula, G., Paszke, A., VanderPlas, J., Wanderman-Milne, S., and Zhang, Q. JAX: composable transformations of Python+NumPy programs, 2018. URL http://github.com/jax-ml/jax.

- Cai, T., Li, Y., Geng, Z., Peng, H., Lee, J. D., Chen, D., and Dao, T. Medusa: Simple llm inference acceleration framework with multiple decoding heads. In *Proceedings of the 41st International Conference on Machine Learning*, ICML'24. JMLR.org, 2024.

- Chee, J., Cai, Y., Kuleshov, V., and De Sa, C. M. Quip: 2-bit quantization of large language models with guarantees.

- Advances in Neural Information Processing Systems, 36: 4396–4429, 2023.

- Dao, T. Flashattention-2: Faster attention with better parallelism and work partitioning. *arXiv* preprint *arXiv*:2307.08691, 2023.

- Dao, T. FlashAttention-2: Faster attention with better parallelism and work partitioning. In *International Conference* on *Learning Representations (ICLR)*, 2024.

- Dao, T., Fu, D. Y., Ermon, S., Rudra, A., and Ré, C. FlashAttention: Fast and memory-efficient exact attention with IO-awareness. In Advances in Neural Information Processing Systems (NeurIPS), 2022.

- Dao, T., Haziza, D., Massa, F., and Sizov, G. Flash-decoding for long-context inference, 2023. URL https://crfm.stanford.edu/2023/10/12/flashdecoding.html.

- DeepSeek-AI. Deepseek-v2: A strong, economical, and efficient mixture-of-experts language model, 2024.

- Frantar, E., Ashkboos, S., Hoefler, T., and Alistarh, D. GPTQ: Accurate post-training compression for generative pretrained transformers. *arXiv* preprint *arXiv*:2210.17323, 2022.

- Grattafiori, A., Dubey, A., Jauhri, A., Pandey, A., Kadian, A., Al-Dahle, A., Letman, A., Mathur, A., Schelten, A., Vaughan, A., et al. The llama 3 herd of models. *arXiv* preprint arXiv:2407.21783, 2024.

- Guessous, D., Liang, Y., Dong, J., and He, H. Flexattention: The flexibility of pytorch with the performance of flashattention, 8 2024. URL https://pytorch.org/blog/flexattention/. Accessed on March 29, 2025.

- Jiang, Z., Gu, J., Zhu, H., and Pan, D. Pre-rmsnorm and precrmsnorm transformers: equivalent and efficient pre-ln transformers. Advances in Neural Information Processing Systems, 36:45777–45793, 2023.

- Kwon, W., Li, Z., Zhuang, S., Sheng, Y., Zheng, L., Yu, C. H., Gonzalez, J., Zhang, H., and Stoica, I. Efficient memory management for large language model serving with pagedattention. In *Proceedings of the 29th Symposium on Operating Systems Principles*, SOSP '23, pp. 611–626, New York, NY, USA, 2023. Association for Computing Machinery. ISBN 9798400702297. doi: 10.1145/3600006.3613165. URL https://doi.org/10.1145/3600006.3613165.

- Leviathan, Y., Kalman, M., and Matias, Y. Fast inference from transformers via speculative decoding, 2022.

- Li, Y., Wei, F., Zhang, C., and Zhang, H. Eagle: Speculative sampling requires rethinking feature uncertainty, 2024.

- Milakov, M. and Gimelshein, N. Online normalizer calculation for softmax, 2018. URL https://arxiv.org/abs/1805.02867.

- Sabne, A. Xla: Compiling machine learning for peak performance, 2020.

- Shah, J., Bikshandi, G., Zhang, Y., Thakkar, V., Ramani, P., and Dao, T. Flashattention-3: Fast and accurate attention with asynchrony and low-precision, 2024a. URL https://arxiv.org/abs/2407.08608.

- Shah, J., Bikshandi, G., Zhang, Y., Thakkar, V., Ramani, P., and Dao, T. FlashAttention-3: Fast and Accurate Attention with Asynchrony and Low-precision. November 2024b.

- Shazeer, N. Glu variants improve transformer. *arXiv* preprint arXiv:2002.05202, 2020.

- Spector, B., Singhal, A., Fu, D., and Ré, C. Thundermla: Flashmla, faster and fused-er!, 2023. URL https://hazyresearch.stanford.edu/blog/2025-03-04-thundermla.

- Su, J., Lu, Y., Pan, S., Wen, B., and Liu, Y. RoFormer: Enhanced Transformer with Rotary Position Embedding. *CoRR*, abs/2104.09864, 2021. arXiv: 2104.09864.

- Tillet, P., Kung, H. T., and Cox, D. Triton: an intermediate language and compiler for tiled neural network computations. In *Proceedings of the 3rd ACM SIGPLAN International Workshop on Machine Learning and Programming Languages*, MAPL 2019, pp. 10–19, New York, NY, USA, 2019. Association for Computing Machinery. ISBN 9781450367196. doi: 10.1145/3315508.3329973. URL https://doi.org/10.1145/3315508.3329973.

- Wu, M., Cheng, X., Liu, S., Shi, C., Ji, J., Ao, K., Velliengiri, P., Miao, X., Padon, O., and Jia, Z. Mirage: A multi-level superoptimizer for tensor programs. In 19th USENIX Symposium on Operating Systems Design and Implementation (OSDI 25), Boston, MA, July 2025. USENIX Association.

- Yao, Z., Yazdani Aminabadi, R., Zhang, M., Wu, X., Li, C., and He, Y. Zeroquant: Efficient and affordable posttraining quantization for large-scale transformers. Advances in Neural Information Processing Systems, 35: 27168–27183, 2022.

# A METAPROGRAMMING LANGUAGE EXAMPLE

Table  $10~{\rm shows}$  more examples from our Cheetah metaprogramming language.

#### **Python Implementation**

```

class AsyncBarrierGTSCopyFn(SmartScopeFn):

def setup(

self.

src_cfg: SDIPConfig,

dst_cfg: SDIPConfig,

thread_idx: DimName,

cpy_idx: DimName,

):

def generate(

ix: Indices,

src_ptr: SafeDataIndexPtr,

dst_ptr: SafeDataIndexPtr,

barrier: SharedMBarrier,

size = (ix.size(self.cpy_idx) *

dst_ptr.get_elem_size())

ix.set_index(self.cpy_idx, ch.const(0, ty.i32))

assert size % 16 == 0

with ch.if_(ix[self.thread_idx] == 0):

ch.asm(

f"cp.async.bulk.shared::cluster.global.

mbarrier::complete_tx::bytes [

$dst_ptr], [$src_ptr], {size},

$barrierl:",

dst ptr=dst ptr.idx offset(),

src ptr=src ptr.idx offset().

barrier=barrier.ptr,

ch.asm(

f"mbarrier.expect tx.relaxed.cta.shared.

b64 [$barrier], {size};",

barrier=barrier.ptr,

ch.raw_stmt("__syncwarp();")

async_gts_copy_fn(ix, src_ptr, shared_ptr,

shared barrier)

```

#### **Generated CUDA Kernel**

```

int32_t elem_idx0 = 0;

if (thread_idx == 0) {

asm ("cp.async.bulk.shared::cluster.global.

mbarrier::complete_tx::bytes [%0], [%1],

32768, [%2];" :: "l"(&shared[elem_idx0]),

"l"(&x[elem_idx0]), "r"(mbar_shmem));

asm ("mbarrier.expect_tx.relaxed.cta.shared.b64

[%0], 32768;" :: "r"(mbar_shmem));

}

__syncwarp();

```

```

self.qk_compute_fn(

ix,

self.shared_query_buffer_ptr,

k_buffer,

self.scores_ptr,

self.mem_pipeline.consumer_barrier,

```

```

for (int32_t k_iter_idx1 = 0; k_iter_idx1 < 16;

k_iter_idx1 += 1) {

for (int32_t n_iter_idx1 = 0; n_iter_idx1 < 4;

n_{iter_idx1} += 1) {

asm volatile (

"mma.sync.aligned.m16n8k8.row.col.f32.

bf16.bf16.f32 { %0, %1, %2, %3}\n"

", { %8, 0.0}\n"

{ %9}\n"

", { %4, %6, %5, %7};\n" : "=f"(f0), "=f"(f1), "=f"(f2), "=f"(f3) : "f"(

out_cache0[n_iter_idx2 * 2 + 0]),

f"(0.0f), "f"(out_cache0[

n_{iter_idx2 * 2 + 1]), "f"(0.0f),

r"(reinterpret_cast<int32_t*>(&

mat1\_cache0[k\_iter\_idx1 * 2 + 0])

[0]), "r"(reinterpret_cast<int32_t

*>(&mat2_cache0[n_iter_idx2 * 2 +

0])[0]));

out_cache0[n_iter_idx2 * 2 + 0] = f0;

out\_cache0[n\_iter\_idx2 * 2 + 1] = f1;

}

```

Table 10: Upper Left: A CHEETAH Python class that used for bulk async copies. Through the use of input configs and knowledge of valid use of the assembly instruction, it automates validation. When called during kernel generation it first checks the validity of the barrier and copy size, then solves index math, then outputs the code snippet on the right. Names can be specified for CUDA variables, and assembly and raw CUDA can be inserted at any point of program flow. Lower Left: an example of a higher level CHEETAH function, for the QK projection in attention. After the m,k, and n of the matmul are specified, loops and assembly instructions are automatically generated. In this particular example, only half of the outputs of the MMA are used due to the size of the computation, which is also automatically handled.